CENG 241 Digital Design 1 Lecture 3 Amirali

- Slides: 26

CENG 241 Digital Design 1 Lecture 3 Amirali Baniasadi amirali@ece. uvic. ca

This Lecture z Review of last lecture z Boolean Algebra 2

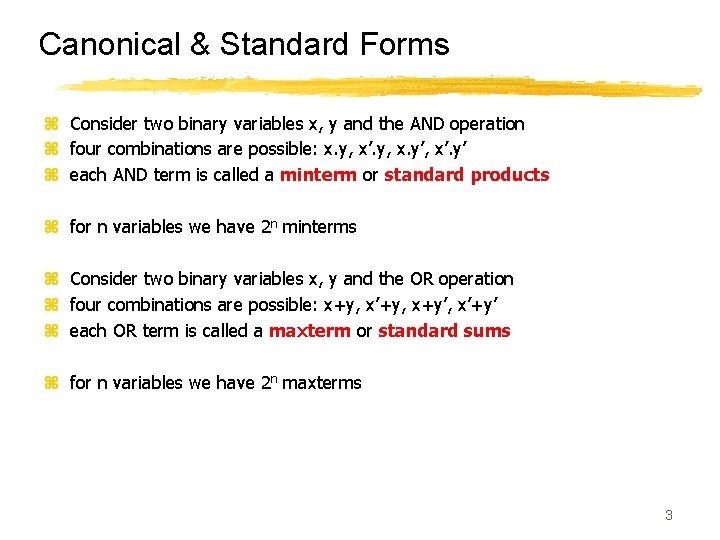

Canonical & Standard Forms z Consider two binary variables x, y and the AND operation z four combinations are possible: x. y, x’. y, x. y’, x’. y’ z each AND term is called a minterm or standard products z for n variables we have 2 n minterms z Consider two binary variables x, y and the OR operation z four combinations are possible: x+y, x’+y, x+y’, x’+y’ z each OR term is called a maxterm or standard sums z for n variables we have 2 n maxterms 3

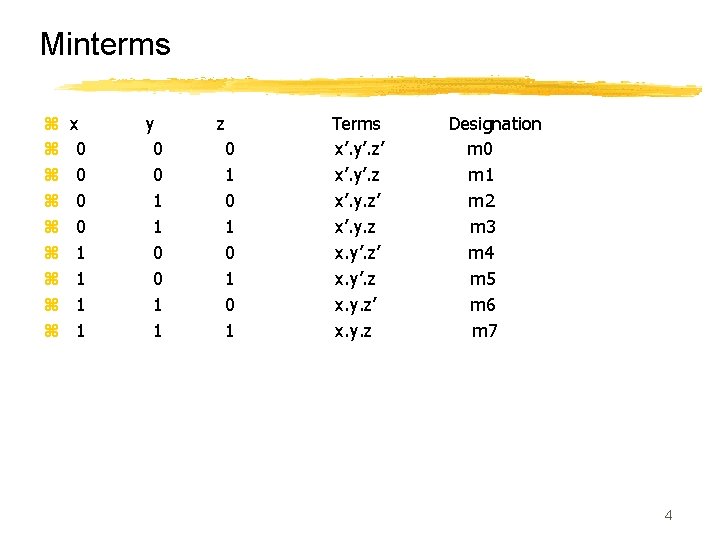

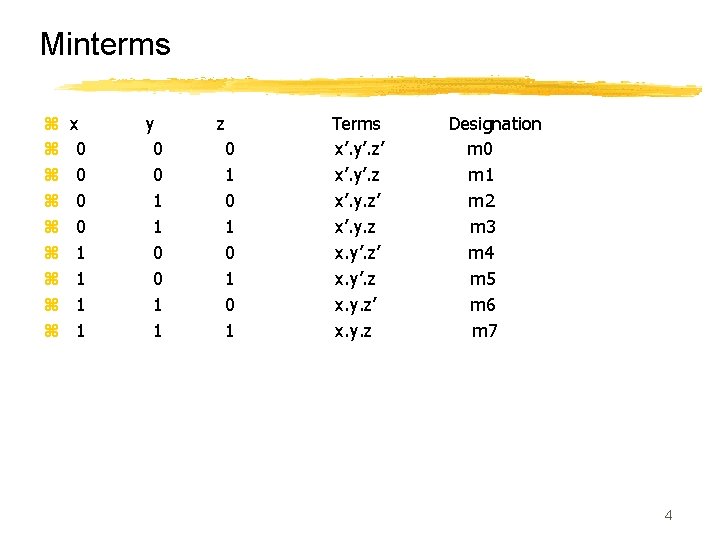

Minterms z z z z z x 0 0 1 1 y 0 0 1 1 z 0 1 0 1 Terms x’. y’. z’ x’. y’. z x’. y. z’ x’. y. z x. y’. z’ x. y’. z x. y. z’ x. y. z Designation m 0 m 1 m 2 m 3 m 4 m 5 m 6 m 7 4

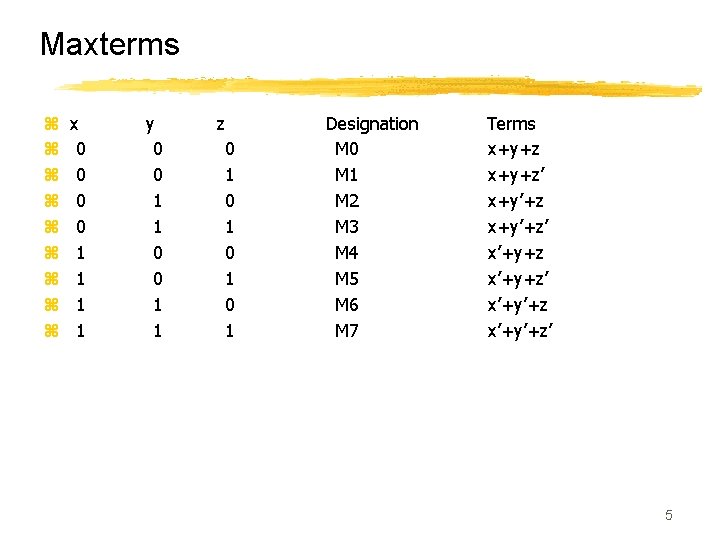

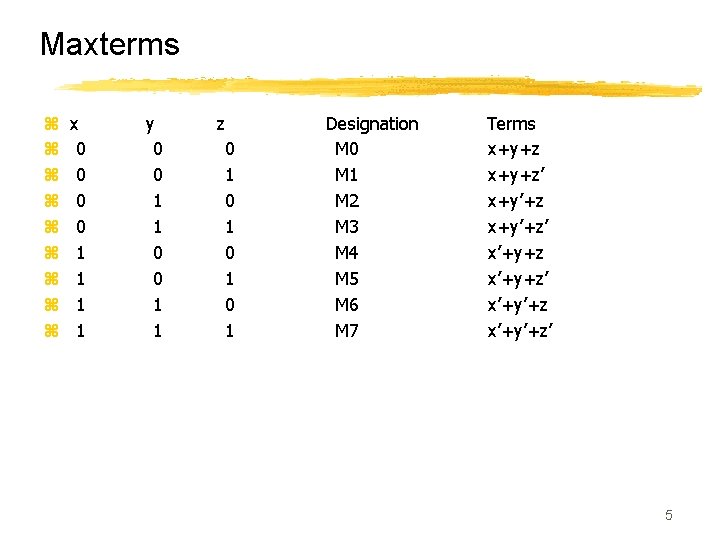

Maxterms z z z z z x 0 0 1 1 y 0 0 1 1 z 0 1 0 1 Designation M 0 M 1 M 2 M 3 M 4 M 5 M 6 M 7 Terms x+y+z’ x+y’+z’ x’+y+z’ x’+y’+z’ 5

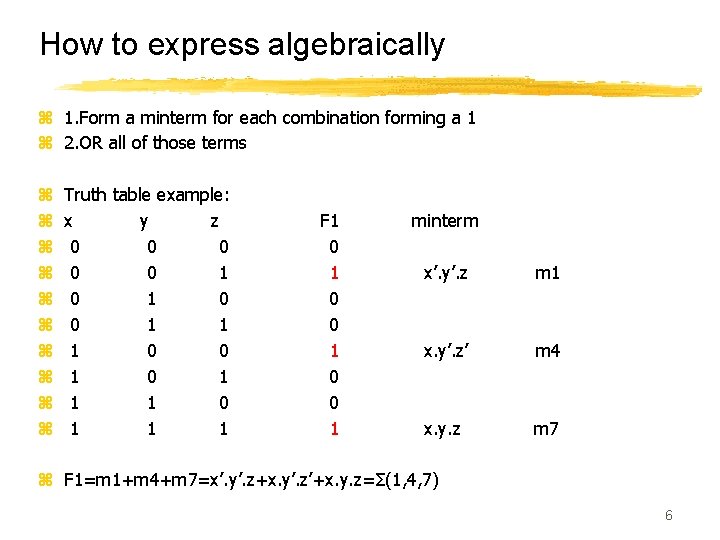

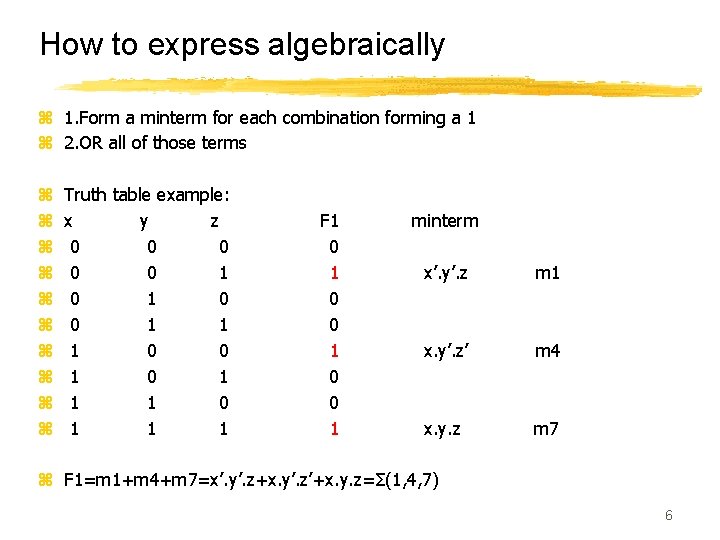

How to express algebraically z 1. Form a minterm for each combination forming a 1 z 2. OR all of those terms z z z z z Truth table example: x y z 0 0 0 1 1 1 0 0 1 1 1 F 1 0 0 1 minterm x’. y’. z m 1 x. y’. z’ m 4 x. y. z m 7 z F 1=m 1+m 4+m 7=x’. y’. z+x. y’. z’+x. y. z=Σ(1, 4, 7) 6

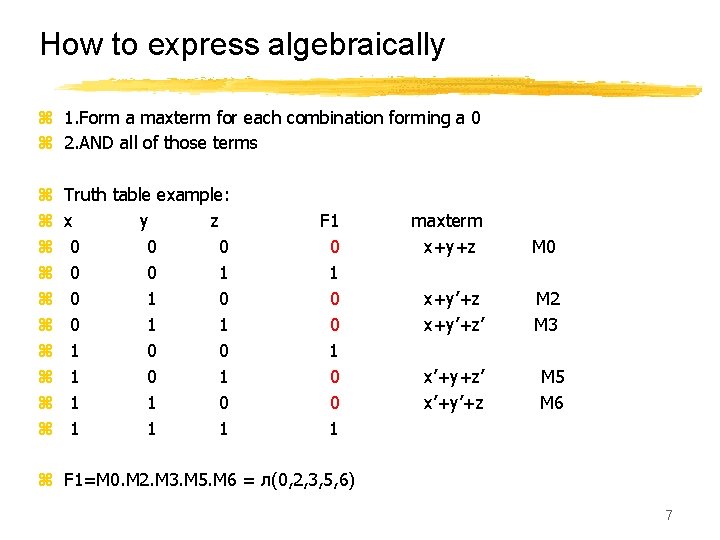

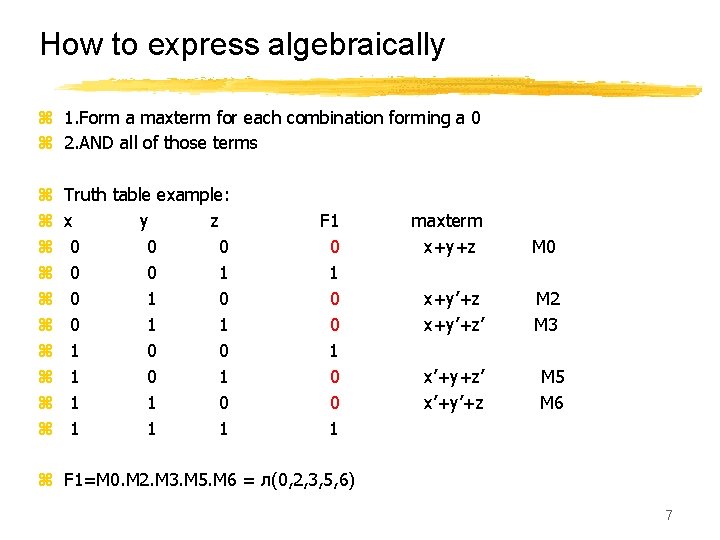

How to express algebraically z 1. Form a maxterm for each combination forming a 0 z 2. AND all of those terms z z z z z Truth table example: x y z 0 0 0 1 1 1 0 0 1 1 1 F 1 0 0 1 maxterm x+y+z M 0 x+y’+z’ M 2 M 3 x’+y+z’ x’+y’+z M 5 M 6 z F 1=M 0. M 2. M 3. M 5. M 6 = л(0, 2, 3, 5, 6) 7

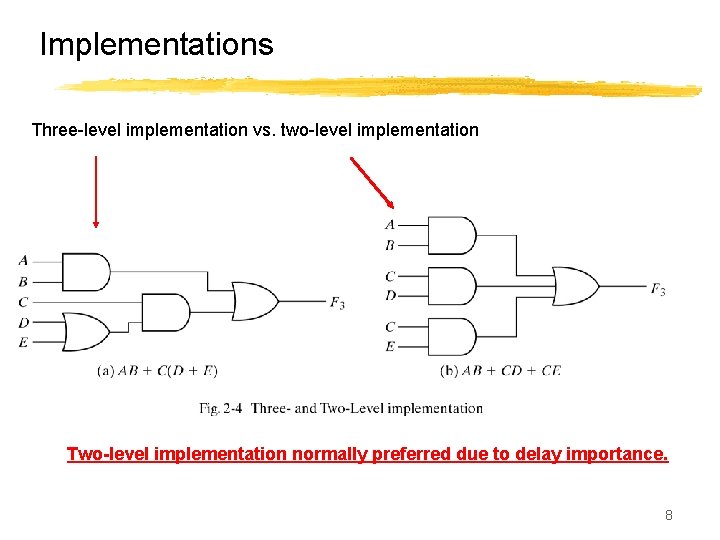

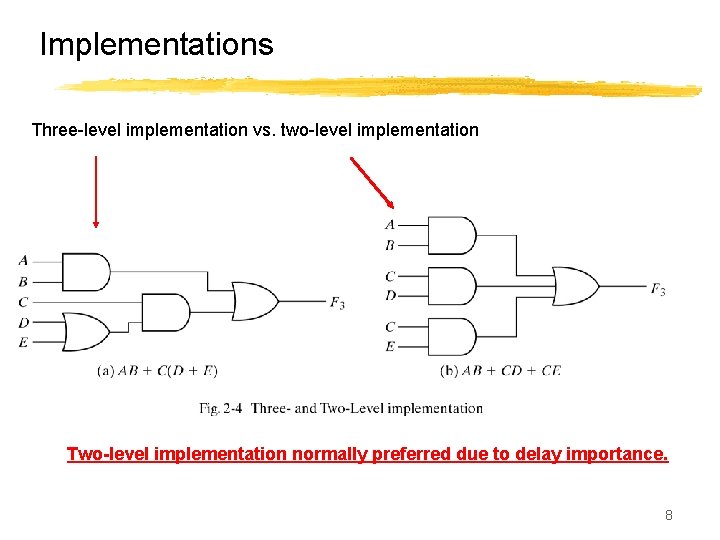

Implementations Three-level implementation vs. two-level implementation Two-level implementation normally preferred due to delay importance. 8

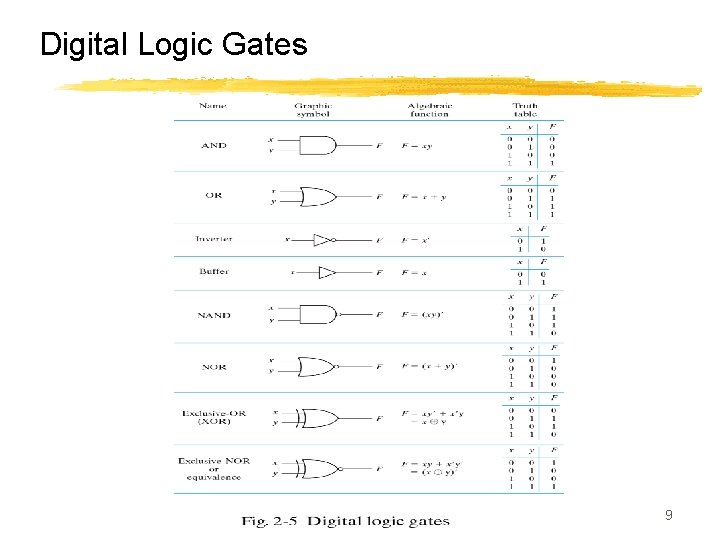

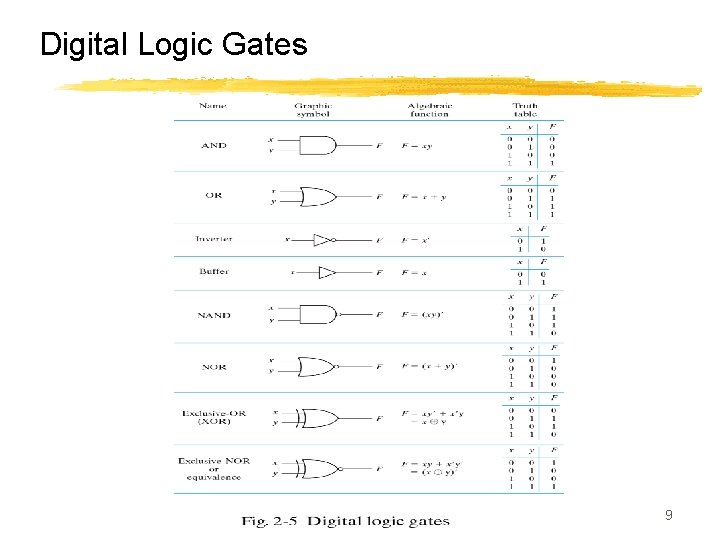

Digital Logic Gates 9

Integrated Circuits (ICs) z Levels of Integration z z SSI: fewer than 10 gates on chip MSI: 10 to 1000 gates on chip LSI: thousands of gates on chip VLSI: Millions of gates on chip z z z Digital Logic Families TTL transistor-transistor logic ECL emitter-coupled logic MOS metal-oxide semiconductor CMOS complementary metal-oxide semiconductor 10

Digital Logic Parameters z Fan-out: maximum number of output signals z Fan-in : number of inputs z Power dissipation z Propagation delay z Noise margin: maximum noise 11

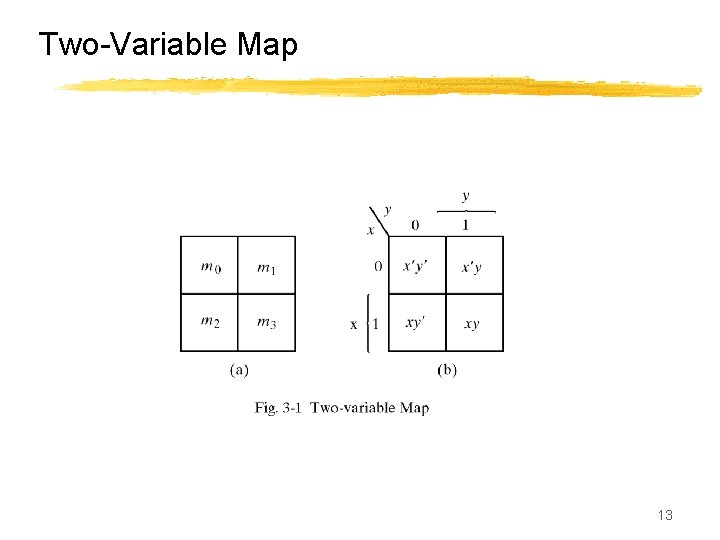

Gate-Level Minimization z The Map Method: z A simple method for minimizing Boolean functions z Map: diagram made up of squares z Each square represents a minterm 12

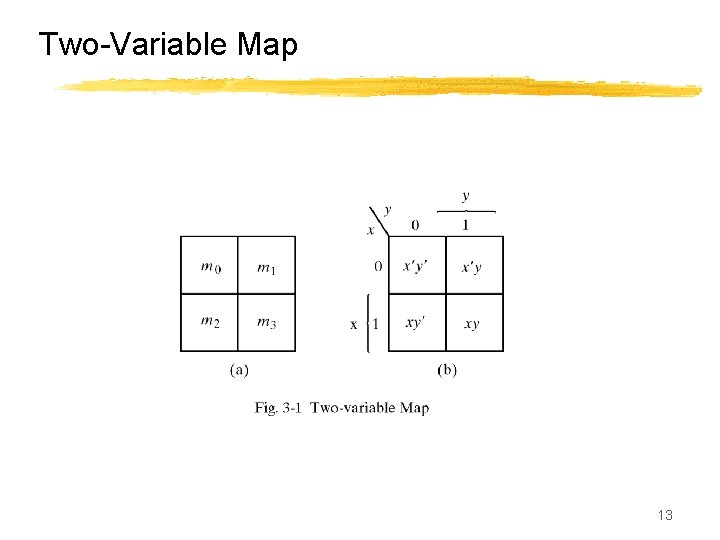

Two-Variable Map 13

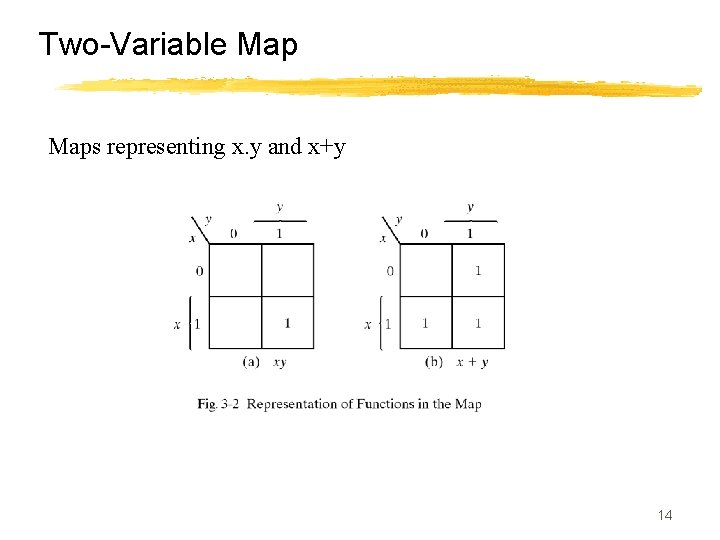

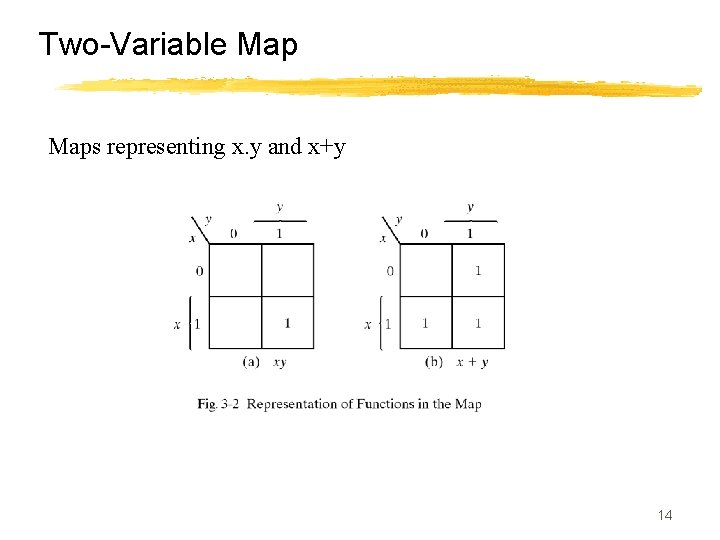

Two-Variable Maps representing x. y and x+y 14

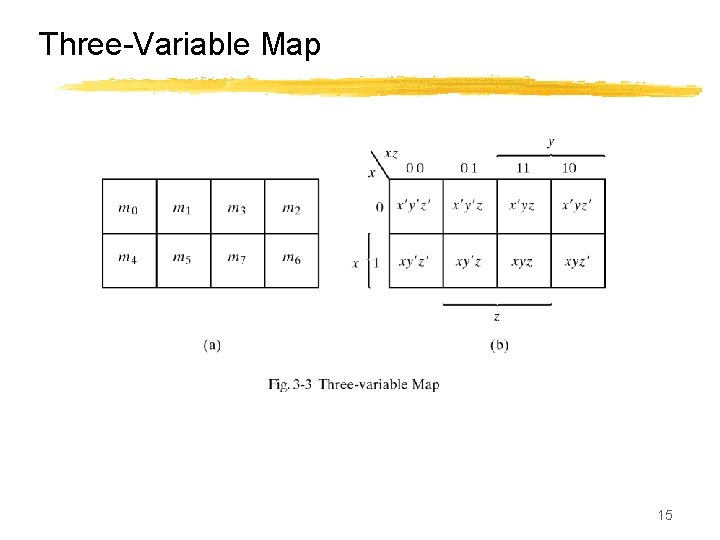

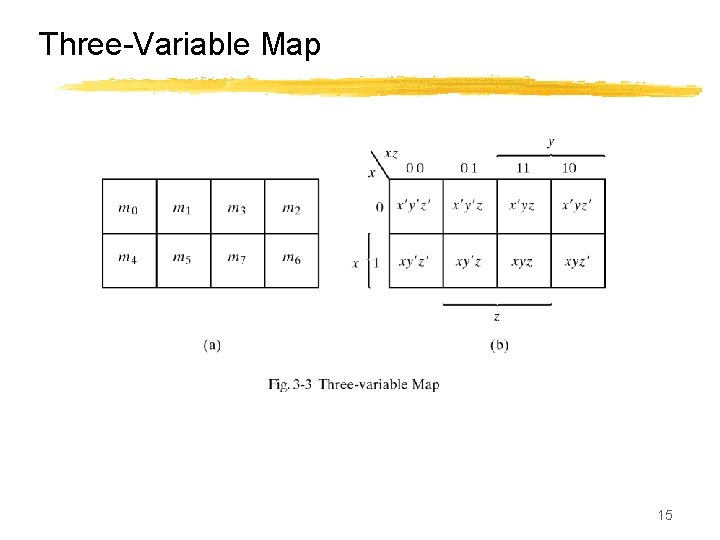

Three-Variable Map 15

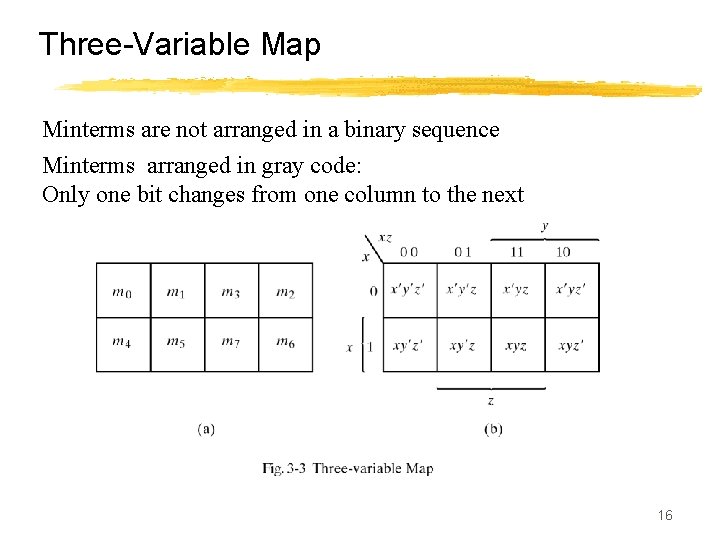

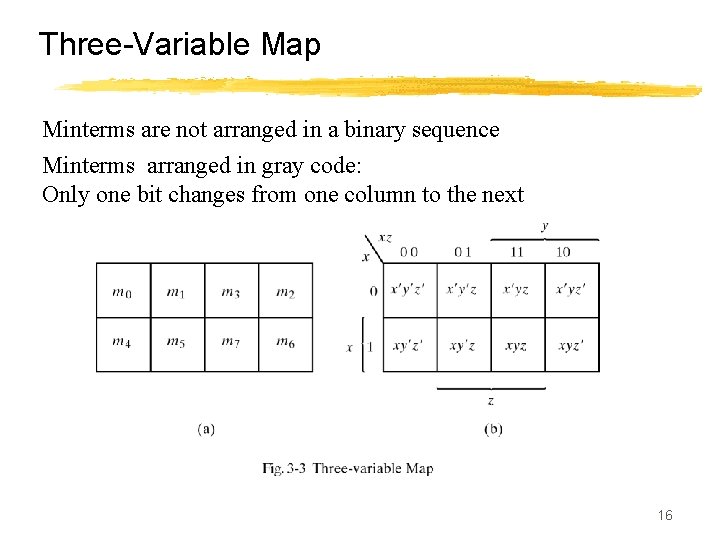

Three-Variable Map Minterms are not arranged in a binary sequence Minterms arranged in gray code: Only one bit changes from one column to the next 16

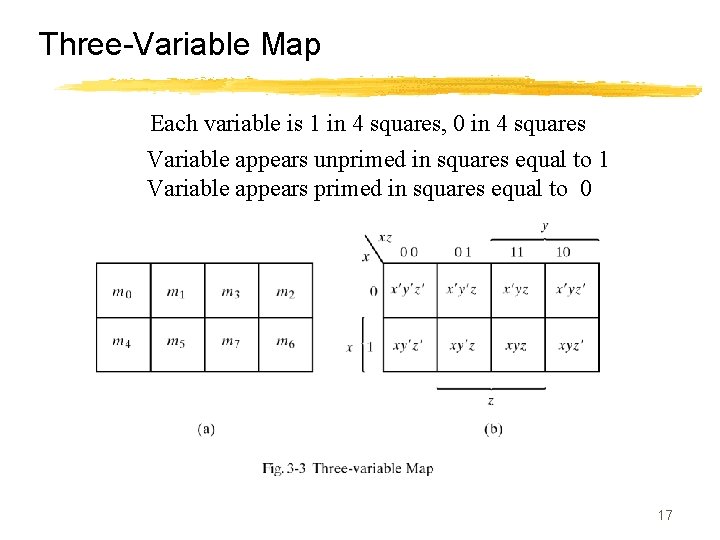

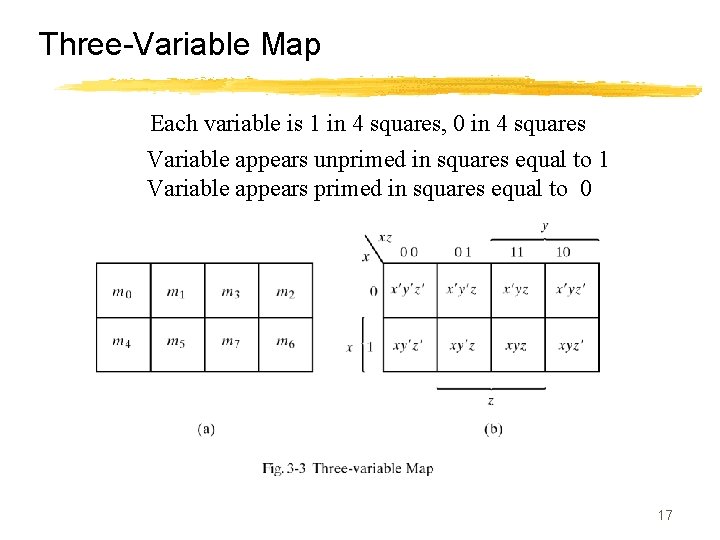

Three-Variable Map Each variable is 1 in 4 squares, 0 in 4 squares Variable appears unprimed in squares equal to 1 Variable appears primed in squares equal to 0 17

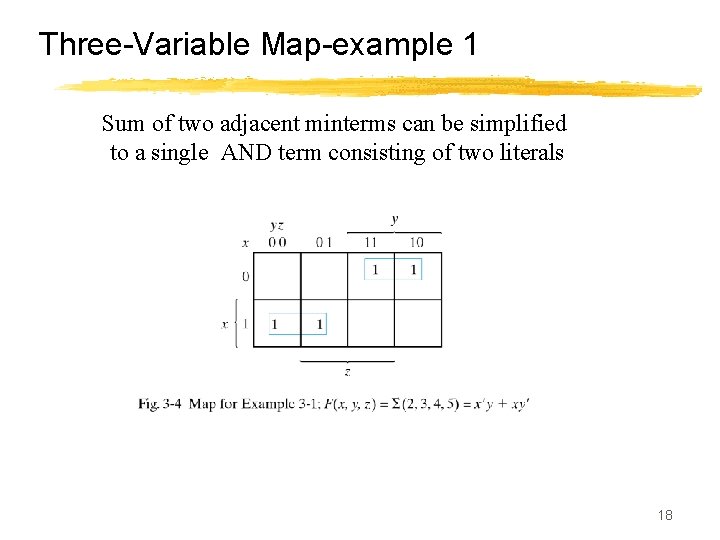

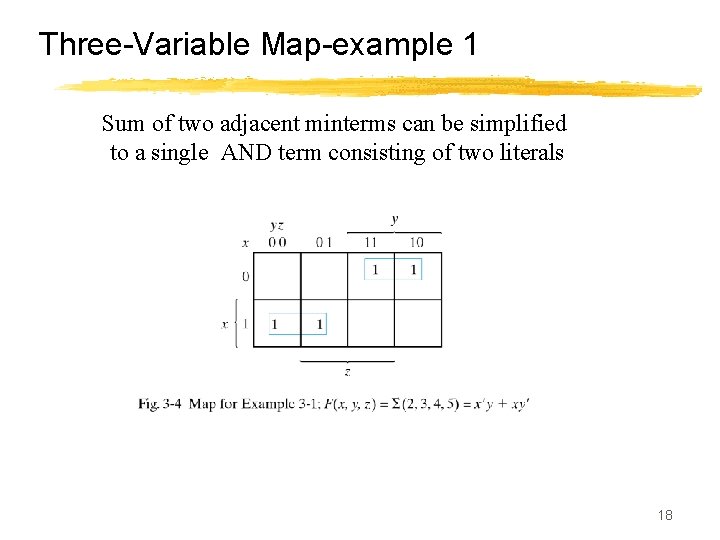

Three-Variable Map-example 1 Sum of two adjacent minterms can be simplified to a single AND term consisting of two literals 18

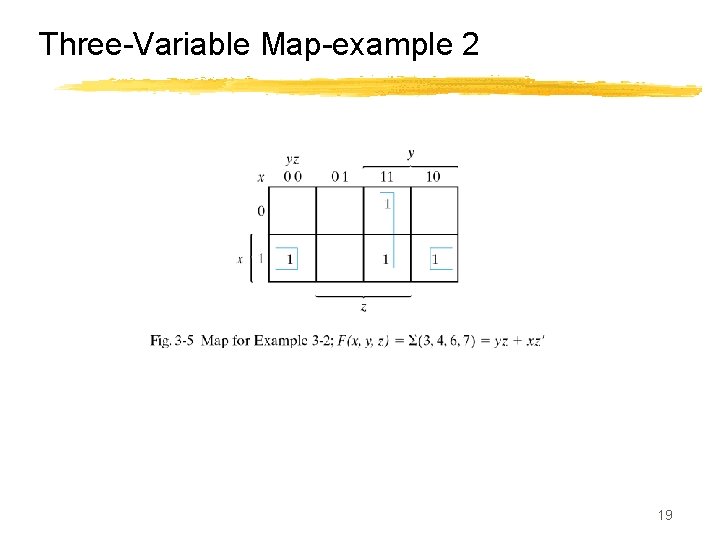

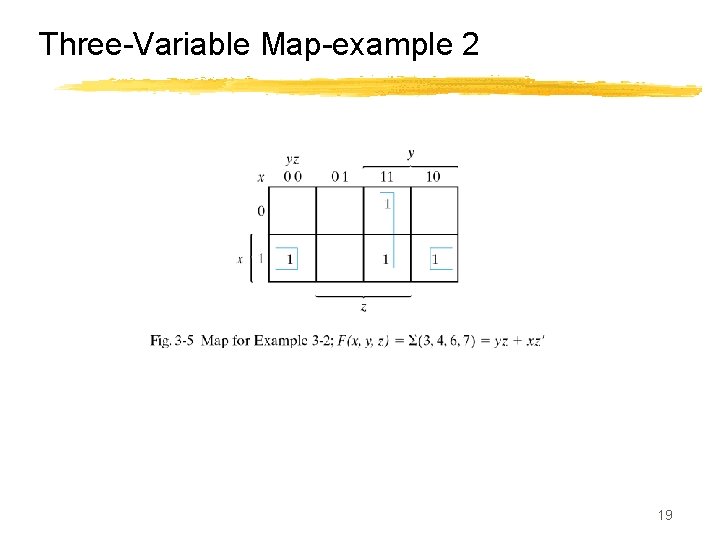

Three-Variable Map-example 2 19

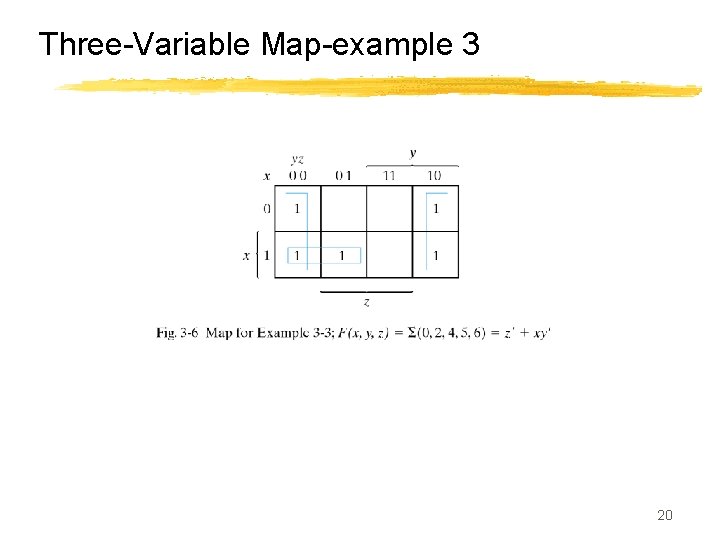

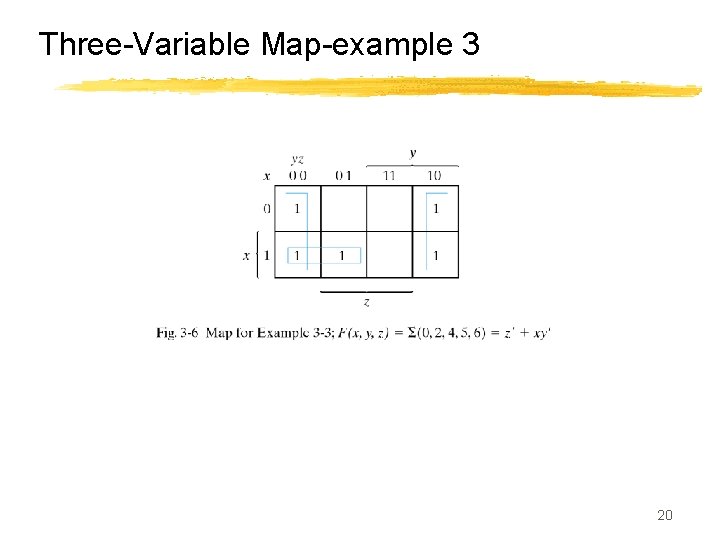

Three-Variable Map-example 3 20

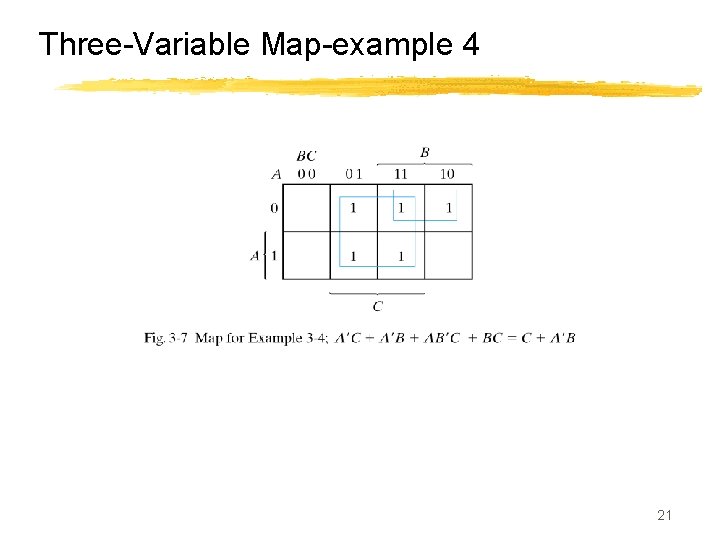

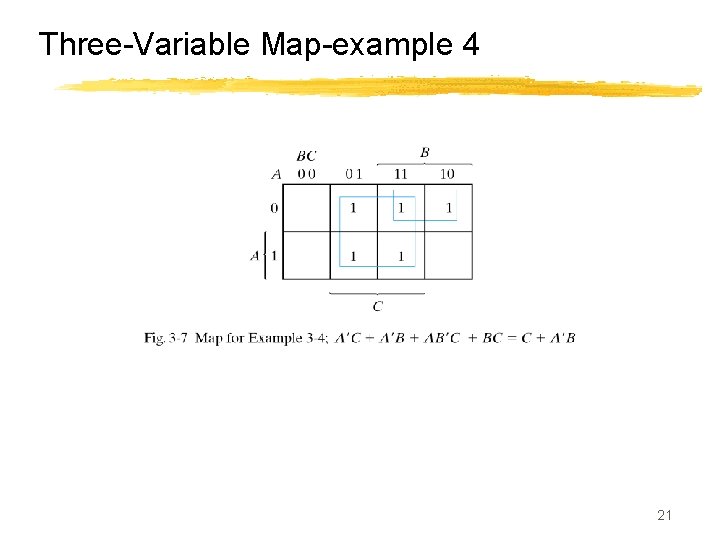

Three-Variable Map-example 4 21

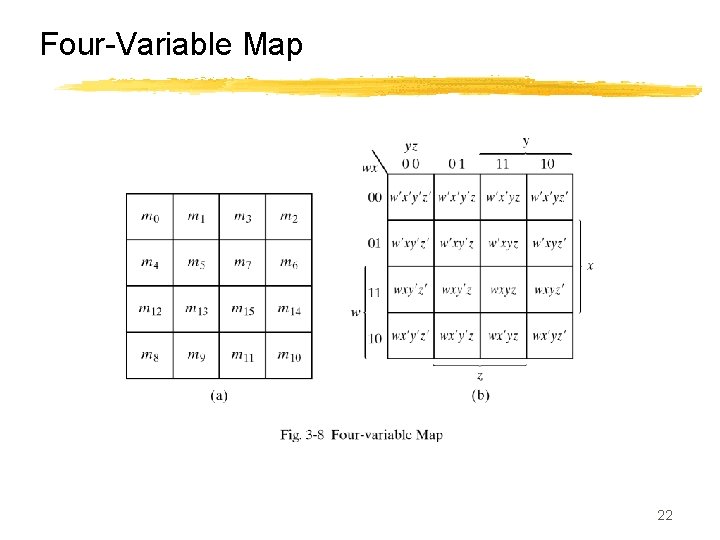

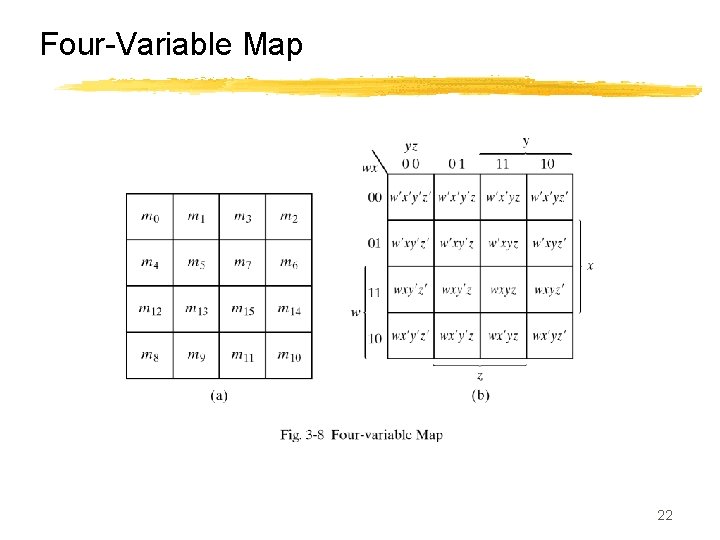

Four-Variable Map 22

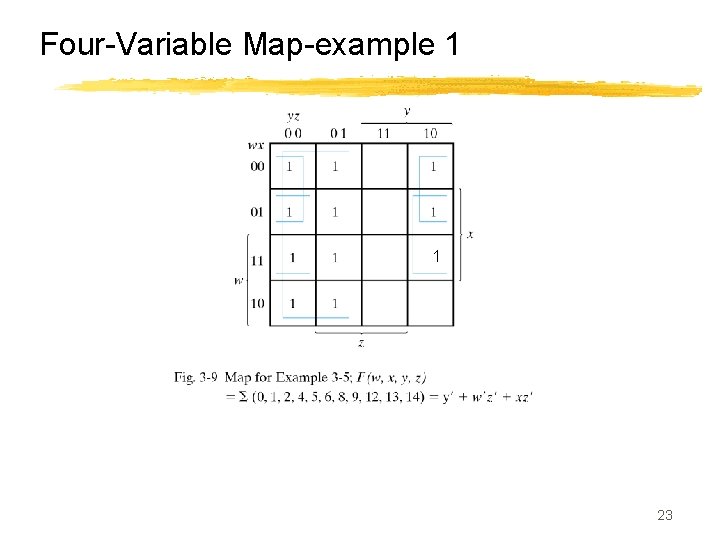

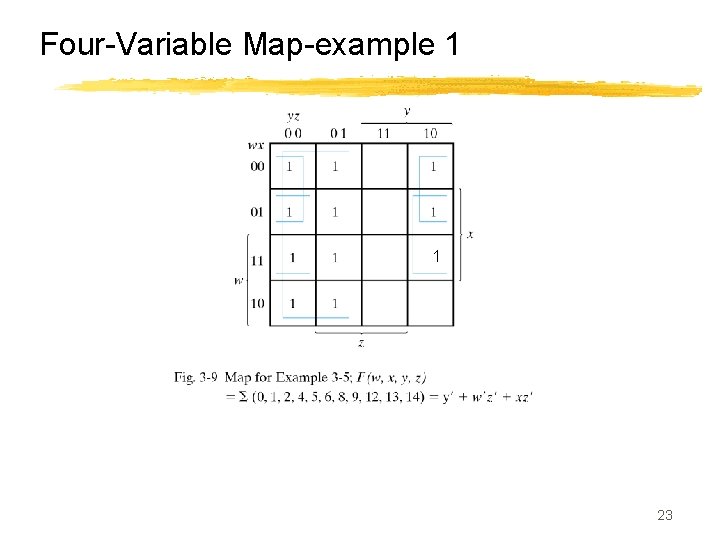

Four-Variable Map-example 1 1 23

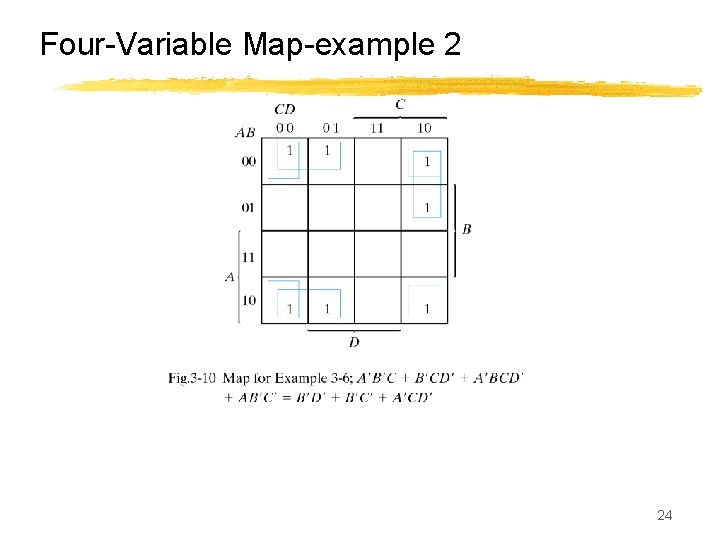

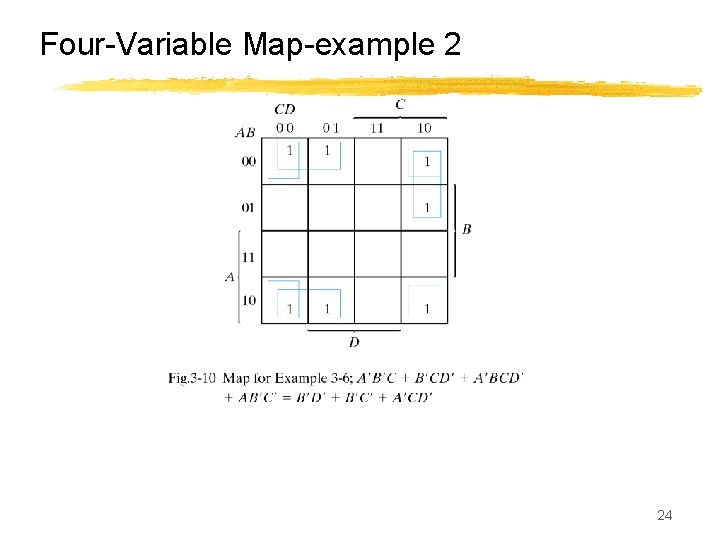

Four-Variable Map-example 2 24

HW #1 z HW #1 - Due Friday, May 23 rd (4: 00 PM) z Solve the following problems from the textbook (5 th edition): 2 -20, 2 -21. 32, 3 -4, 3 -5 and 3 -12. 25

Summary z z Extension to multiple inputs Positive & Negative Logic Integrated Circuits Gate Level Minimization 26