CENG 241 Digital Design 1 Lecture 11 Amirali

- Slides: 33

CENG 241 Digital Design 1 Lecture 11 Amirali Baniasadi amirali@ece. uvic. ca

This Lecture z Chapter 6: Registers and Counters 2

Registers z Sequential circuits are classified based in their function, e. g. , registers. z Register: A group of flip-flops each storing one bit of information. z Registers include flip-flops and gates: flip-flops hold the information, gates control how the information is transferred to the register. z Counter is a register that goes through a predetermined sequence of states. 3

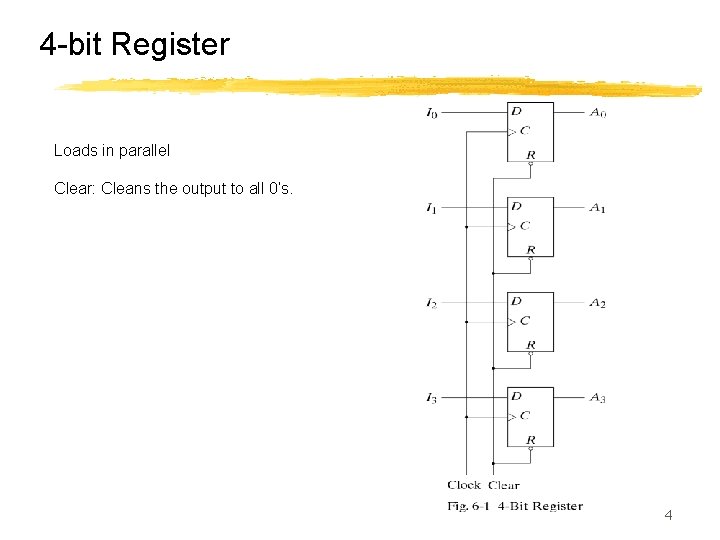

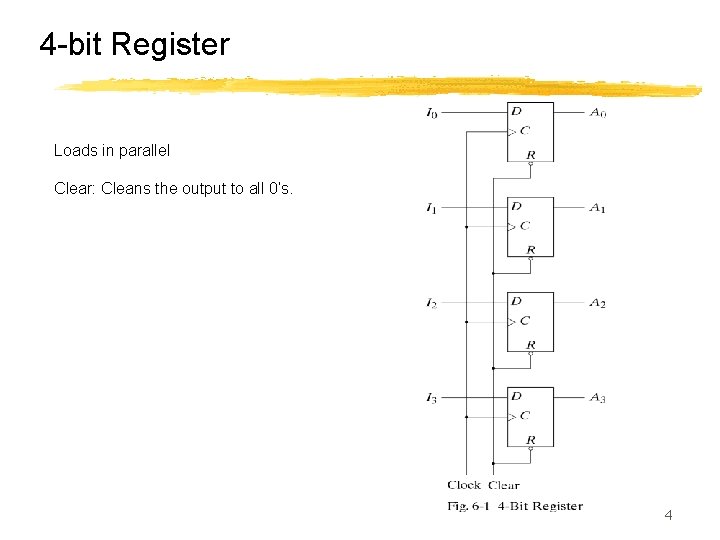

4 -bit Register Loads in parallel Clear: Cleans the output to all 0’s. 4

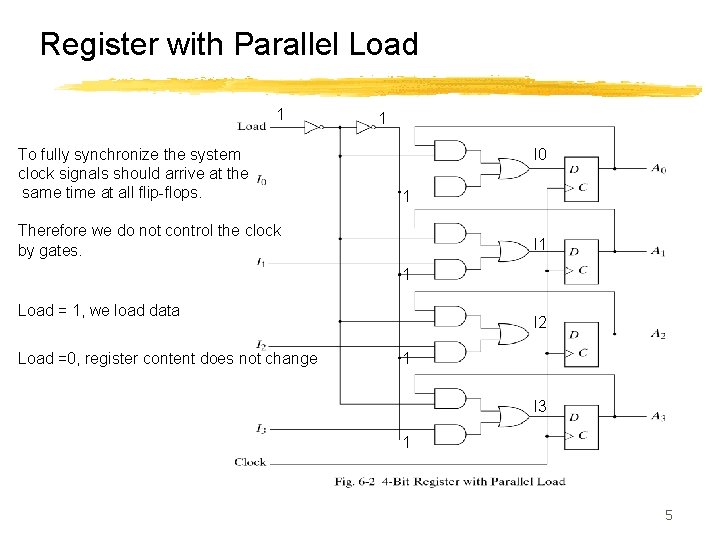

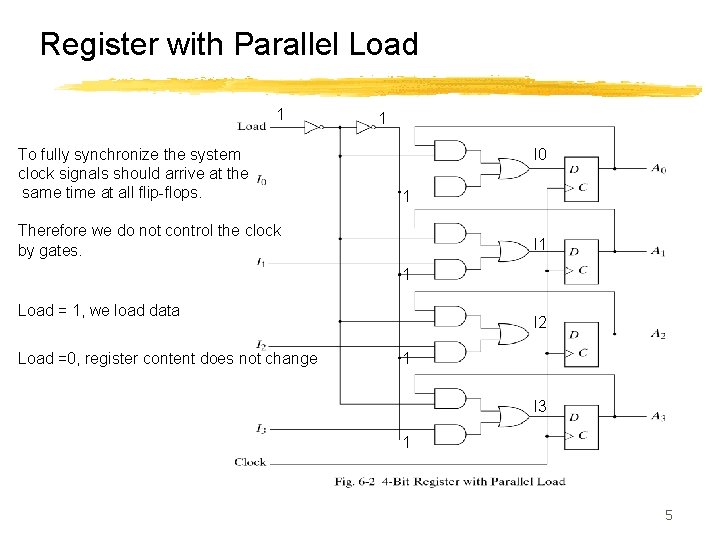

Register with Parallel Load 1 To fully synchronize the system clock signals should arrive at the same time at all flip-flops. 1 I 0 1 Therefore we do not control the clock by gates. I 1 1 Load = 1, we load data Load =0, register content does not change I 2 1 I 3 1 5

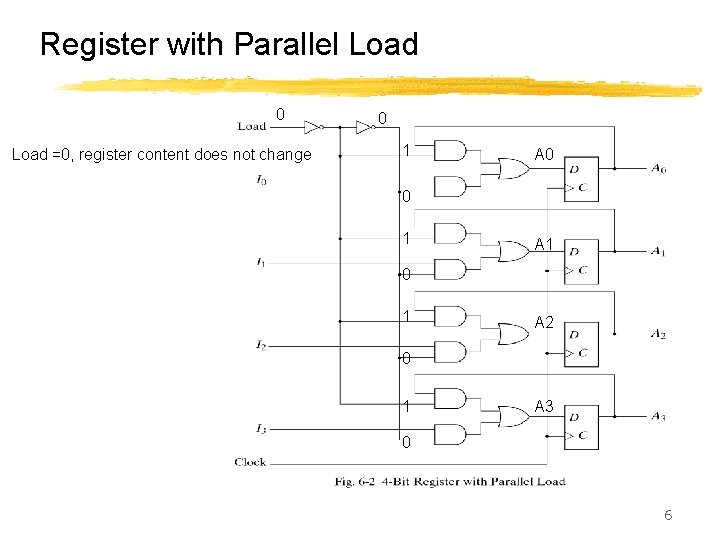

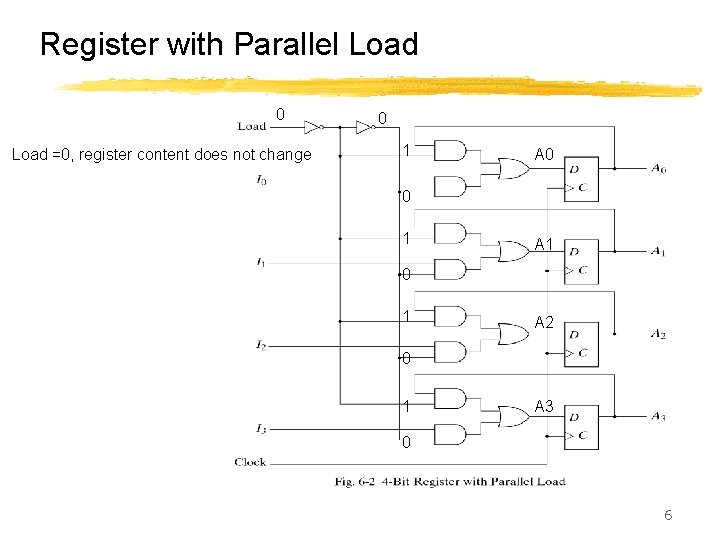

Register with Parallel Load 0 Load =0, register content does not change 0 1 A 0 0 1 A 1 0 1 A 2 0 1 A 3 0 6

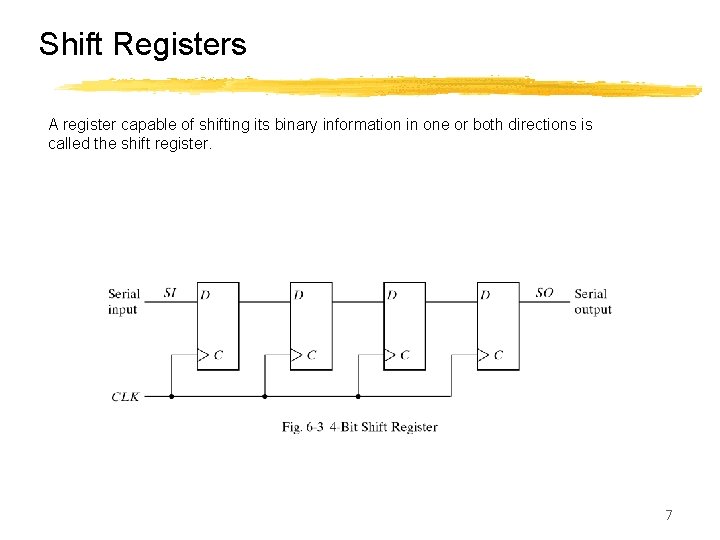

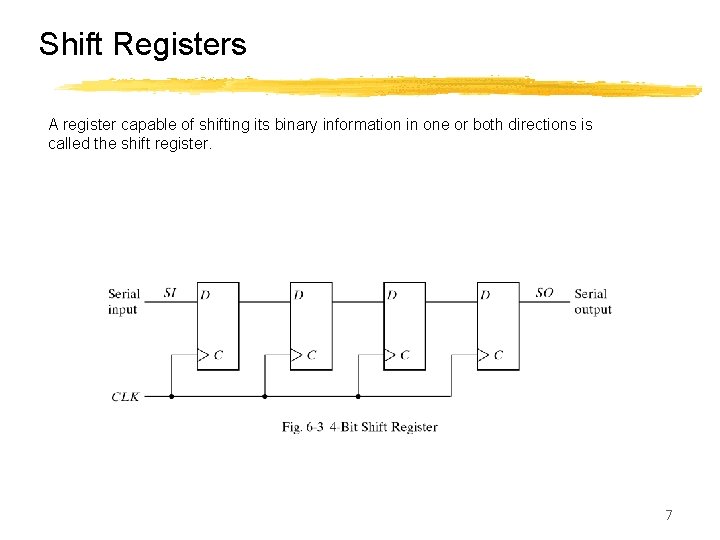

Shift Registers A register capable of shifting its binary information in one or both directions is called the shift register. 7

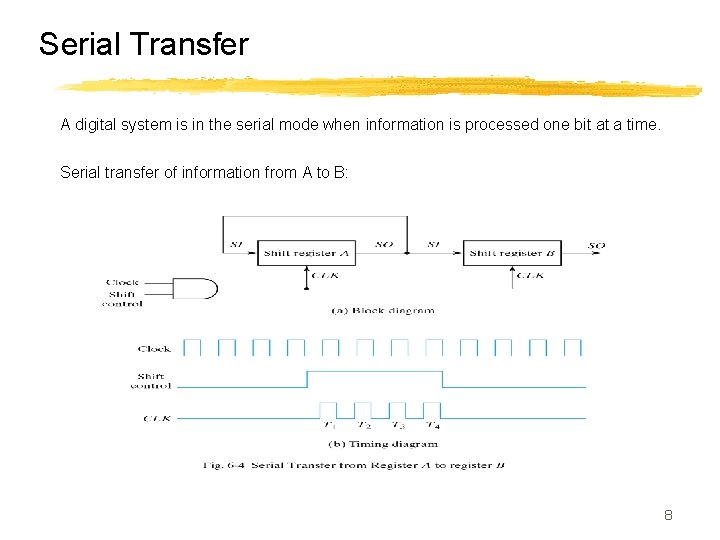

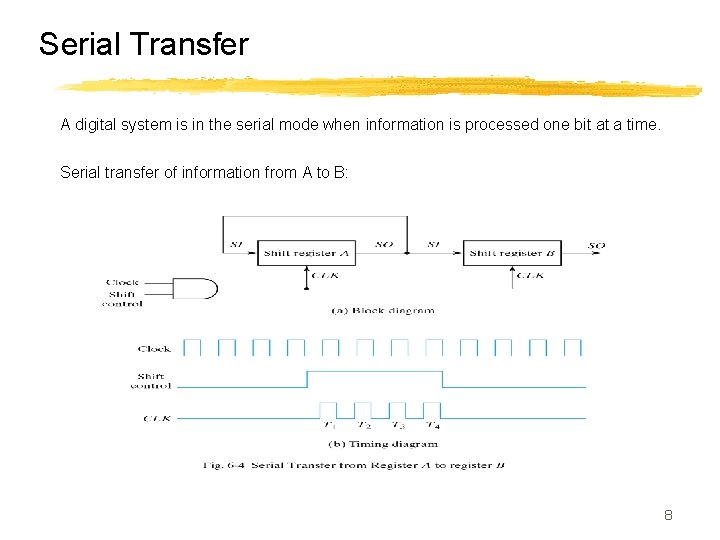

Serial Transfer A digital system is in the serial mode when information is processed one bit at a time. Serial transfer of information from A to B: 8

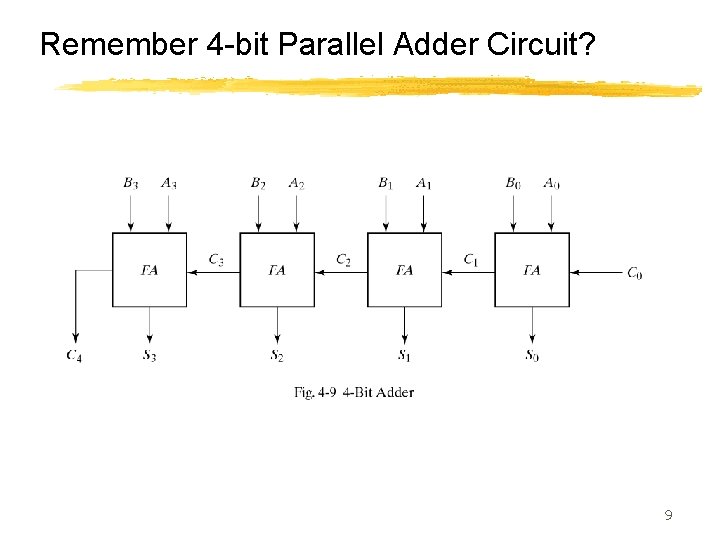

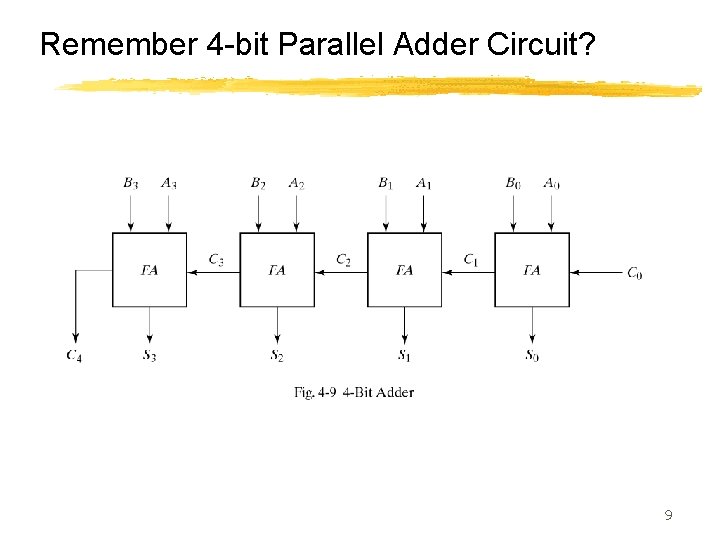

Remember 4 -bit Parallel Adder Circuit? 9

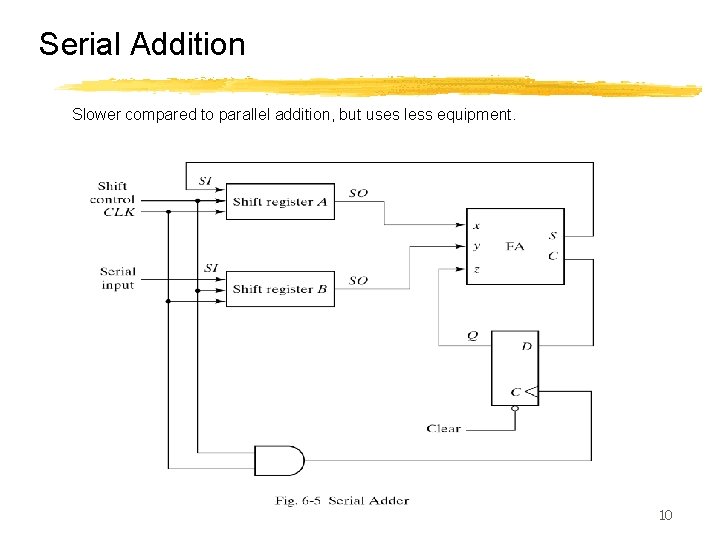

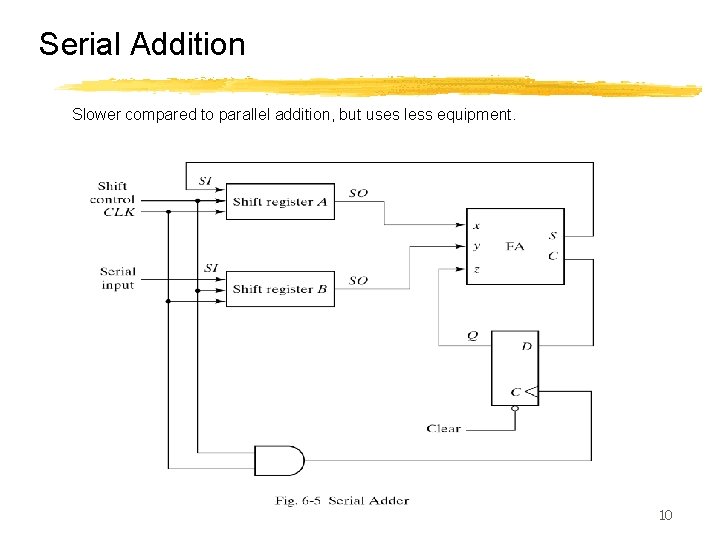

Serial Addition Slower compared to parallel addition, but uses less equipment. 10

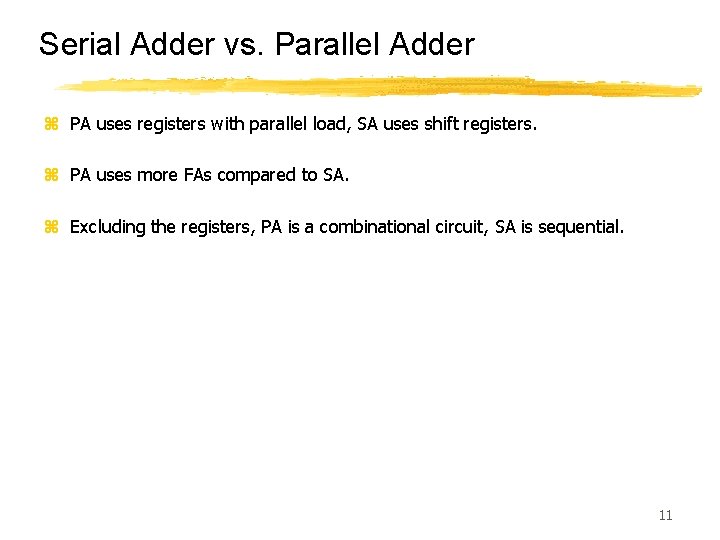

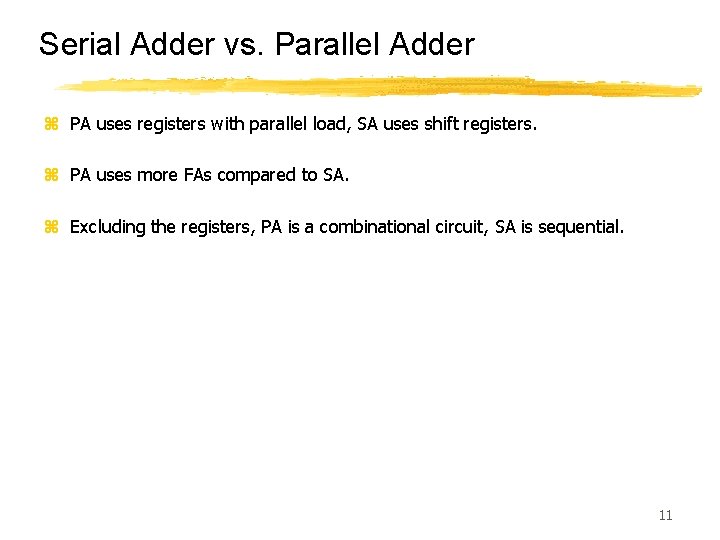

Serial Adder vs. Parallel Adder z PA uses registers with parallel load, SA uses shift registers. z PA uses more FAs compared to SA. z Excluding the registers, PA is a combinational circuit, SA is sequential. 11

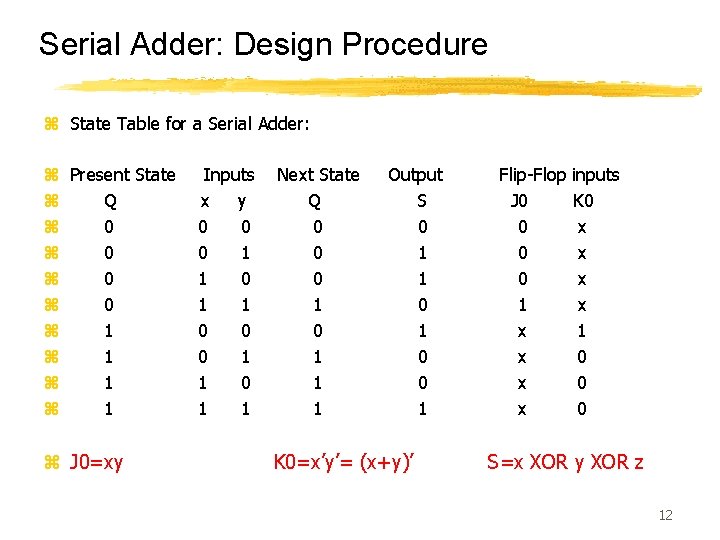

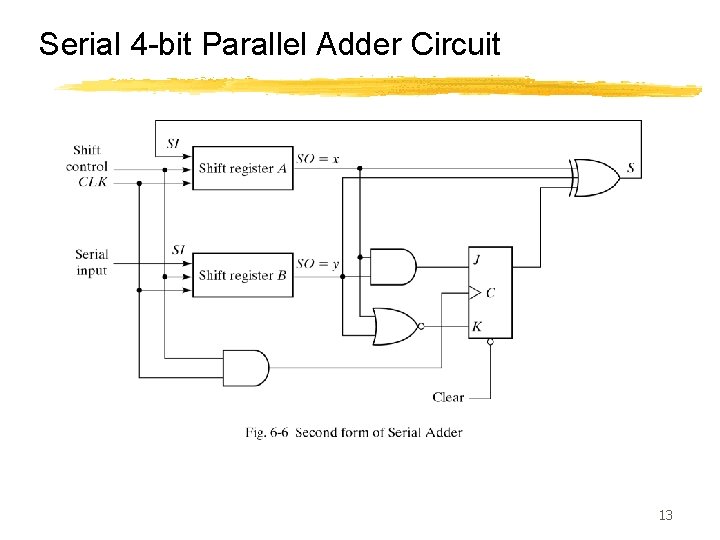

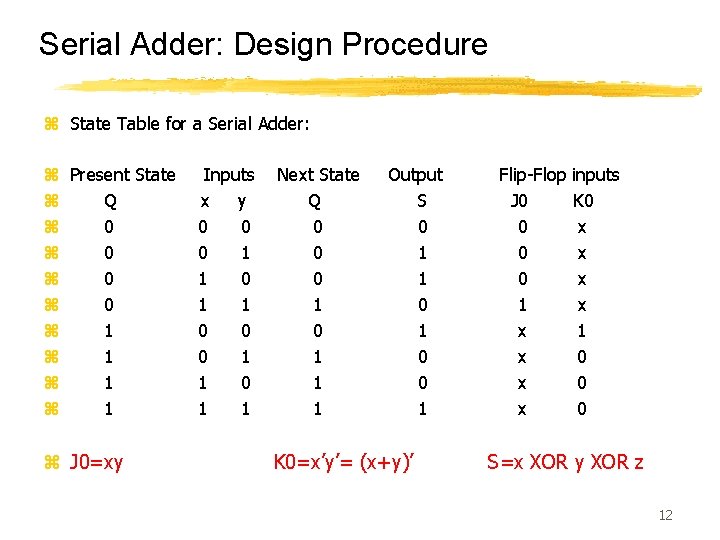

Serial Adder: Design Procedure z State Table for a Serial Adder: z Present State z Q z 0 z 0 z 1 z 1 z J 0=xy Inputs x y 0 0 0 1 1 Next State Q 0 0 0 1 1 1 Output S 0 1 1 0 0 1 K 0=x’y’= (x+y)’ Flip-Flop J 0 0 1 x x inputs K 0 x x 1 0 0 0 S=x XOR y XOR z 12

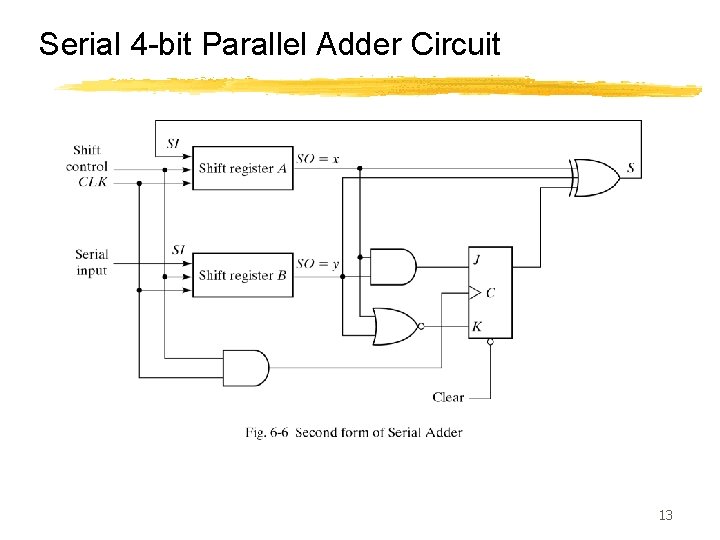

Serial 4 -bit Parallel Adder Circuit 13

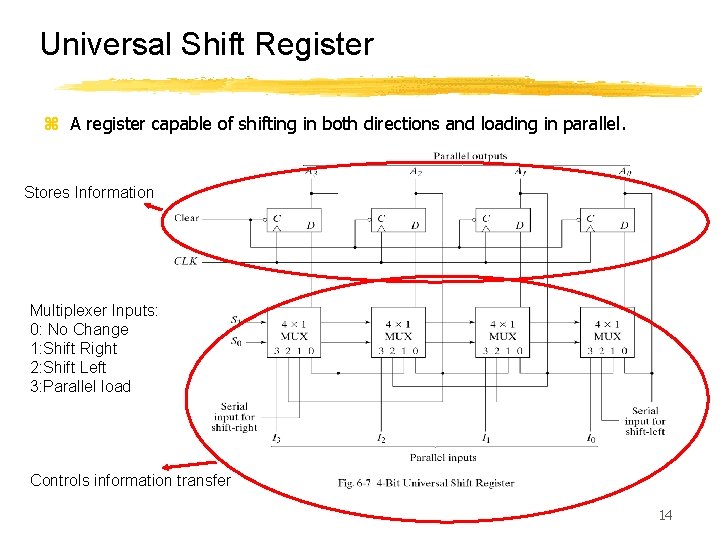

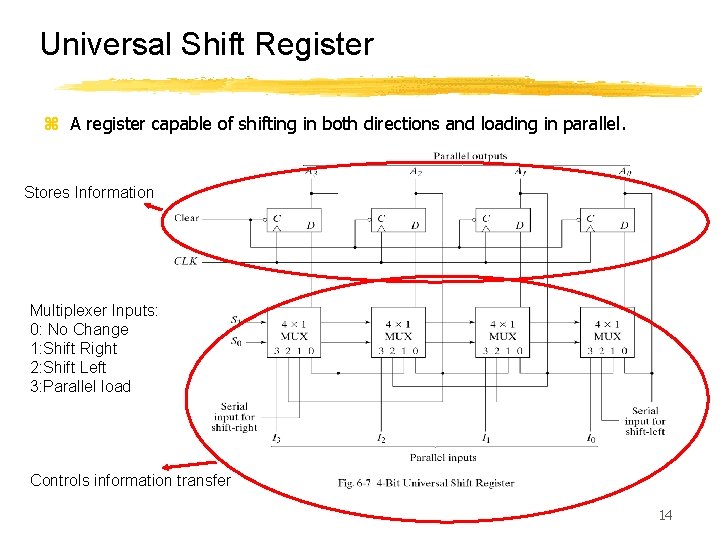

Universal Shift Register z A register capable of shifting in both directions and loading in parallel. Stores Information Multiplexer Inputs: 0: No Change 1: Shift Right 2: Shift Left 3: Parallel load Controls information transfer 14

Ripple Counters z A register that goes trough a prescribed sequence of states is called a counter. z There are two groups of counters: Ripple counters and Synchronous counters. z Ripple counters: The flip-flop output triggers other flip-flops. z Synchronous counters count the clock. 15

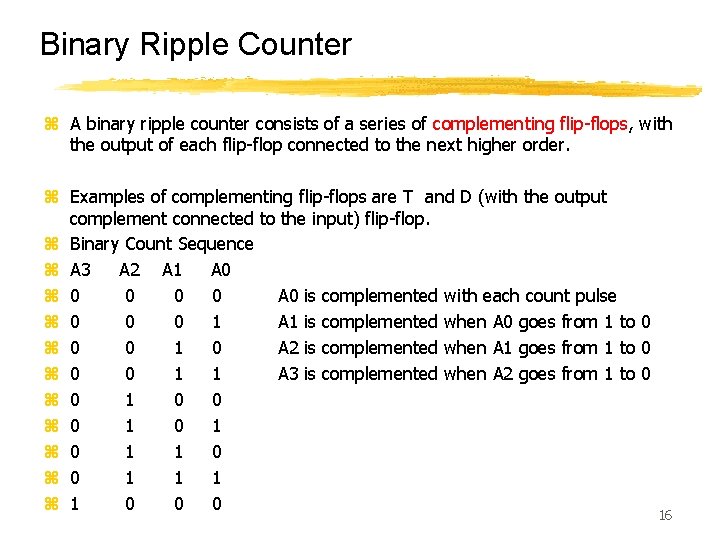

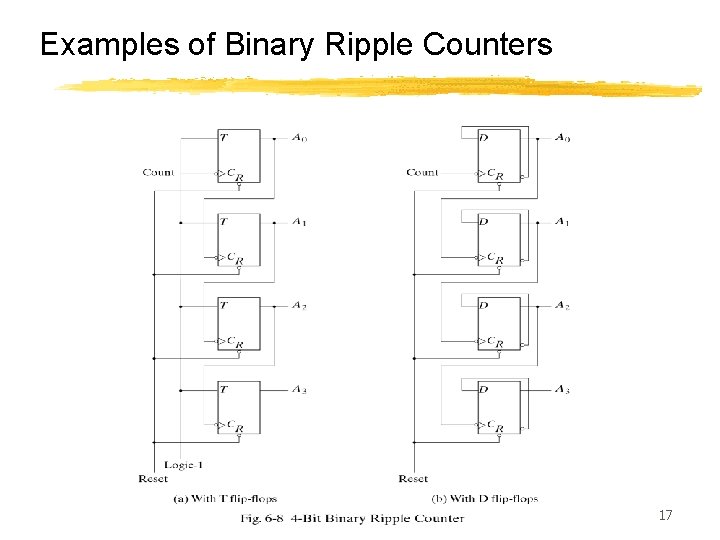

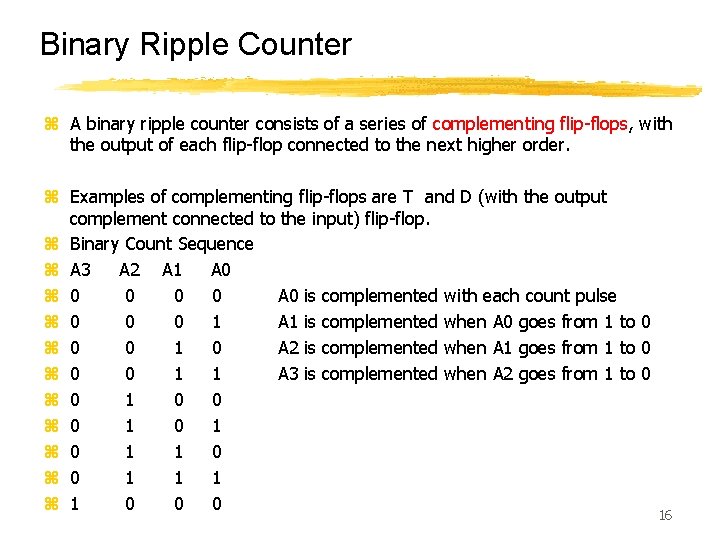

Binary Ripple Counter z A binary ripple counter consists of a series of complementing flip-flops, with the output of each flip-flop connected to the next higher order. z Examples of complementing flip-flops are T and D (with the output complement connected to the input) flip-flop. z Binary Count Sequence z A 3 A 2 A 1 A 0 z 0 0 A 0 is complemented with each count pulse z 0 0 0 1 A 1 is complemented when A 0 goes from 1 to 0 z 0 0 1 0 A 2 is complemented when A 1 goes from 1 to 0 z 0 0 1 1 A 3 is complemented when A 2 goes from 1 to 0 z 0 1 0 1 z 0 1 1 0 z 0 1 1 1 z 1 0 0 0 16

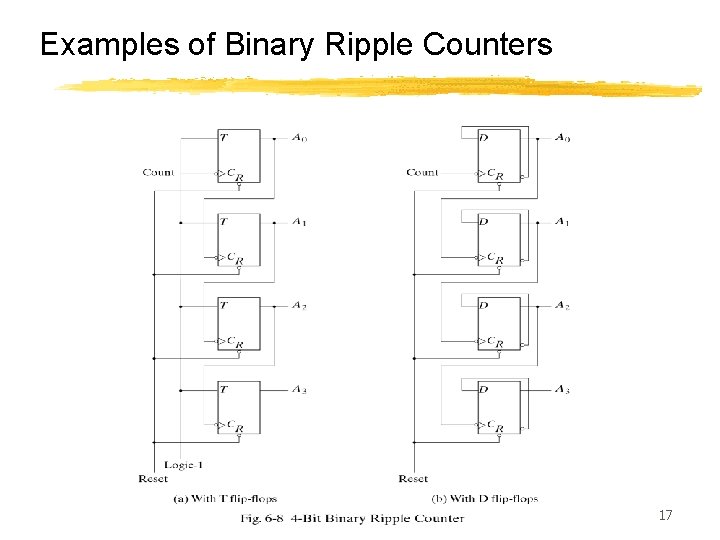

Examples of Binary Ripple Counters 17

Binary Ripple Counter z Count-down counter: A binary counter with reverse count: Starts from 15 goes down. z In a count-down counter the least significant bit is complemented with every count pulse. Any other bit is complemented if the previous bit goes from 0 to 1. z We can use the same counter design with negative edge flip-flops to make a count-down flip-flop. 18

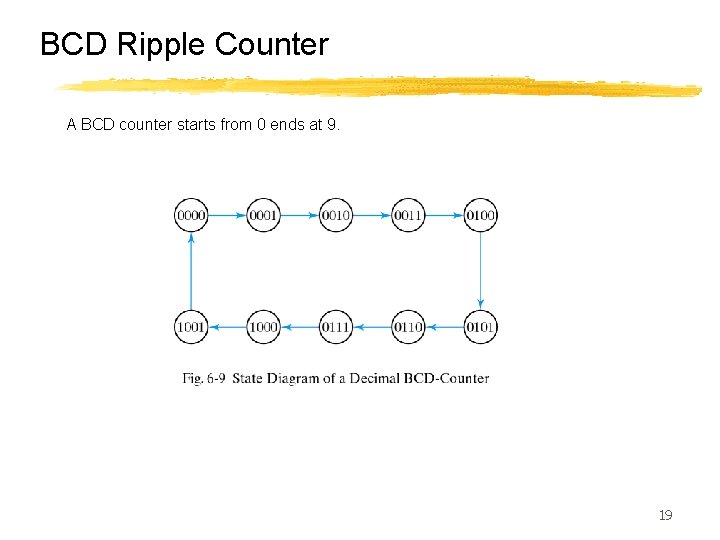

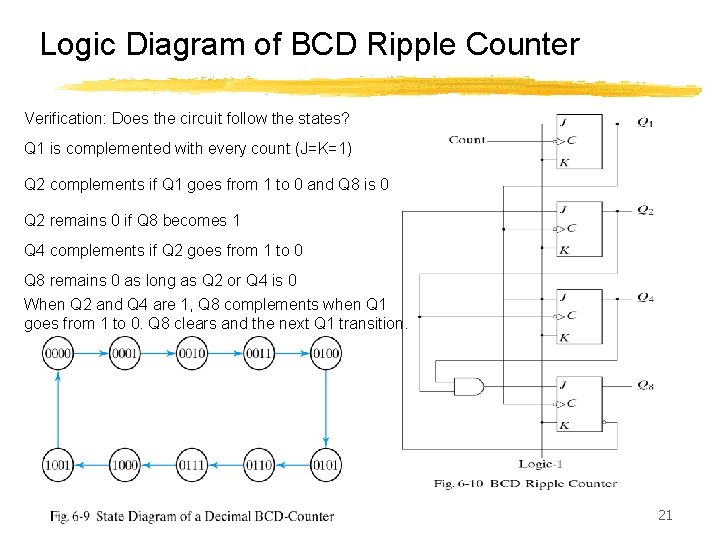

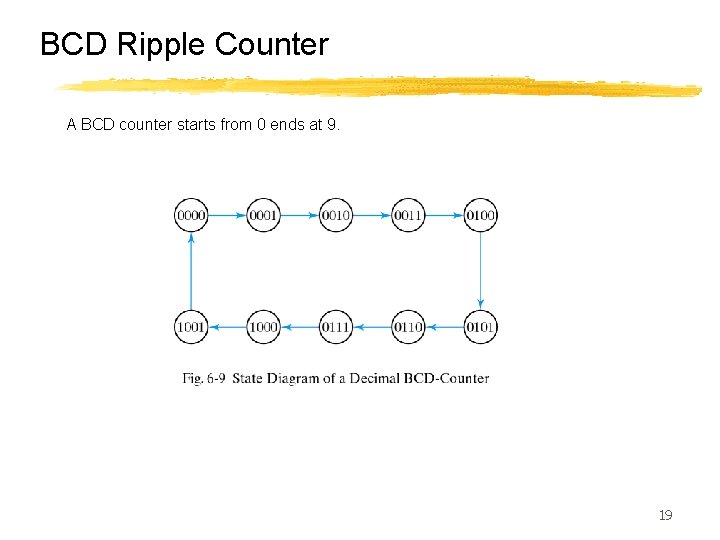

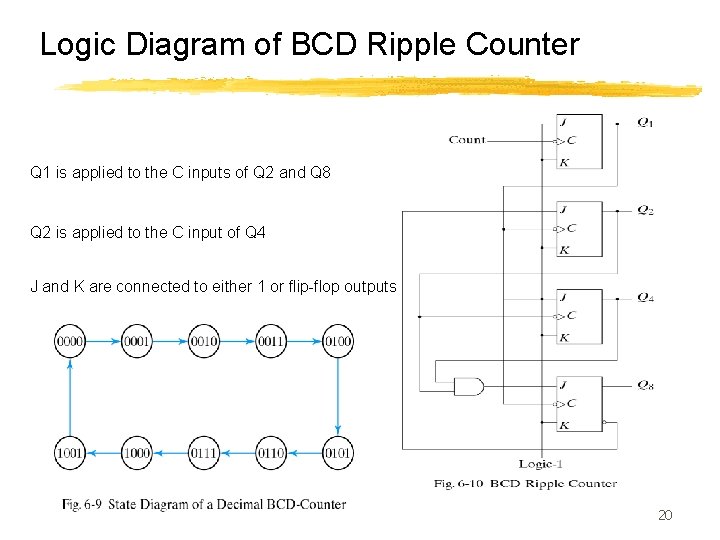

BCD Ripple Counter A BCD counter starts from 0 ends at 9. 19

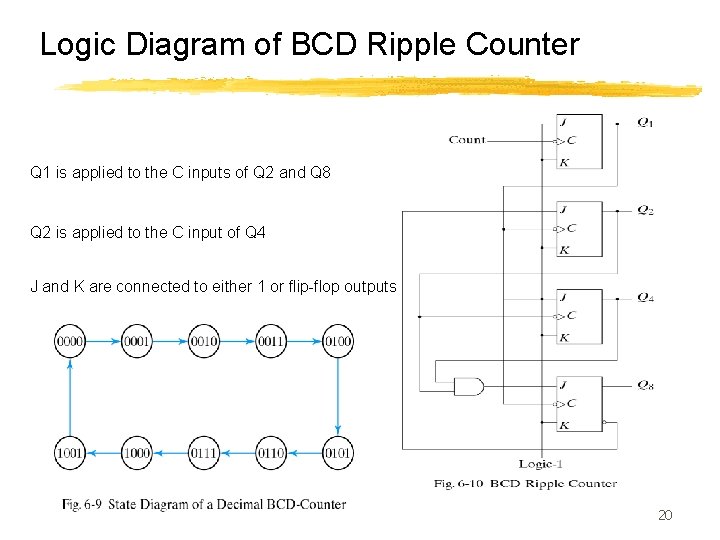

Logic Diagram of BCD Ripple Counter Q 1 is applied to the C inputs of Q 2 and Q 8 Q 2 is applied to the C input of Q 4 J and K are connected to either 1 or flip-flop outputs 20

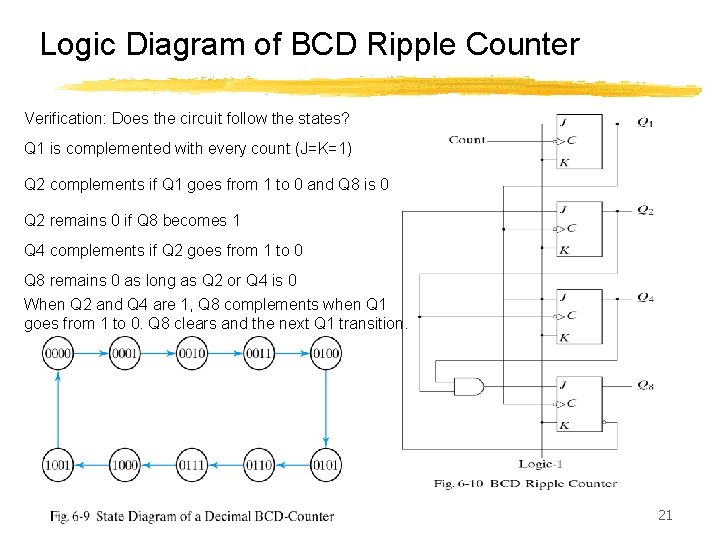

Logic Diagram of BCD Ripple Counter Verification: Does the circuit follow the states? Q 1 is complemented with every count (J=K=1) Q 2 complements if Q 1 goes from 1 to 0 and Q 8 is 0 Q 2 remains 0 if Q 8 becomes 1 Q 4 complements if Q 2 goes from 1 to 0 Q 8 remains 0 as long as Q 2 or Q 4 is 0 When Q 2 and Q 4 are 1, Q 8 complements when Q 1 goes from 1 to 0. Q 8 clears and the next Q 1 transition. 21

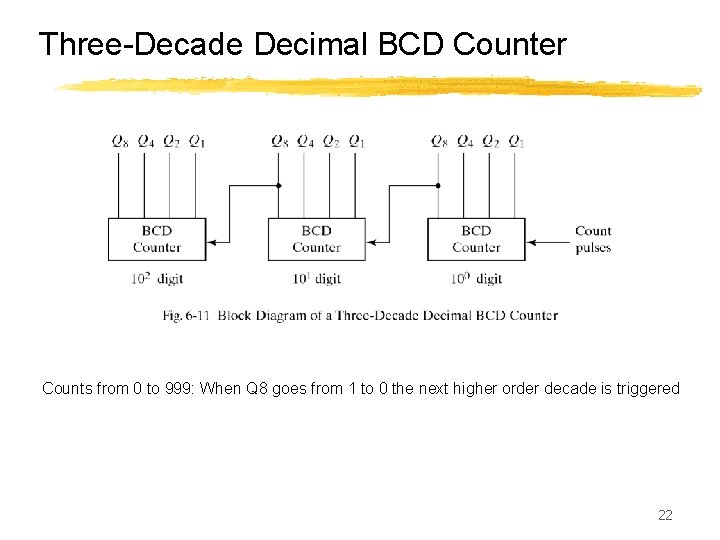

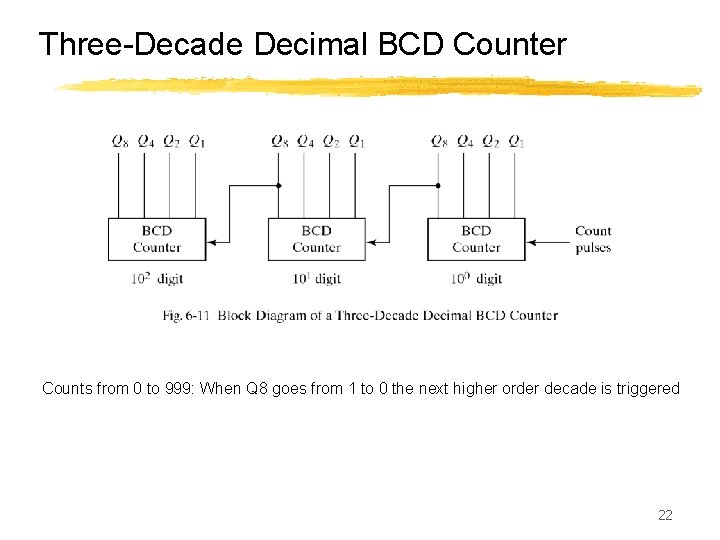

Three-Decade Decimal BCD Counter Counts from 0 to 999: When Q 8 goes from 1 to 0 the next higher order decade is triggered 22

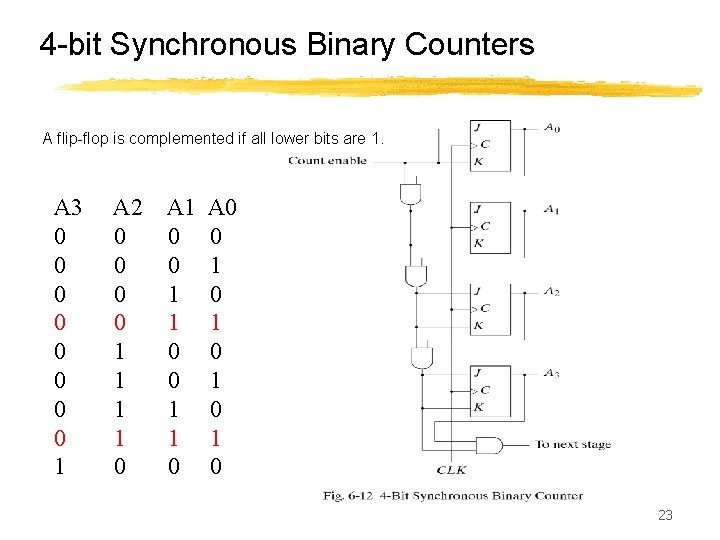

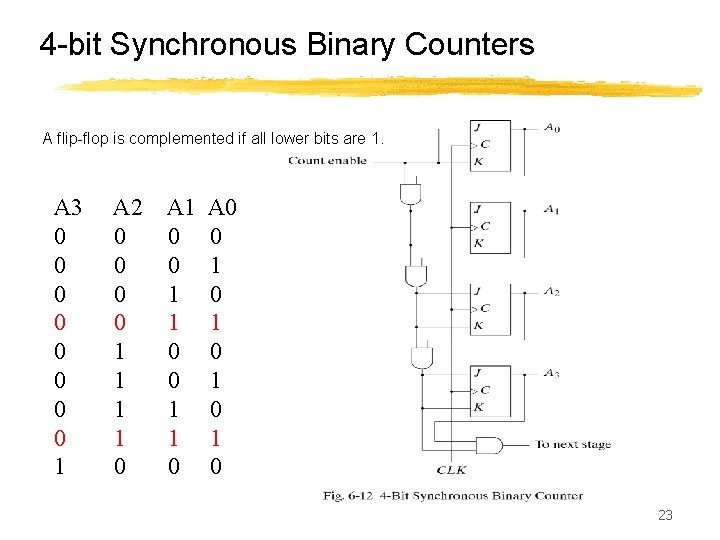

4 -bit Synchronous Binary Counters A flip-flop is complemented if all lower bits are 1. A 3 0 0 0 0 1 A 2 0 0 1 1 0 A 1 0 0 1 1 0 A 0 0 1 0 1 0 23

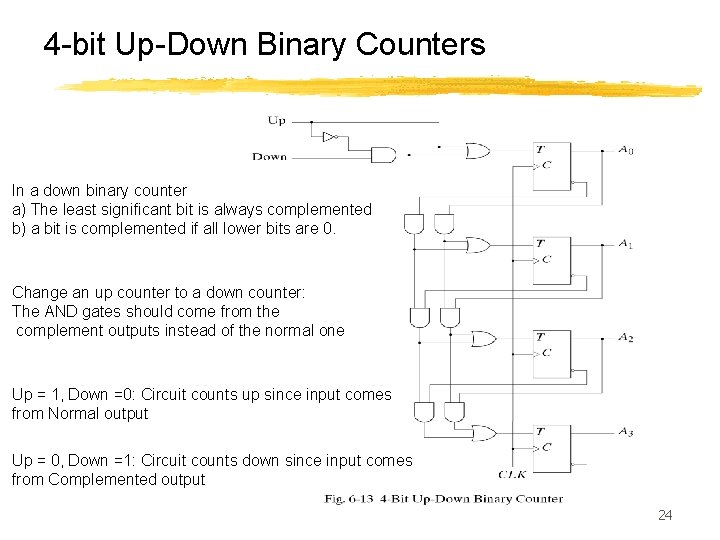

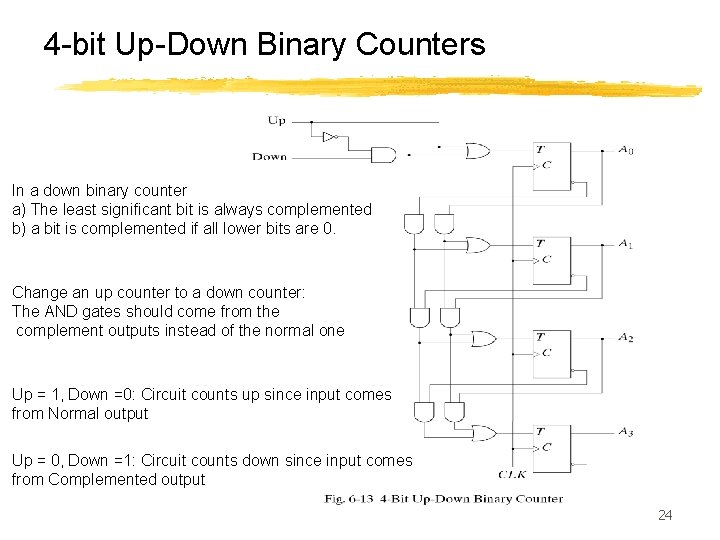

4 -bit Up-Down Binary Counters In a down binary counter a) The least significant bit is always complemented b) a bit is complemented if all lower bits are 0. Change an up counter to a down counter: The AND gates should come from the complement outputs instead of the normal one Up = 1, Down =0: Circuit counts up since input comes from Normal output Up = 0, Down =1: Circuit counts down since input comes from Complemented output 24

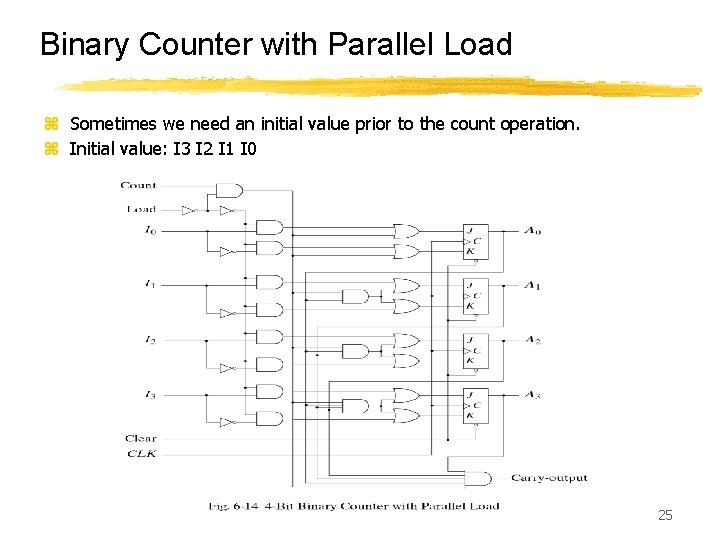

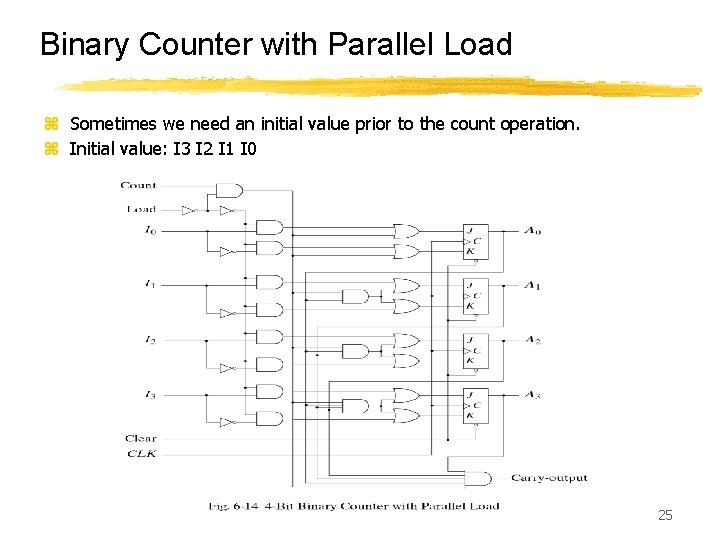

Binary Counter with Parallel Load z Sometimes we need an initial value prior to the count operation. z Initial value: I 3 I 2 I 1 I 0 25

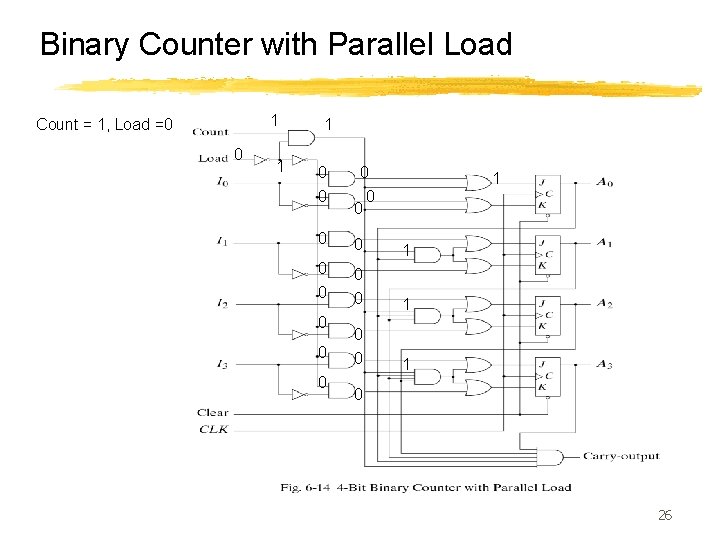

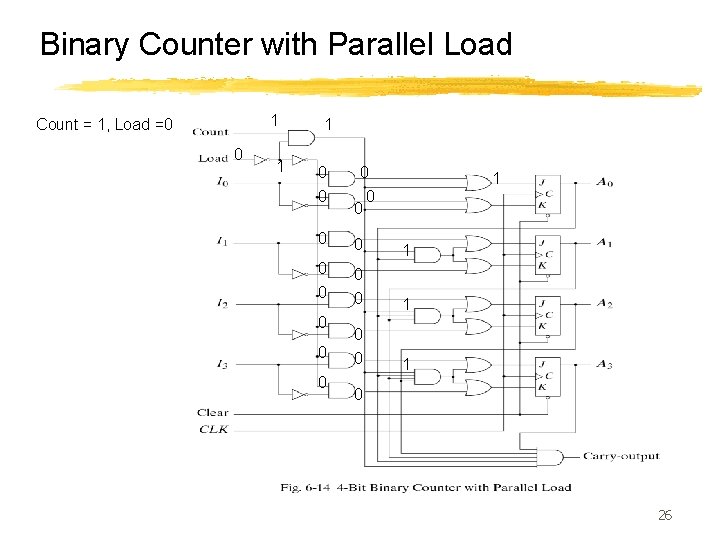

Binary Counter with Parallel Load 1 Count = 1, Load =0 0 1 1 0 0 0 0 1 0 0 0 1 0 26

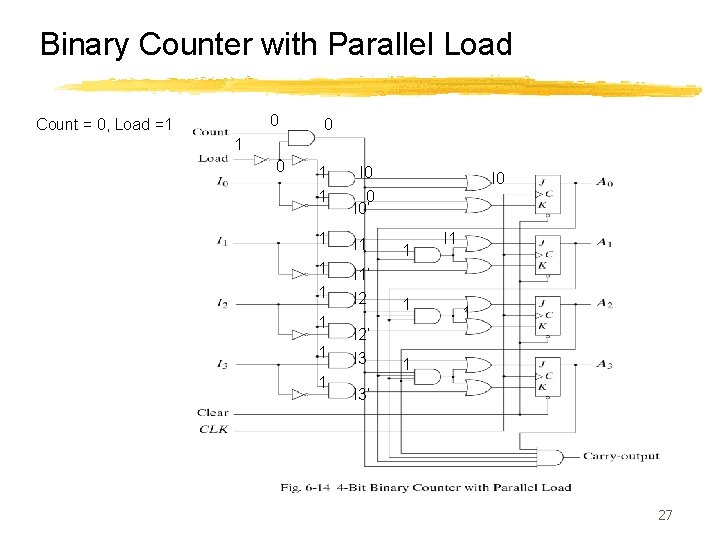

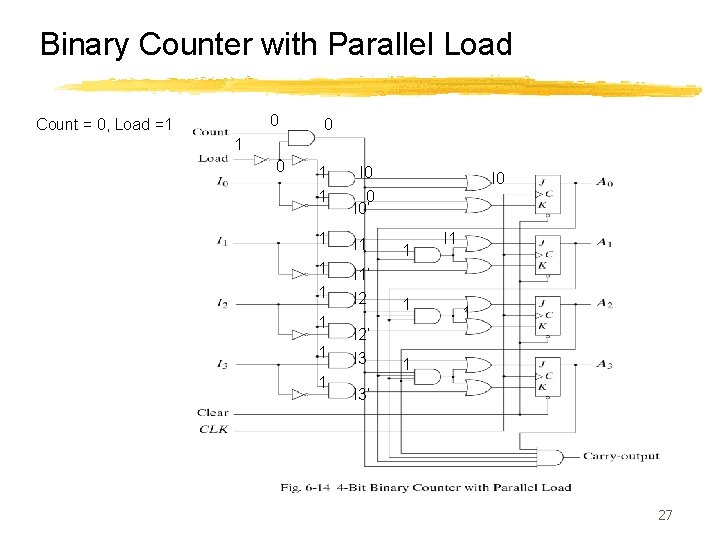

Binary Counter with Parallel Load 0 Count = 0, Load =1 0 1 1 I 0 0 I 0’ 1 I 1’ I 2 1 I 2’ I 3 1 1 I 0 I 1 1 I 3’ 27

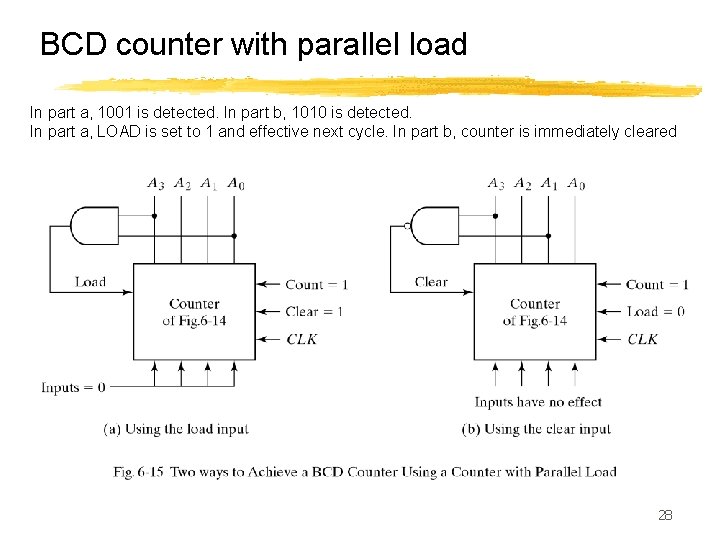

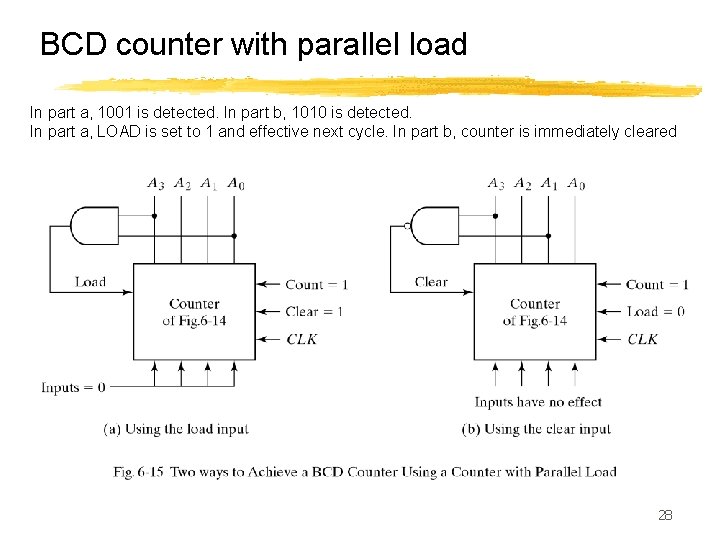

BCD counter with parallel load In part a, 1001 is detected. In part b, 1010 is detected. In part a, LOAD is set to 1 and effective next cycle. In part b, counter is immediately cleared 28

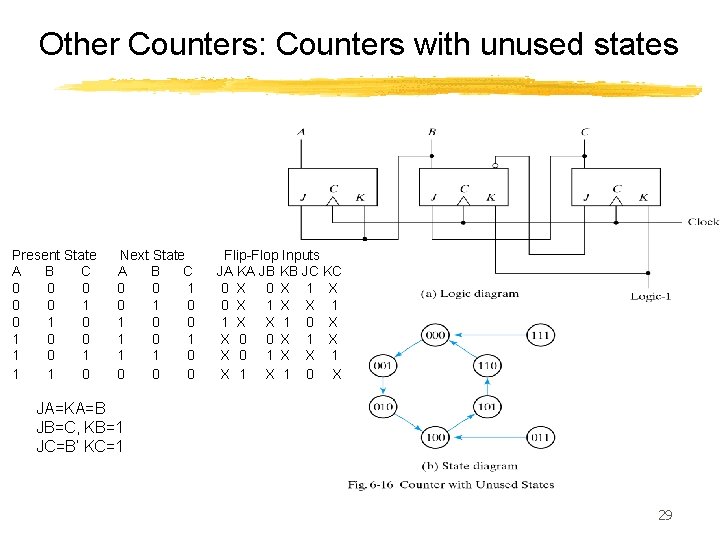

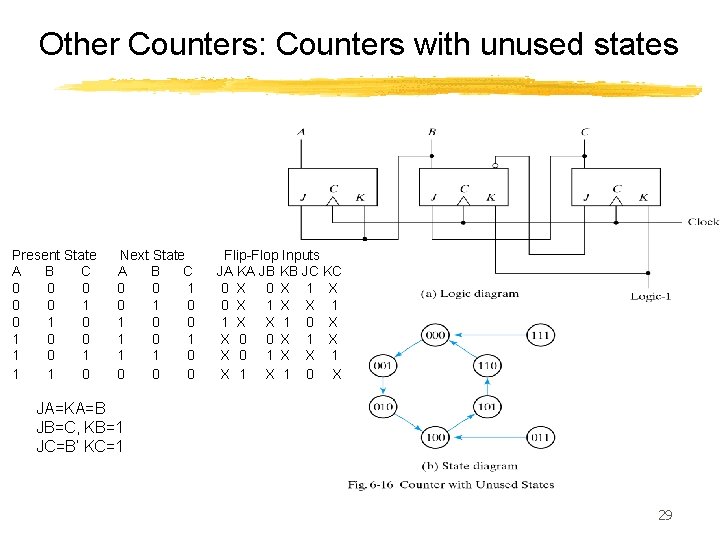

Other Counters: Counters with unused states Present State A B C 0 0 0 1 0 1 0 1 1 1 0 Next State A B C 0 0 1 0 1 0 1 1 1 0 0 Flip-Flop Inputs JA KA JB KB JC KC 0 X 1 X X 1 0 X X 0 0 X 1 X X 0 1 X X 1 X 1 0 X JA=KA=B JB=C, KB=1 JC=B’ KC=1 29

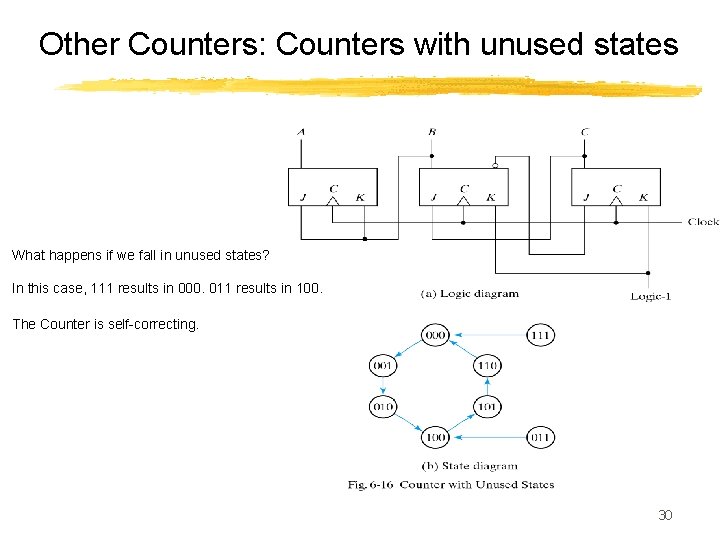

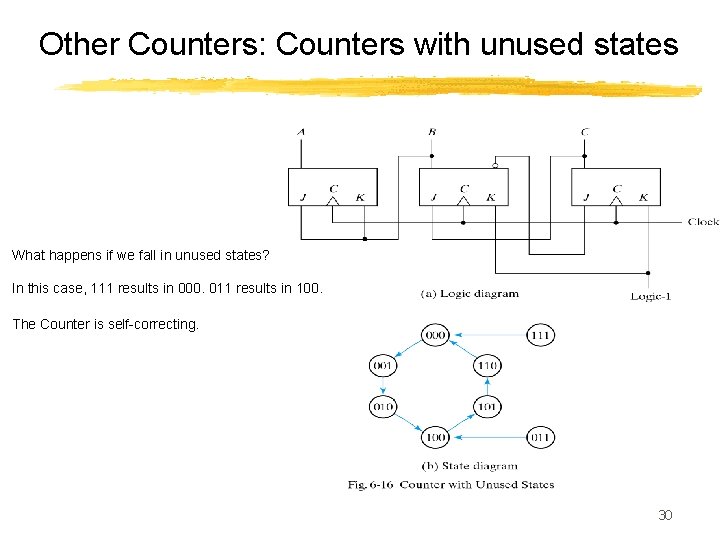

Other Counters: Counters with unused states What happens if we fall in unused states? In this case, 111 results in 000. 011 results in 100. The Counter is self-correcting. 30

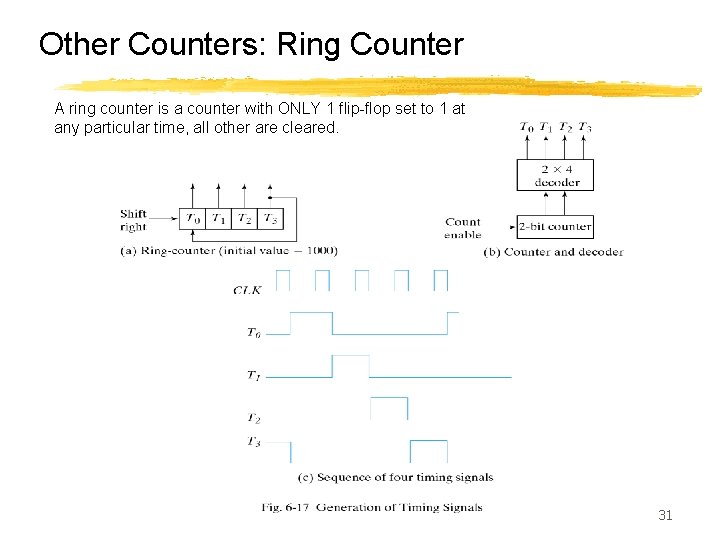

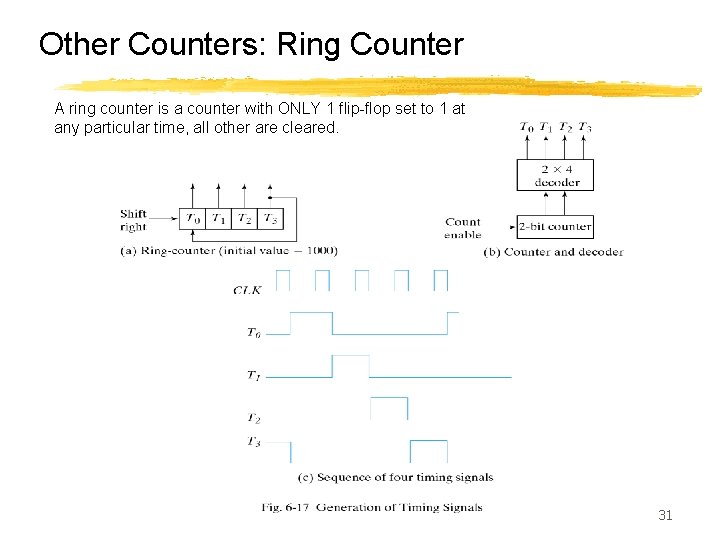

Other Counters: Ring Counter A ring counter is a counter with ONLY 1 flip-flop set to 1 at any particular time, all other are cleared. 31

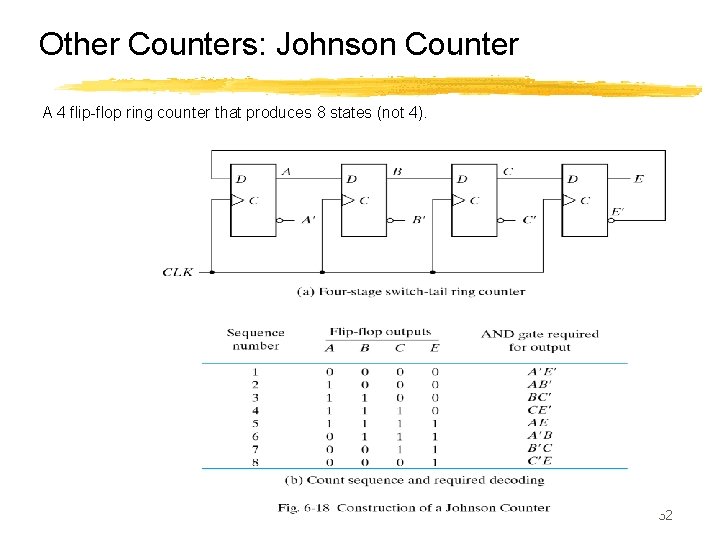

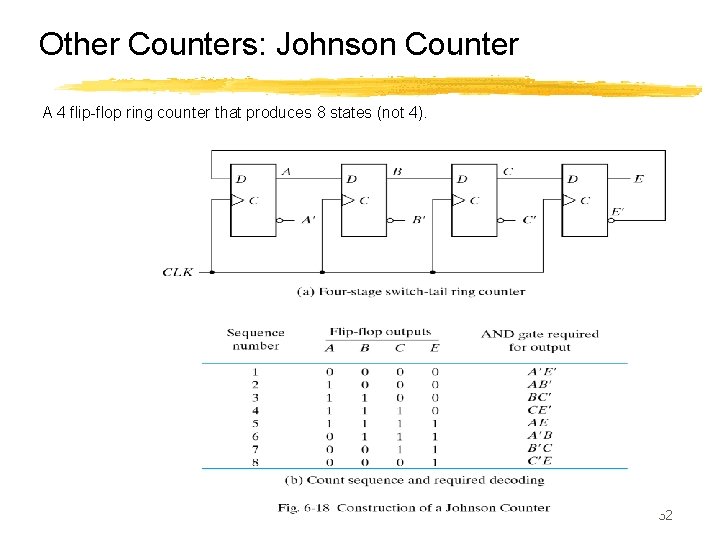

Other Counters: Johnson Counter A 4 flip-flop ring counter that produces 8 states (not 4). 32

Summary z Counters & Registers z Reading up to page 269 z Homework 5 -Chapter 6 problems 6, 7, 11, 15, 18, 19, 23, 29 and 30 Due Wednesday July 30 th. 33