Asynchronous CPUs Peter Ding History of Asynchronous CPUs

![References • [1] Barton, R. S. (1961). A new approach to the functional design References • [1] Barton, R. S. (1961). A new approach to the functional design](https://slidetodoc.com/presentation_image_h2/a107b9095e7c062983c56b9d3e98108e/image-12.jpg)

- Slides: 12

Asynchronous CPUs Peter Ding

History of Asynchronous CPUs • In 1952, the University of Illinois built the Ordnance Discrete Variable Automatic Computer • ORDVAC • In 1962, the University of Illinois built the Illinois Automatic Computer ILLIAC II • Speed-Independent Circuity • Mersenne Prime Numbers •

Caltech Asynchronous Microprocessor • World’s first asynchronous microprocessor in 1988 • Hot coffee caused the pulse rate to slow down • Liquid nitrogen caused the pulse rate to speed up • Ran on a potato

Asynchronous CPUs • No central clock • “Pipeline controls” or “FIFO sequencers” • Starts the next stage of logic after the existing stage is completed • Speed only limited by propagation delays of logic gates • Components can run at different speeds • Clocked CPU components are synchronized with the central clock

Asynchronous CPUs • Lower power consumption • Clock can consume 40 -70% of the power budget • Consumes next to zero energy when idle • Lower electromagnetic interference Clocked CPUs will have large regular spikes of radio frequency energy during peak current demands • Different components at different speeds yield irregular spikes with small amplitudes and wider peaks •

Asynchronous CPUs • Not bottlenecked by a clock • Avoids clock skew

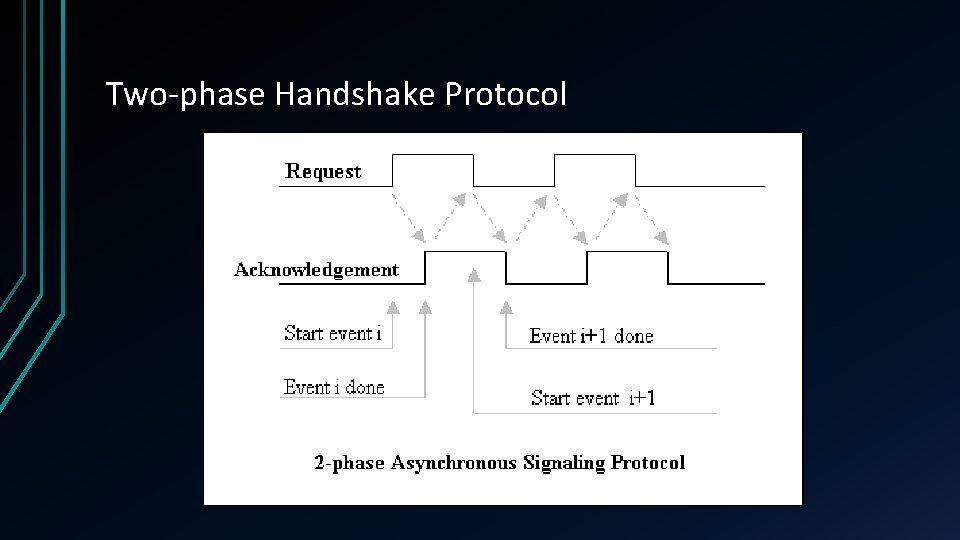

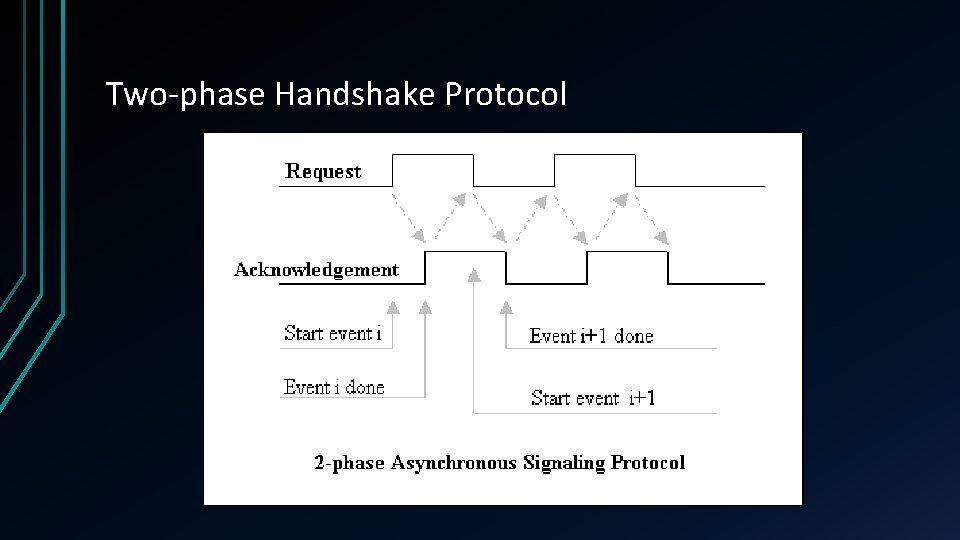

Two-phase Handshake Protocol

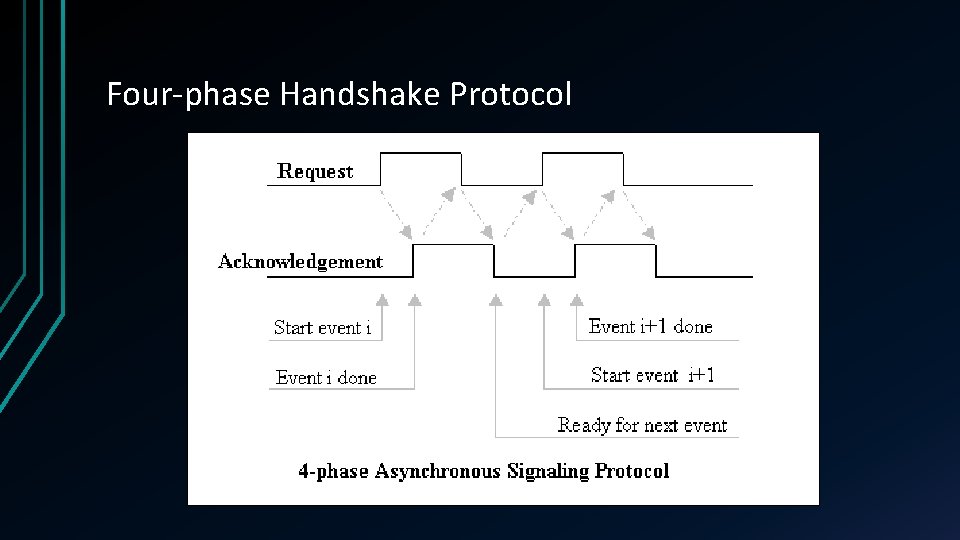

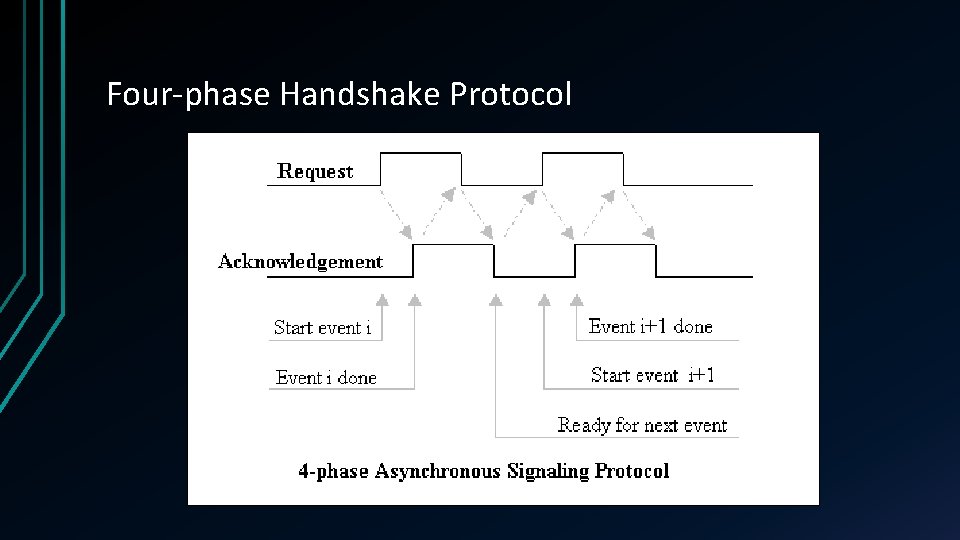

Four-phase Handshake Protocol

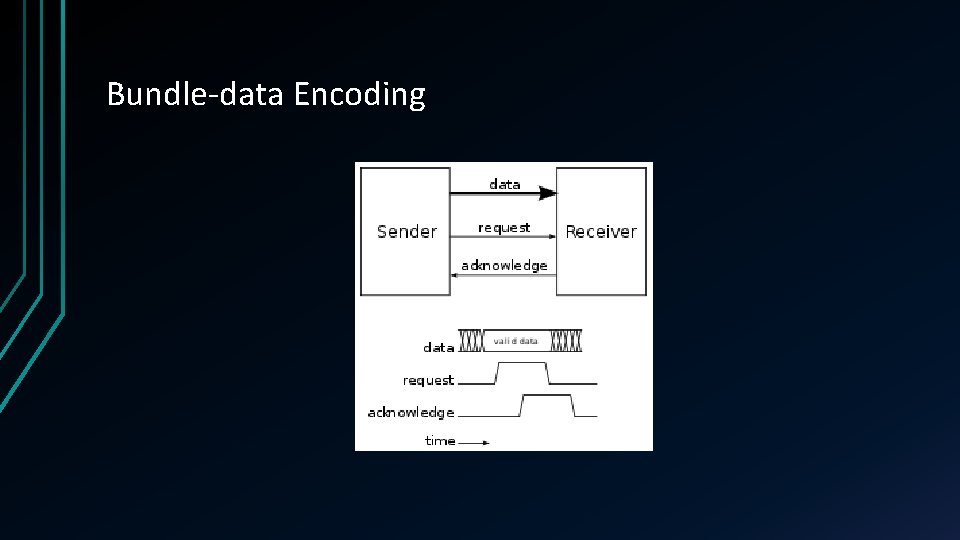

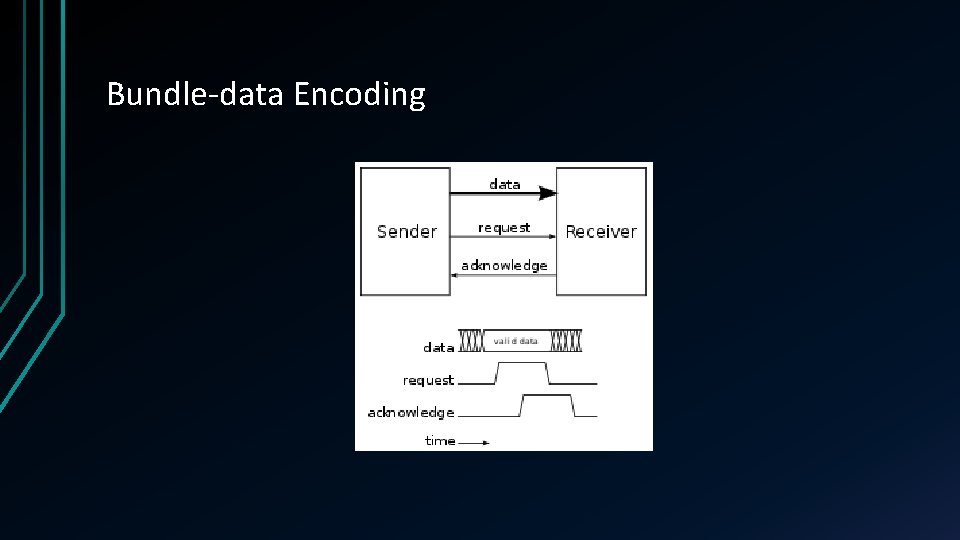

Bundle-data Encoding

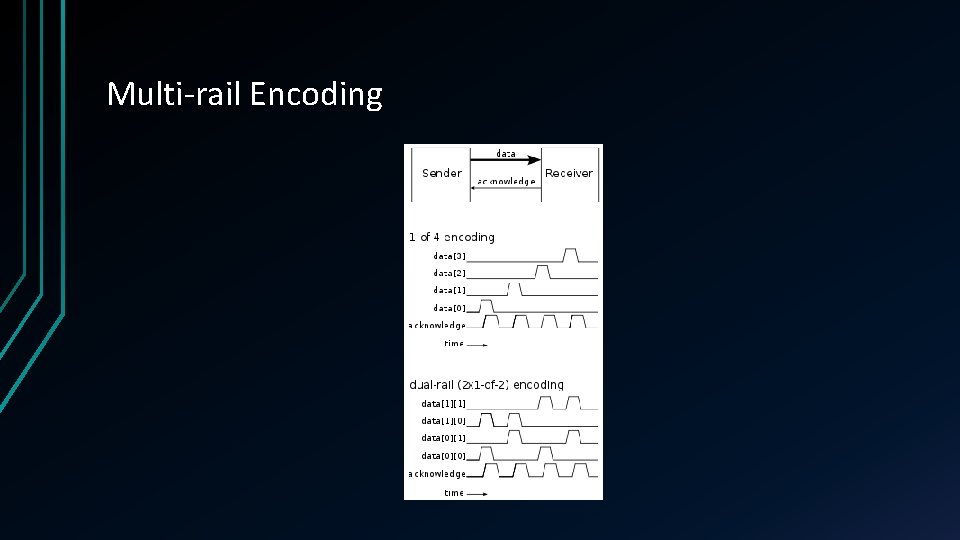

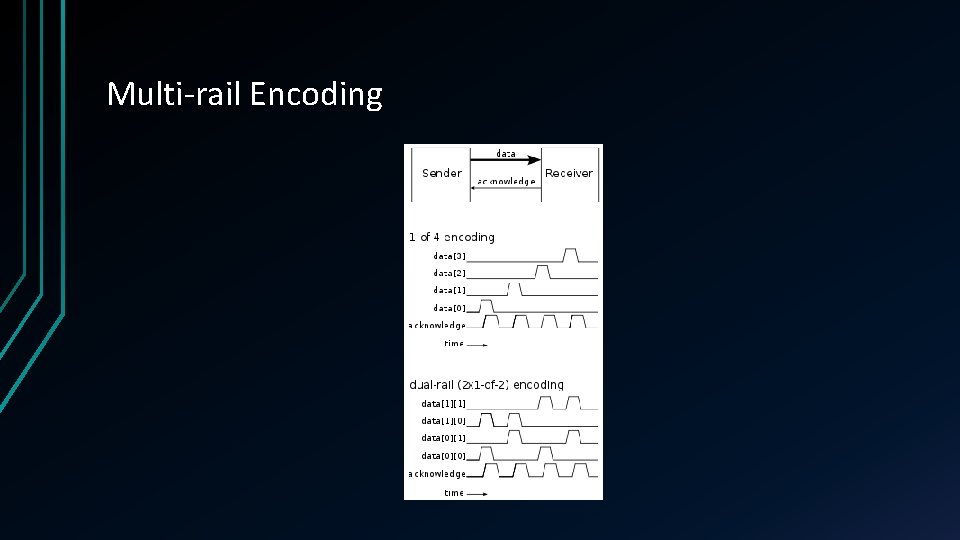

Multi-rail Encoding

Obstacles of Asynchronous CPUs • Testability • Design Tools Support • Design Practice

![References 1 Barton R S 1961 A new approach to the functional design References • [1] Barton, R. S. (1961). A new approach to the functional design](https://slidetodoc.com/presentation_image_h2/a107b9095e7c062983c56b9d3e98108e/image-12.jpg)

References • [1] Barton, R. S. (1961). A new approach to the functional design of a digital computer. IRE-AIEE -ACM '61 (Western) Papers, 393 -396. • [2] Electronic computers within the Ordnance Corps. Retrieved from http: //ftp. arl. mil/mike/comphist/61 ordnance/chap 4. html • [3] ILLIAC II-A Short Description and Annotated Bibliography. (1965). IEEE Transactions on Electronic Computers, IEEE Transactions on, IEEE Trans. Electron. Comput, (3), 399. doi: 10. 1109/PGEC. 1965. 264146 • [4] Martin, Alain J. , Burns, Steven M. , Lee, T. K. , Borkovic, Drazen. , Hazewindus, Pieter J. (1989). The Design of an Asynchronous Microprocessor. Proc. Decennial Caltech Conference on VLSI, 20 -22 • [5] Potato Power. Retrieved from http: //www. async. caltech. edu/~mika/potato 3. html • [6] Pahinkar, Sanskriti. , Negandhi, Harshita. (2013). Asynchronous Microprocessor. International Journal of Scientific and Research Publications (3) • [7] Asynchronous Design. Retrieved from http: //hdlplanet. tripod. com/comp_arch/async. html