AMICSA Follow up G Spiezia RADWG AMICSA Followup

- Slides: 11

AMICSA Follow up G. Spiezia RADWG- AMICSA Follow-up September 30 th 2014

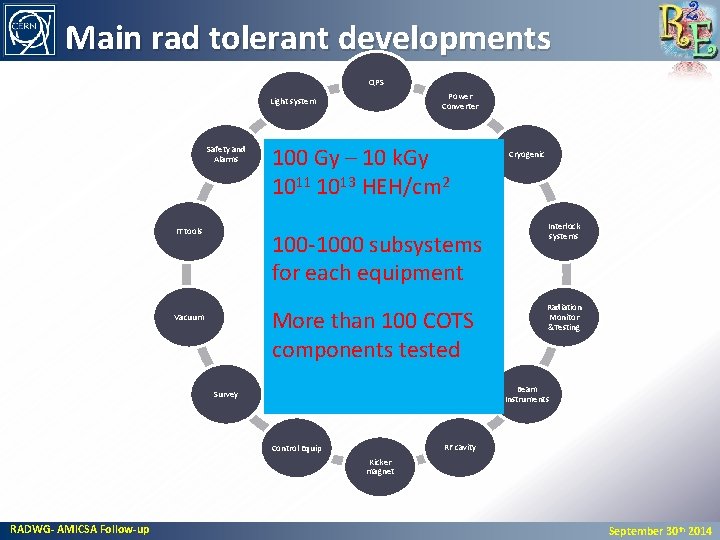

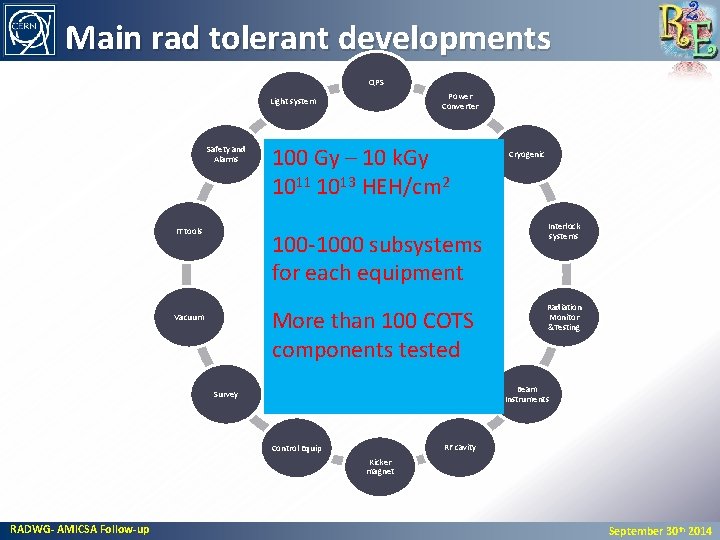

Main rad tolerant developments QPS Power Converter Light system Safety and Alarms IT tools 100 Gy – 10 k. Gy 1011 1013 HEH/cm 2 100 -1000 subsystems for each equipment A&T More than 100 COTS components tested Vacuum Cryogenic Interlock systems Radiation Monitor &Testing Beam Instruments Survey RF cavity Control Equip Kicker magnet RADWG- AMICSA Follow-up September 30 th 2014

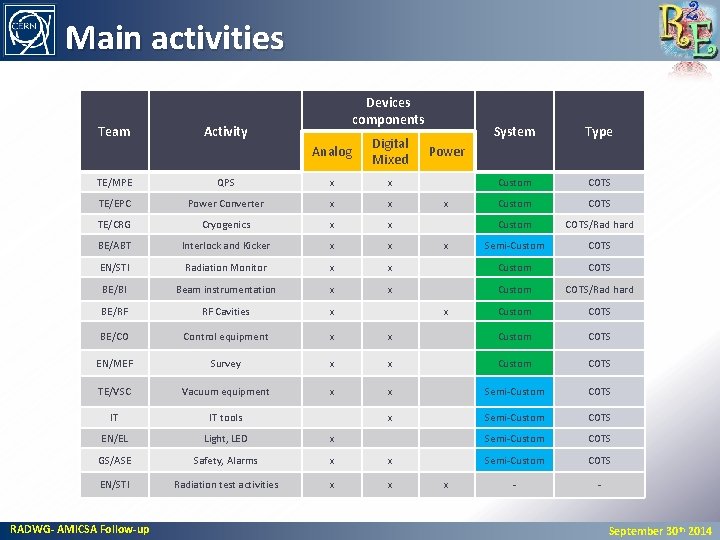

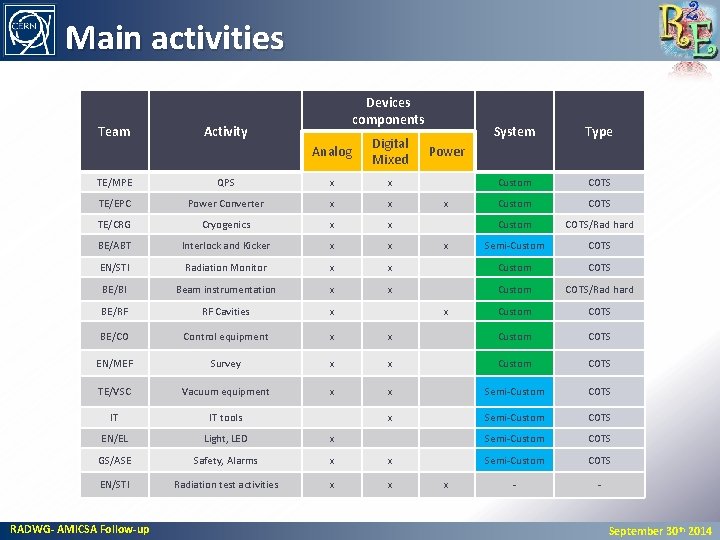

Main activities Team Devices components Activity Analog Digital Mixed System Type Custom COTS/Rad hard Semi-Custom COTS Power TE/MPE QPS x x TE/EPC Power Converter x x TE/CRG Cryogenics x x BE/ABT Interlock and Kicker x x EN/STI Radiation Monitor x x Custom COTS BE/BI Beam instrumentation x x Custom COTS/Rad hard BE/RF RF Cavities x Custom COTS BE/CO Control equipment x x Custom COTS EN/MEF Survey x x Custom COTS TE/VSC Vacuum equipment x x Semi-Custom COTS IT IT tools x Semi-Custom COTS EN/EL Light, LED x Semi-Custom COTS GS/ASE Safety, Alarms x x Semi-Custom COTS EN/STI Radiation test activities x x - - RADWG- AMICSA Follow-up x x September 30 th 2014

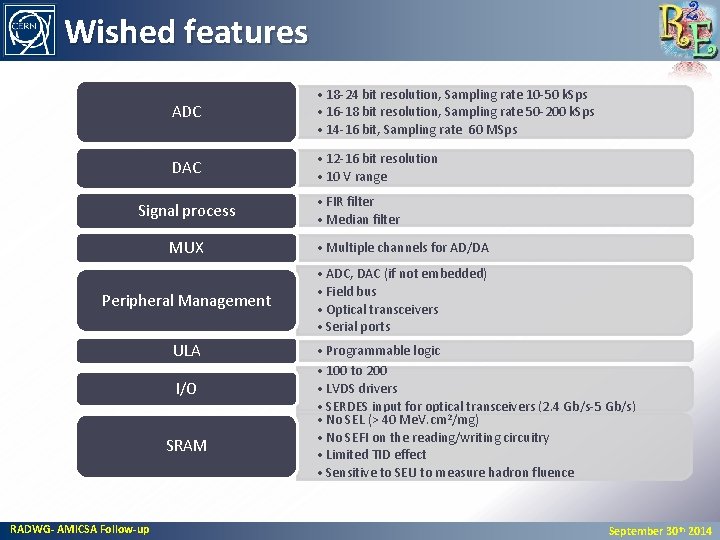

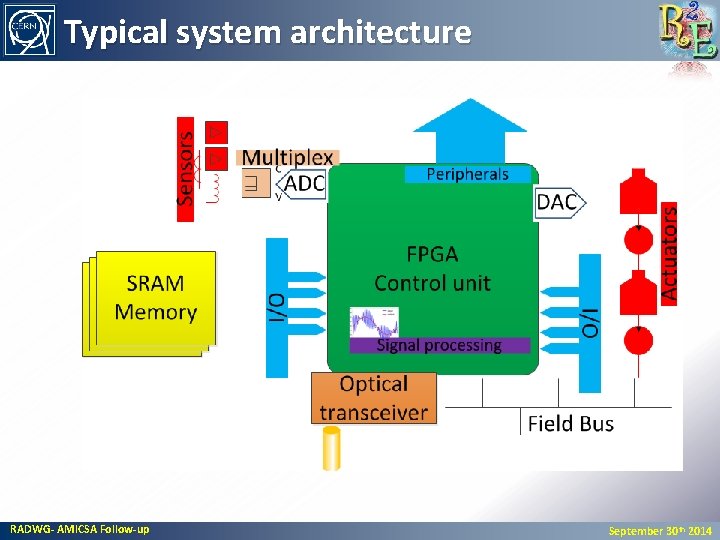

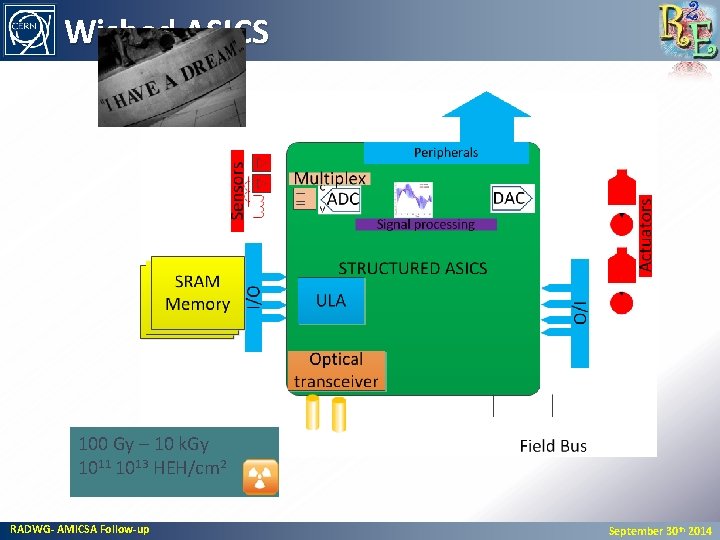

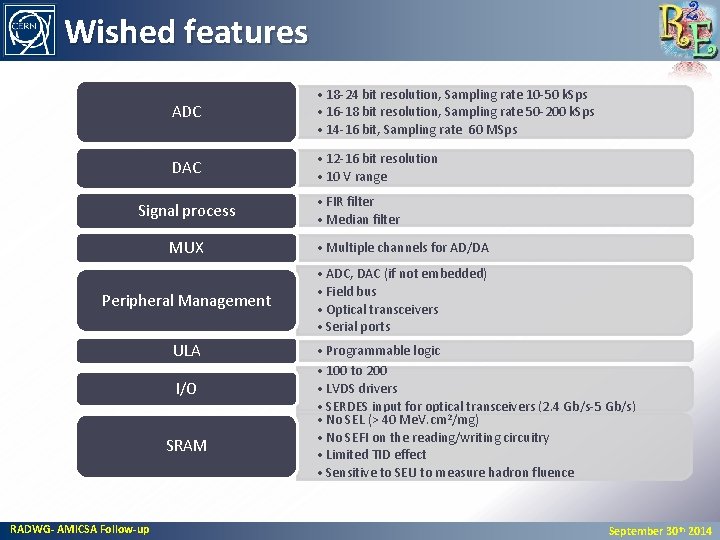

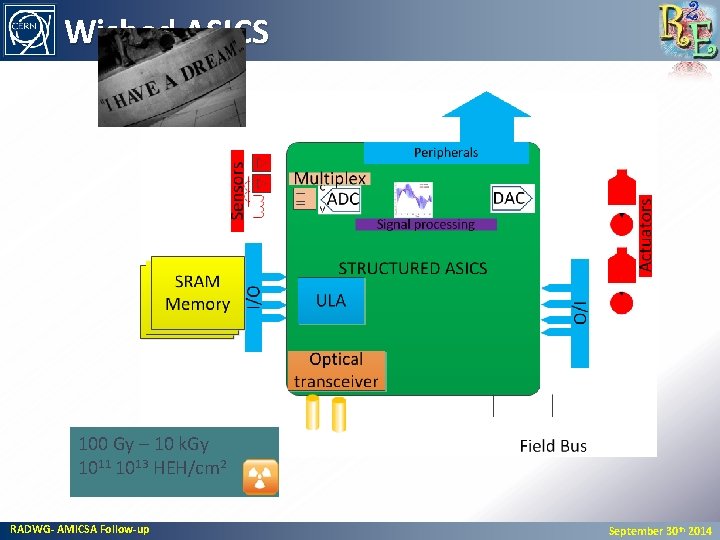

Wished features ADC • 18 -24 bit resolution, Sampling rate 10 -50 k. Sps • 16 -18 bit resolution, Sampling rate 50 -200 k. Sps • 14 -16 bit, Sampling rate 60 MSps DAC • 12 -16 bit resolution • 10 V range Signal process • FIR filter • Median filter MUX • Multiple channels for AD/DA Peripheral Management • ADC, DAC (if not embedded) • Field bus • Optical transceivers • Serial ports ULA I/O SRAM RADWG- AMICSA Follow-up • Programmable logic • 100 to 200 • LVDS drivers • SERDES input for optical transceivers (2. 4 Gb/s-5 Gb/s) • No SEL (> 40 Me. V. cm 2/mg) • No SEFI on the reading/writing circuitry • Limited TID effect • Sensitive to SEU to measure hadron fluence September 30 th 2014

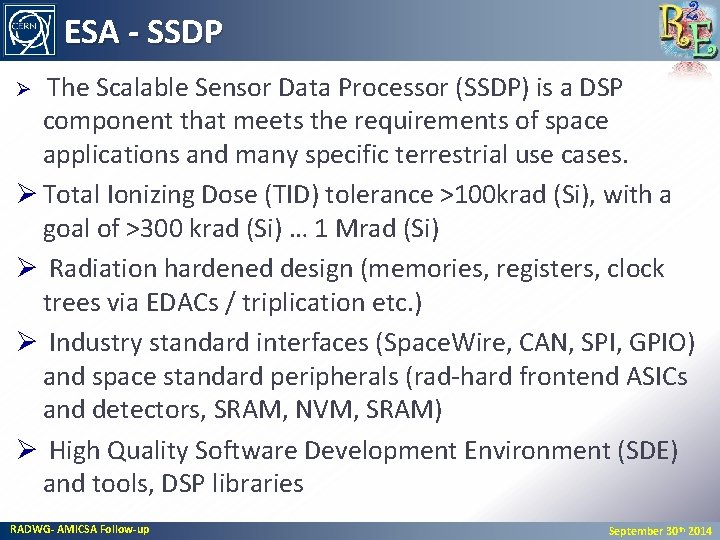

ESA - SSDP Ø The Scalable Sensor Data Processor (SSDP) is a DSP component that meets the requirements of space applications and many specific terrestrial use cases. Ø Total Ionizing Dose (TID) tolerance >100 krad (Si), with a goal of >300 krad (Si) … 1 Mrad (Si) Ø Radiation hardened design (memories, registers, clock trees via EDACs / triplication etc. ) Ø Industry standard interfaces (Space. Wire, CAN, SPI, GPIO) and space standard peripherals (rad-hard frontend ASICs and detectors, SRAM, NVM, SRAM) Ø High Quality Software Development Environment (SDE) and tools, DSP libraries RADWG- AMICSA Follow-up September 30 th 2014

ESA - SSDP Ø Integration of analogue / mixed signal features, including ADCs and circuitry for housekeeping data acquisition from typical sensors Ø 15/16 bit up to 100 MSps - ADC Ø 12 bit 100 k. Sps - ADC Ø The Scalable Sensor Data Processor (SSDP) is based on a previous prototype (DARE 180 library), already bench marked by companies (RUAG, Astrium) Ø No access restrictions for European users (ITAR free) Ø Rad-hard prototypes are expected for end 2015, with flight models Ø To understand: How we can make proposals at this stage RADWG- AMICSA Follow-up September 30 th 2014

Arquimea - products Ø ADC proposed for qualification Ø 19 -bit 100 Ksps Ø 16 -bit 1 Msps Ø 13 bit 10 Msps Ø 15 -bit 10 to 100 Msps Ø DAC(s): Ø 15 -bit 10 to 100 Msps DAC Ø 18 -bit 100 Ksps DAC Ø 16 -bit 1 Msps DAC Ø 13 bit 10 Msps DAC Ø List of product is here (https: //indico. cern. ch/event/343316/material/0/) Ø The company will be at CERN on 28 -29 October (SPAIN@CERN) RADWG- AMICSA Follow-up September 30 th 2014

Discussion Ø Are we interested? Ø Can we focus on functions which can be common to several groups? Ø Eventually propose a target number of chips Ø Each group should propose a list of a (some) key components/functionality Ø Check to which extent we can join the ESA development and or buy from private companies Ø Advantage: Ø standard package Ø No mechanical characterization Ø We could reach a significant number of chips Ø Points to be checked Ø Max TID for space qualification is 300 krad. Fine for LHC and some of the injection lines Ø Environment is different RADWG- AMICSA Follow-up September 30 th 2014

RADWG- AMICSA Follow-up September 30 th 2014

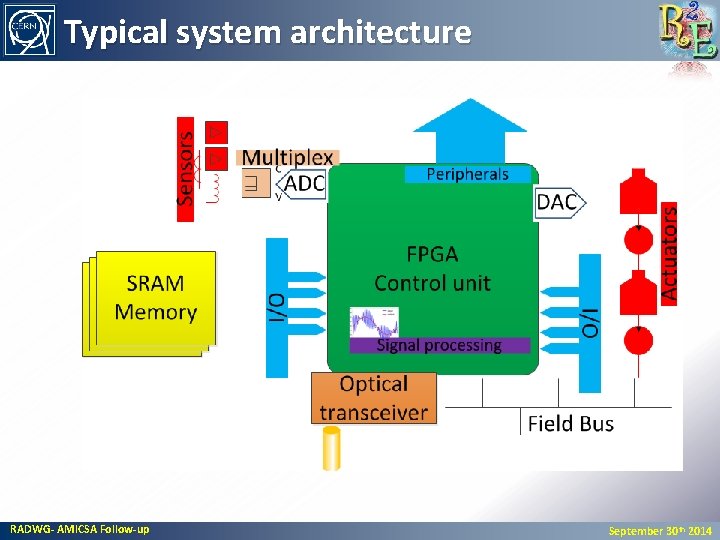

Typical system architecture RADWG- AMICSA Follow-up September 30 th 2014

Wished ASICS 100 Gy – 10 k. Gy 1011 1013 HEH/cm 2 RADWG- AMICSA Follow-up September 30 th 2014