ELMB RADWG Meeting 20 11 2017 EPESEFE Kamil

ELMB++: RADWG Meeting 20 -11 -2017 EP-ESE-FE Kamil Nicpon kamil. nicpon@cern. ch EP-ESE-FE 14 -3/003 09 -Sep-20 ELMB++ 1

Agenda • ELMB • Motivation for upgrade • Investigated possibilities • Solutions chosen for development 09 -Sep-20 ELMB++ 2

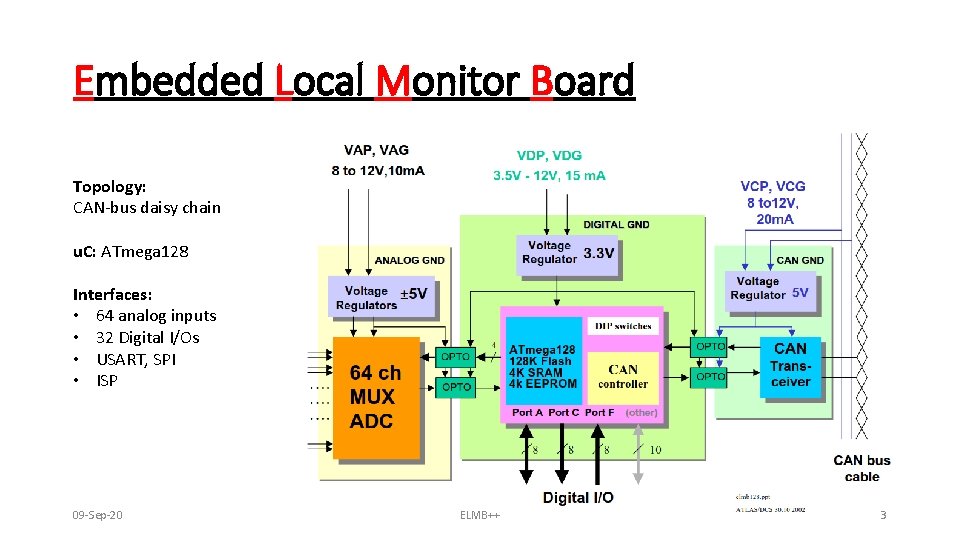

Embedded Local Monitor Board Topology: CAN-bus daisy chain u. C: ATmega 128 Interfaces: • 64 analog inputs • 32 Digital I/Os • USART, SPI • ISP 09 -Sep-20 ELMB++ 3

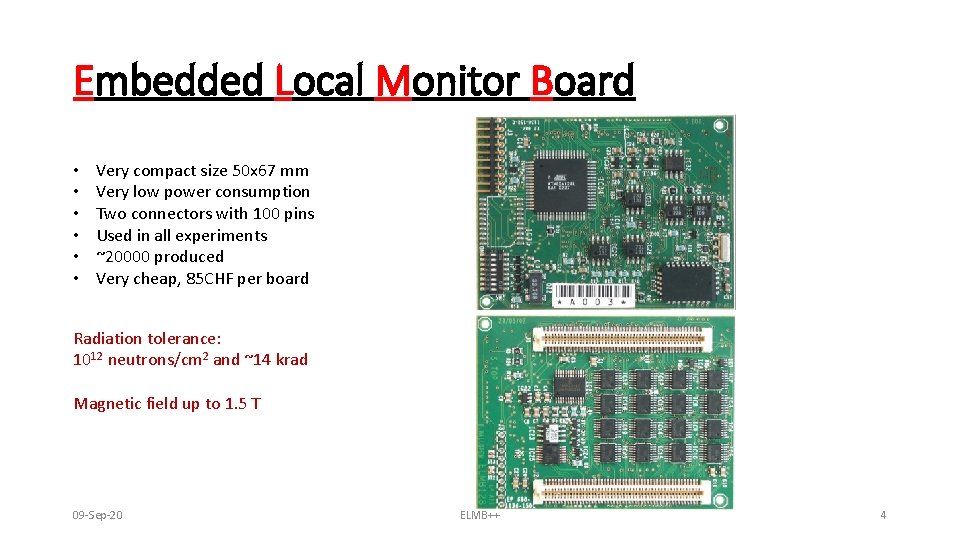

Embedded Local Monitor Board • • • Very compact size 50 x 67 mm Very low power consumption Two connectors with 100 pins Used in all experiments ~20000 produced Very cheap, 85 CHF per board Radiation tolerance: 1012 neutrons/cm 2 and ~14 krad Magnetic field up to 1. 5 T 09 -Sep-20 ELMB++ 4

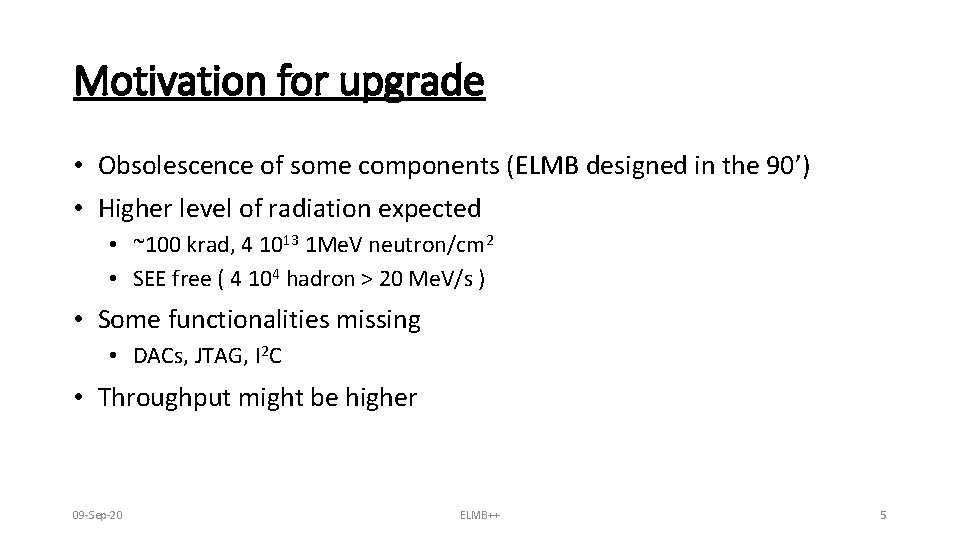

Motivation for upgrade • Obsolescence of some components (ELMB designed in the 90’) • Higher level of radiation expected • ~100 krad, 4 1013 1 Me. V neutron/cm 2 • SEE free ( 4 104 hadron > 20 Me. V/s ) • Some functionalities missing • DACs, JTAG, I 2 C • Throughput might be higher 09 -Sep-20 ELMB++ 5

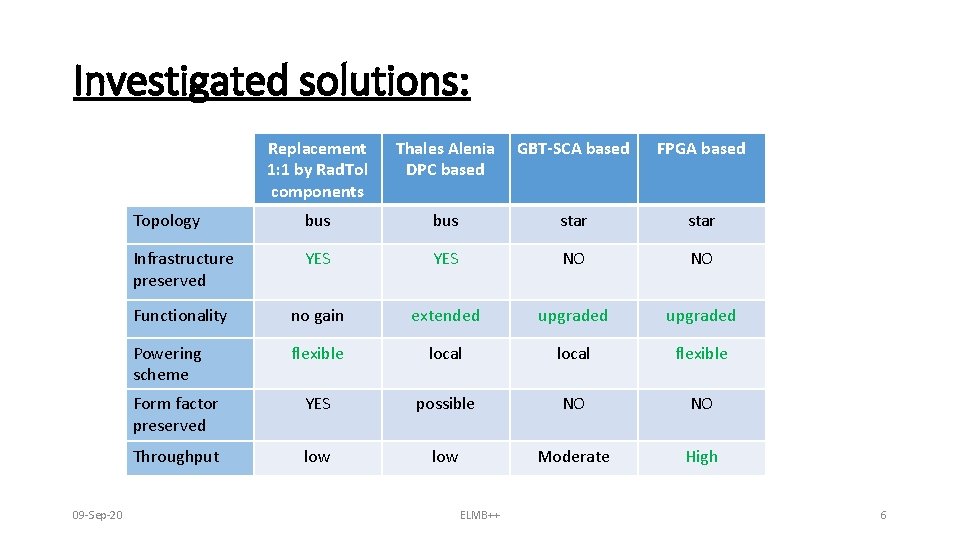

Investigated solutions: 09 -Sep-20 Replacement 1: 1 by Rad. Tol components Thales Alenia DPC based GBT-SCA based FPGA based Topology bus star Infrastructure preserved YES NO NO Functionality no gain extended upgraded Powering scheme flexible local flexible Form factor preserved YES possible NO NO Throughput low Moderate High ELMB++ 6

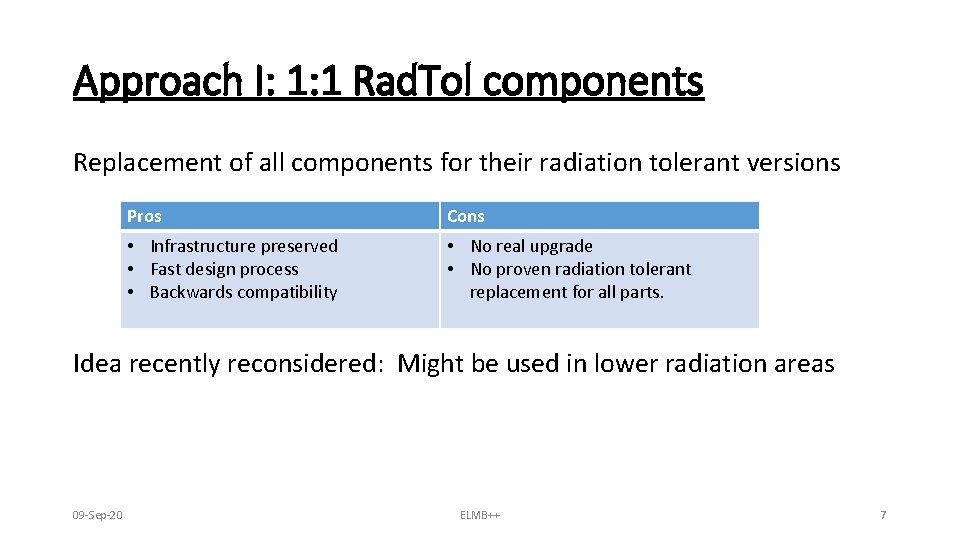

Approach I: 1: 1 Rad. Tol components Replacement of all components for their radiation tolerant versions Pros Cons • Infrastructure preserved • Fast design process • Backwards compatibility • No real upgrade • No proven radiation tolerant replacement for all parts. Idea recently reconsidered: Might be used in lower radiation areas 09 -Sep-20 ELMB++ 7

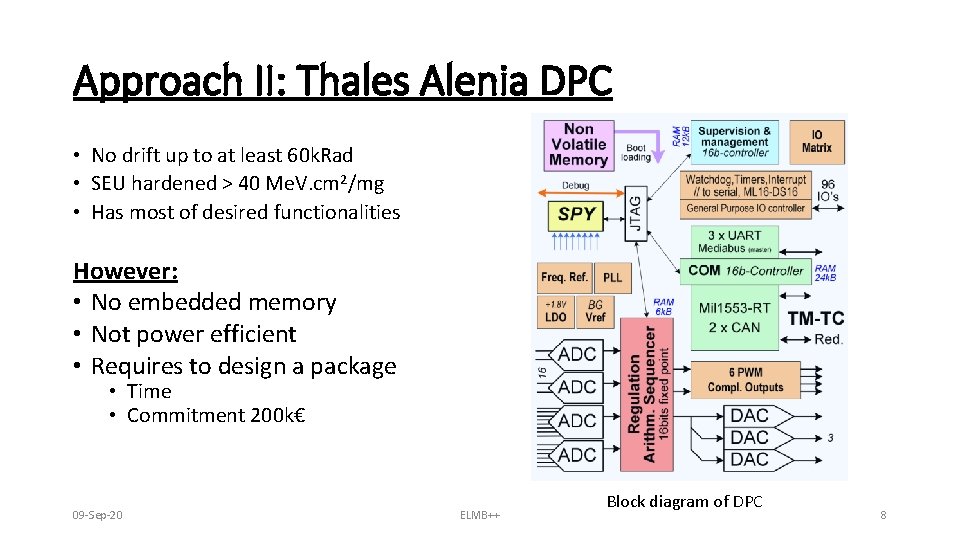

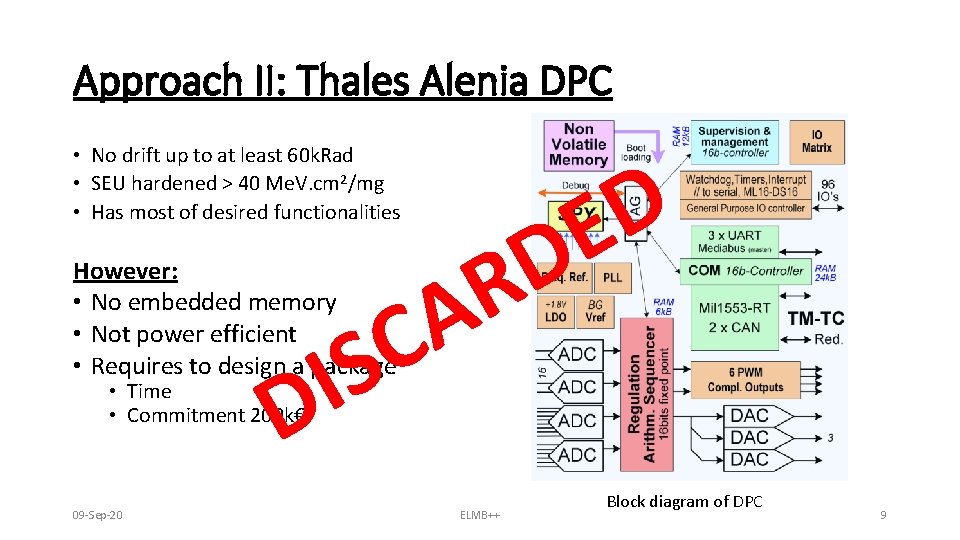

Approach II: Thales Alenia DPC • No drift up to at least 60 k. Rad • SEU hardened > 40 Me. V. cm 2/mg • Has most of desired functionalities However: • No embedded memory • Not power efficient • Requires to design a package • Time • Commitment 200 k€ 09 -Sep-20 ELMB++ Block diagram of DPC 8

Approach II: Thales Alenia DPC • No drift up to at least 60 k. Rad • SEU hardened > 40 Me. V. cm 2/mg • Has most of desired functionalities However: • No embedded memory • Not power efficient • Requires to design a package D E D R A C S I D • Time • Commitment 200 k€ 09 -Sep-20 ELMB++ Block diagram of DPC 9

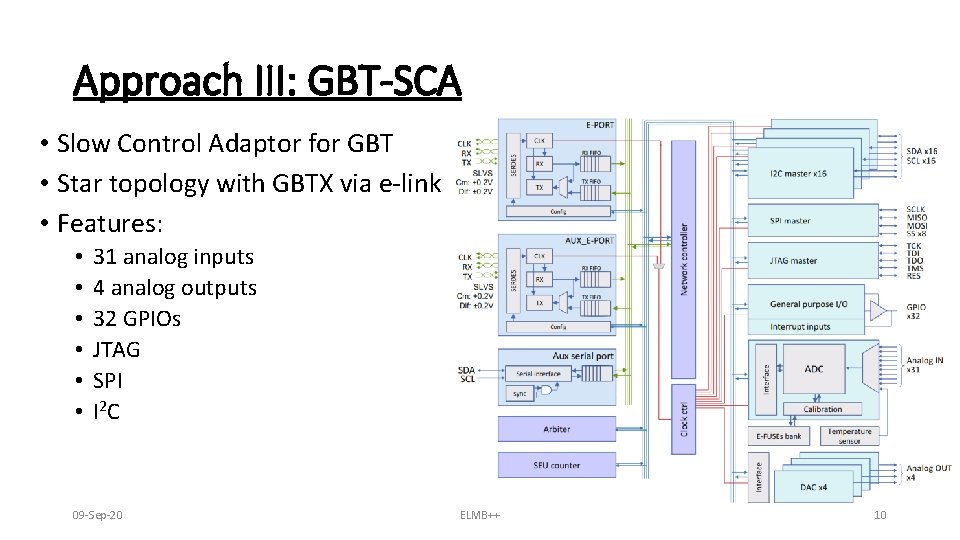

Approach III: GBT-SCA • Slow Control Adaptor for GBT • Star topology with GBTX via e-link • Features: • • • 31 analog inputs 4 analog outputs 32 GPIOs JTAG SPI I 2 C 09 -Sep-20 ELMB++ 10

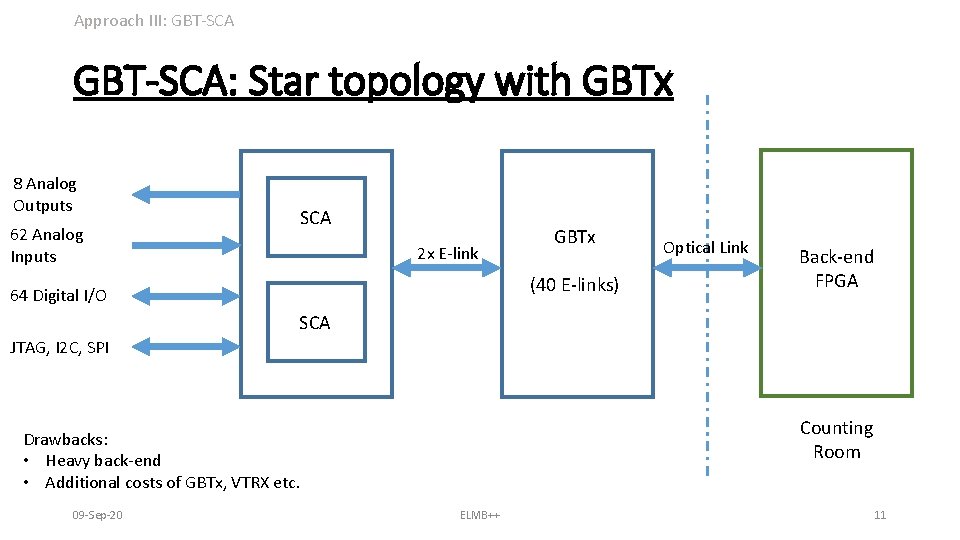

Approach III: GBT-SCA: Star topology with GBTx 8 Analog Outputs 62 Analog Inputs SCA 2 x E-link GBTx (40 E-links) 64 Digital I/O Optical Link Back-end FPGA SCA JTAG, I 2 C, SPI Counting Room Drawbacks: • Heavy back-end • Additional costs of GBTx, VTRX etc. 09 -Sep-20 ELMB++ 11

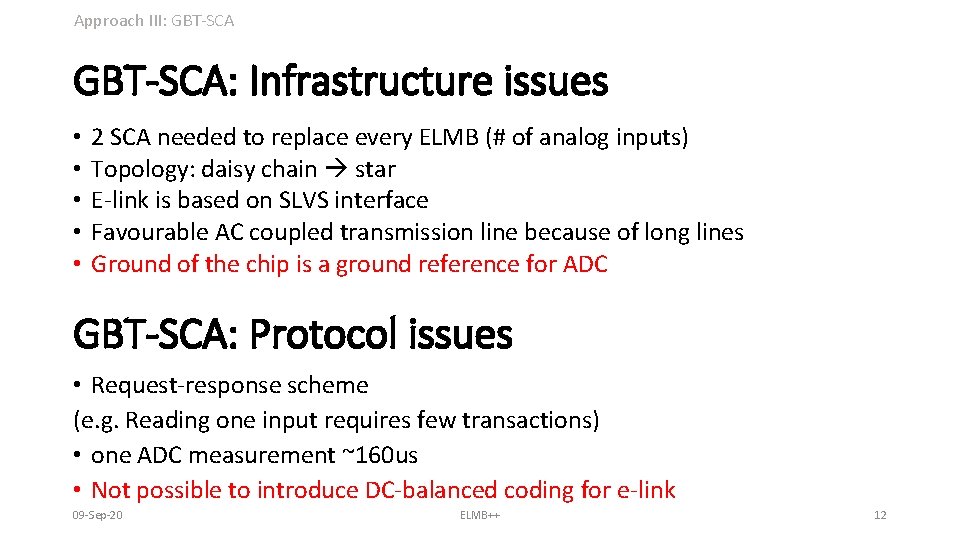

Approach III: GBT-SCA: Infrastructure issues • • • 2 SCA needed to replace every ELMB (# of analog inputs) Topology: daisy chain star E-link is based on SLVS interface Favourable AC coupled transmission line because of long lines Ground of the chip is a ground reference for ADC GBT-SCA: Protocol issues • Request-response scheme (e. g. Reading one input requires few transactions) • one ADC measurement ~160 us • Not possible to introduce DC-balanced coding for e-link 09 -Sep-20 ELMB++ 12

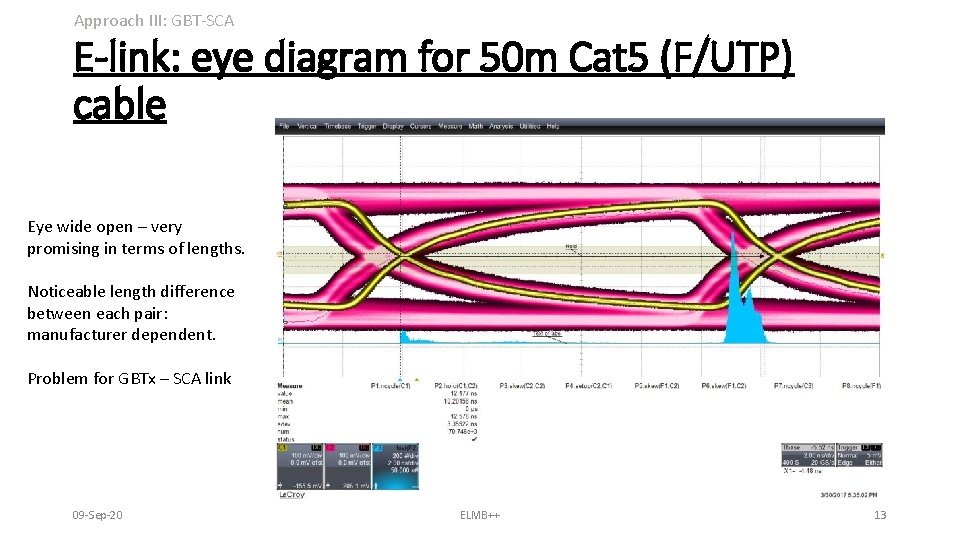

Approach III: GBT-SCA E-link: eye diagram for 50 m Cat 5 (F/UTP) cable Eye wide open – very promising in terms of lengths. Noticeable length difference between each pair: manufacturer dependent. Problem for GBTx – SCA link 09 -Sep-20 ELMB++ 13

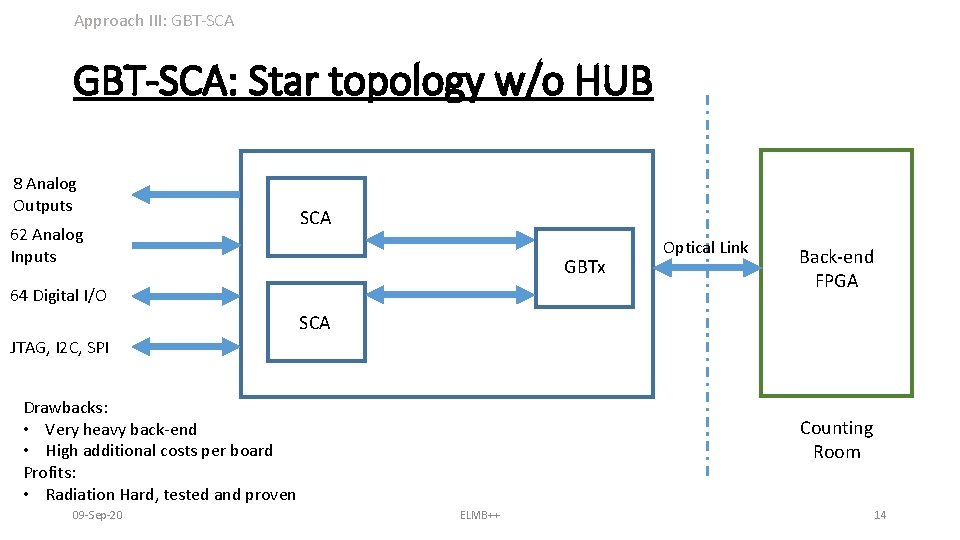

Approach III: GBT-SCA: Star topology w/o HUB 8 Analog Outputs 62 Analog Inputs SCA GBTx 64 Digital I/O Optical Link Back-end FPGA SCA JTAG, I 2 C, SPI Drawbacks: • Very heavy back-end • High additional costs per board Profits: • Radiation Hard, tested and proven 09 -Sep-20 Counting Room ELMB++ 14

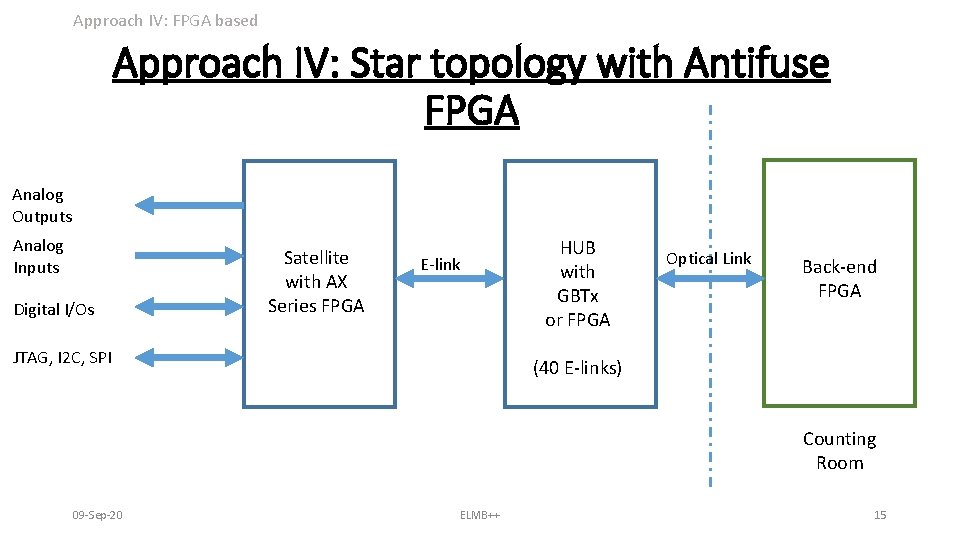

Approach IV: FPGA based Approach IV: Star topology with Antifuse FPGA Analog Outputs Analog Inputs Digital I/Os Satellite with AX Series FPGA E-link JTAG, I 2 C, SPI HUB with GBTx or FPGA Optical Link Back-end FPGA (40 E-links) Counting Room 09 -Sep-20 ELMB++ 15

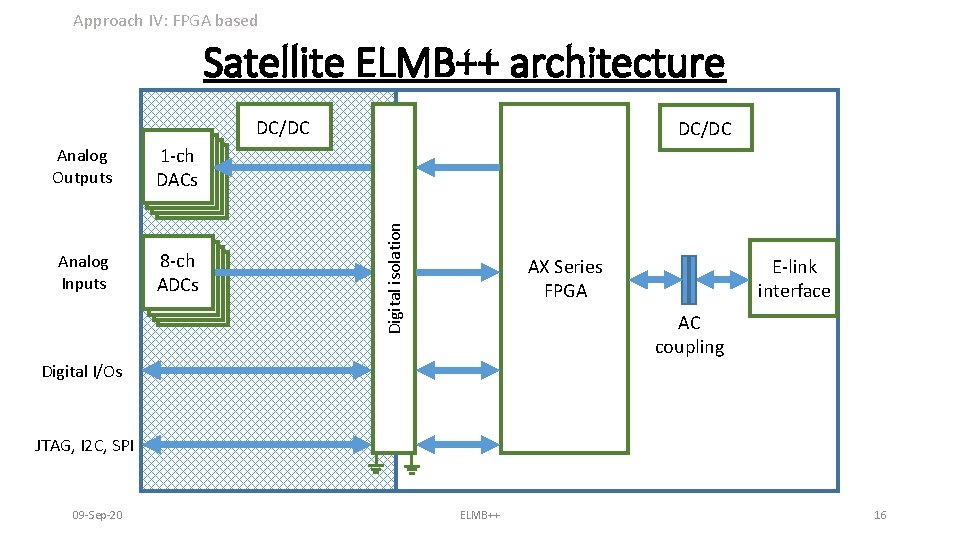

Approach IV: FPGA based Satellite ELMB++ architecture DC/DC 1 -ch DACs Analog Inputs 8 -ch ADCs Digital isolation Analog Outputs DC/DC AX Series FPGA E-link interface AC coupling Digital I/Os JTAG, I 2 C, SPI 09 -Sep-20 ELMB++ 16

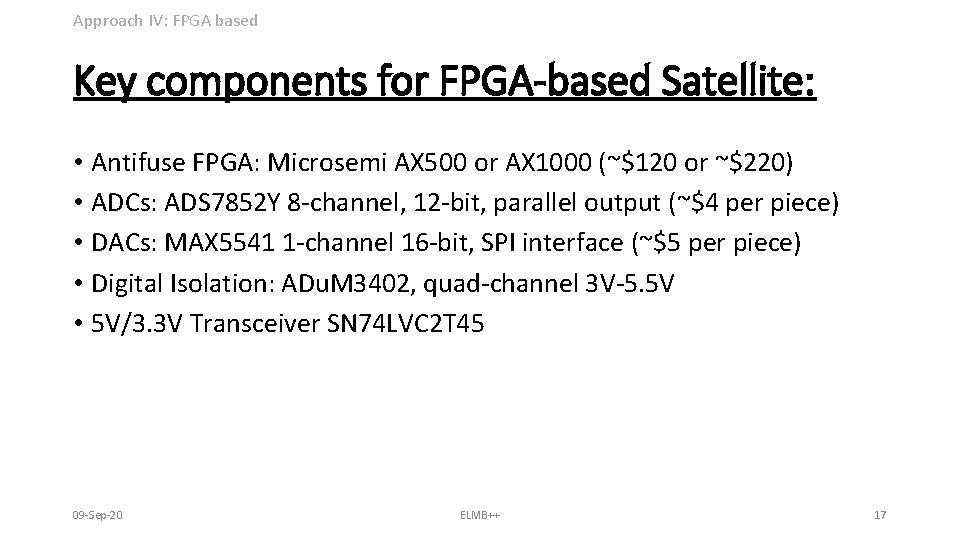

Approach IV: FPGA based Key components for FPGA-based Satellite: • Antifuse FPGA: Microsemi AX 500 or AX 1000 (~$120 or ~$220) • ADCs: ADS 7852 Y 8 -channel, 12 -bit, parallel output (~$4 per piece) • DACs: MAX 5541 1 -channel 16 -bit, SPI interface (~$5 per piece) • Digital Isolation: ADu. M 3402, quad-channel 3 V-5. 5 V • 5 V/3. 3 V Transceiver SN 74 LVC 2 T 45 09 -Sep-20 ELMB++ 17

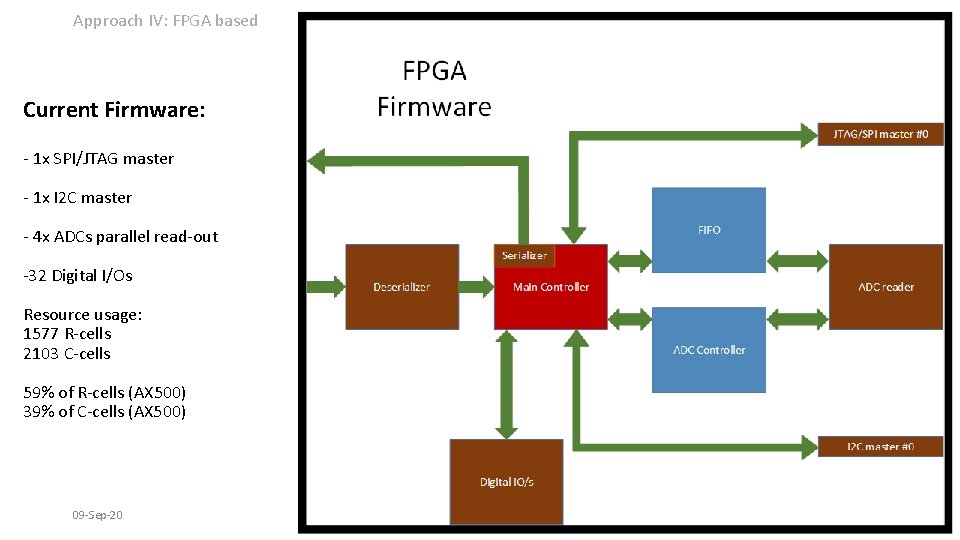

Approach IV: FPGA based Current Firmware: - 1 x SPI/JTAG master - 1 x I 2 C master - 4 x ADCs parallel read-out -32 Digital I/Os Resource usage: 1577 R-cells 2103 C-cells 59% of R-cells (AX 500) 39% of C-cells (AX 500) 09 -Sep-20 ELMB++ 18

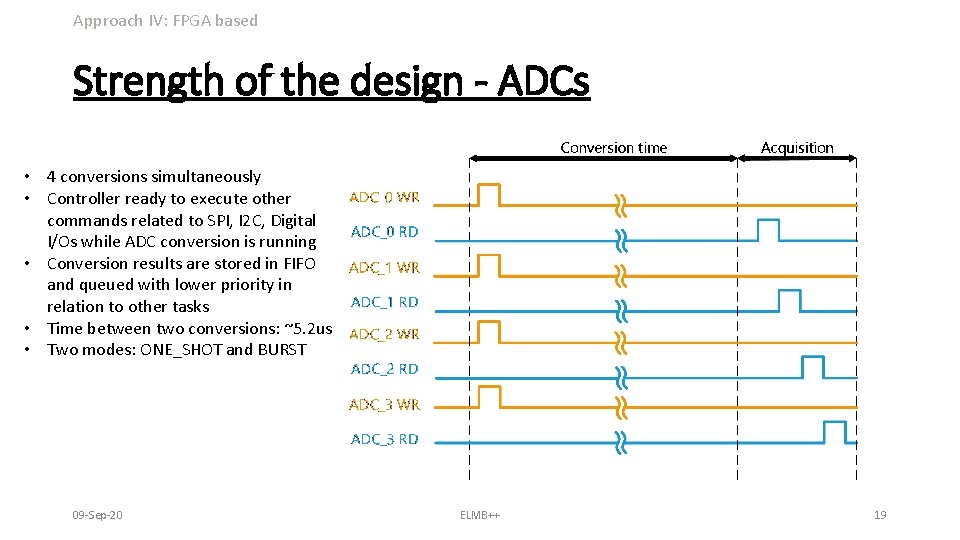

Approach IV: FPGA based Strength of the design - ADCs • 4 conversions simultaneously • Controller ready to execute other commands related to SPI, I 2 C, Digital I/Os while ADC conversion is running • Conversion results are stored in FIFO and queued with lower priority in relation to other tasks • Time between two conversions: ~5. 2 us • Two modes: ONE_SHOT and BURST 09 -Sep-20 ELMB++ 19

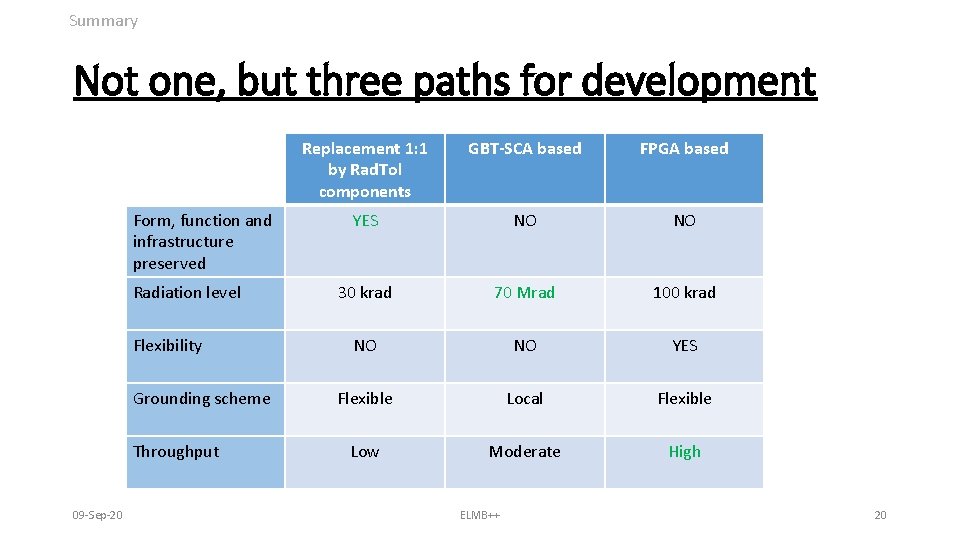

Summary Not one, but three paths for development Form, function and infrastructure preserved Radiation level Flexibility Grounding scheme Throughput 09 -Sep-20 Replacement 1: 1 by Rad. Tol components GBT-SCA based FPGA based YES NO NO 30 krad 70 Mrad 100 krad NO NO YES Flexible Local Flexible Low Moderate High ELMB++ 20

Thank You 09 -Sep-20 ELMB++ 21

- Slides: 21