Remote Firmware Down Load Firmware Download Diagram for

- Slides: 8

Remote Firmware Down Load

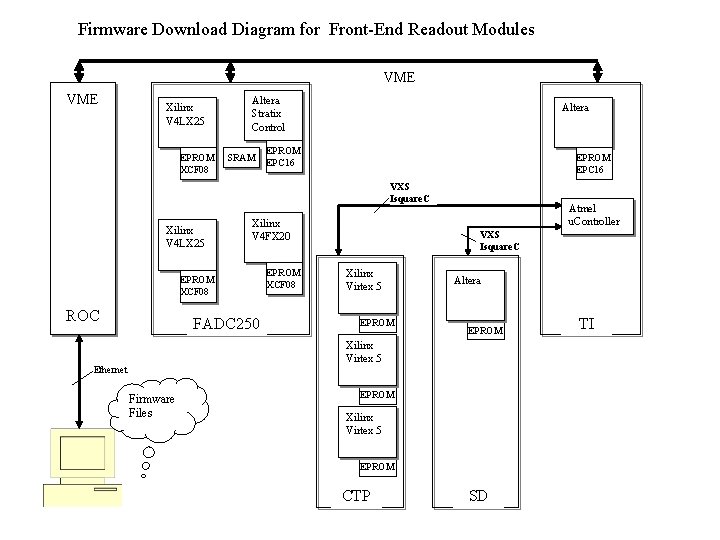

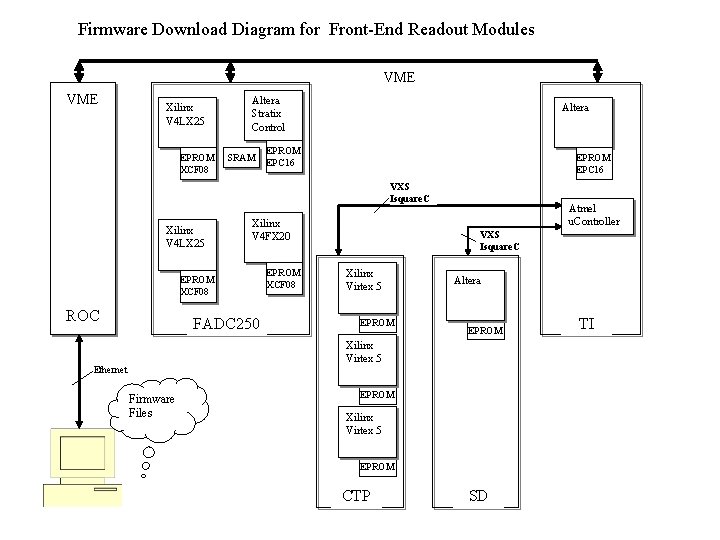

Firmware Download Diagram for Front-End Readout Modules VME Xilinx V 4 LX 25 EPROM XCF 08 Altera Stratix Control SRAM Altera EPROM EPC 16 VXS Isquare. C Xilinx V 4 LX 25 Xilinx V 4 FX 20 EPROM XCF 08 ROC FADC 250 EPROM XCF 08 Atmel u. Controller VXS Isquare. C Xilinx Virtex 5 EPROM Altera EPROM Xilinx Virtex 5 Ethernet Firmware Files EPROM Xilinx Virtex 5 EPROM CTP SD TI

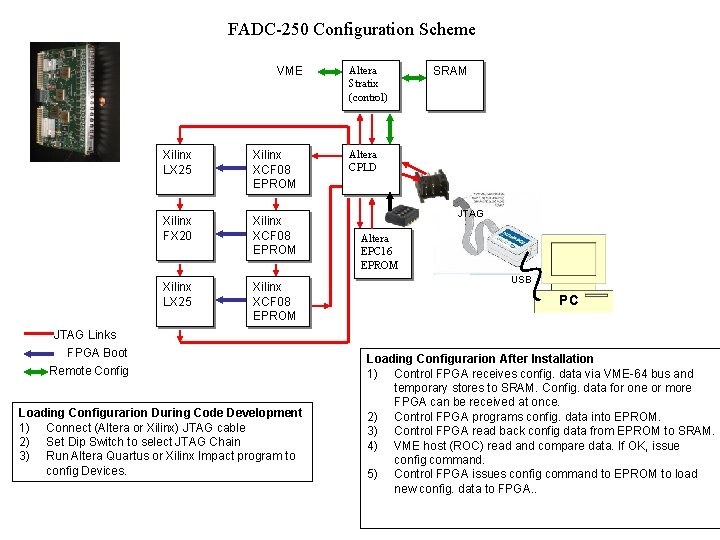

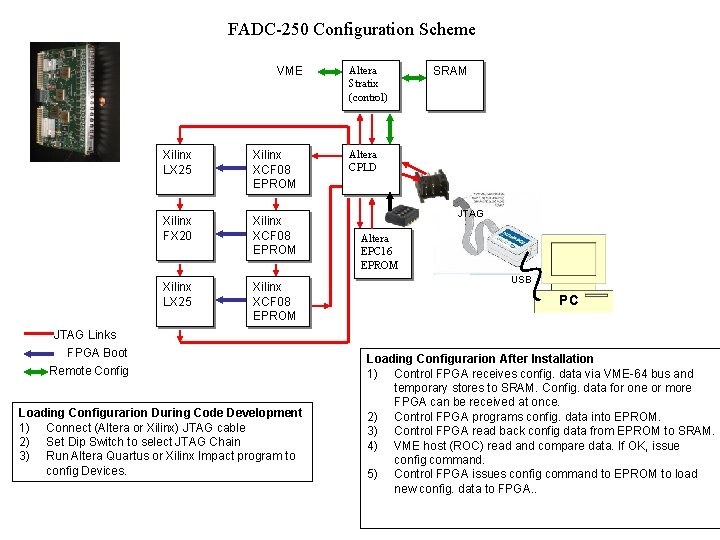

FADC-250 Configuration Scheme VME Xilinx LX 25 Xilinx XCF 08 EPROM Xilinx FX 20 Xilinx XCF 08 EPROM Xilinx LX 25 Xilinx XCF 08 EPROM JTAG Links FPGA Boot Remote Config Loading Configurarion During Code Development 1) Connect (Altera or Xilinx) JTAG cable 2) Set Dip Switch to select JTAG Chain 3) Run Altera Quartus or Xilinx Impact program to config Devices. Altera Stratix (control) SRAM Altera CPLD JTAG Altera EPC 16 EPROM USB PC Loading Configurarion After Installation 1) Control FPGA receives config. data via VME-64 bus and temporary stores to SRAM. Config. data for one or more FPGA can be received at once. 2) Control FPGA programs config. data into EPROM. 3) Control FPGA read back config data from EPROM to SRAM. 4) VME host (ROC) read and compare data. If OK, issue config command. 5) Control FPGA issues config command to EPROM to load new config. data to FPGA. .

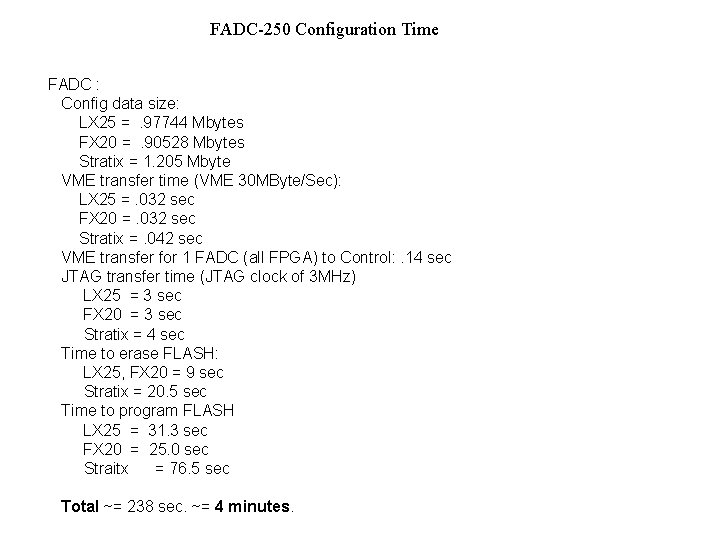

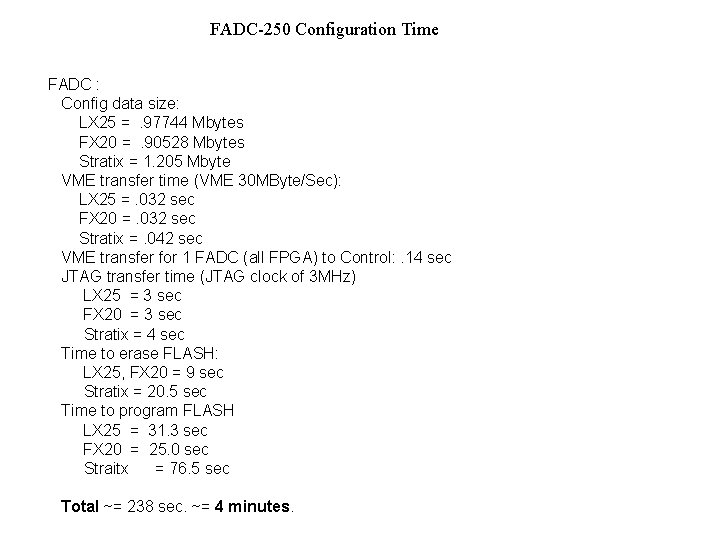

FADC-250 Configuration Time FADC : Config data size: LX 25 =. 97744 Mbytes FX 20 =. 90528 Mbytes Stratix = 1. 205 Mbyte VME transfer time (VME 30 MByte/Sec): LX 25 =. 032 sec FX 20 =. 032 sec Stratix =. 042 sec VME transfer for 1 FADC (all FPGA) to Control: . 14 sec JTAG transfer time (JTAG clock of 3 MHz) LX 25 = 3 sec FX 20 = 3 sec Stratix = 4 sec Time to erase FLASH: LX 25, FX 20 = 9 sec Stratix = 20. 5 sec Time to program FLASH LX 25 = 31. 3 sec FX 20 = 25. 0 sec Straitx = 76. 5 sec Total ~= 238 sec. ~= 4 minutes.

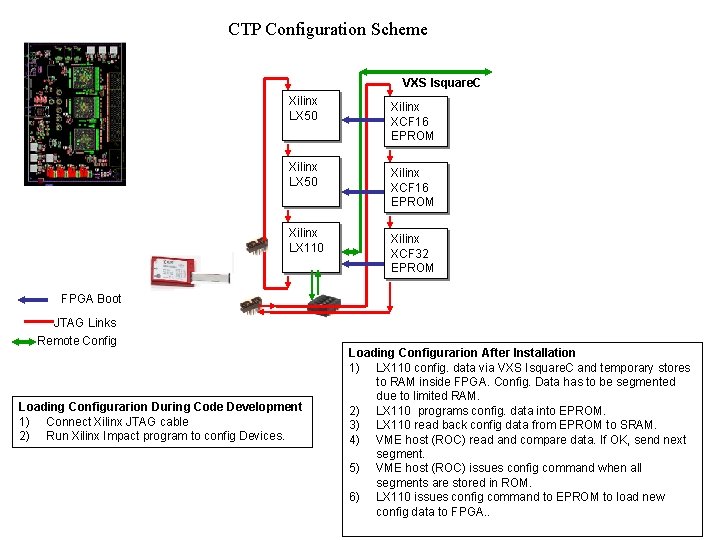

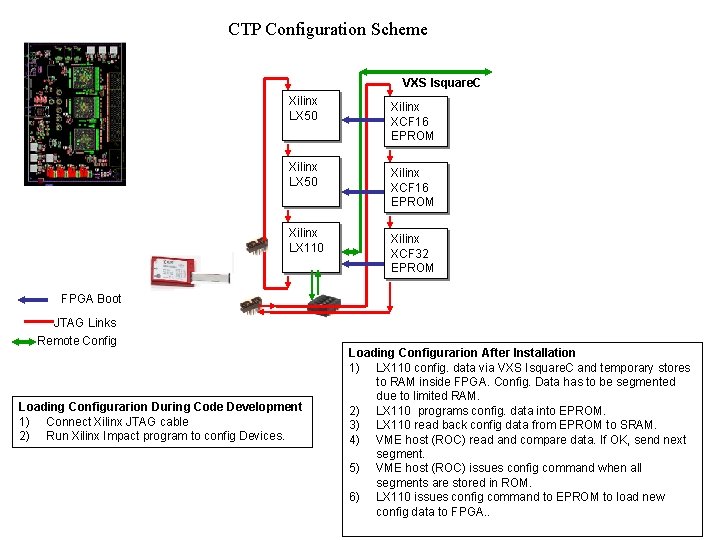

CTP Configuration Scheme VXS Isquare. C Xilinx LX 50 Xilinx XCF 16 EPROM Xilinx LX 110 Xilinx XCF 32 EPROM FPGA Boot JTAG Links Remote Config Loading Configurarion During Code Development 1) Connect Xilinx JTAG cable 2) Run Xilinx Impact program to config Devices. Loading Configurarion After Installation 1) LX 110 config. data via VXS Isquare. C and temporary stores to RAM inside FPGA. Config. Data has to be segmented due to limited RAM. 2) LX 110 programs config. data into EPROM. 3) LX 110 read back config data from EPROM to SRAM. 4) VME host (ROC) read and compare data. If OK, send next segment. 5) VME host (ROC) issues config command when all segments are stored in ROM. 6) LX 110 issues config command to EPROM to load new config data to FPGA. .

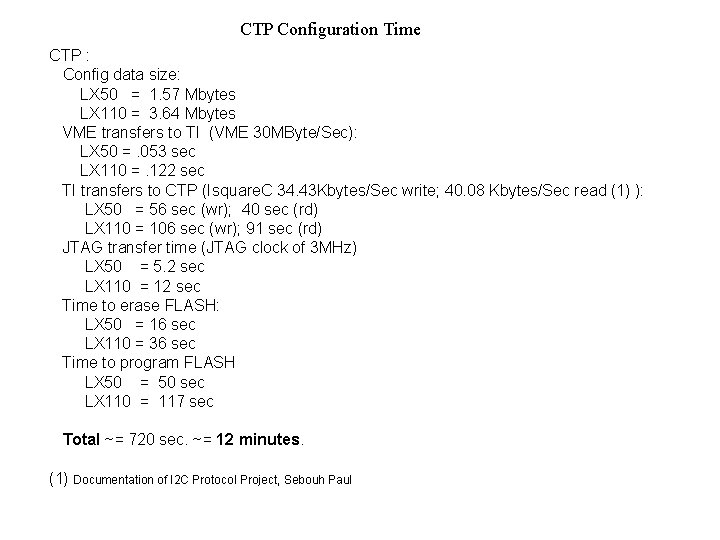

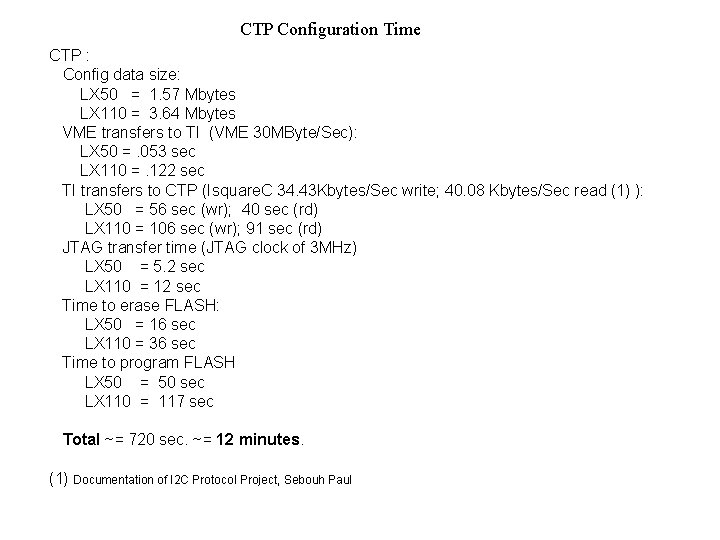

CTP Configuration Time CTP : Config data size: LX 50 = 1. 57 Mbytes LX 110 = 3. 64 Mbytes VME transfers to TI (VME 30 MByte/Sec): LX 50 =. 053 sec LX 110 =. 122 sec TI transfers to CTP (Isquare. C 34. 43 Kbytes/Sec write; 40. 08 Kbytes/Sec read (1) ): LX 50 = 56 sec (wr); 40 sec (rd) LX 110 = 106 sec (wr); 91 sec (rd) JTAG transfer time (JTAG clock of 3 MHz) LX 50 = 5. 2 sec LX 110 = 12 sec Time to erase FLASH: LX 50 = 16 sec LX 110 = 36 sec Time to program FLASH LX 50 = 50 sec LX 110 = 117 sec Total ~= 720 sec. ~= 12 minutes. (1) Documentation of I 2 C Protocol Project, Sebouh Paul

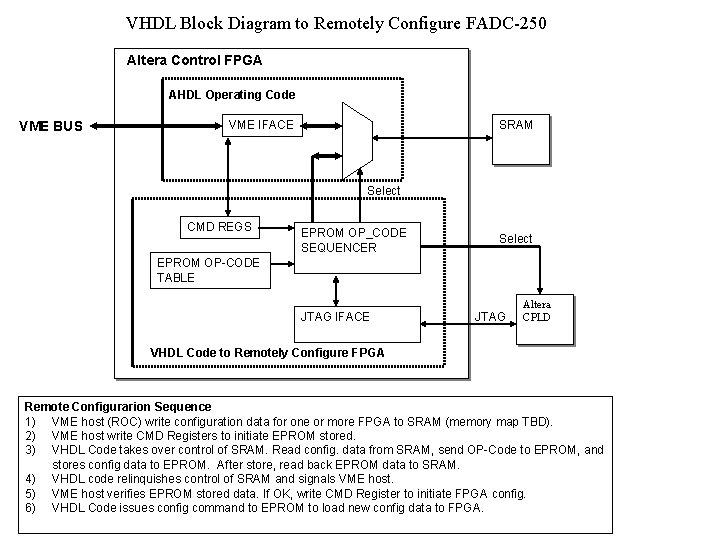

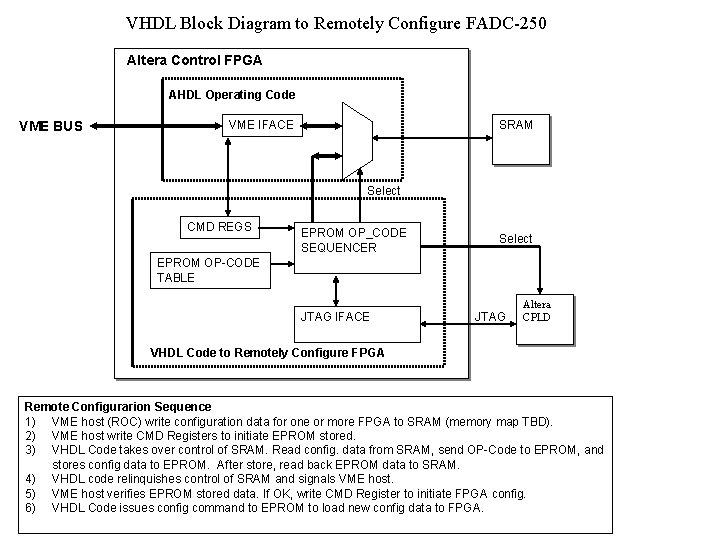

VHDL Block Diagram to Remotely Configure FADC-250 Altera Control FPGA AHDL Operating Code VME BUS SRAM VME IFACE Select CMD REGS EPROM OP_CODE SEQUENCER Select EPROM OP-CODE TABLE JTAG IFACE JTAG Altera CPLD VHDL Code to Remotely Configure FPGA Remote Configurarion Sequence 1) VME host (ROC) write configuration data for one or more FPGA to SRAM (memory map TBD). 2) VME host write CMD Registers to initiate EPROM stored. 3) VHDL Code takes over control of SRAM. Read config. data from SRAM, send OP-Code to EPROM, and stores config data to EPROM. After store, read back EPROM data to SRAM. 4) VHDL code relinquishes control of SRAM and signals VME host. 5) VME host verifies EPROM stored data. If OK, write CMD Register to initiate FPGA config. 6) VHDL Code issues config command to EPROM to load new config data to FPGA.

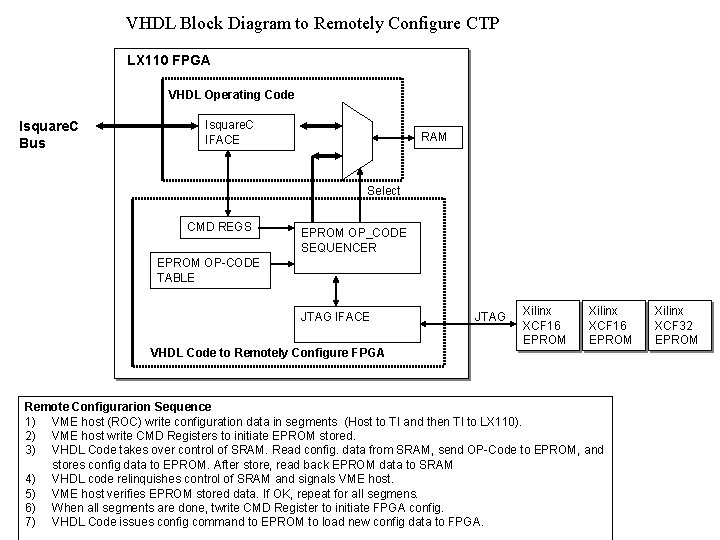

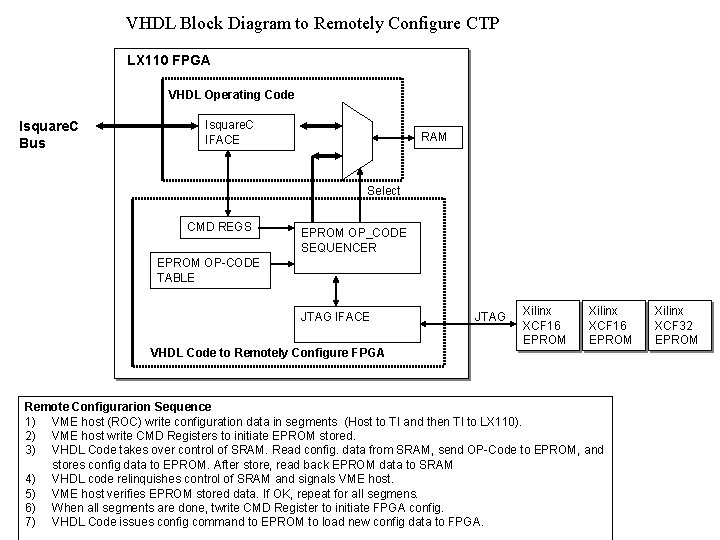

VHDL Block Diagram to Remotely Configure CTP LX 110 FPGA VHDL Operating Code Isquare. C Bus Isquare. C IFACE RAM Select CMD REGS EPROM OP_CODE SEQUENCER EPROM OP-CODE TABLE JTAG IFACE VHDL Code to Remotely Configure FPGA JTAG Xilinx XCF 16 EPROM Remote Configurarion Sequence 1) VME host (ROC) write configuration data in segments (Host to TI and then TI to LX 110). 2) VME host write CMD Registers to initiate EPROM stored. 3) VHDL Code takes over control of SRAM. Read config. data from SRAM, send OP-Code to EPROM, and stores config data to EPROM. After store, read back EPROM data to SRAM 4) VHDL code relinquishes control of SRAM and signals VME host. 5) VME host verifies EPROM stored data. If OK, repeat for all segmens. 6) When all segments are done, twrite CMD Register to initiate FPGA config. 7) VHDL Code issues config command to EPROM to load new config data to FPGA. Xilinx XCF 32 EPROM