Muistit Muisteja kytetn tietovarastoina tietokoneissa ja sulautetuissa jrjestelmiss

- Slides: 93

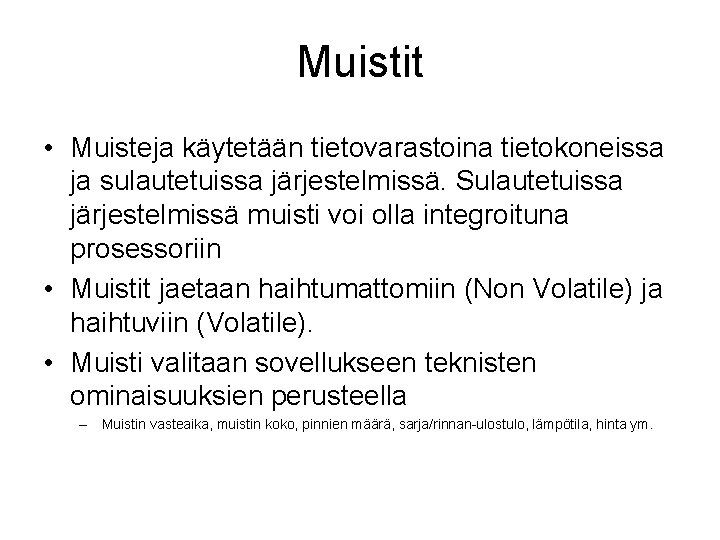

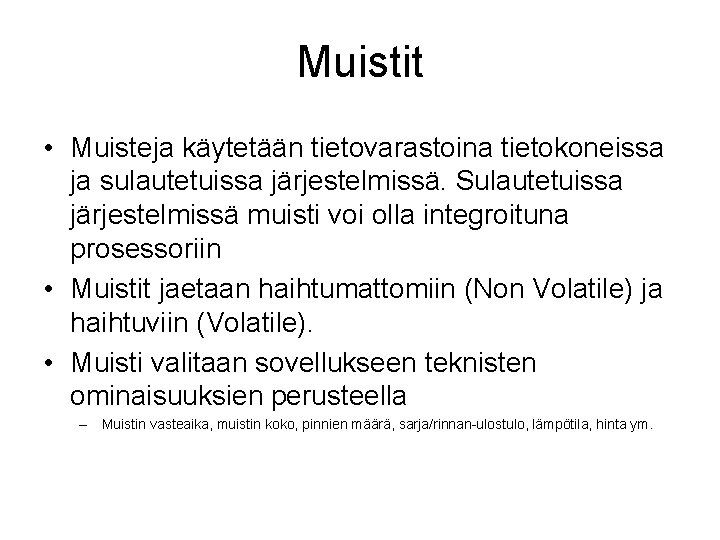

Muistit • Muisteja käytetään tietovarastoina tietokoneissa ja sulautetuissa järjestelmissä. Sulautetuissa järjestelmissä muisti voi olla integroituna prosessoriin • Muistit jaetaan haihtumattomiin (Non Volatile) ja haihtuviin (Volatile). • Muisti valitaan sovellukseen teknisten ominaisuuksien perusteella – Muistin vasteaika, muistin koko, pinnien määrä, sarja/rinnan-ulostulo, lämpötila, hinta ym.

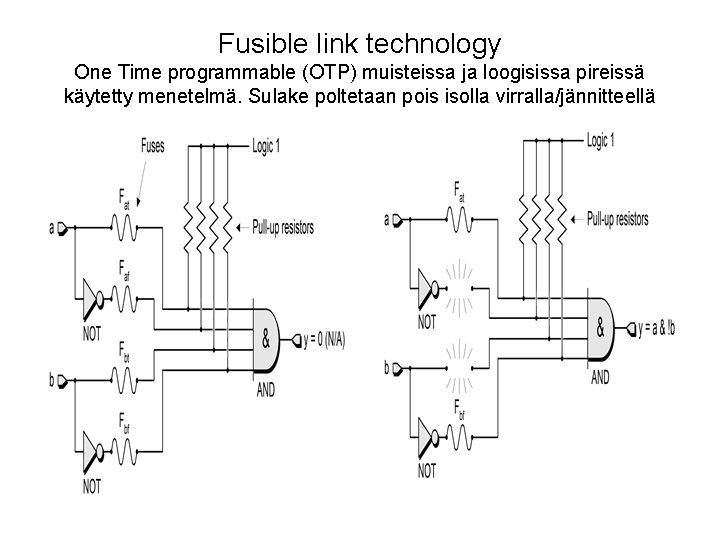

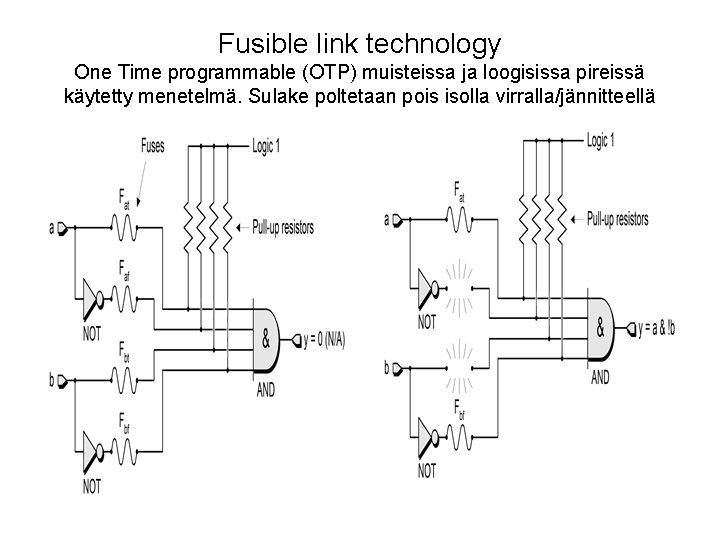

Fusible link technology One Time programmable (OTP) muisteissa ja loogisissa pireissä käytetty menetelmä. Sulake poltetaan pois isolla virralla/jännitteellä

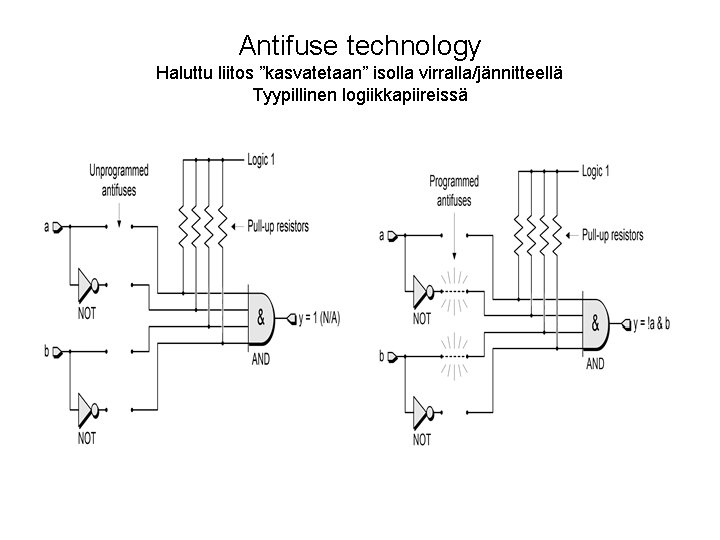

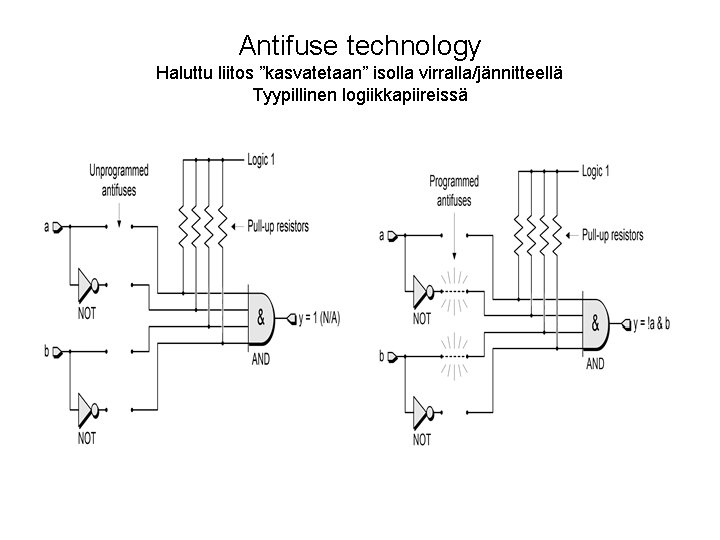

Antifuse technology Haluttu liitos ”kasvatetaan” isolla virralla/jännitteellä Tyypillinen logiikkapiireissä

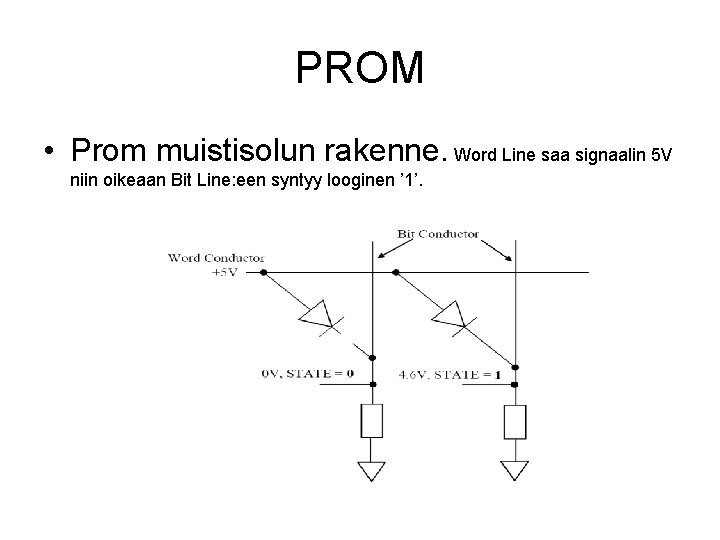

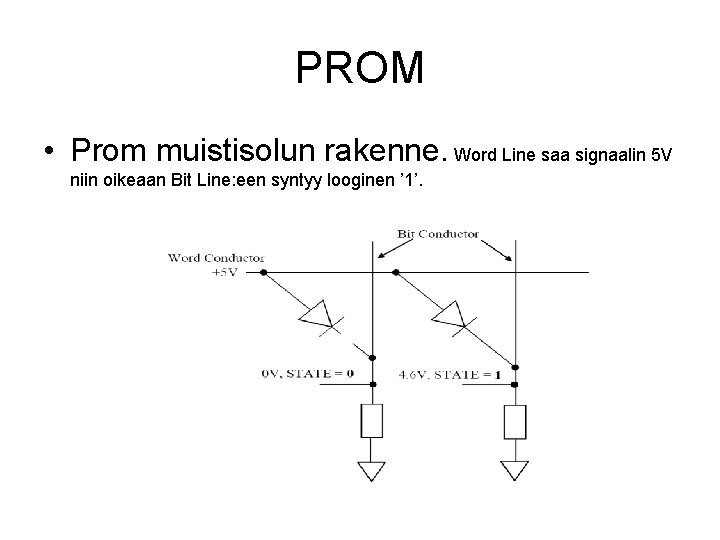

PROM • Prom muistisolun rakenne. Word Line saa signaalin 5 V niin oikeaan Bit Line: een syntyy looginen ’ 1’.

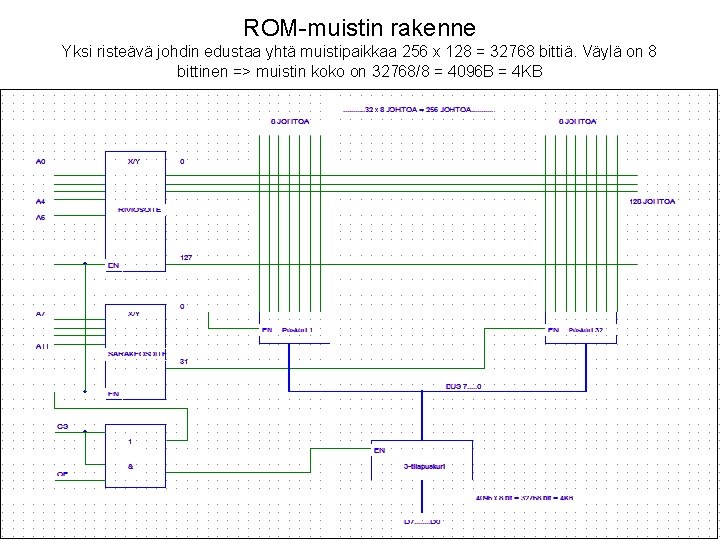

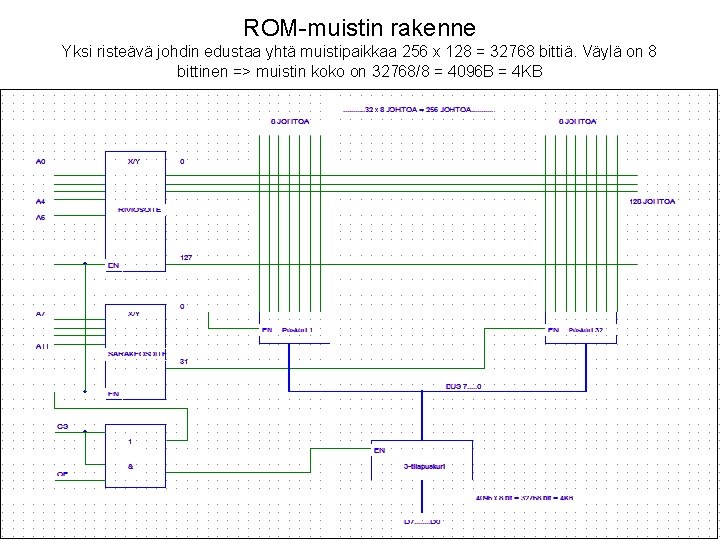

ROM-muistin rakenne Yksi risteävä johdin edustaa yhtä muistipaikkaa 256 x 128 = 32768 bittiä. Väylä on 8 bittinen => muistin koko on 32768/8 = 4096 B = 4 KB

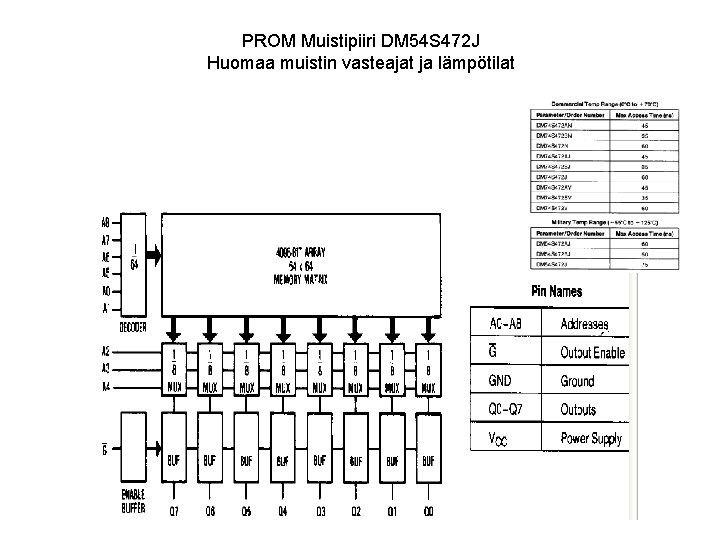

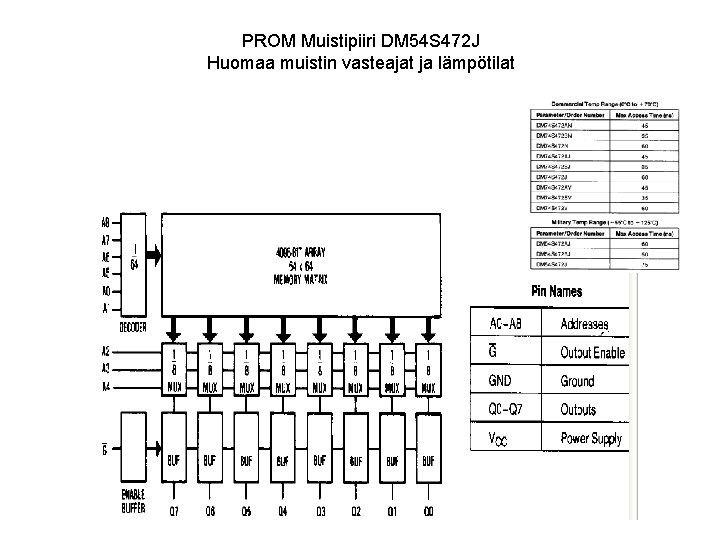

PROM Muistipiiri DM 54 S 472 J Huomaa muistin vasteajat ja lämpötilat

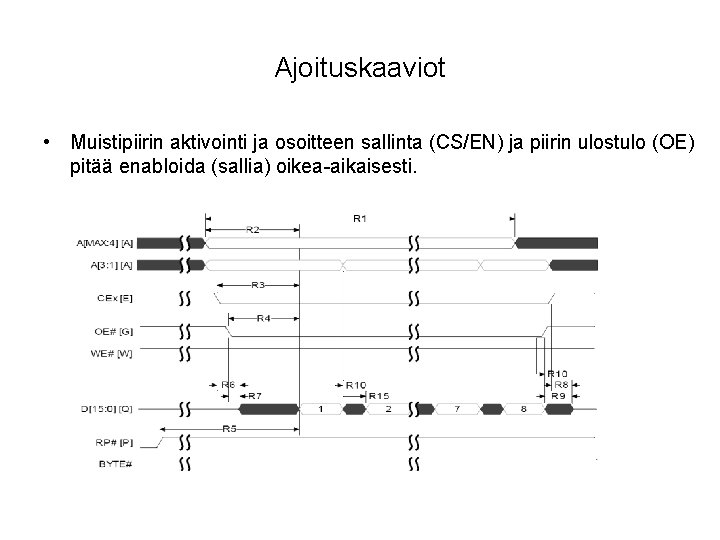

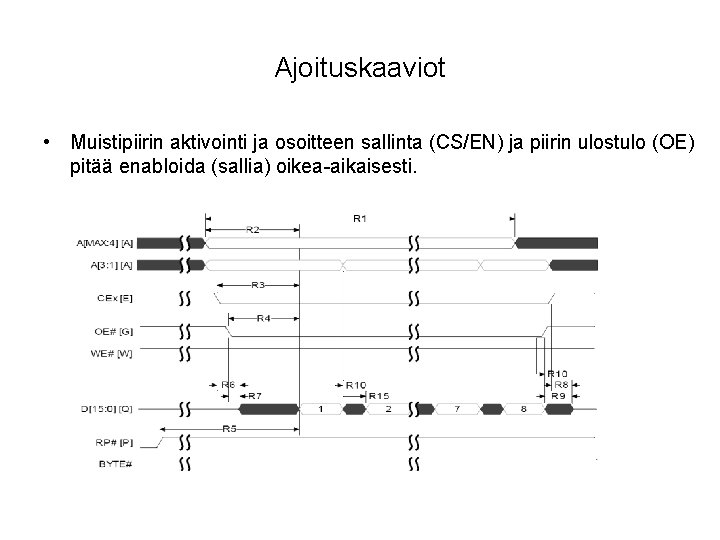

Ajoituskaaviot • Muistipiirin aktivointi ja osoitteen sallinta (CS/EN) ja piirin ulostulo (OE) pitää enabloida (sallia) oikea-aikaisesti.

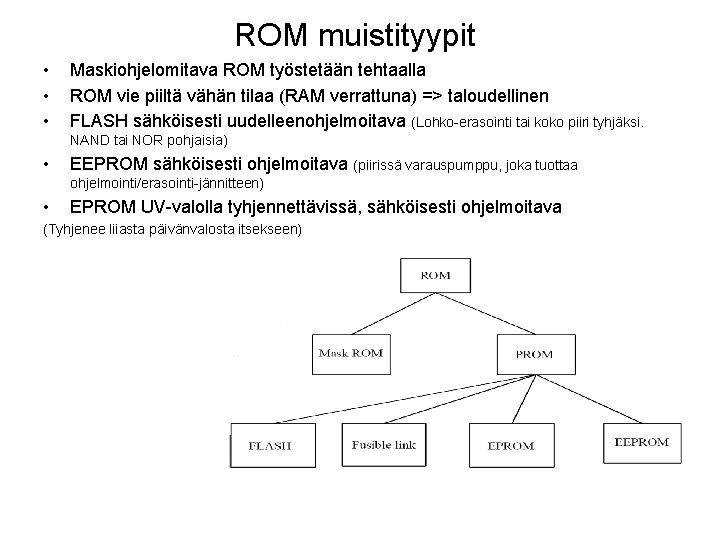

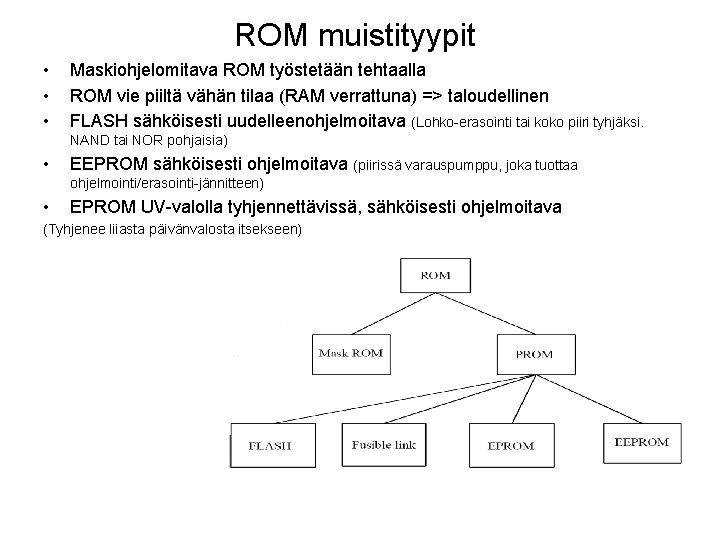

ROM muistityypit • • • Maskiohjelomitava ROM työstetään tehtaalla ROM vie piiltä vähän tilaa (RAM verrattuna) => taloudellinen FLASH sähköisesti uudelleenohjelmoitava (Lohko-erasointi tai koko piiri tyhjäksi. NAND tai NOR pohjaisia) • EEPROM sähköisesti ohjelmoitava (piirissä varauspumppu, joka tuottaa ohjelmointi/erasointi-jännitteen) • EPROM UV-valolla tyhjennettävissä, sähköisesti ohjelmoitava (Tyhjenee liiasta päivänvalosta itsekseen)

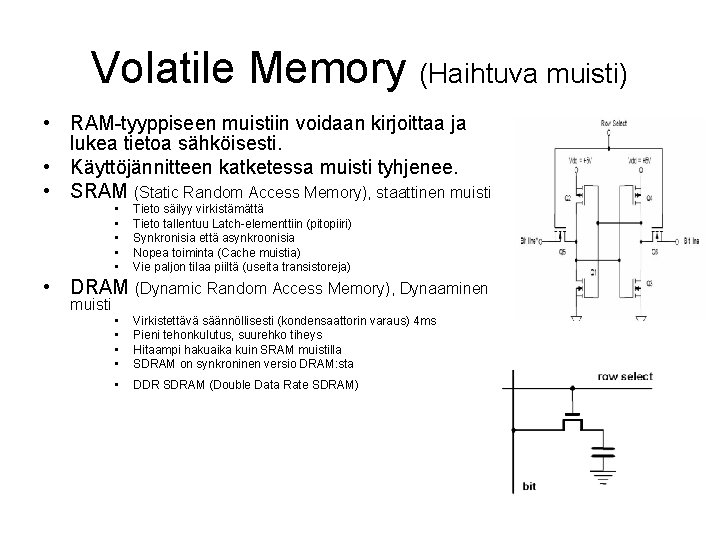

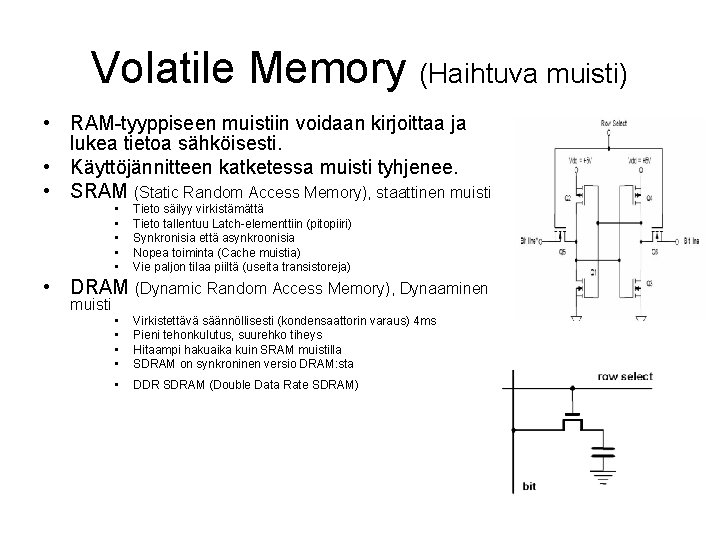

Volatile Memory (Haihtuva muisti) • RAM-tyyppiseen muistiin voidaan kirjoittaa ja lukea tietoa sähköisesti. • Käyttöjännitteen katketessa muisti tyhjenee. • SRAM (Static Random Access Memory), staattinen muisti • • • Tieto säilyy virkistämättä Tieto tallentuu Latch-elementtiin (pitopiiri) Synkronisia että asynkroonisia Nopea toiminta (Cache muistia) Vie paljon tilaa piiltä (useita transistoreja) • DRAM (Dynamic Random Access Memory), Dynaaminen muisti • • Virkistettävä säännöllisesti (kondensaattorin varaus) 4 ms Pieni tehonkulutus, suurehko tiheys Hitaampi hakuaika kuin SRAM muistilla SDRAM on synkroninen versio DRAM: sta • DDR SDRAM (Double Data Rate SDRAM)

Uudet muistityypit • Fe. Ram (Ferrosähköiset muistipiirit) • • • Haihtumaton muisti, Pieni tehonkulutus Noin 1000 kertaa FLASH. a nopeampaa (datan kirjoitus) Hyvä ohjelmoitavuus, ohjelmointi/tyhjennys sähköisesti Halpa • MRAM (Magnetic RAM) • • • haihtumaton muisti, ohjelmointi/tyhjennys sähköisesti korkea hakunopeus, suuri tiheys, pitkä elinikä, matala tehonkulutus ja • hyvä säteilynkestävyys

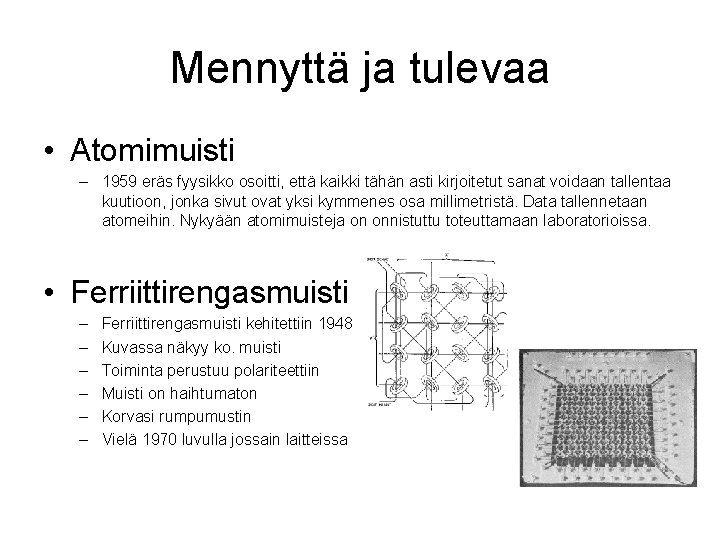

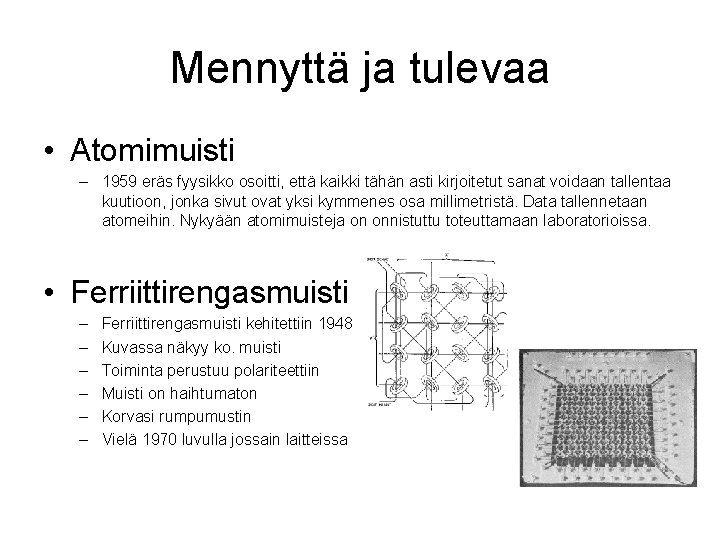

Mennyttä ja tulevaa • Atomimuisti – 1959 eräs fyysikko osoitti, että kaikki tähän asti kirjoitetut sanat voidaan tallentaa kuutioon, jonka sivut ovat yksi kymmenes osa millimetristä. Data tallennetaan atomeihin. Nykyään atomimuisteja on onnistuttu toteuttamaan laboratorioissa. • Ferriittirengasmuisti – – – Ferriittirengasmuisti kehitettiin 1948 Kuvassa näkyy ko. muisti Toiminta perustuu polariteettiin Muisti on haihtumaton Korvasi rumpumustin Vielä 1970 luvulla jossain laitteissa

Mikrokontrollerin perusliitännät • Sarjaportti – RS-232 tiedonsiirto on diffrentiaalista +/- 12 V. Mikrokontrollerin käyttöjännite on tyypillisesti 5 V, 3, 3 V tai joku muu. Liitettäessä kontrolleri esim. tietokoneen sarjaporttiin täytyy jännitetasot sovittaa oikeiksi. UART-piirit (Universal Asynchronous Receiver Transmitter) hoitavat asian helposti (MAX 232) • USB-portti – Usein kontrollerissa USB-kommunikointi hoidetaan erillisillä piireillä • JTAG-portti – Lähes kaikissa nykyisissä kontrollereissa ja ohjelmoitavissa piireissä on Boundary-Scan-liitäntä ohjelman latausta ja/tai systeemin testausta varten. USBsignalointi konvertoidaan usein esim. JTAG-pinneihin • IIC-väylä – Piirikortin sisäinen (sarja) väylä, jolla ohjataan esim. AD-muuntimia, säädettäviä vahvistimia, digitaalisia potentiometrejä ym. laitteita. Väylän jokaisella piirillä on oma osoite, johon isäntä osoittaa datan siirron yhteydessä

Arkkitehtuurit • SISD-arkkitehturi (Single Instruction Single Data) on tyypillisin ratkaisu • MIMD (Multiple Instruction. Multiple Data) tarkoittaa rinakkaisprosessointia ja se vahvasti on tulossa joka paikkaan • SISD-prosessorien käsky ja data-väylät voivat olla rakenteellisesti erilaisia. Näitä väyläarkkitehtuutreita kutsutaan Von Neumanin tai Harvardin arkkitehtuureiksi. • Von Neumanin arkkitehtuurissa (yleinen) data ja käskyt sijaitsevat samassa muistissa • Harvard-arkkitehtuurissa data- ja käskymuisti ovat erillisiä. Uuden käskyn haku ja datan tallennus voivat olla samanaikaisia operaatioita. Signaaliprosessorit käyttävät tätä arkkitehtuuria.

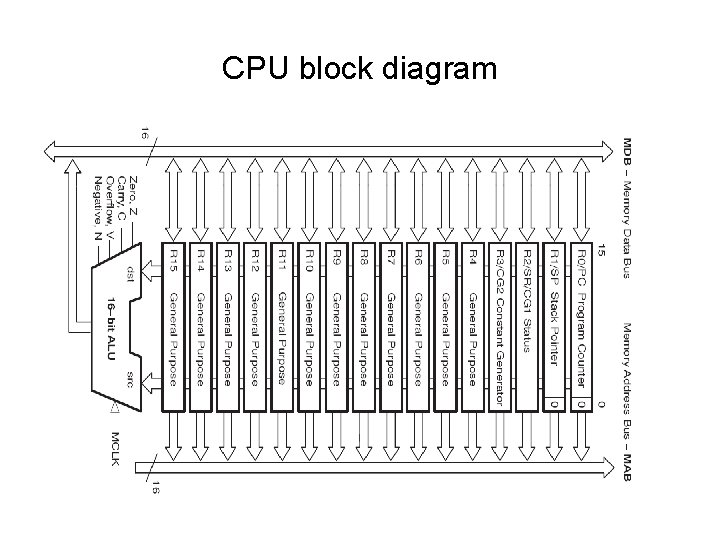

Prosessorin rakenne ja toiminta • Rekisterit: Rekisterit jaetaan yleiskäyttöisiin ja erikoisfunktiorekistereihin. Yleiskäyttöiseen rekisteriin ohjelmoija voi ladata esim muuttujien arvoja. Rekisteristä haettu muuttuja nopeuttaa ohjelman suoritusta merkittävästi verrattuna tilanteeseen, että muuttujan arvo haetaan ulkopuolisesta muistista. SFR (special Function Register) sisältää prosessorin oheispiirien ohjauskoodit. Esimerkiksi AD-muunnosta tehtäessä täytyy valita AD-kanava, josta muunnos tehdään. Tällöin kyseiseen rekisteriin tulee kirjoittaa oikeanlainen bitti-koodi. • Väylät: Prosessorin sisäinen osoite- ja dataväylä on tyypillisesti 32 tai 16 -bittinen. Pienempiä väyliä löytyy mikrokontrollereista. Väylät voidaan tuoda prosessorista piirikortille. Piirikortilla väylä voi olla kapeampi kuin prosessorin sisäinen väylä. • Aritmeettislooginen yksikkö (ALU): ALU hoitaa aritmeettiset, loogiset ja päättelyoperaatiot. Esimerkiksi kahden luvun yhteenlaskussa ALU: n tulee molempien lukujen arvot rekistereistä. ALU: n ohjaussignaali kertoo, että luvut pitää laskea yhteen. Tulos palautetaan rekisteriin. Joissain prosessoreissa AKKU on yleiskäyttöisin rekisteri, jota voidaan operoida kaikista monipulisimmin.

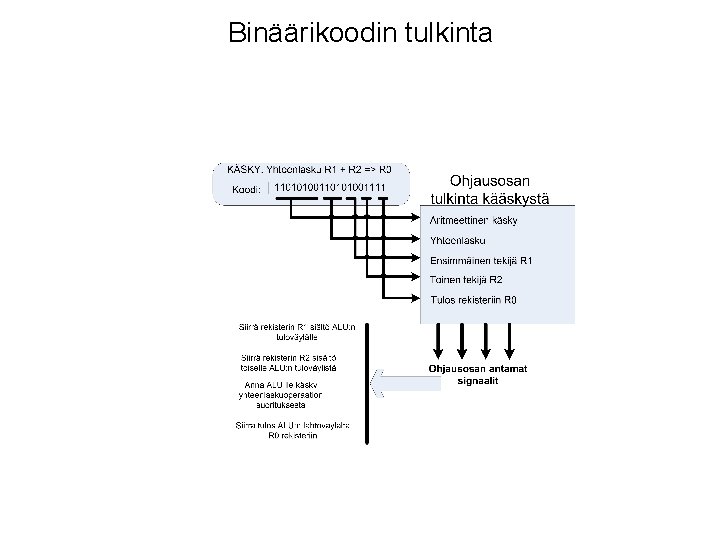

Ohjausosa • • Sisäinen tilakonen huolehtii muistien, ALU: n, väylien ja muiden oheislaitteiden ohjauksesta. Ohjausosan tunnistamat käskyt määrittävät prosessorin käskykannan Ohjausosan logiikka voidaan toteuttaa langoitettuna (hard-wire) tai muistipiirille toteutettuna logiikkana (micro code) => käskykantaa voidaan muuttaa Program counter sisältää aina seuraavaksi muistista haettavan käskyn osoitteen (Ohjelmalaskurin koko määrää ohjelmalohkon suurimman koon 32 b => 4 GB, 16 b =>64 KB…). • Käskyä haettaessa: Ohjelmalaskurin sisältö siirtyy osoiterekisteriin => ohjausosa käskee lukusignaalin avulla muistia etsimään annetun osoitteen sisällön ja siirtämään sen dataväylälle => muisti ilmoittaa ready-signaalilla ohjausosalle, että data on käytettävissä => ohjausosa siirtää tiedon datarekisteriin => ohjausosa kasvattaa ohjelmalaskurin arvoa, joka osoittaa sitten seuraavaksi haettavaan käskyyn Memory Register PC SR = Status Register

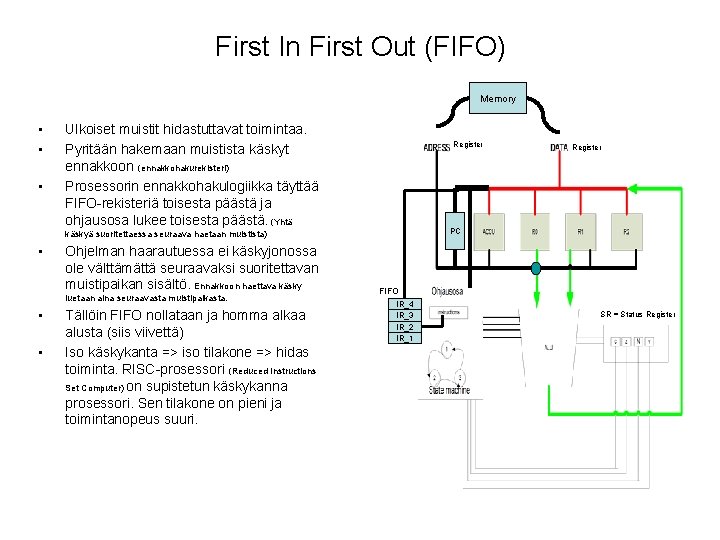

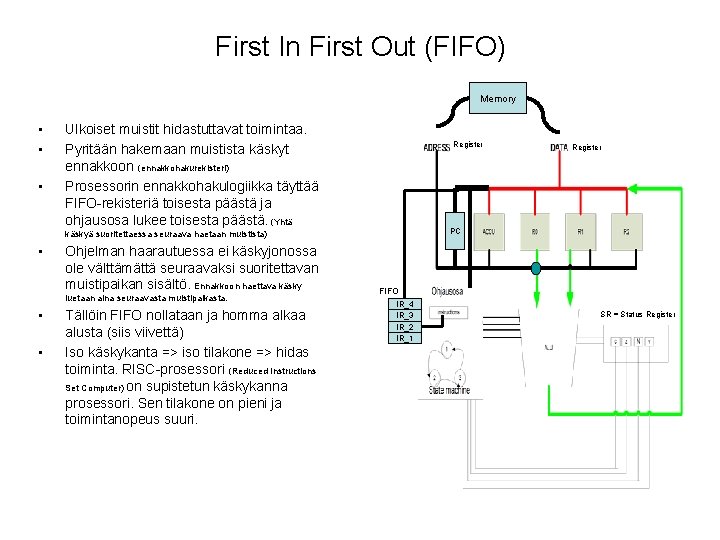

First In First Out (FIFO) Memory • • • Ulkoiset muistit hidastuttavat toimintaa. Pyritään hakemaan muistista käskyt ennakkoon (ennakkohakurekisteri) Prosessorin ennakkohakulogiikka täyttää FIFO-rekisteriä toisesta päästä ja ohjausosa lukee toisesta päästä. (Yhtä Register PC käskyä suoritettaessa seuraava haetaan muistista) • Ohjelman haarautuessa ei käskyjonossa ole välttämättä seuraavaksi suoritettavan muistipaikan sisältö. Ennakkoon haettava käsky luetaan aina seuraavasta muistipaikasta. • • Tällöin FIFO nollataan ja homma alkaa alusta (siis viivettä) Iso käskykanta => iso tilakone => hidas toiminta. RISC-prosessori (Reduced Instructions Set Computer) on supistetun käskykanna prosessori. Sen tilakone on pieni ja toimintanopeus suuri. Register FIFO IR_4 IR_3 IR_2 IR_1 SR = Status Register

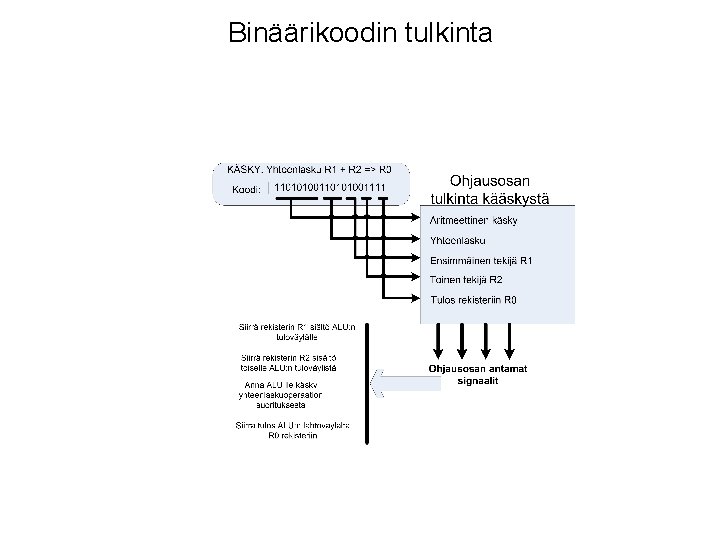

Binäärikoodin tulkinta

Boundary-Scan Basic (JTAG) Basic Principle and Device Architecture Board Level Implementation Applications BSDL language Design For Test Benefits & Drawbacks Additional Information

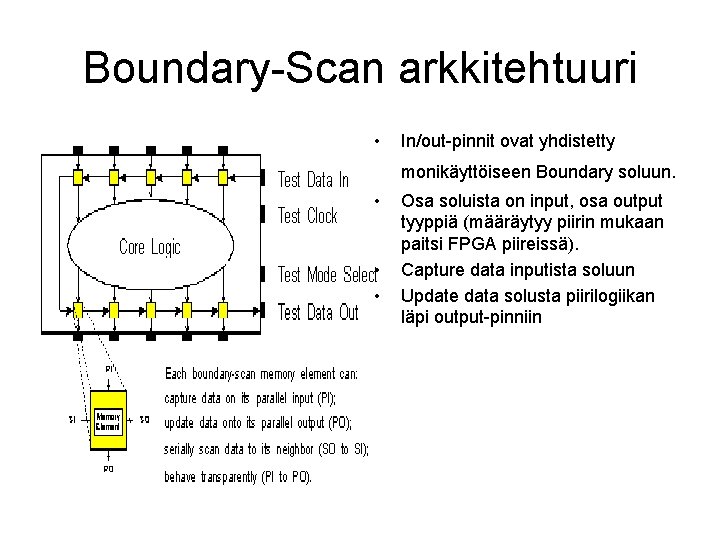

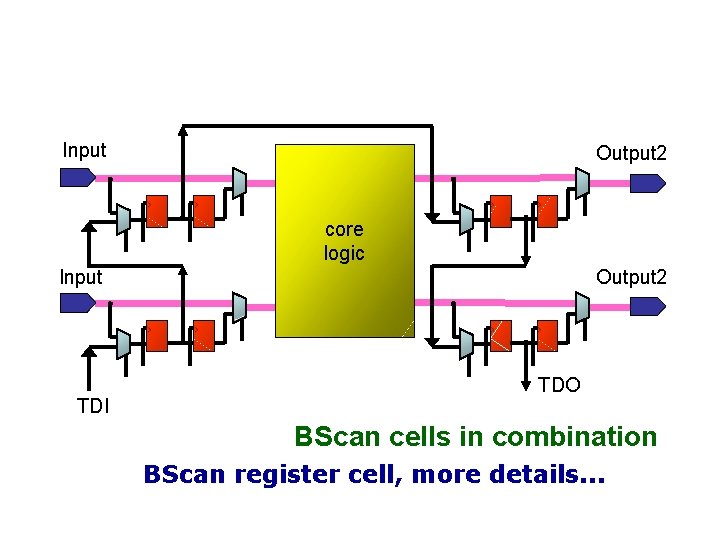

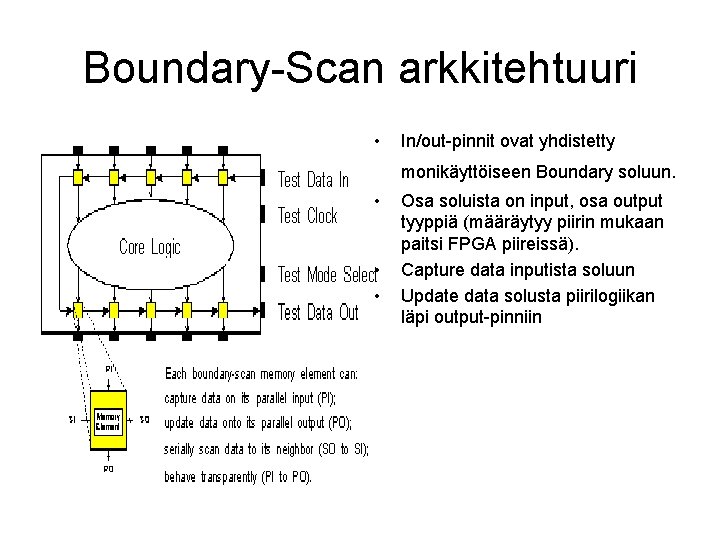

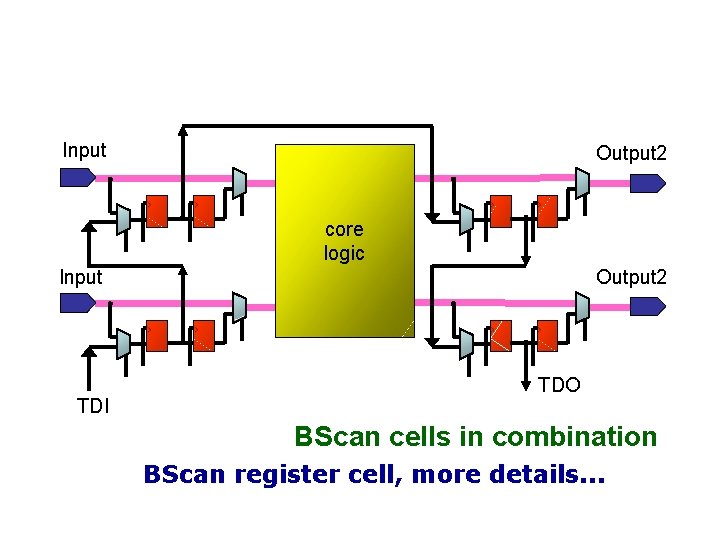

Boundary-Scan arkkitehtuuri • In/out-pinnit ovat yhdistetty monikäyttöiseen Boundary soluun. • • • Osa soluista on input, osa output tyyppiä (määräytyy piirin mukaan paitsi FPGA piireissä). Capture data inputista soluun Update data solusta piirilogiikan läpi output-pinniin

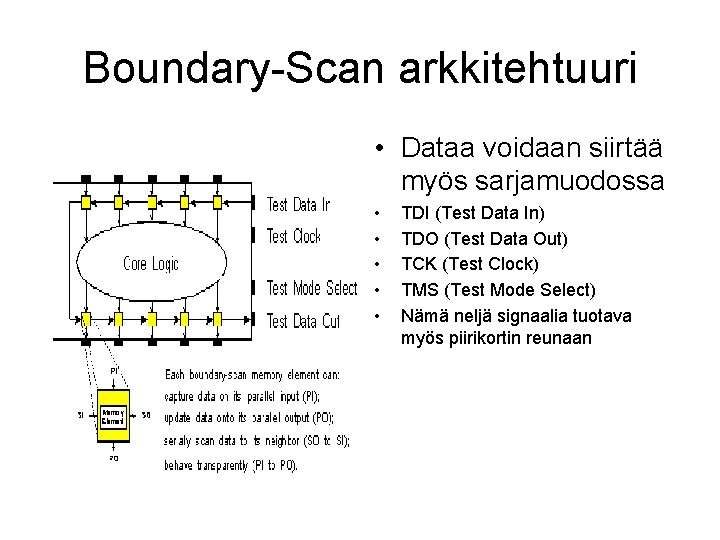

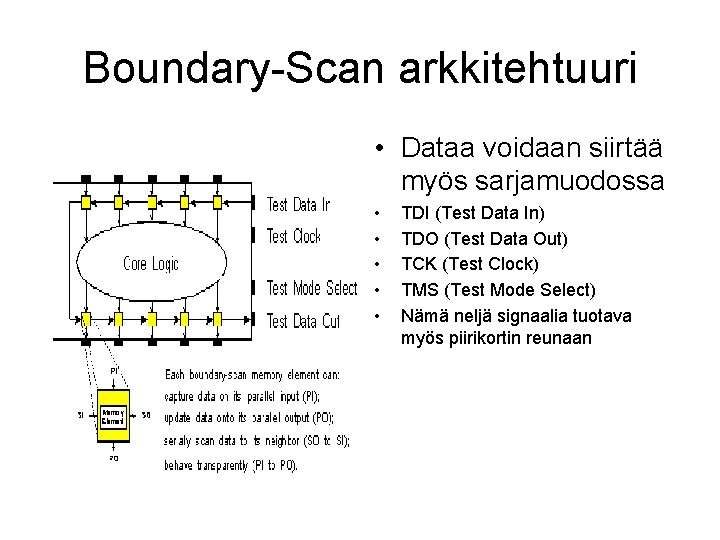

Boundary-Scan arkkitehtuuri • Dataa voidaan siirtää myös sarjamuodossa • • • TDI (Test Data In) TDO (Test Data Out) TCK (Test Clock) TMS (Test Mode Select) Nämä neljä signaalia tuotava myös piirikortin reunaan

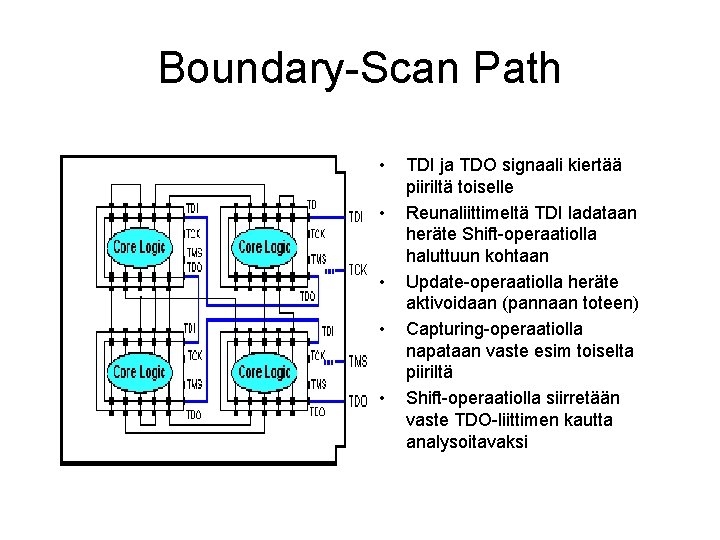

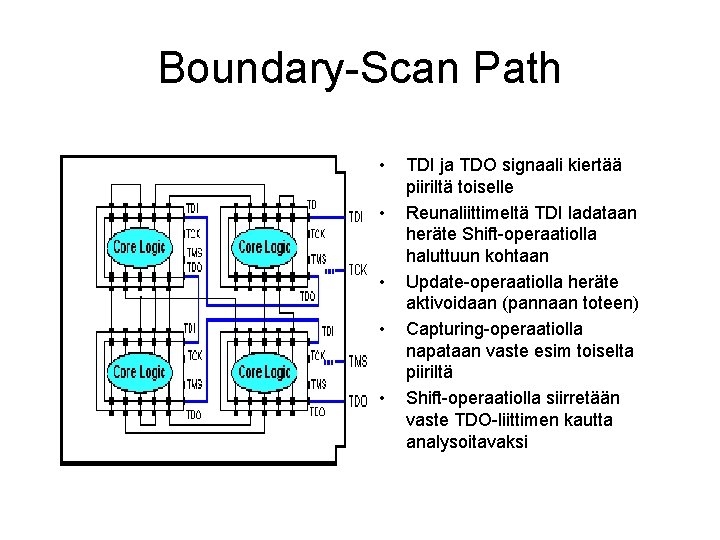

Boundary-Scan Path • • • TDI ja TDO signaali kiertää piiriltä toiselle Reunaliittimeltä TDI ladataan heräte Shift-operaatiolla haluttuun kohtaan Update-operaatiolla heräte aktivoidaan (pannaan toteen) Capturing-operaatiolla napataan vaste esim toiselta piiriltä Shift-operaatiolla siirretään vaste TDO-liittimen kautta analysoitavaksi

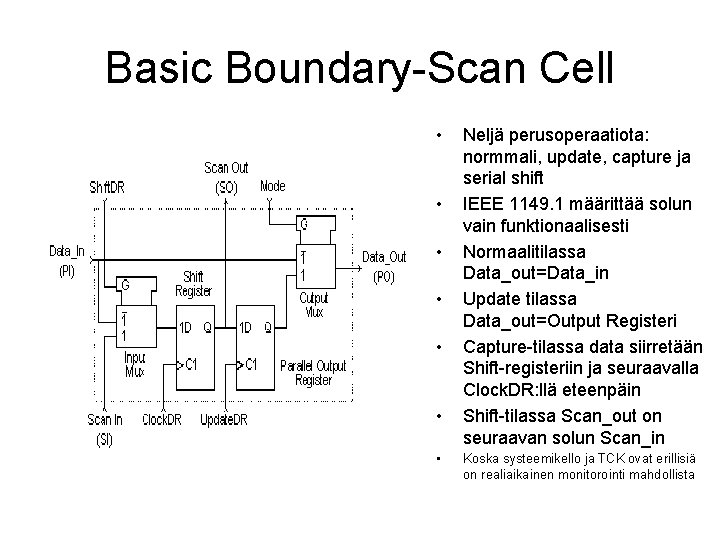

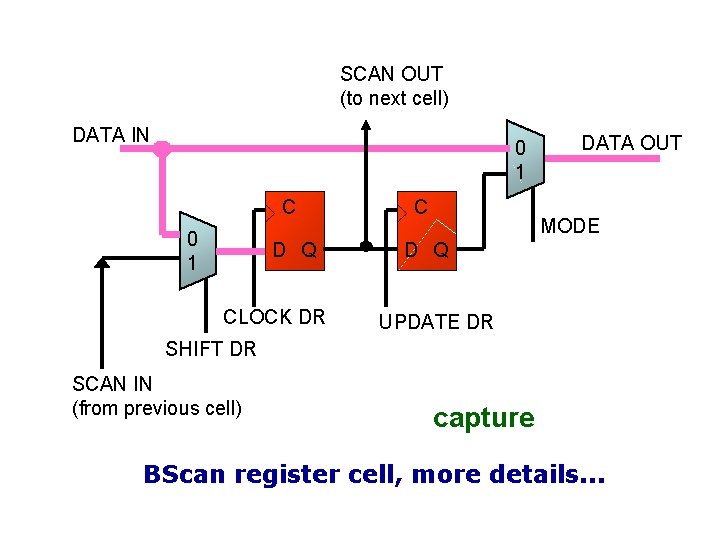

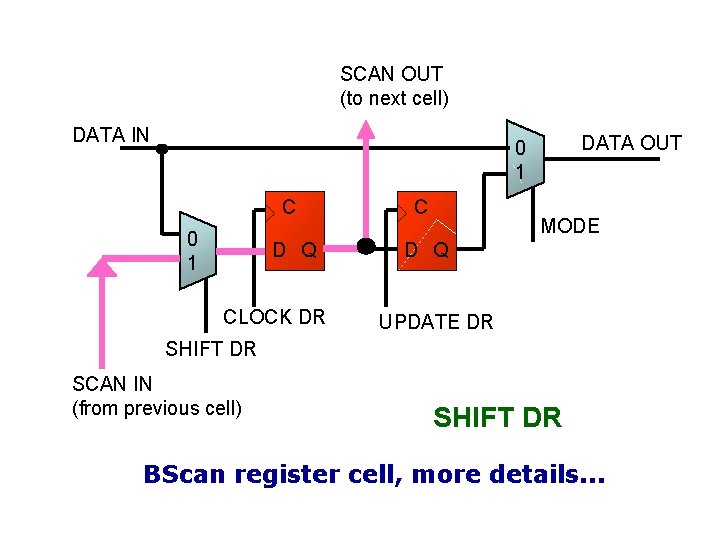

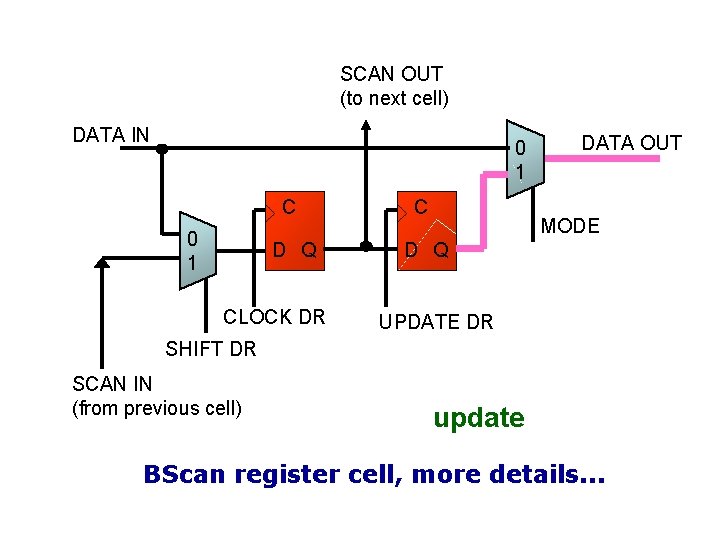

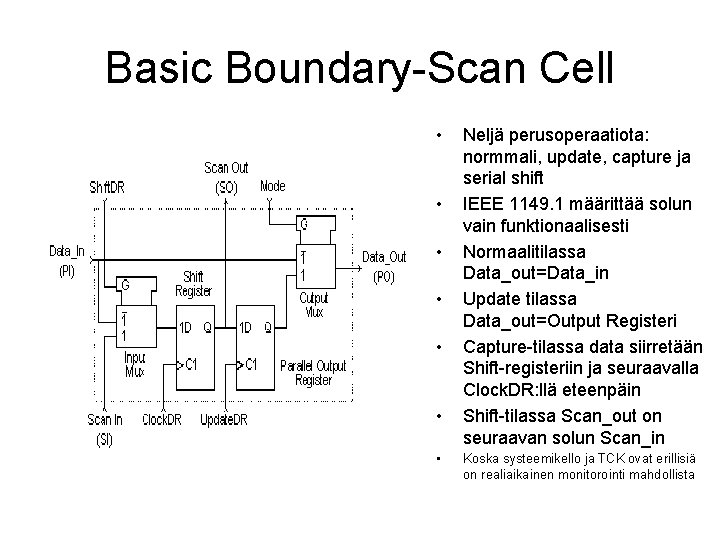

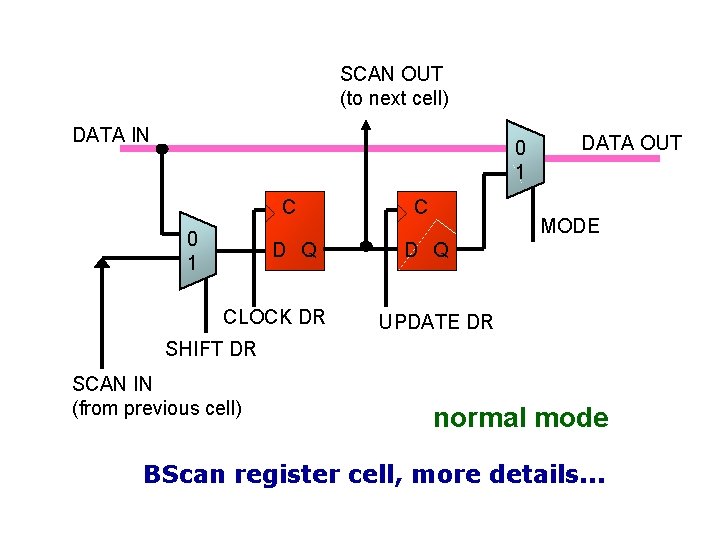

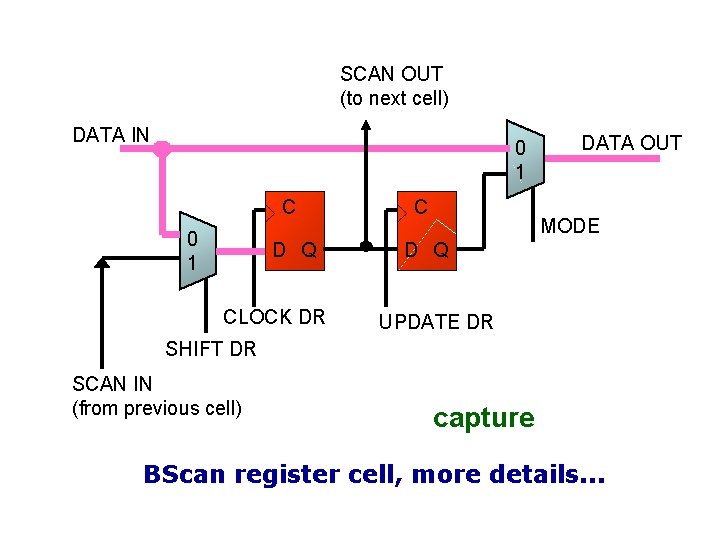

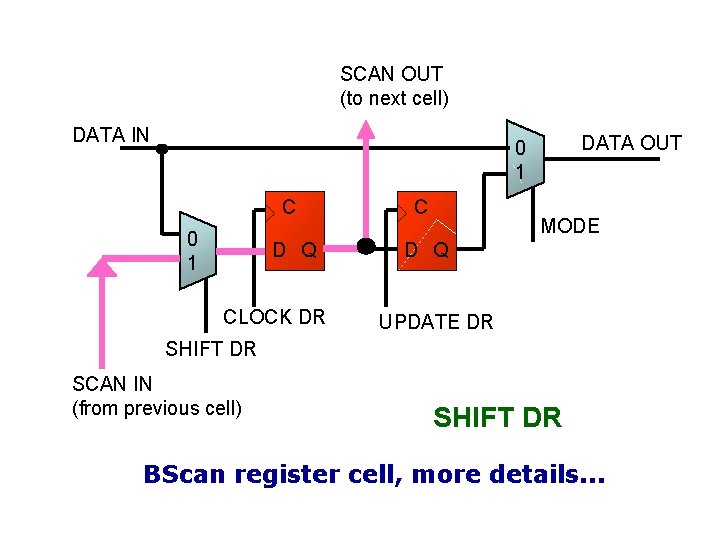

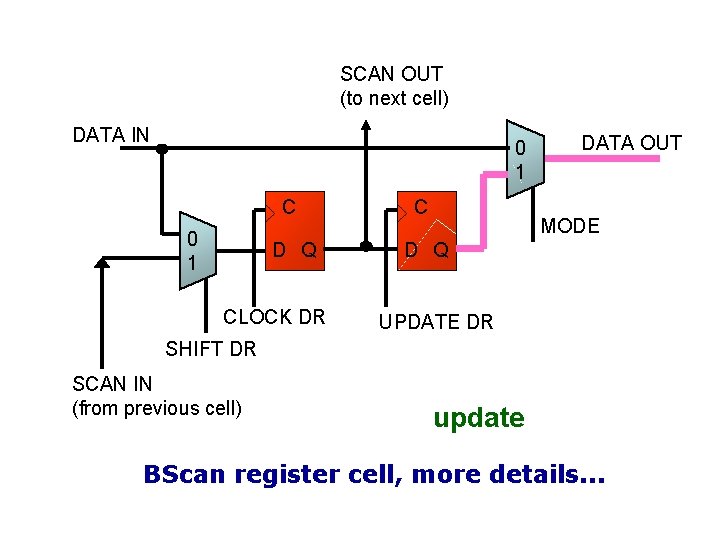

Basic Boundary-Scan Cell • • Neljä perusoperaatiota: normmali, update, capture ja serial shift IEEE 1149. 1 määrittää solun vain funktionaalisesti Normaalitilassa Data_out=Data_in Update tilassa Data_out=Output Registeri Capture-tilassa data siirretään Shift-registeriin ja seuraavalla Clock. DR: llä eteenpäin Shift-tilassa Scan_out on seuraavan solun Scan_in Koska systeemikello ja TCK ovat erillisiä on realiaikainen monitorointi mahdollista

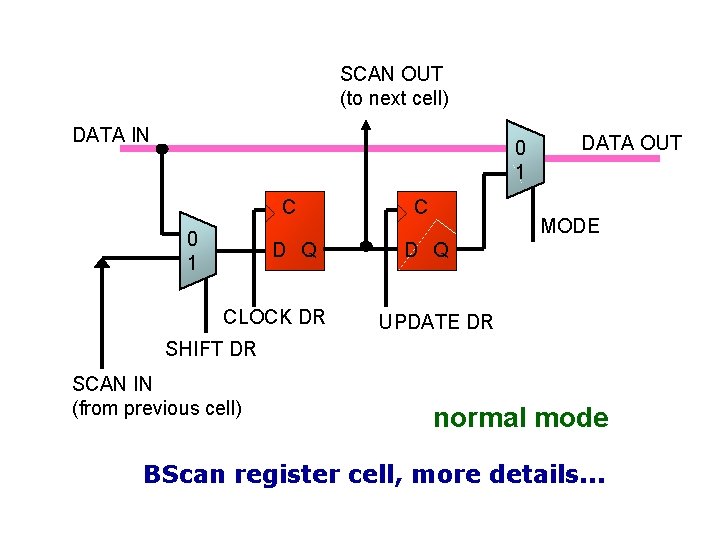

SCAN OUT (to next cell) DATA IN 0 1 C C D Q CLOCK DR DATA OUT MODE UPDATE DR SHIFT DR SCAN IN (from previous cell) normal mode BScan register cell, more details. . .

SCAN OUT (to next cell) DATA IN 0 1 C C D Q CLOCK DR DATA OUT MODE UPDATE DR SHIFT DR SCAN IN (from previous cell) capture BScan register cell, more details. . .

SCAN OUT (to next cell) DATA IN DATA OUT 0 1 C C D Q CLOCK DR MODE UPDATE DR SHIFT DR SCAN IN (from previous cell) SHIFT DR BScan register cell, more details. . .

SCAN OUT (to next cell) DATA IN 0 1 C C D Q CLOCK DR DATA OUT MODE UPDATE DR SHIFT DR SCAN IN (from previous cell) update BScan register cell, more details. . .

Input Output 2 core logic Input TDI Output 2 TDO BScan cells in combination BScan register cell, more details. . .

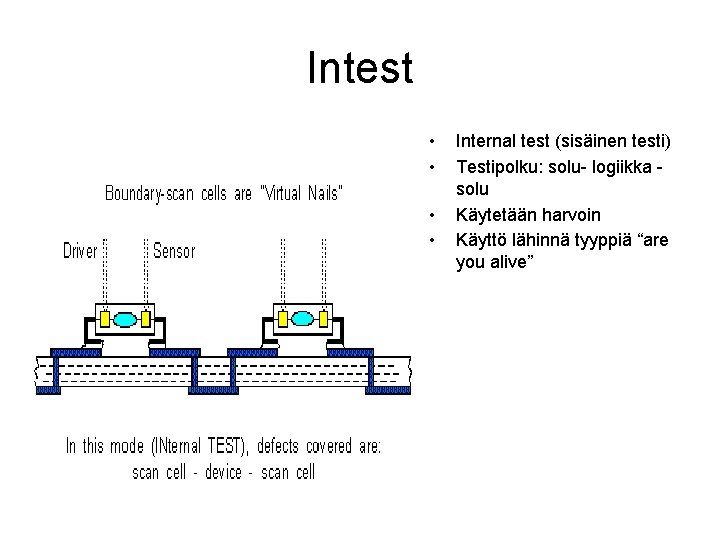

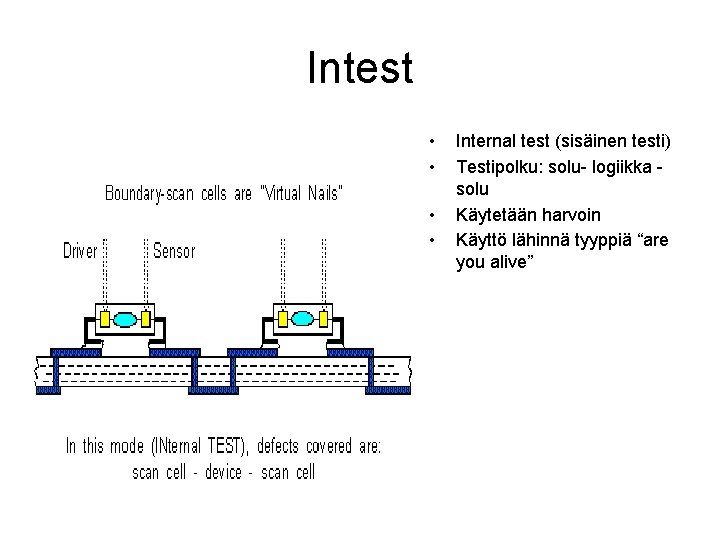

Intest • • Internal test (sisäinen testi) Testipolku: solu- logiikka solu Käytetään harvoin Käyttö lähinnä tyyppiä “are you alive”

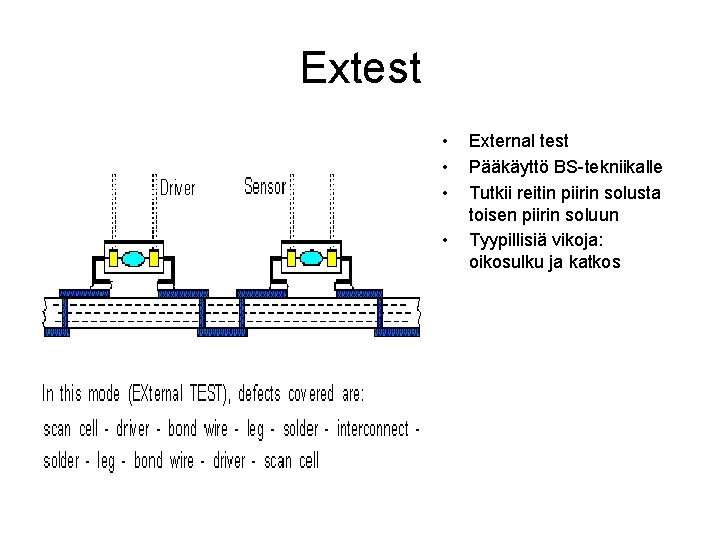

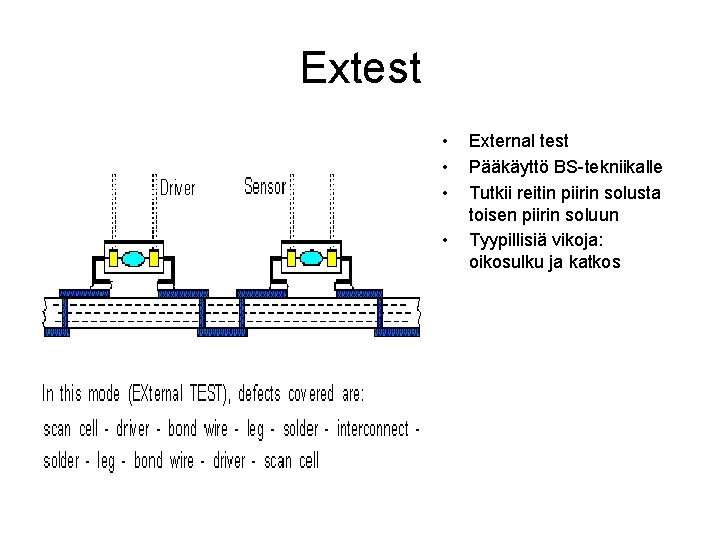

Extest • • External test Pääkäyttö BS-tekniikalle Tutkii reitin piirin solusta toisen piirin soluun Tyypillisiä vikoja: oikosulku ja katkos

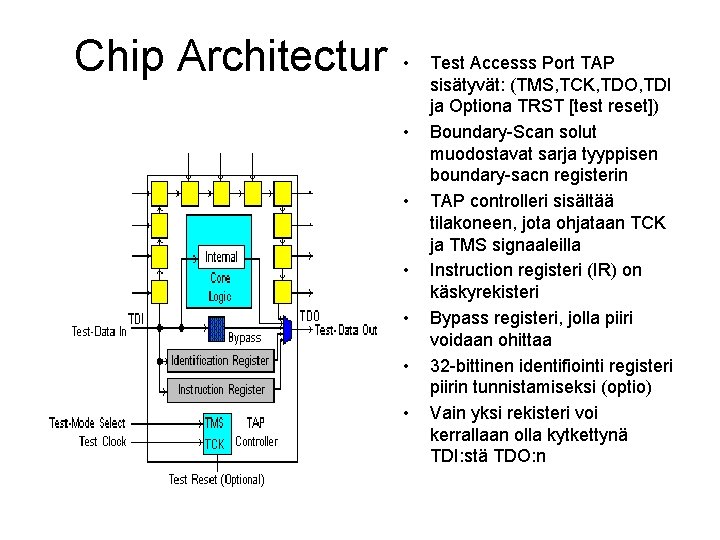

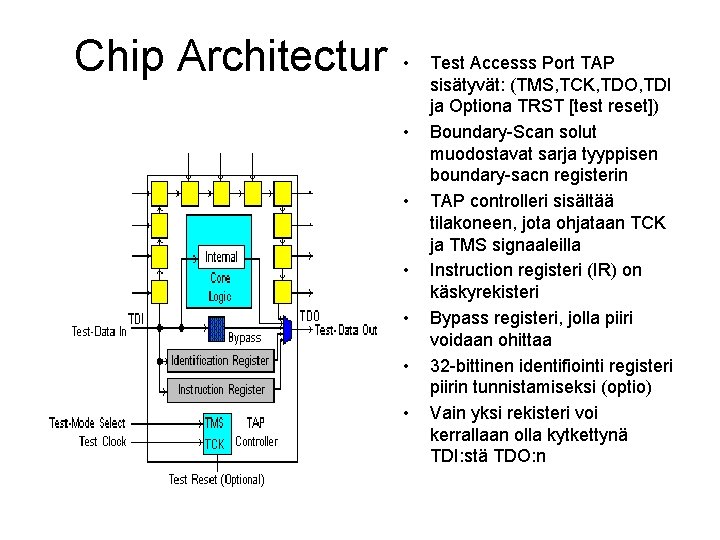

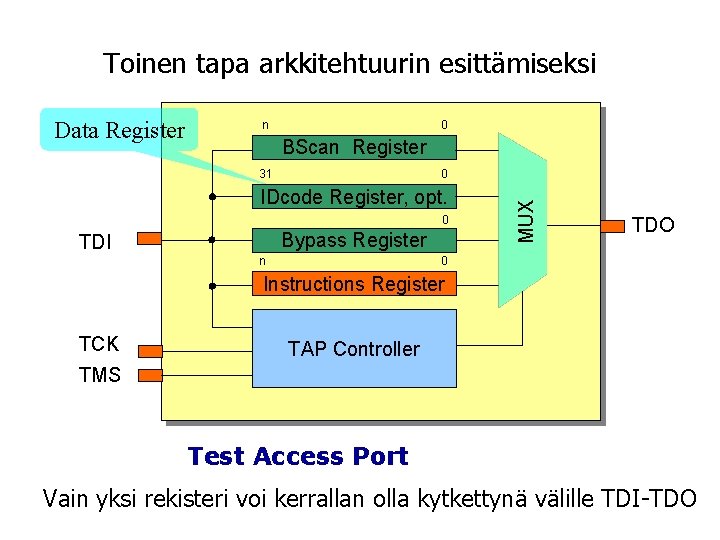

Chip Architectur • • Test Accesss Port TAP sisätyvät: (TMS, TCK, TDO, TDI ja Optiona TRST [test reset]) Boundary-Scan solut muodostavat sarja tyyppisen boundary-sacn registerin TAP controlleri sisältää tilakoneen, jota ohjataan TCK ja TMS signaaleilla Instruction registeri (IR) on käskyrekisteri Bypass registeri, jolla piiri voidaan ohittaa 32 -bittinen identifiointi registeri piirin tunnistamiseksi (optio) Vain yksi rekisteri voi kerrallaan olla kytkettynä TDI: stä TDO: n

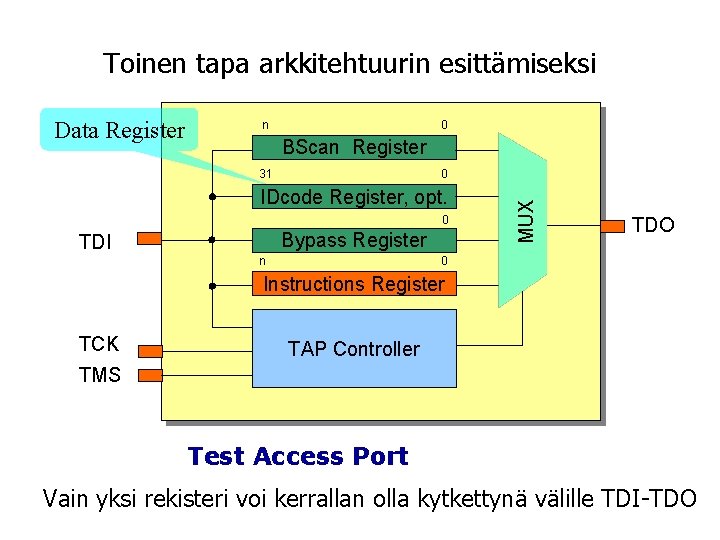

Toinen tapa arkkitehtuurin esittämiseksi n 0 BScan Register 31 0 IDcode Register, opt. 0 Bypass Register TDI n MUX Data Register TDO 0 Instructions Register TCK TAP Controller TMS Test Access Port Vain yksi rekisteri voi kerrallan olla kytkettynä välille TDI-TDO

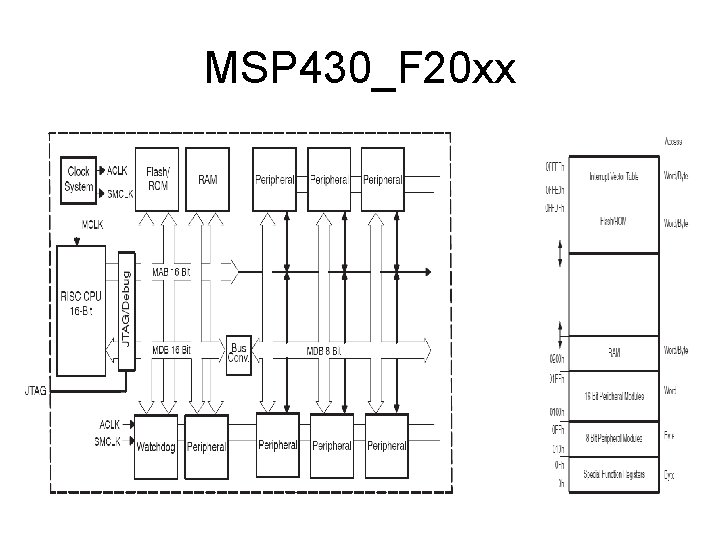

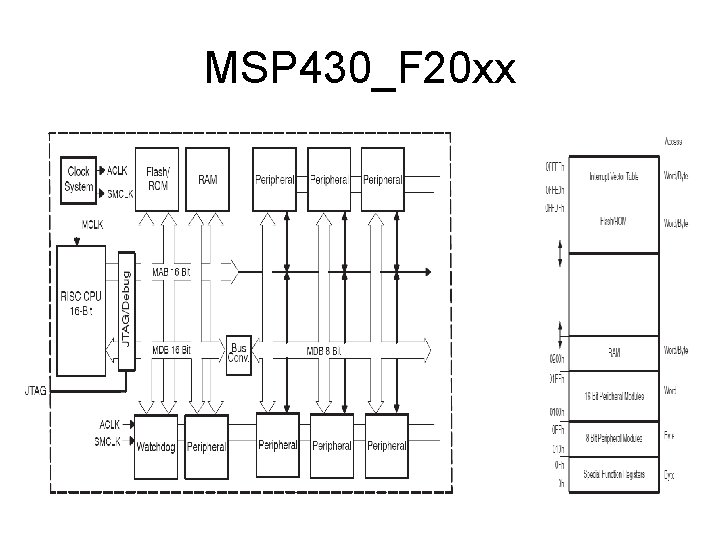

MSP 430_F 20 xx

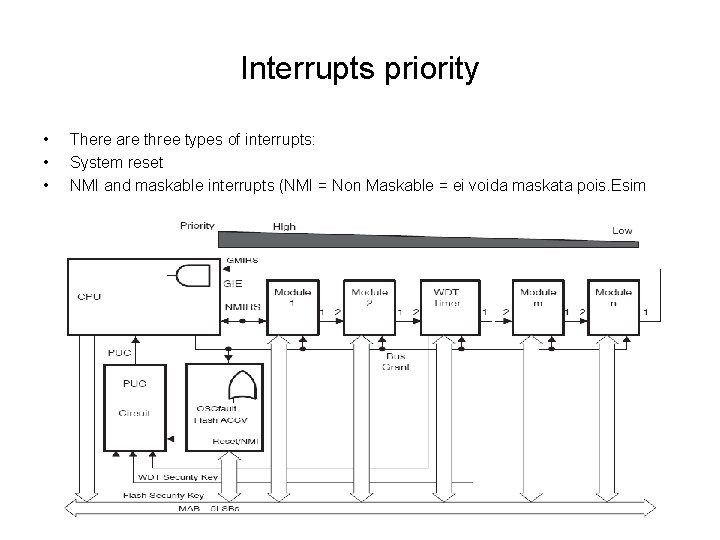

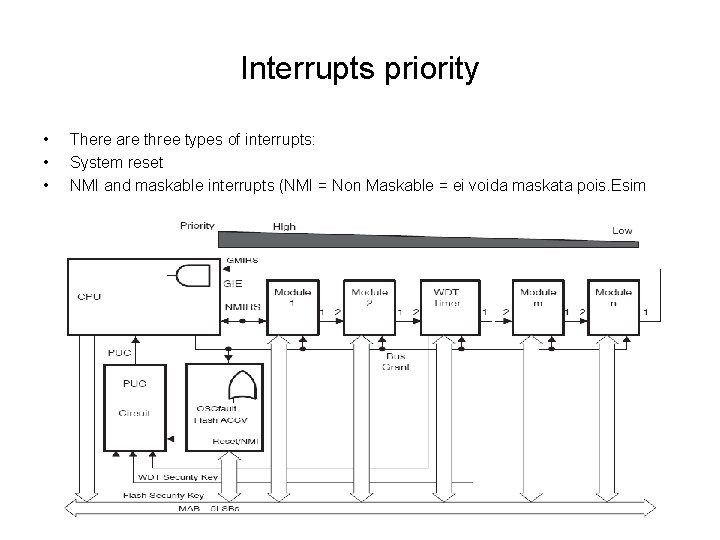

Interrupts priority • • • There are three types of interrupts: System reset NMI and maskable interrupts (NMI = Non Maskable = ei voida maskata pois. Esim vika muistissa tai oskillattorissa johtaa tähän)

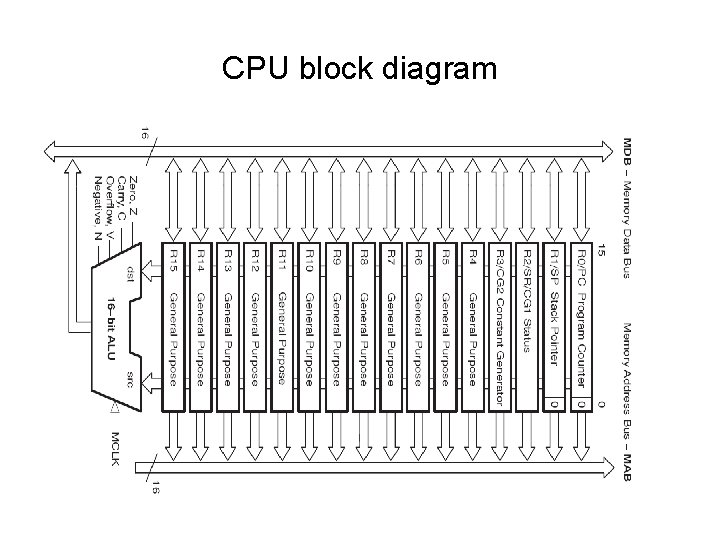

CPU block diagram

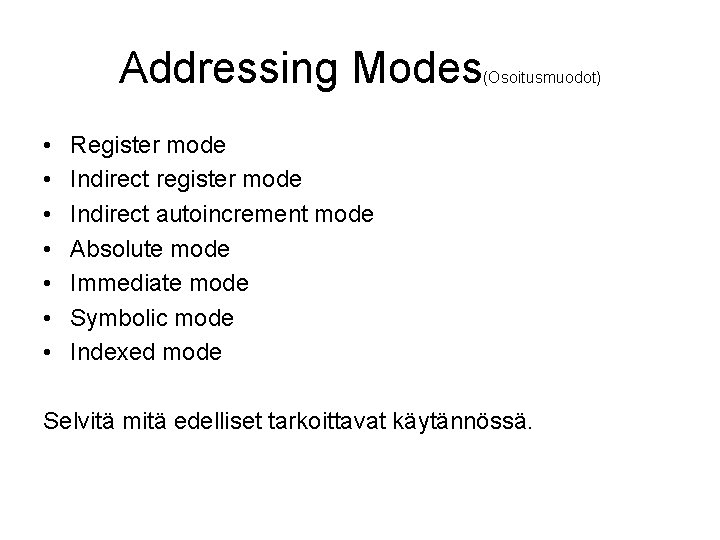

Addressing Modes • • (Osoitusmuodot) Register mode Indirect register mode Indirect autoincrement mode Absolute mode Immediate mode Symbolic mode Indexed mode Selvitä mitä edelliset tarkoittavat käytännössä.

Basic clock module operation • • Toimii ilman ulkoisia komponentteja Toimii kiteen kanssa (tarkka ajastus) Toimii resonaattorin kanssa Tukee pientä energian kulutusta • Perehdy kellopiirin muihin ominaisuuksiin

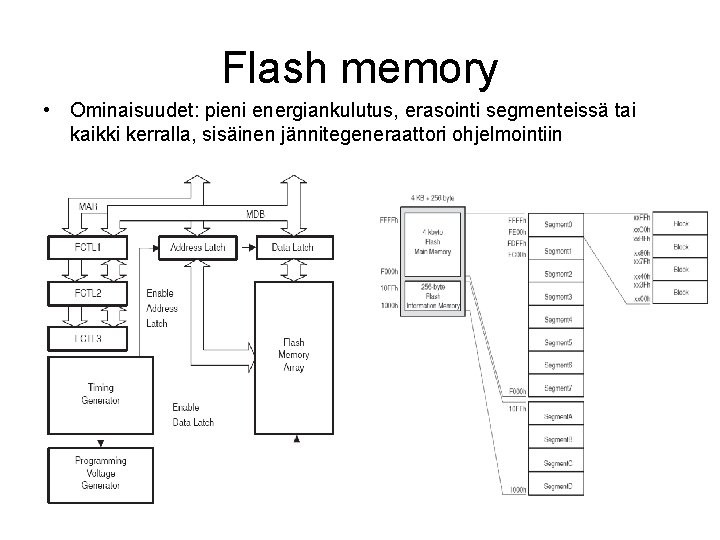

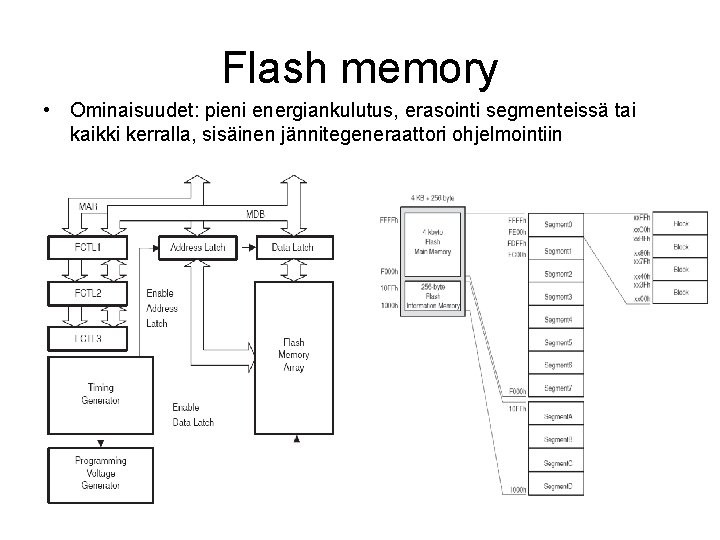

Flash memory • Ominaisuudet: pieni energiankulutus, erasointi segmenteissä tai kaikki kerralla, sisäinen jännitegeneraattori ohjelmointiin

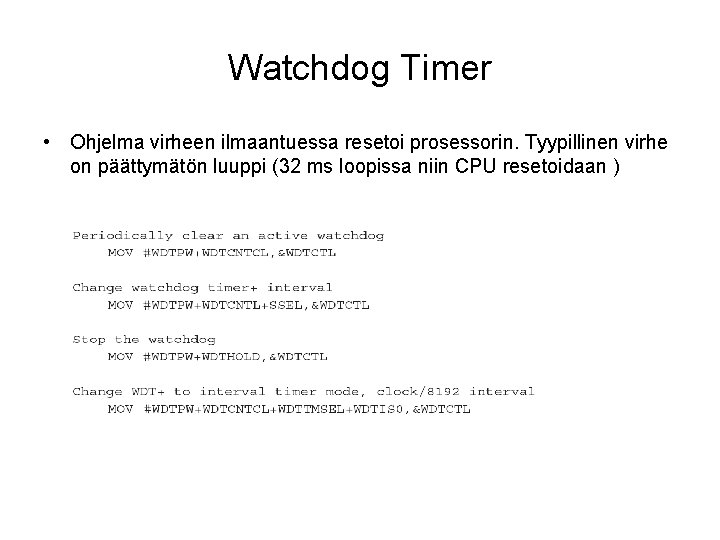

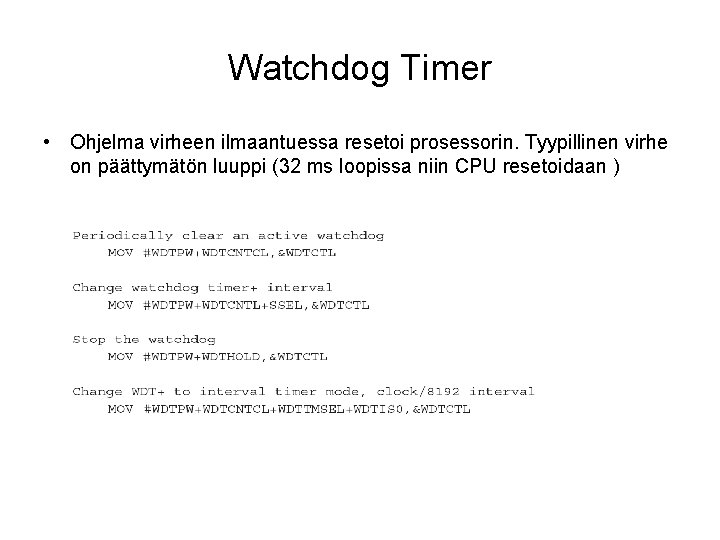

Watchdog Timer • Ohjelma virheen ilmaantuessa resetoi prosessorin. Tyypillinen virhe on päättymätön luuppi (32 ms loopissa niin CPU resetoidaan )

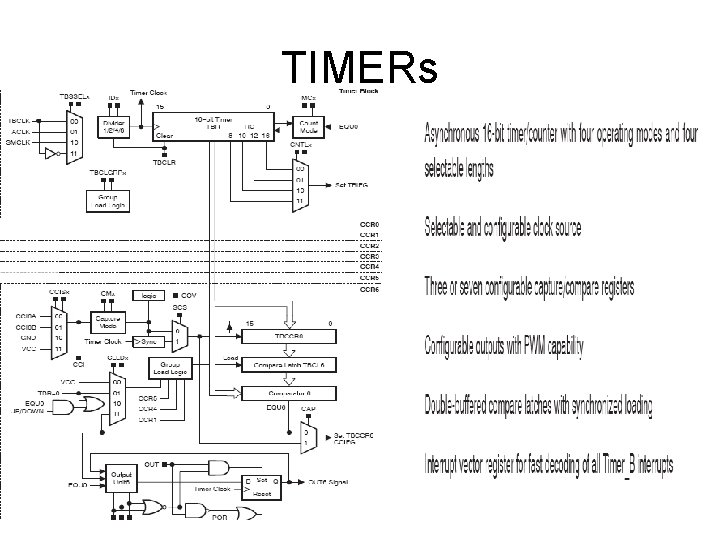

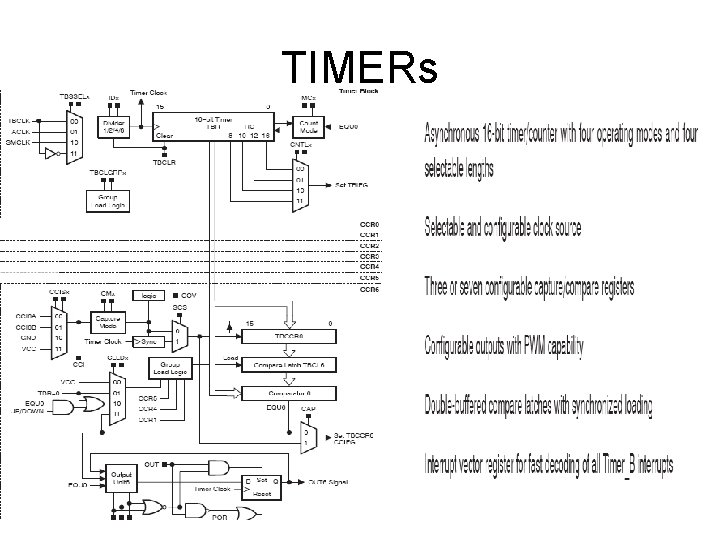

TIMERs

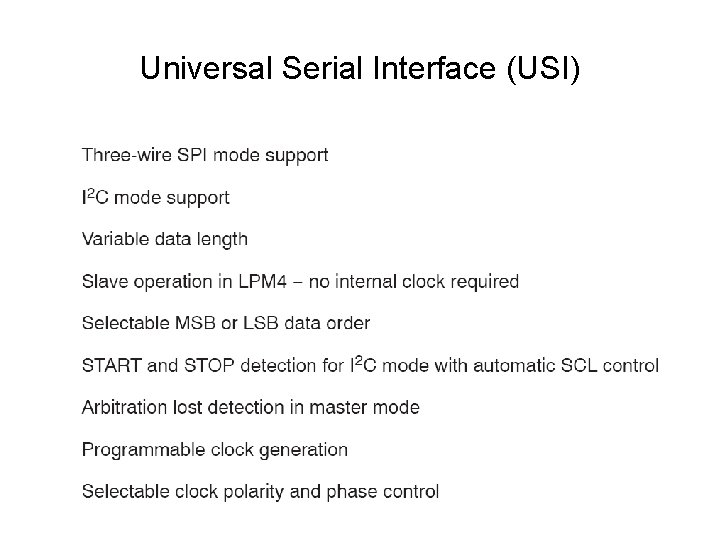

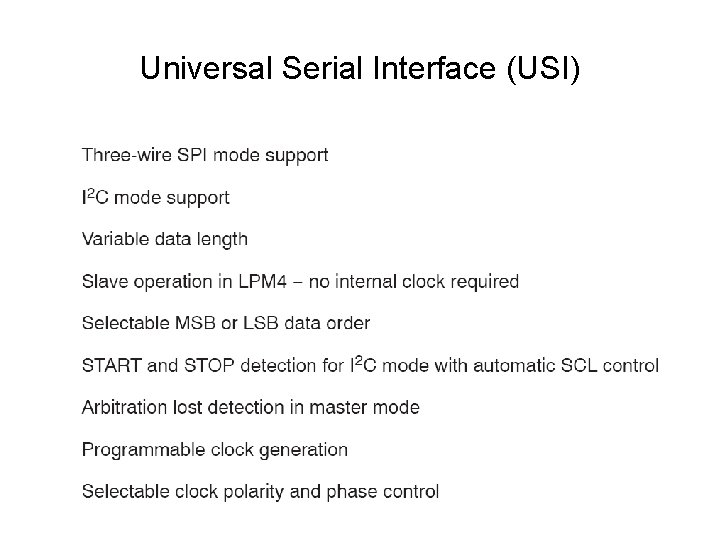

Universal Serial Interface (USI)

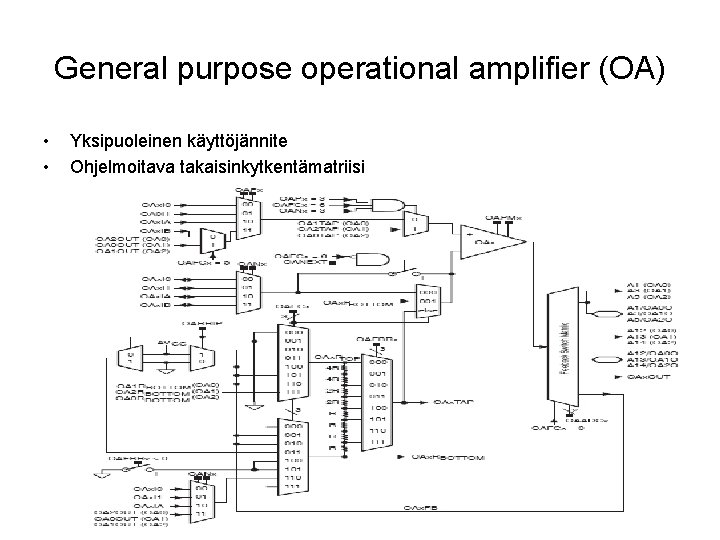

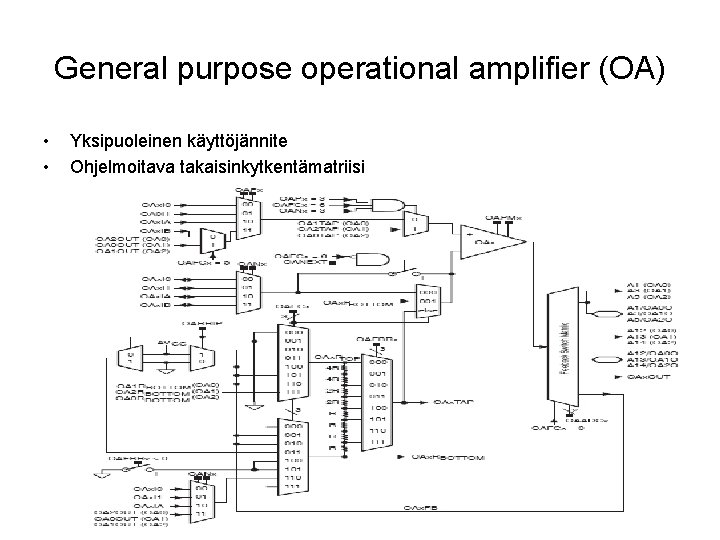

General purpose operational amplifier (OA) • • Yksipuoleinen käyttöjännite Ohjelmoitava takaisinkytkentämatriisi

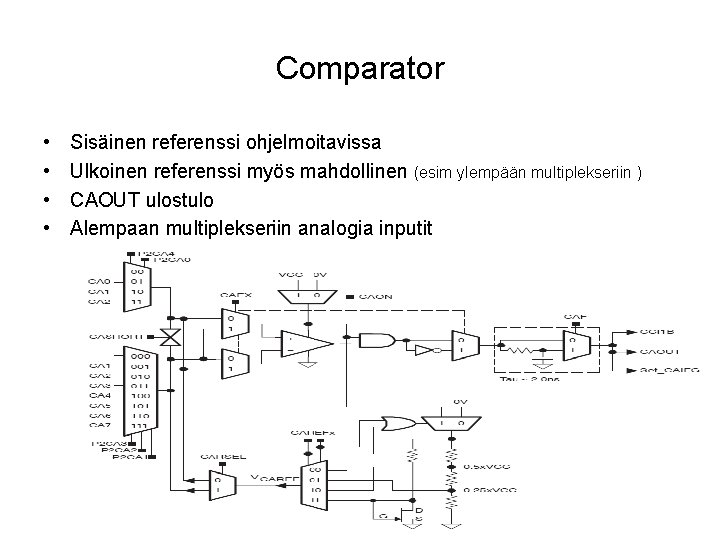

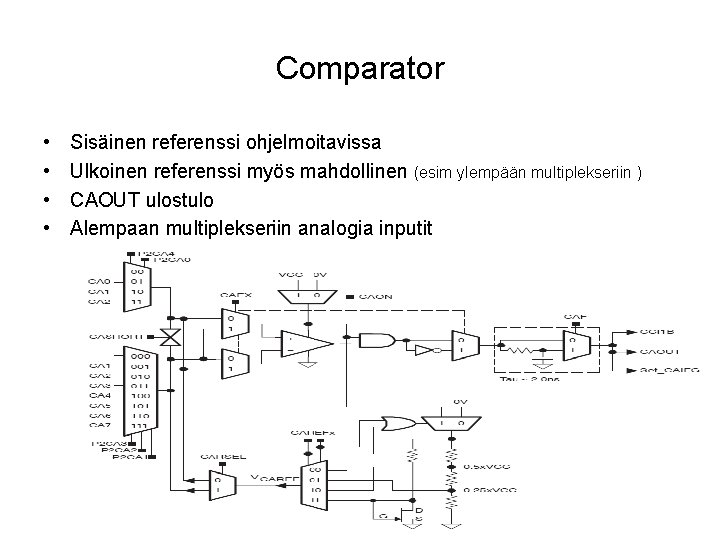

Comparator • • Sisäinen referenssi ohjelmoitavissa Ulkoinen referenssi myös mahdollinen (esim ylempään multiplekseriin ) CAOUT ulostulo Alempaan multiplekseriin analogia inputit

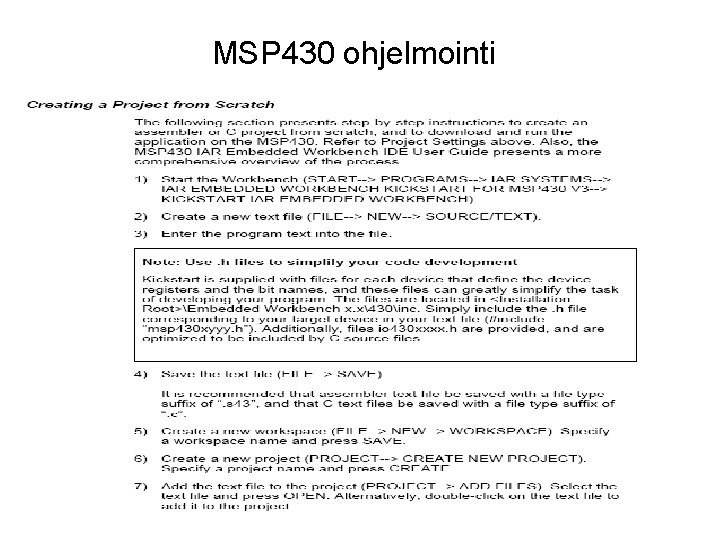

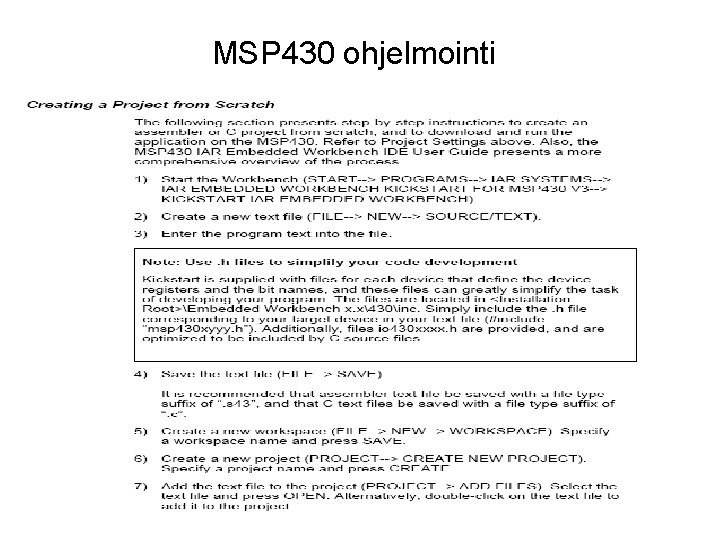

MSP 430 ohjelmointi

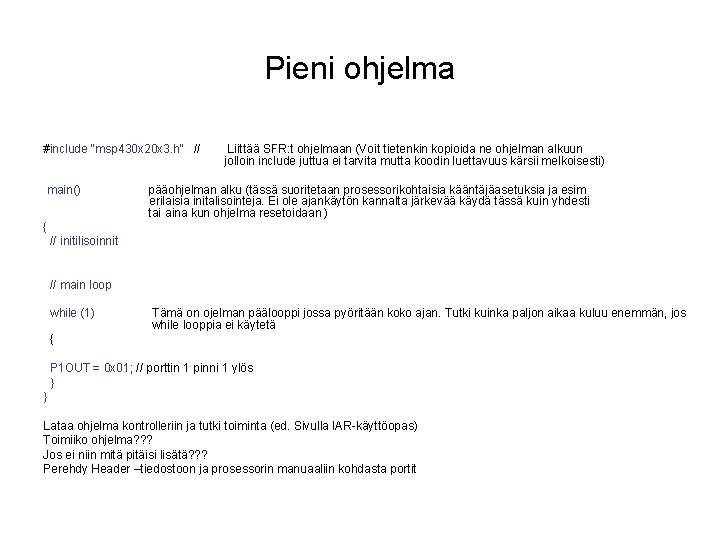

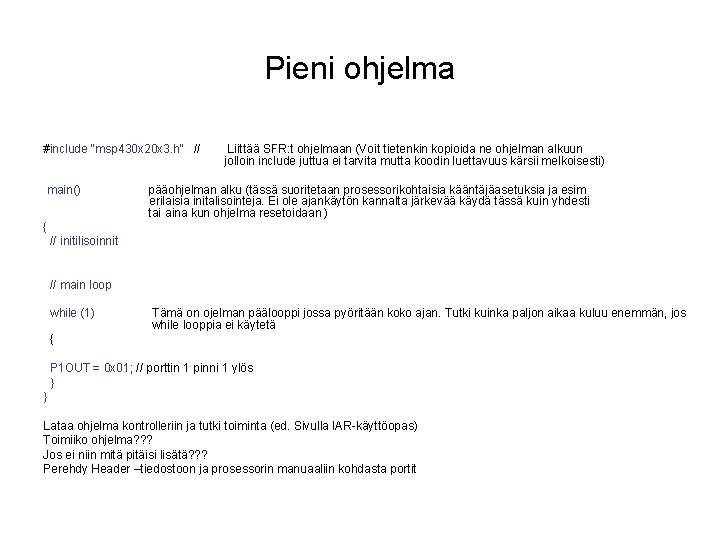

Pieni ohjelma #include "msp 430 x 20 x 3. h“ // main() Liittää SFR: t ohjelmaan (Voit tietenkin kopioida ne ohjelman alkuun jolloin include juttua ei tarvita mutta koodin luettavuus kärsii melkoisesti) pääohjelman alku (tässä suoritetaan prosessorikohtaisia kääntäjäasetuksia ja esim erilaisia initalisointeja. Ei ole ajankäytön kannalta järkevää käydä tässä kuin yhdesti tai aina kun ohjelma resetoidaan ) { // initilisoinnit // main loop while (1) Tämä on ojelman päälooppi jossa pyöritään koko ajan. Tutki kuinka paljon aikaa kuluu enemmän, jos while looppia ei käytetä { P 1 OUT = 0 x 01; // porttin 1 pinni 1 ylös } } Lataa ohjelma kontrolleriin ja tutki toiminta (ed. Sivulla IAR-käyttöopas) Toimiiko ohjelma? ? ? Jos ei niin mitä pitäisi lisätä? ? ? Perehdy Header –tiedostoon ja prosessorin manuaaliin kohdasta portit

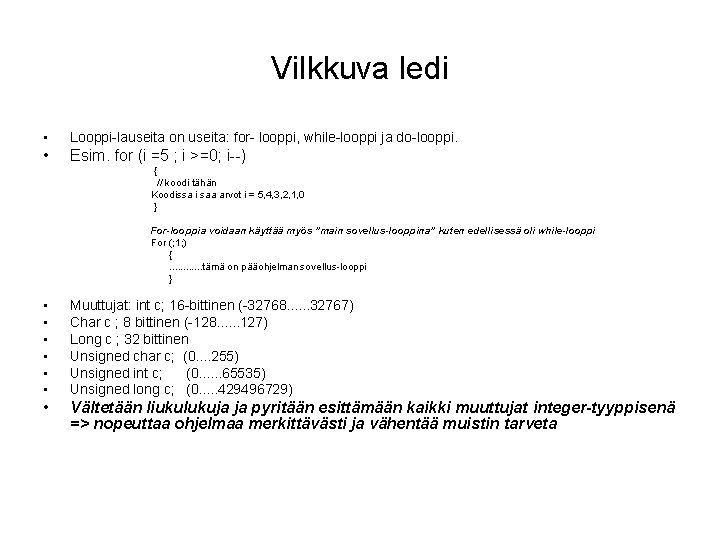

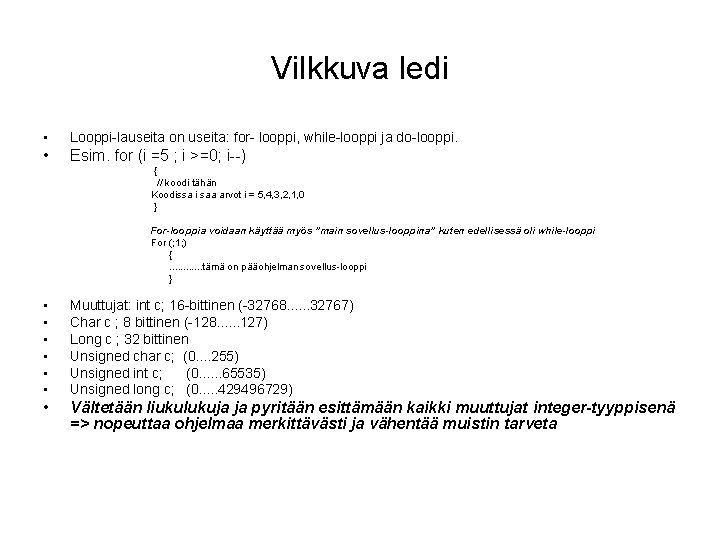

Vilkkuva ledi • Looppi-lauseita on useita: for- looppi, while-looppi ja do-looppi. • Esim. for (i =5 ; i >=0; i--) { // koodi tähän Koodissa i saa arvot i = 5, 4, 3, 2, 1, 0 } For-looppia voidaan käyttää myös ”main sovellus-looppina” kuten edellisessä oli while-looppi For (; 1; ) {. . . tämä on pääohjelman sovellus-looppi } • • • Muuttujat: int c; 16 -bittinen (-32768. . . 32767) Char c ; 8 bittinen (-128. . . 127) Long c ; 32 bittinen Unsigned char c; (0. . 255) Unsigned int c; (0. . . 65535) Unsigned long c; (0. . . 429496729) • Vältetään liukulukuja ja pyritään esittämään kaikki muuttujat integer-tyyppisenä => nopeuttaa ohjelmaa merkittävästi ja vähentää muistin tarveta

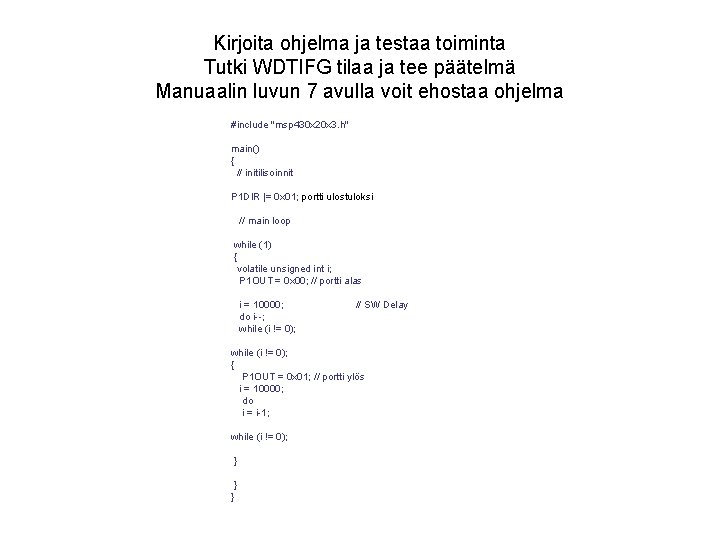

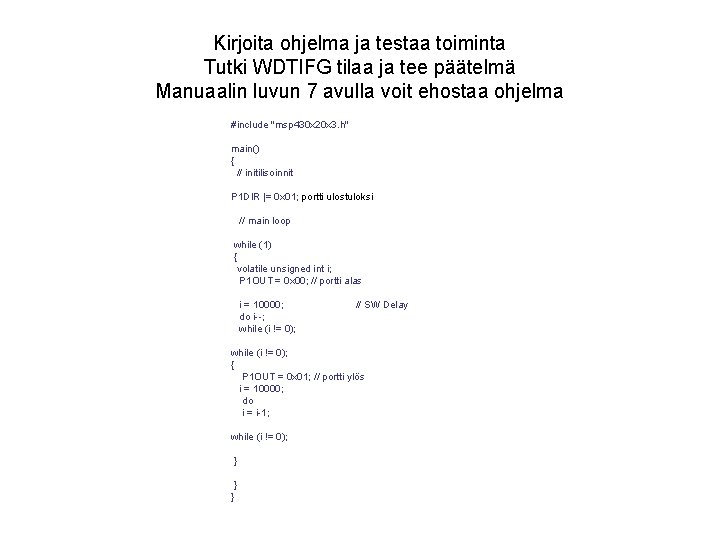

Kirjoita ohjelma ja testaa toiminta Tutki WDTIFG tilaa ja tee päätelmä Manuaalin luvun 7 avulla voit ehostaa ohjelma #include "msp 430 x 20 x 3. h" main() { // initilisoinnit P 1 DIR |= 0 x 01; portti ulostuloksi // main loop while (1) { volatile unsigned int i; P 1 OUT = 0 x 00; // portti alas i = 10000; do i--; while (i != 0); // SW Delay while (i != 0); { P 1 OUT = 0 x 01; // portti ylös i = 10000; do i = i-1; while (i != 0); } } }

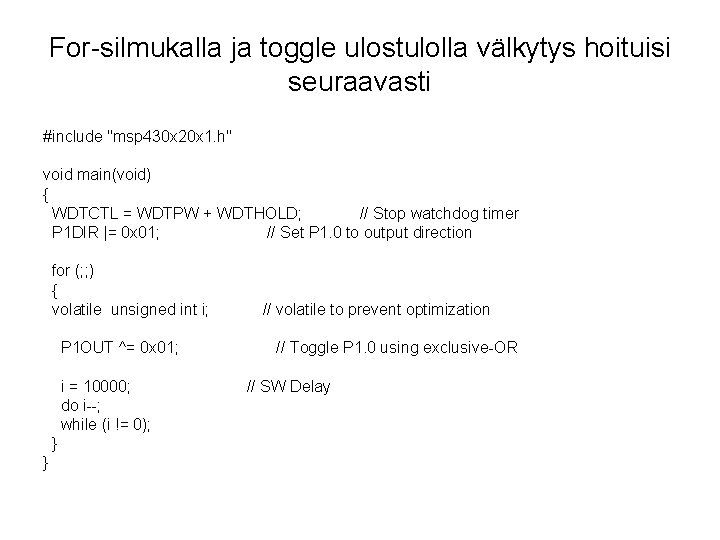

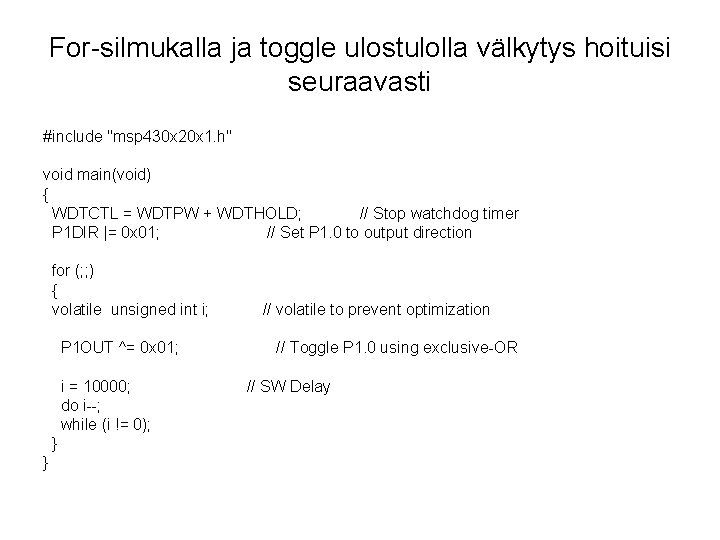

For-silmukalla ja toggle ulostulolla välkytys hoituisi seuraavasti #include "msp 430 x 20 x 1. h" void main(void) { WDTCTL = WDTPW + WDTHOLD; // Stop watchdog timer P 1 DIR |= 0 x 01; // Set P 1. 0 to output direction for (; ; ) { volatile unsigned int i; P 1 OUT ^= 0 x 01; i = 10000; do i--; while (i != 0); } } // volatile to prevent optimization // Toggle P 1. 0 using exclusive-OR // SW Delay

Himmenevä ledi • Toteuta PWM-ohjaus ledille , joka on kytketty P 1. 0. • Suunnittele se niin yksinkertaiseksi kuin mahdollista ja siten , että näet sen toiminna ilman mittalaitteita. • Kytke watchdog pois päältä tässä vaiheessa • Avaa manuaali kohdasta TIMER ja perehdy ajasitmen toimintaan • Tutki ajastimen ohjaamiseen tarvittavia rekistereitä ja päättele mitkä bitit täytyy asettaa ykkösiksi halutun toiminnan aikaansaamiseksi • Debuggerilla voit myös nopeasti kokeilla Timerrekisterien sisällön muuttamista ilman erillisiä koodin käännöksiä. • Mikä on ongelma suunnittelemassasi PWM-koodissa? ? ?

AD_Conversion • ADC 10 muunnin on 10 -bittinen peräkkäisaproksimaatiomuunnin (SAR =Succsesiv Approcsimation Register). Selvitä muuntimen rakenne ja toiminta. • SAR-muuntimen perusominaisuudet ovat: kohtuullinen nopeus (us-luokkaa) ja kohtuulinen tarkkuus. • SD 16 on Sigma-Deltta-muunnin. Mikä on muuntimen periaatteellinen toiminta? ? Mitä hyötyä kahdesta muuntimesta? • Sigma-Deltta muuntimen perusominaisuudet: erittäin tarkka mutta hidas (ms-luokkaa)

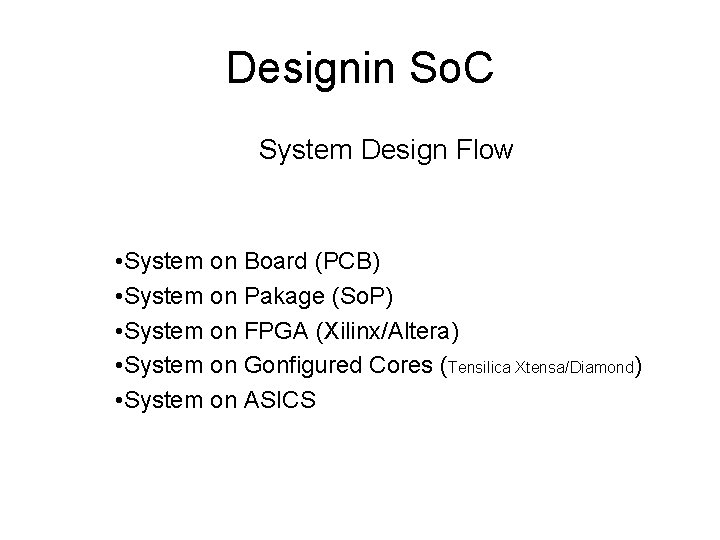

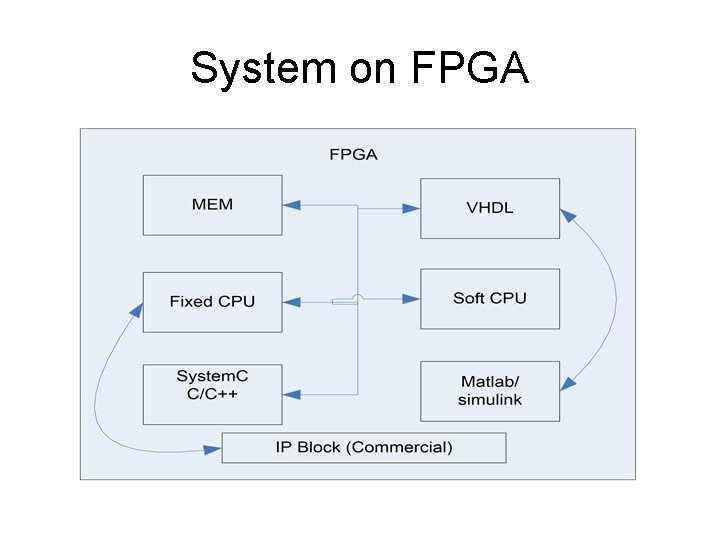

Designin So. C System Design Flow • System on Board (PCB) • System on Pakage (So. P) • System on FPGA (Xilinx/Altera) • System on Gonfigured Cores (Tensilica Xtensa/Diamond) • System on ASICS

System on PCB • Easy to build up (design the board, solder the components) • Easy to program • Easy to test • The complex design refer to the complex PCB • Always quite big dimensions • The long data/adress bus means high capasitance and inductance. The PCB designer have to handel basic RF knowledge. • Needed for long to the future

System on Configured Cores • Tensilica Xtensa/Diamond (several diffrent types of cpu on the same chip) • Altera/Xilinx Nios/Micro. Blace (software processors) • Xilinx Power PC-cores (hard core processors) • ARM-type cores for ASICs

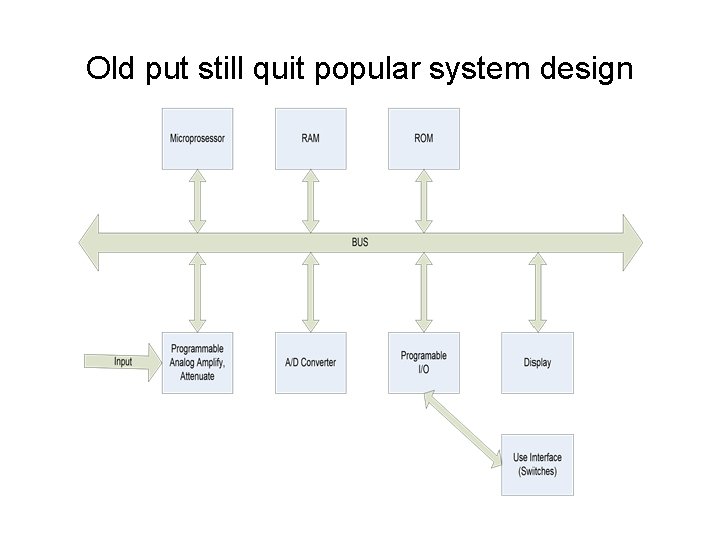

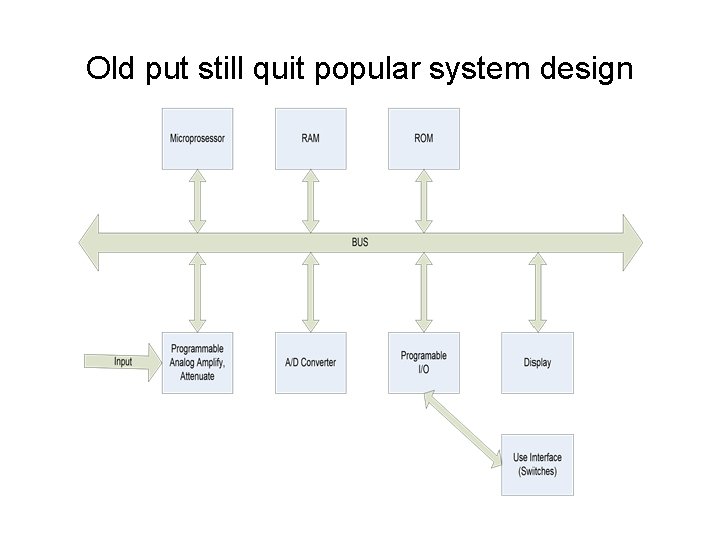

Old put still quit popular system design

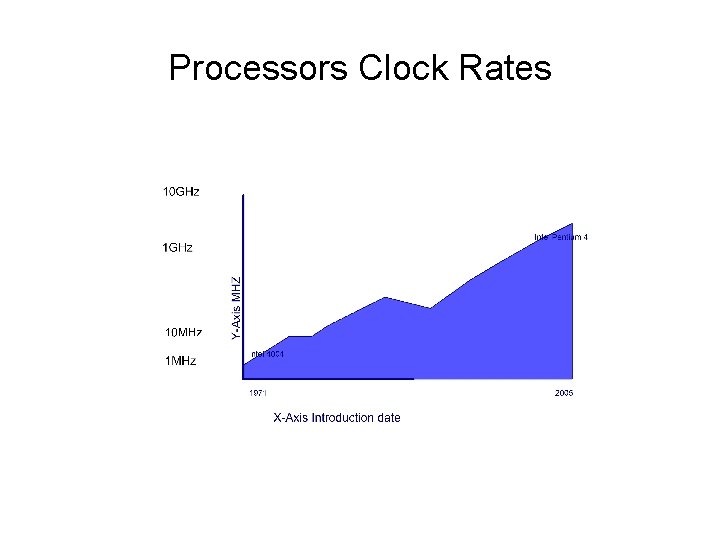

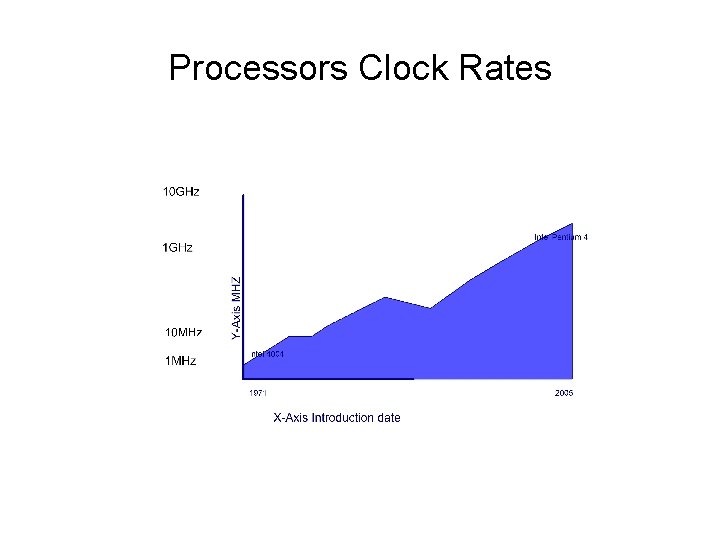

Processors Clock Rates

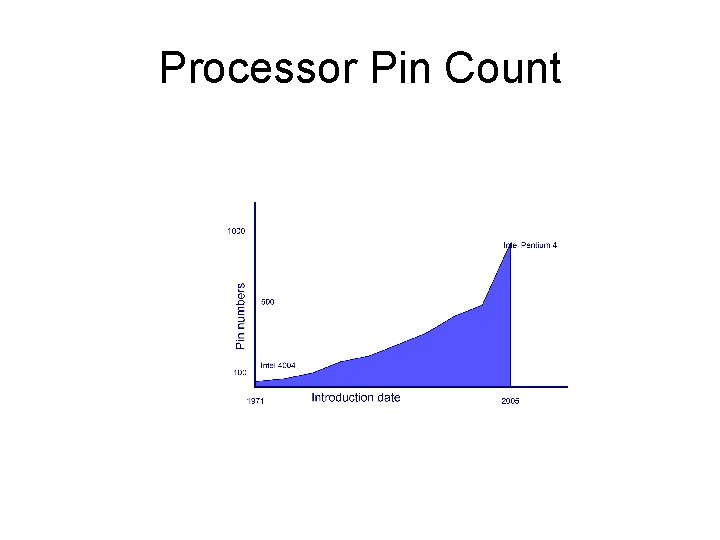

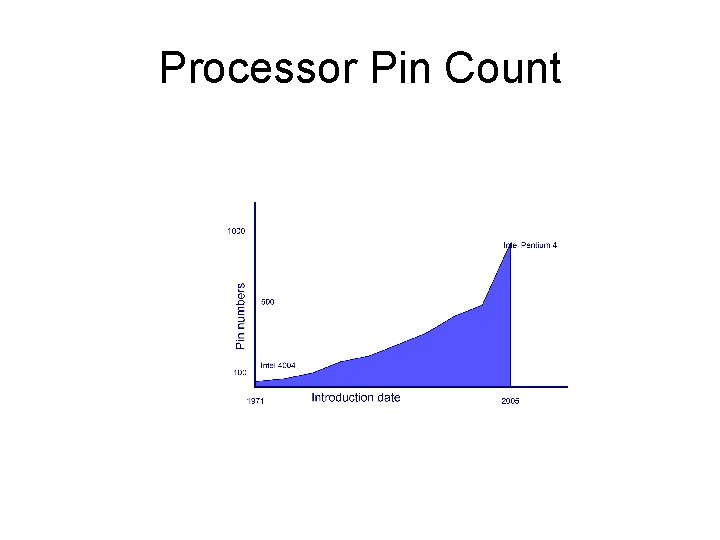

Processor Pin Count

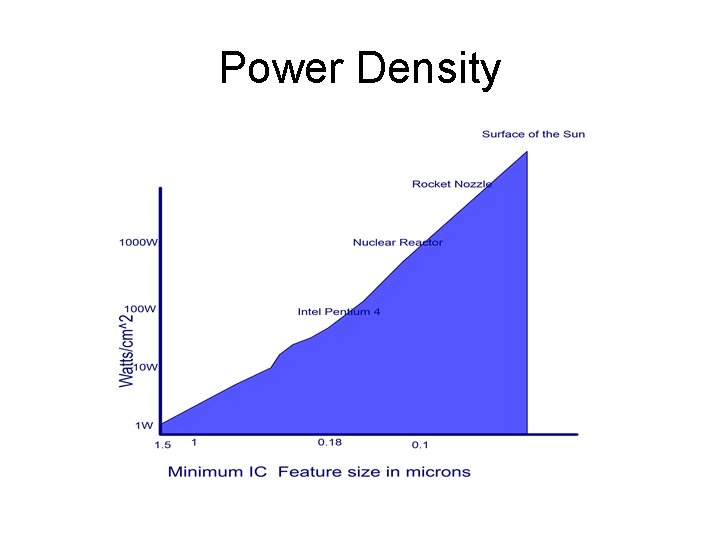

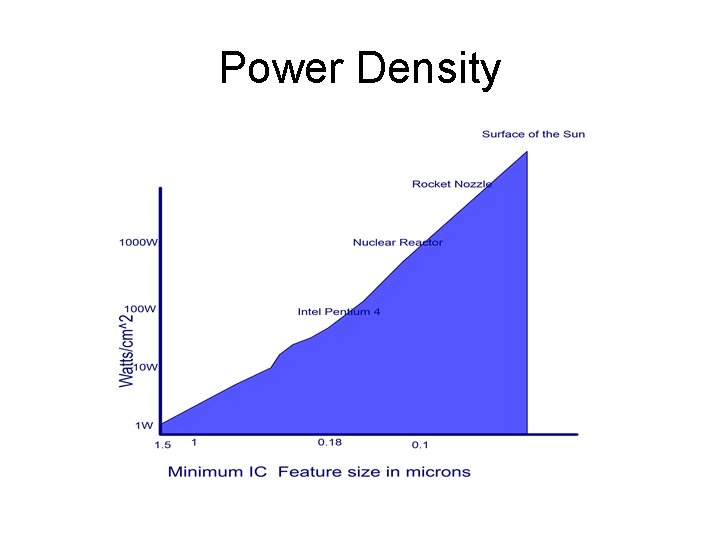

Power Density

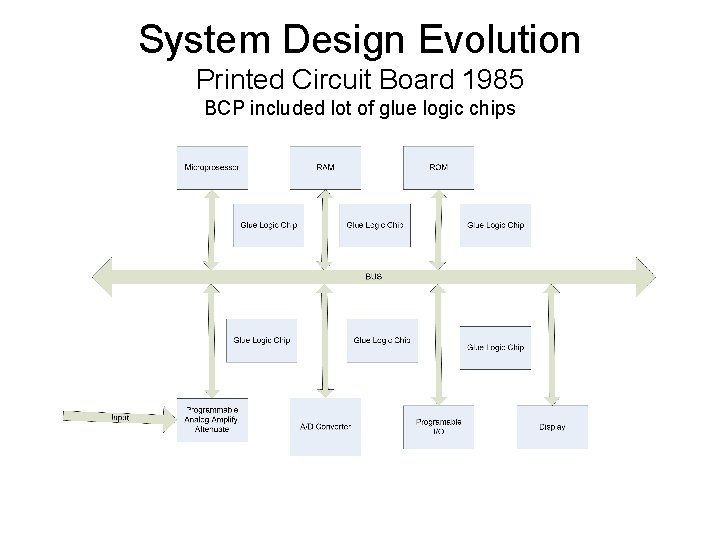

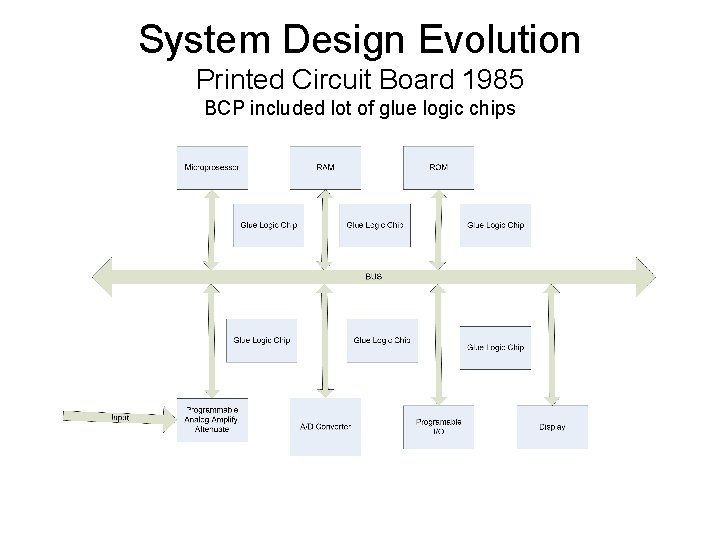

System Design Evolution Printed Circuit Board 1985 BCP included lot of glue logic chips

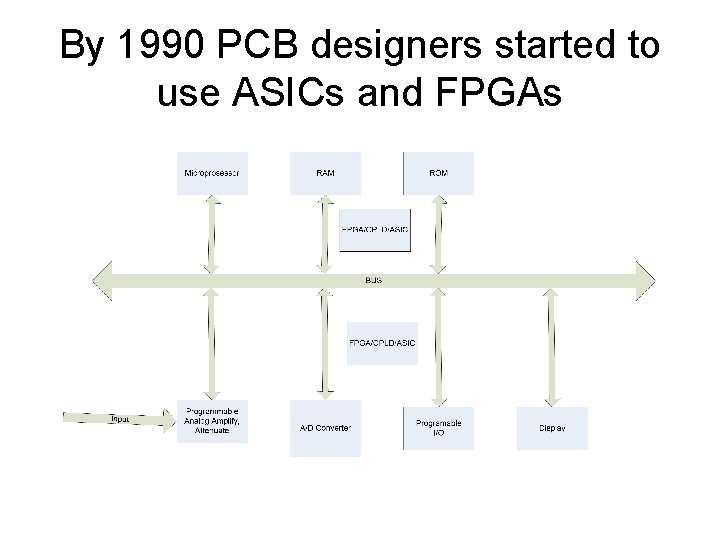

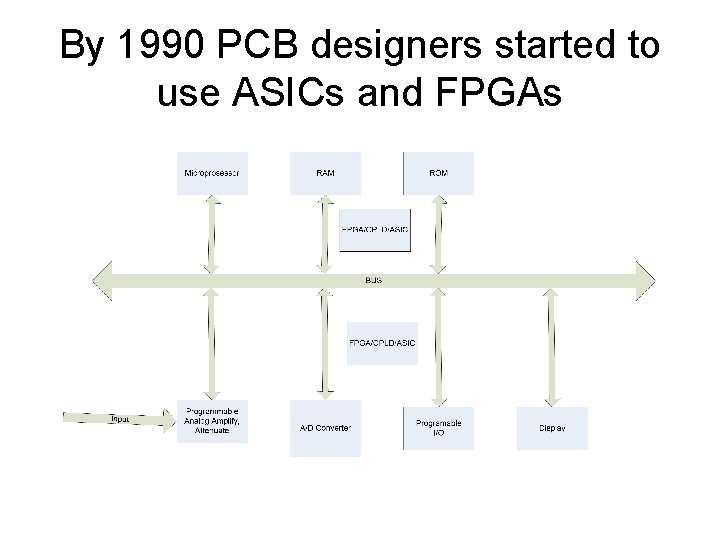

By 1990 PCB designers started to use ASICs and FPGAs

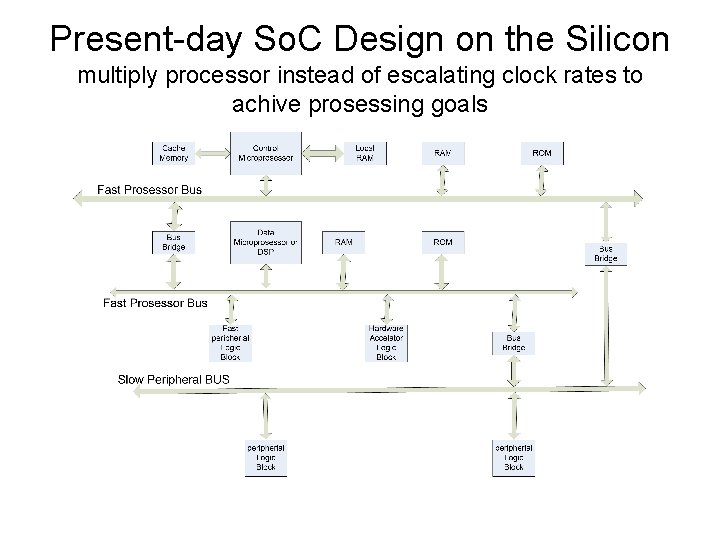

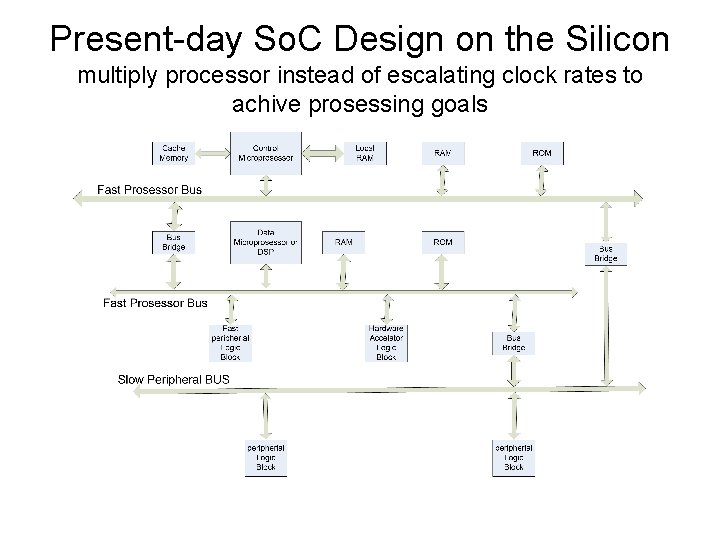

Present-day So. C Design on the Silicon multiply processor instead of escalating clock rates to achive prosessing goals

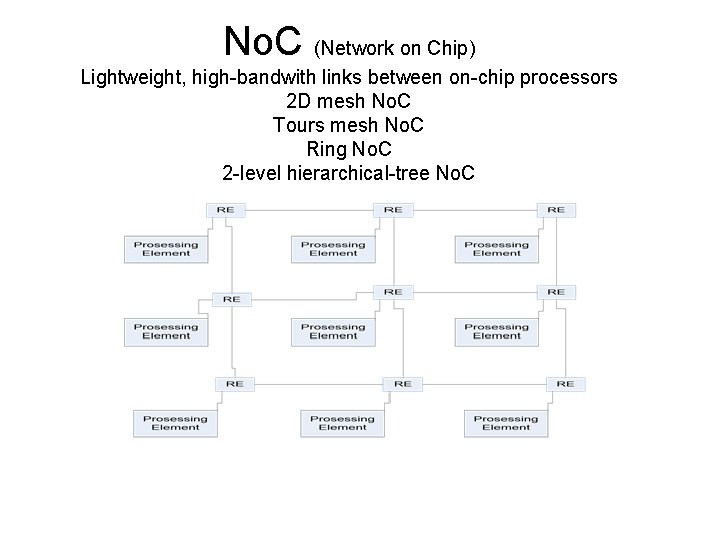

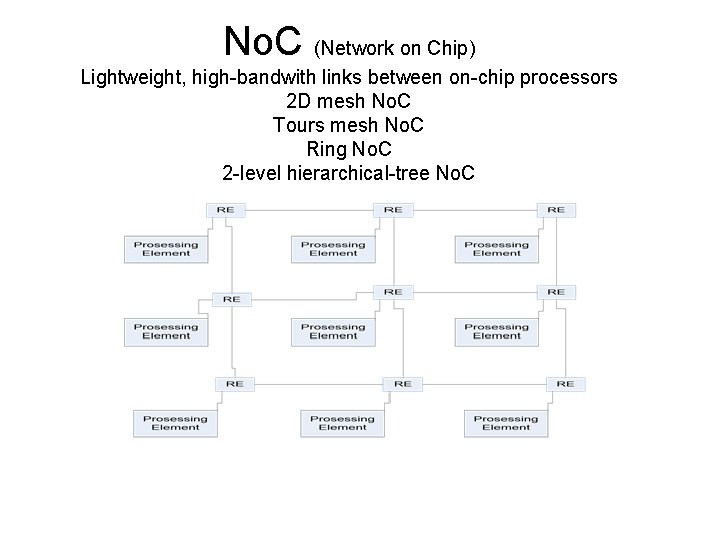

No. C (Network on Chip) Lightweight, high-bandwith links between on-chip processors 2 D mesh No. C Tours mesh No. C Ring No. C 2 -level hierarchical-tree No. C

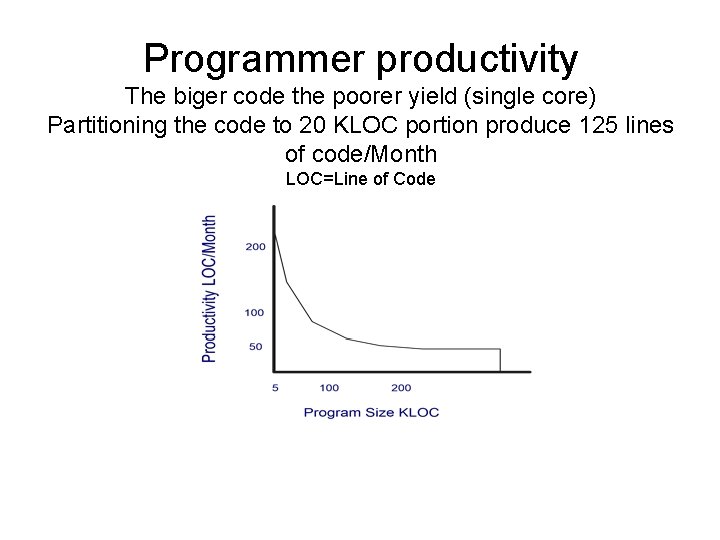

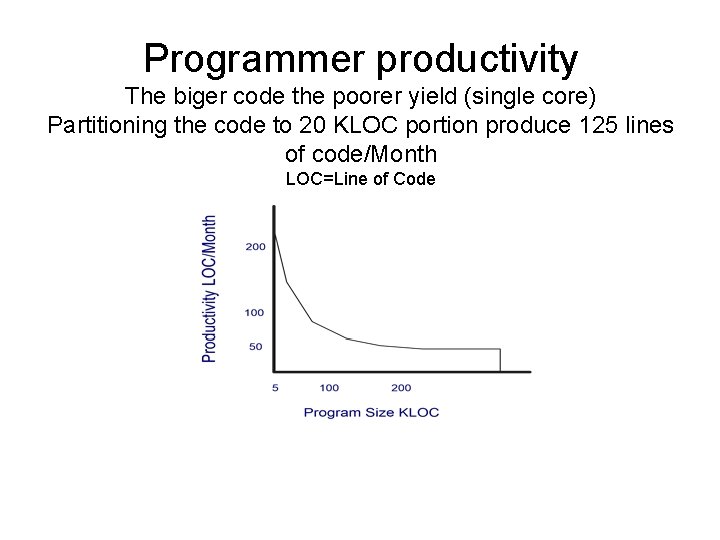

Programmer productivity The biger code the poorer yield (single core) Partitioning the code to 20 KLOC portion produce 125 lines of code/Month LOC=Line of Code

ITRS report identifies five ”grand challanges” related to So. C • • Productivity Power Manufacturability Interference (high frquence, high slew rate, high density of wires and signals, small inductance and cpasitance => long wires must go ) • Reliability

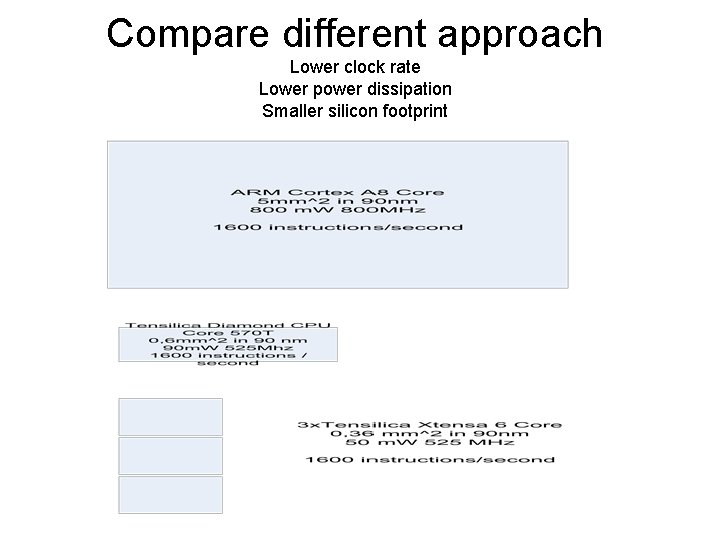

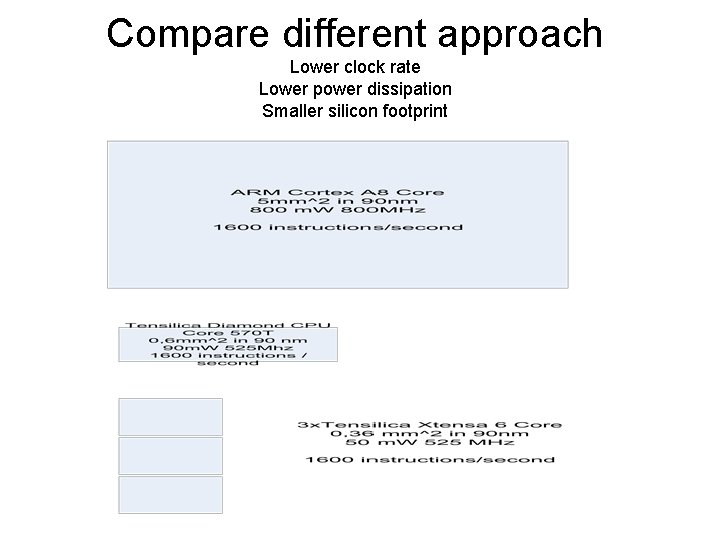

Compare different approach Lower clock rate Lower power dissipation Smaller silicon footprint

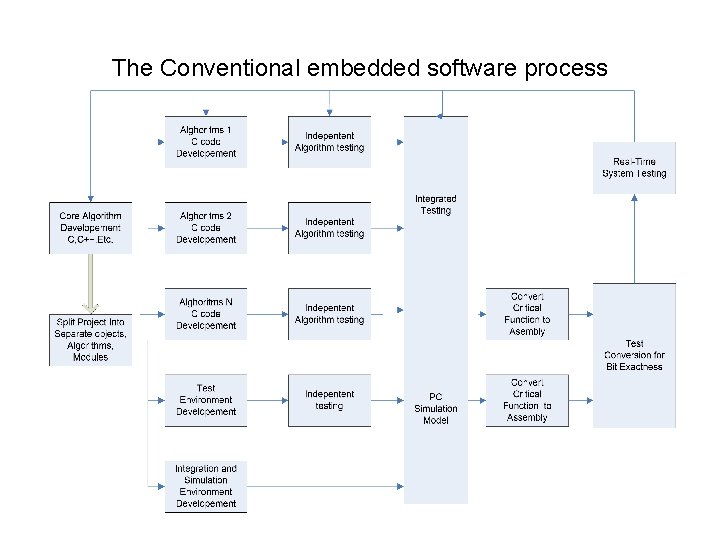

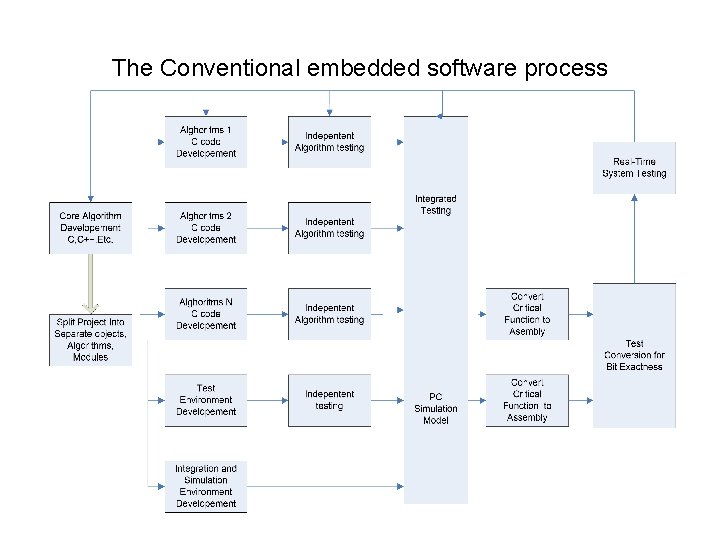

The Conventional embedded software process

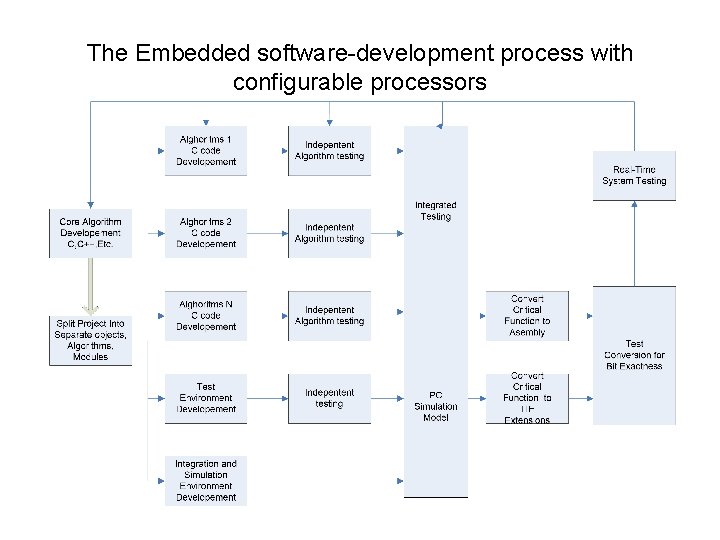

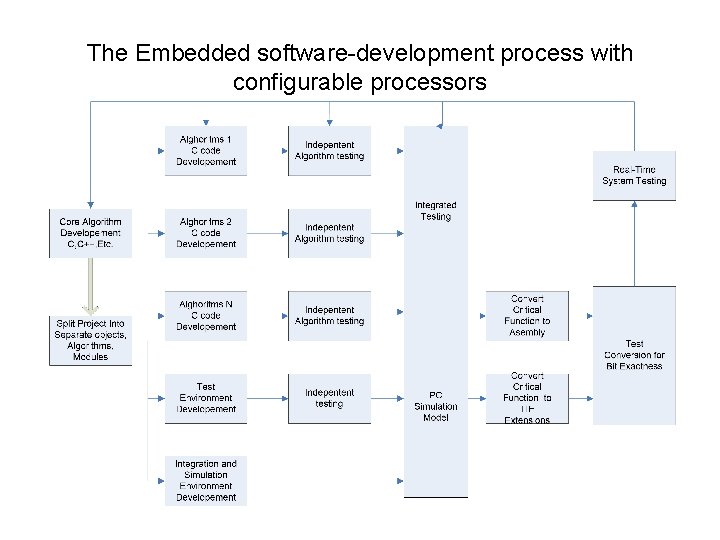

The Embedded software-development process with configurable processors

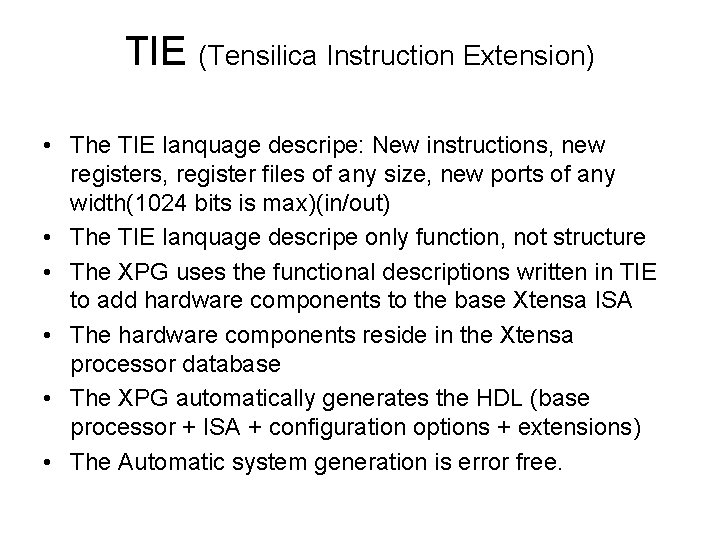

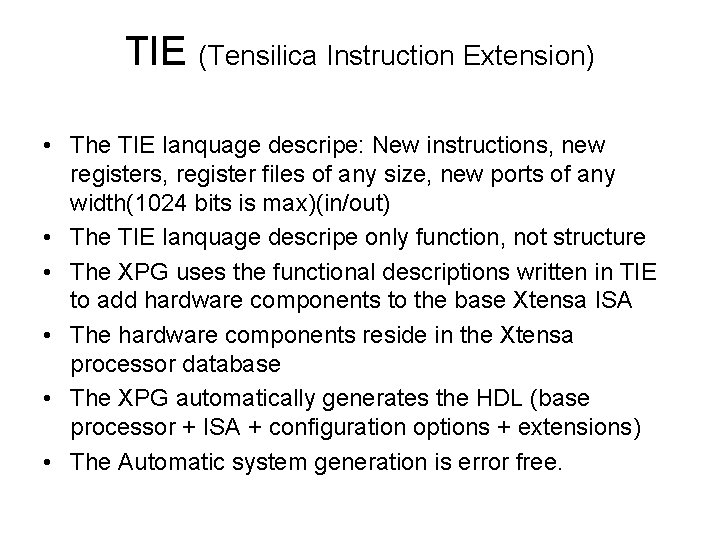

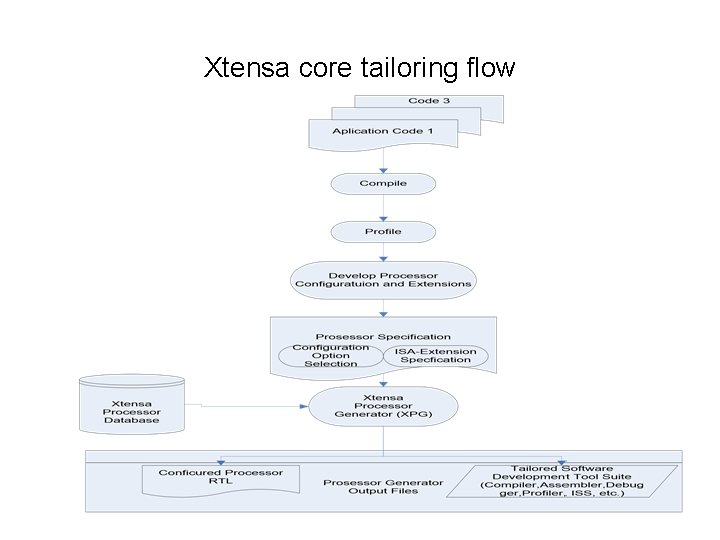

TIE (Tensilica Instruction Extension) • The TIE lanquage descripe: New instructions, new registers, register files of any size, new ports of any width(1024 bits is max)(in/out) • The TIE lanquage descripe only function, not structure • The XPG uses the functional descriptions written in TIE to add hardware components to the base Xtensa ISA • The hardware components reside in the Xtensa processor database • The XPG automatically generates the HDL (base processor + ISA + configuration options + extensions) • The Automatic system generation is error free.

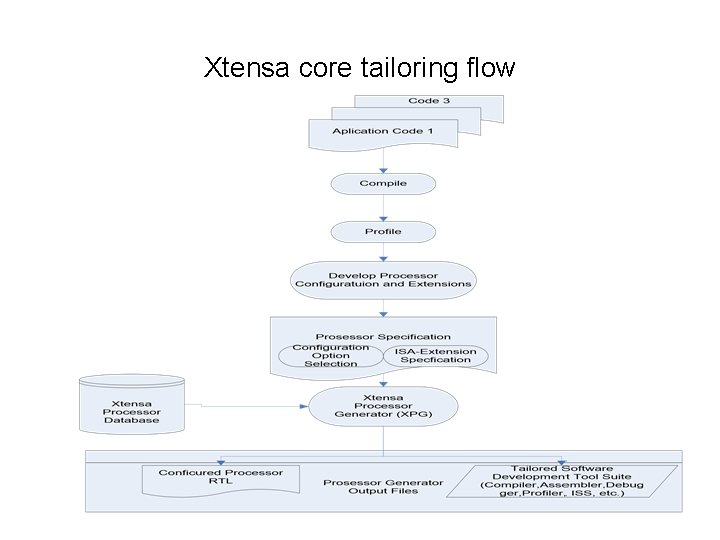

Xtensa core tailoring flow

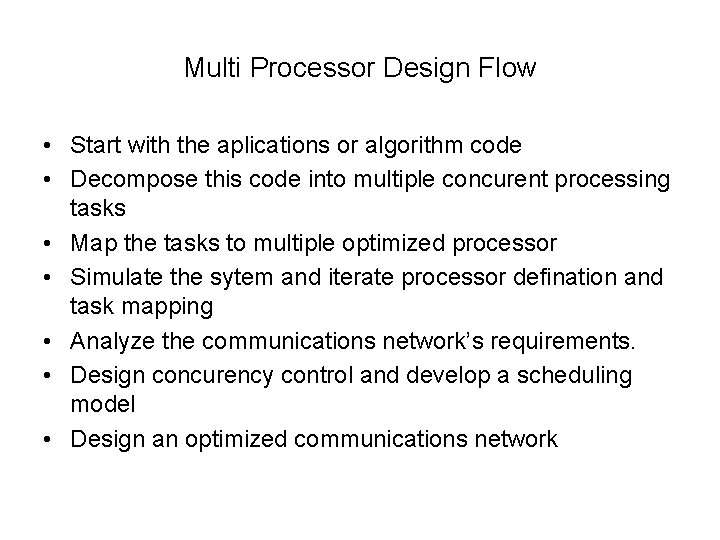

Multi Processor Design Flow • Start with the aplications or algorithm code • Decompose this code into multiple concurent processing tasks • Map the tasks to multiple optimized processor • Simulate the sytem and iterate processor defination and task mapping • Analyze the communications network’s requirements. • Design concurency control and develop a scheduling model • Design an optimized communications network

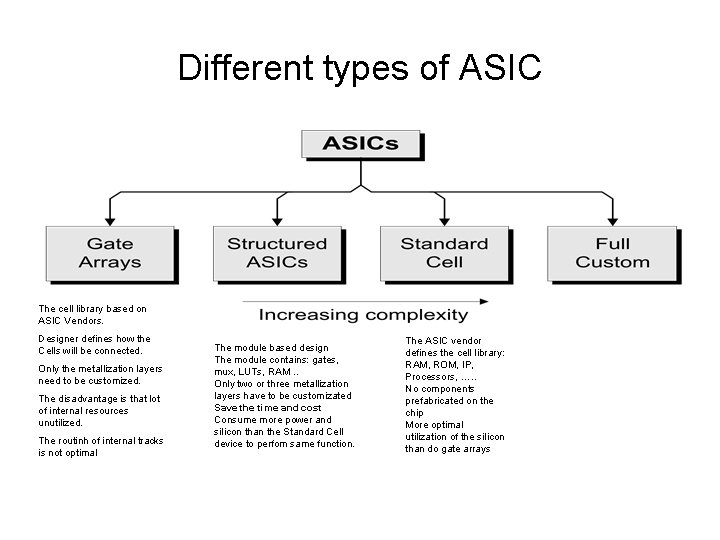

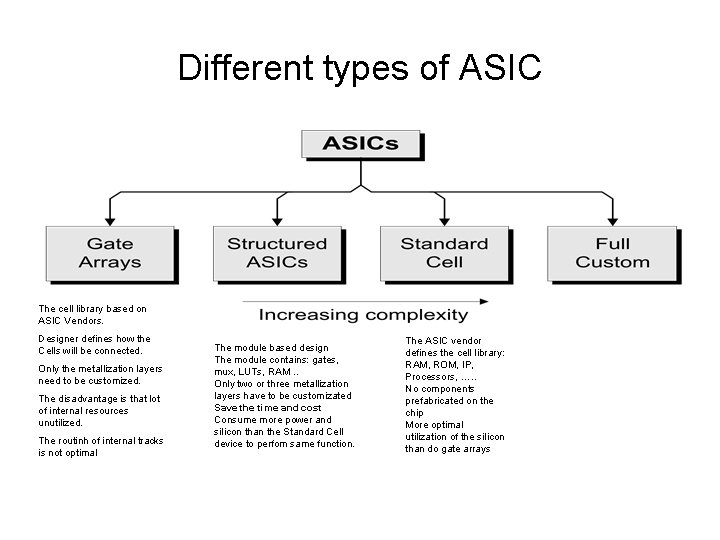

Different types of ASIC The cell library based on ASIC Vendors. Designer defines how the Cells will be connected. Only the metallization layers need to be customized. The disadvantage is that lot of internal resources unutilized. The routinh of internal tracks is not optimal The module based design The module contains: gates, mux, LUTs, RAM. . Only two or three metallization layers have to be customizated Save the time and cost Consume more power and silicon than the Standard Cell device to perfom same function. The ASIC vendor defines the cell library: RAM, ROM, IP, Processors, …. . No components prefabricated on the chip More optimal utilization of the silicon than do gate arrays

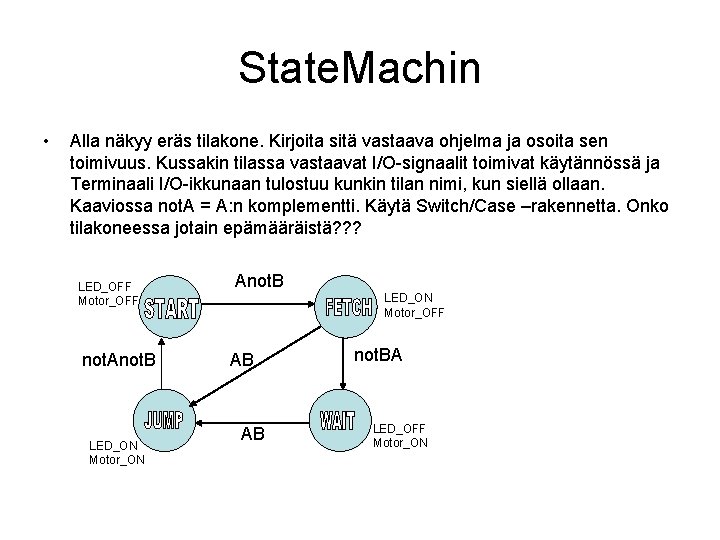

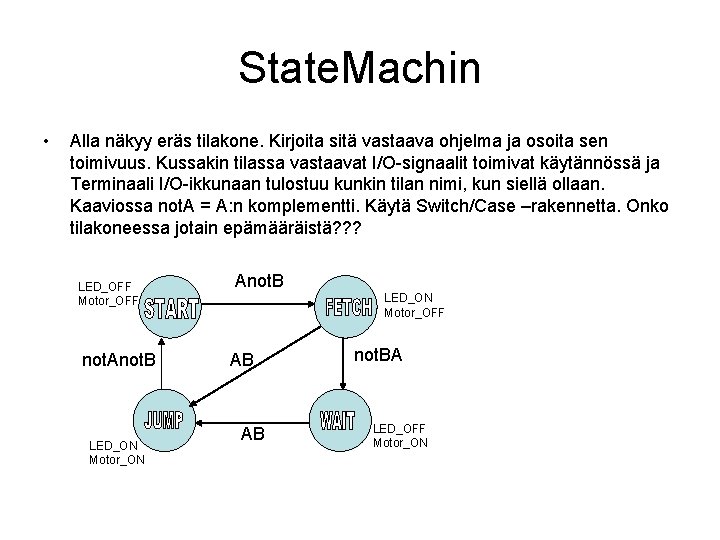

State. Machin • Alla näkyy eräs tilakone. Kirjoita sitä vastaava ohjelma ja osoita sen toimivuus. Kussakin tilassa vastaavat I/O-signaalit toimivat käytännössä ja Terminaali I/O-ikkunaan tulostuu kunkin tilan nimi, kun siellä ollaan. Kaaviossa not. A = A: n komplementti. Käytä Switch/Case –rakennetta. Onko tilakoneessa jotain epämääräistä? ? ? LED_OFF Motor_OFF not. Anot. B LED_ON Motor_ON Anot. B LED_ON Motor_OFF AB AB not. BA LED_OFF Motor_ON

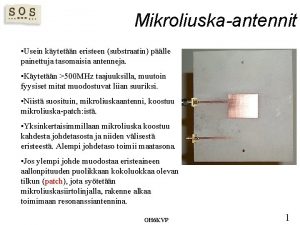

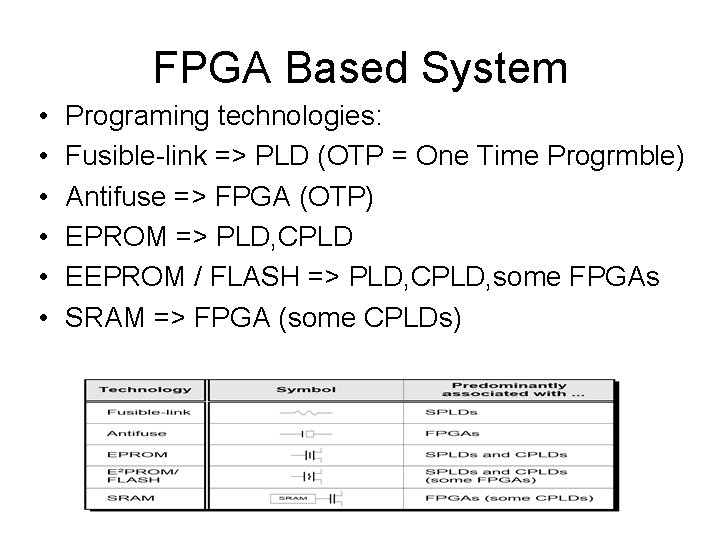

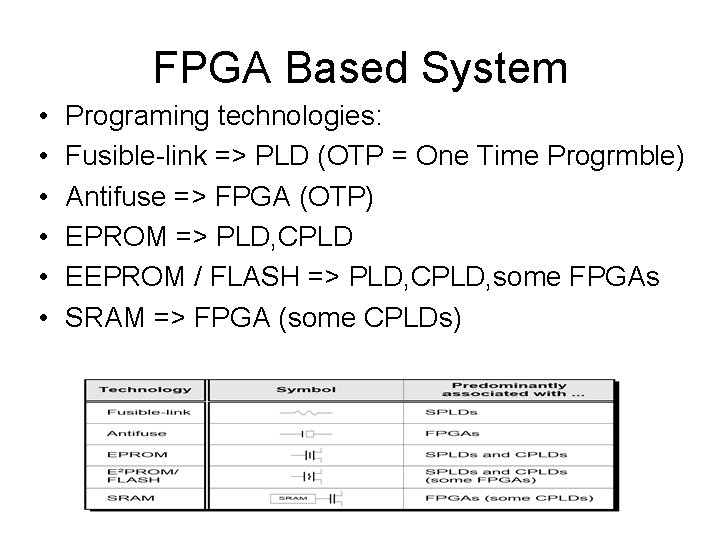

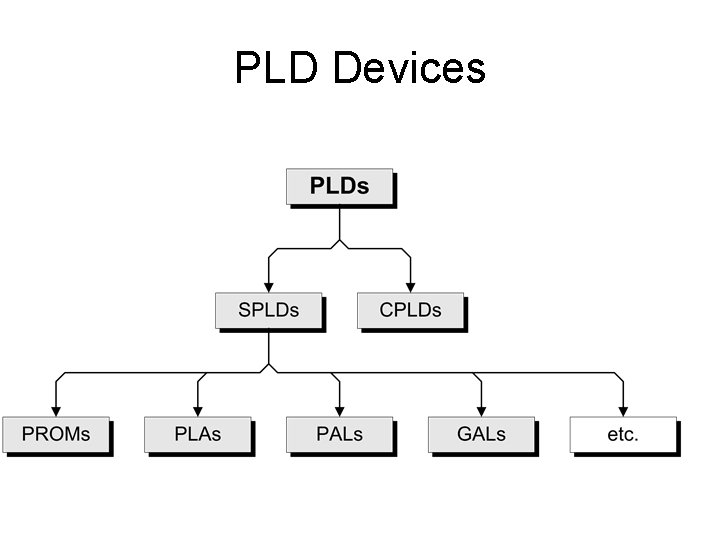

FPGA Based System • • • Programing technologies: Fusible-link => PLD (OTP = One Time Progrmble) Antifuse => FPGA (OTP) EPROM => PLD, CPLD EEPROM / FLASH => PLD, CPLD, some FPGAs SRAM => FPGA (some CPLDs)

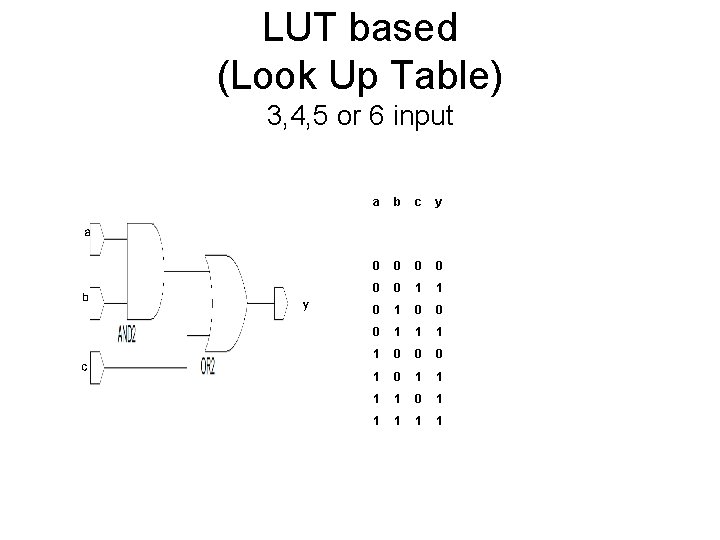

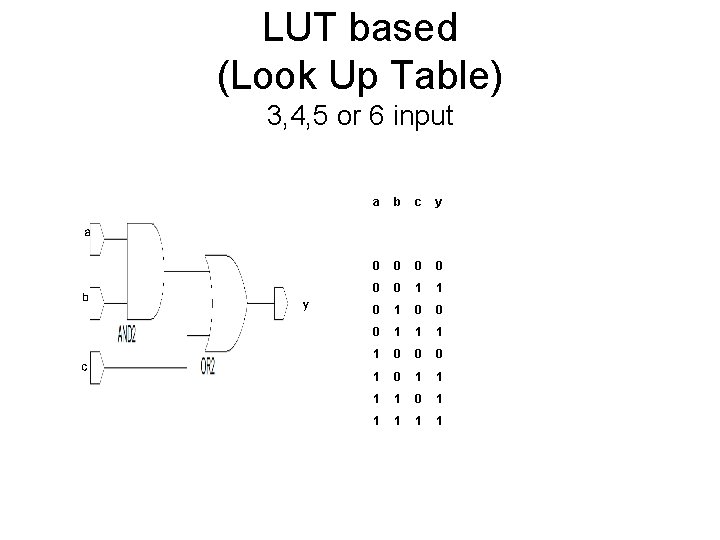

LUT based (Look Up Table) 3, 4, 5 or 6 input a b c y 0 0 0 1 1 0 0 0 1 1 1 1 0 1 1 1

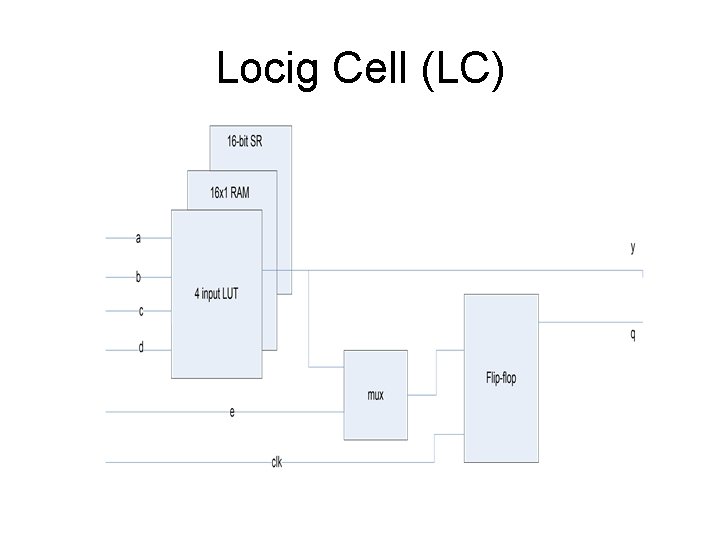

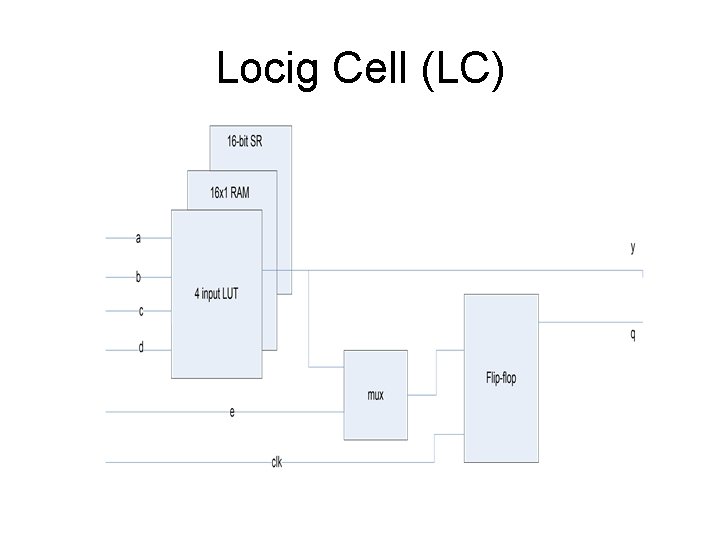

Locig Cell (LC)

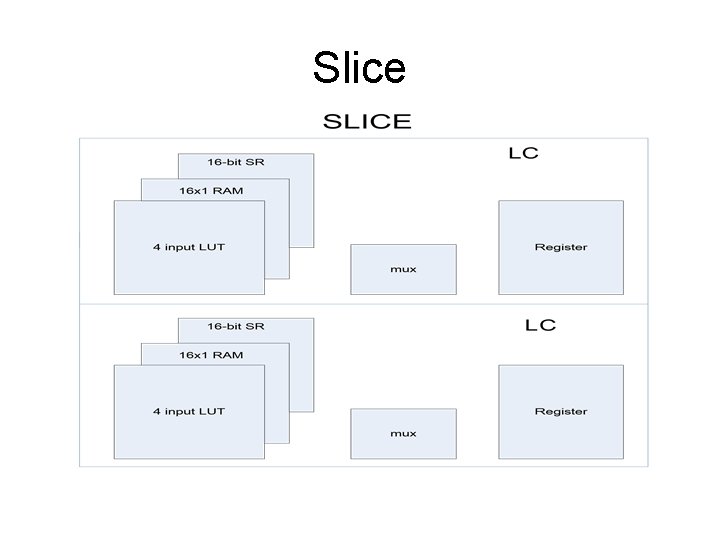

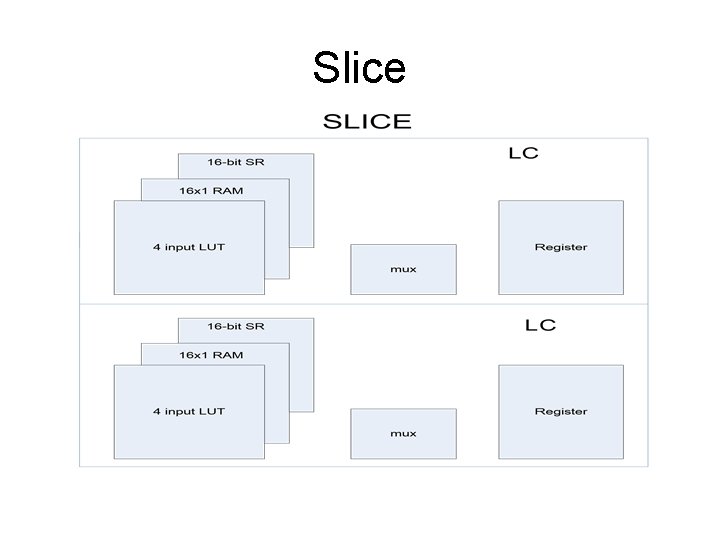

Slice

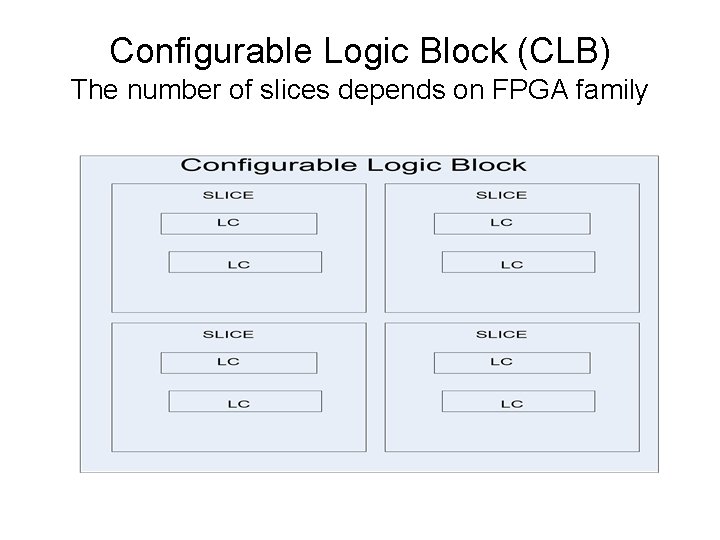

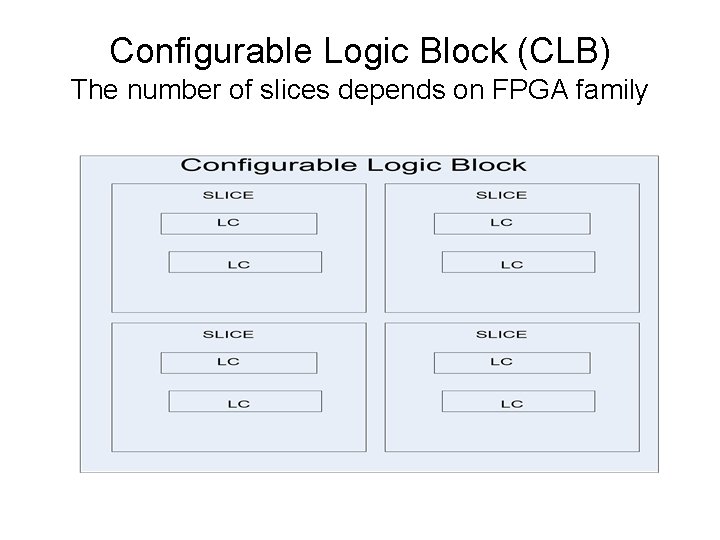

Configurable Logic Block (CLB) The number of slices depends on FPGA family

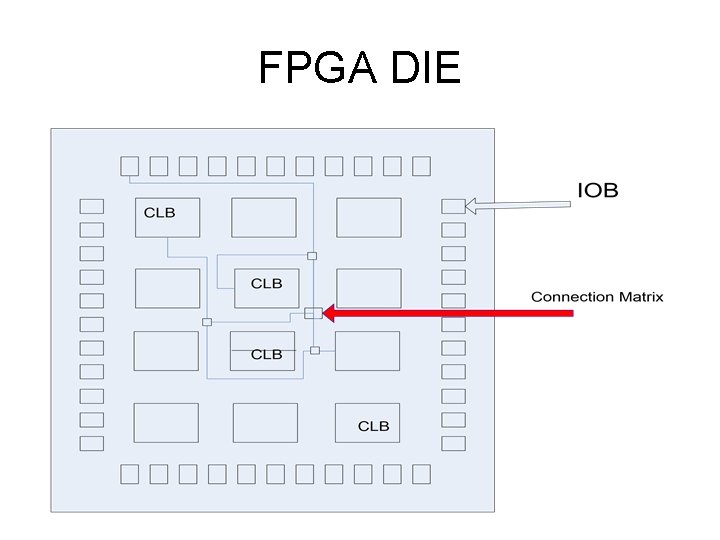

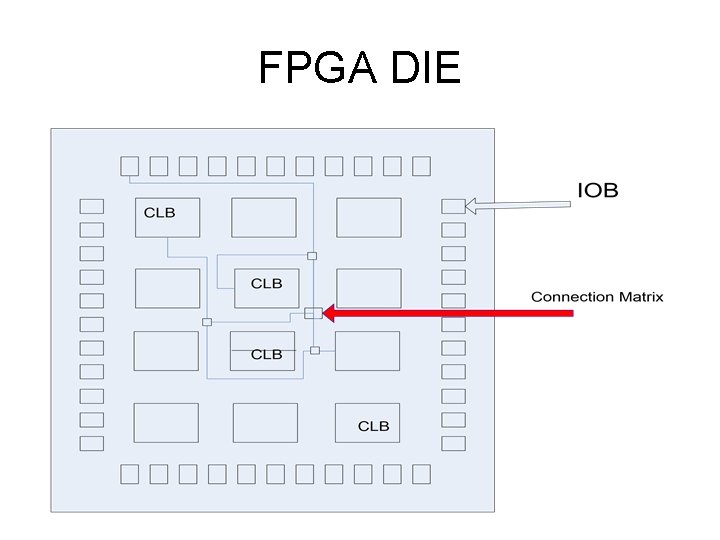

FPGA DIE

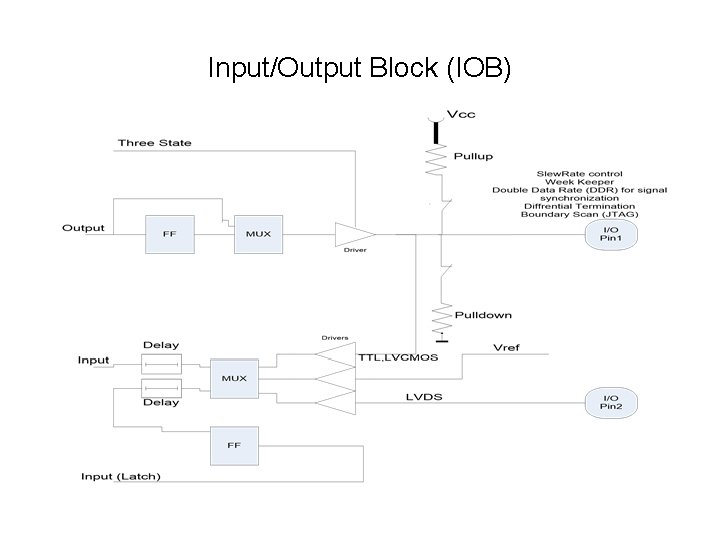

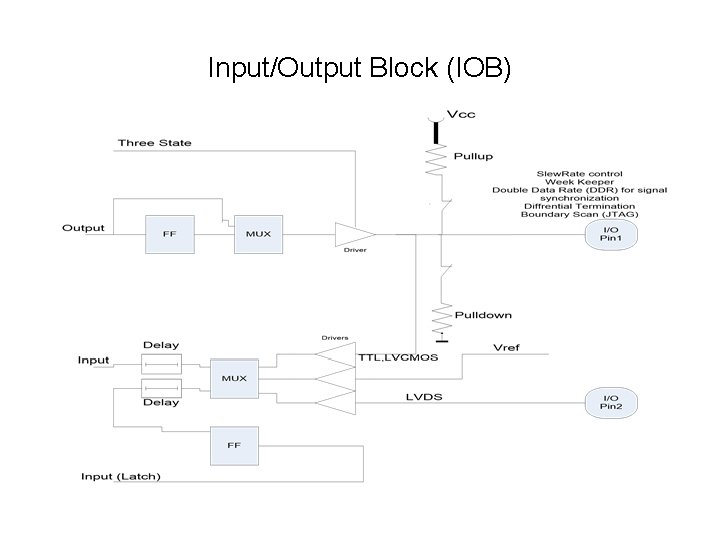

Input/Output Block (IOB)

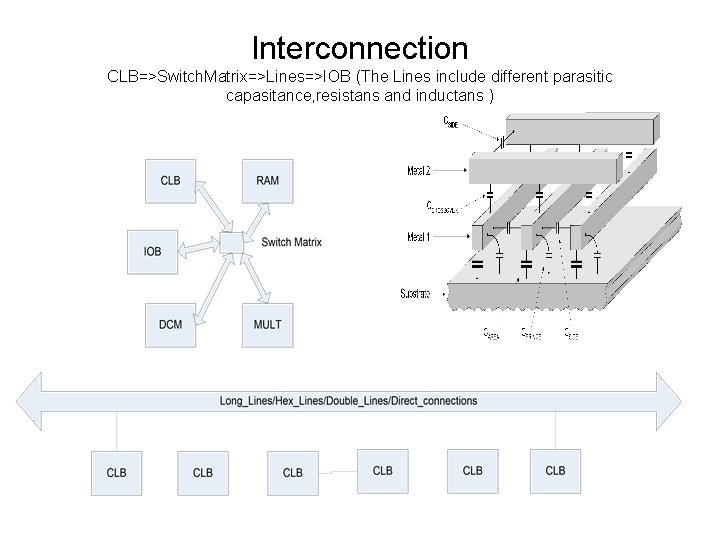

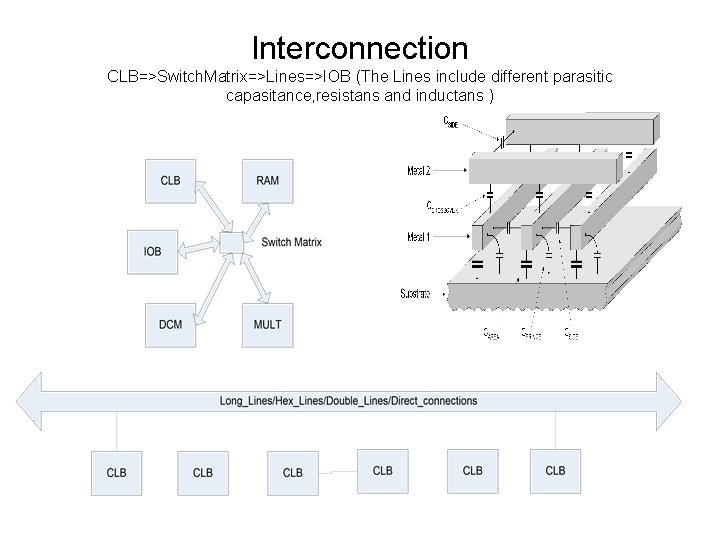

Interconnection CLB=>Switch. Matrix=>Lines=>IOB (The Lines include different parasitic capasitance, resistans and inductans )

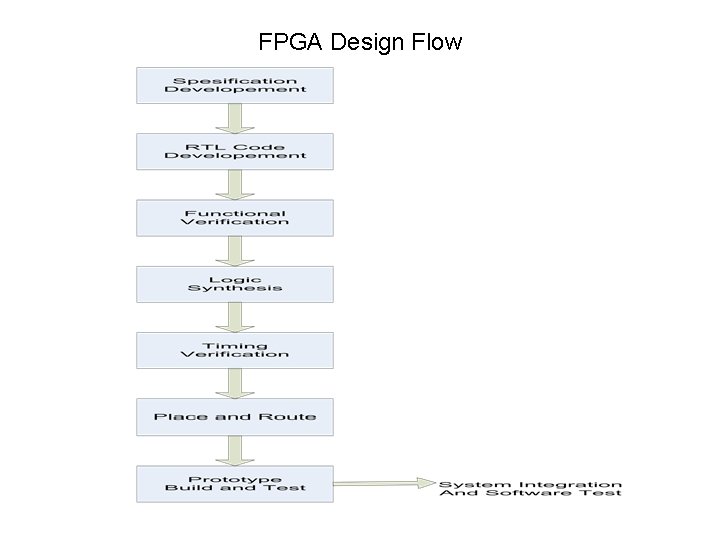

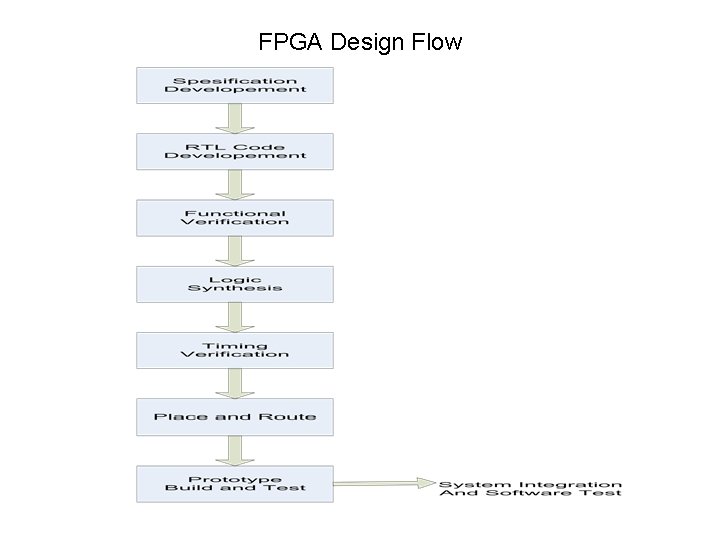

FPGA Design Flow

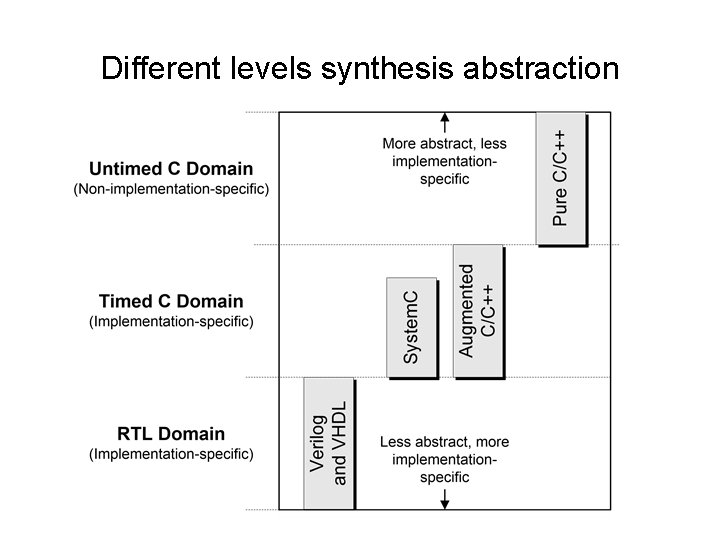

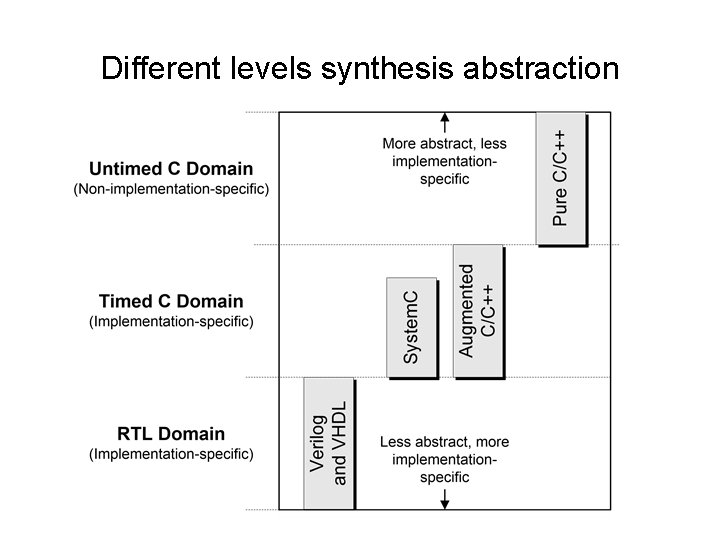

Different levels synthesis abstraction

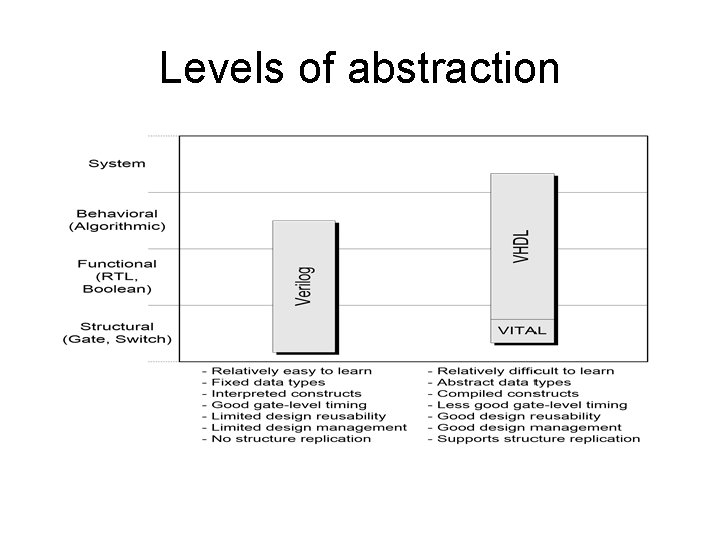

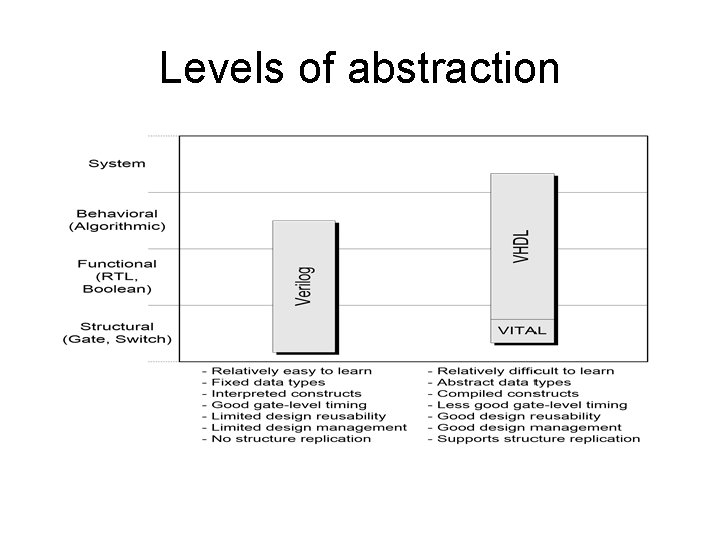

Levels of abstraction

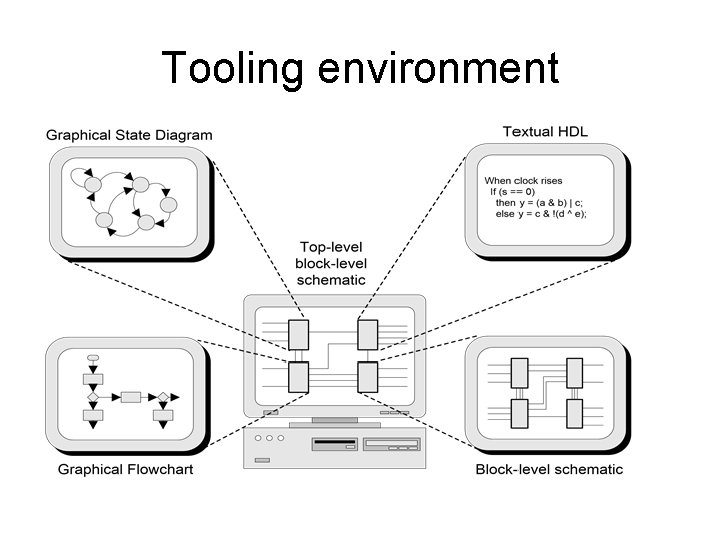

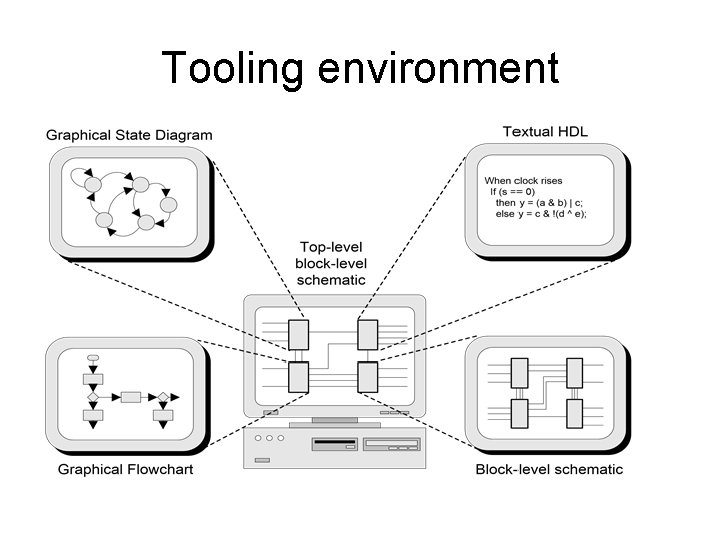

Tooling environment

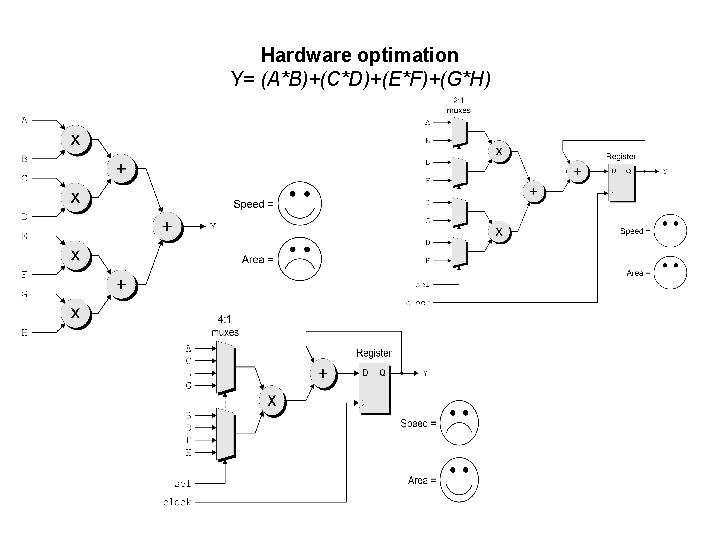

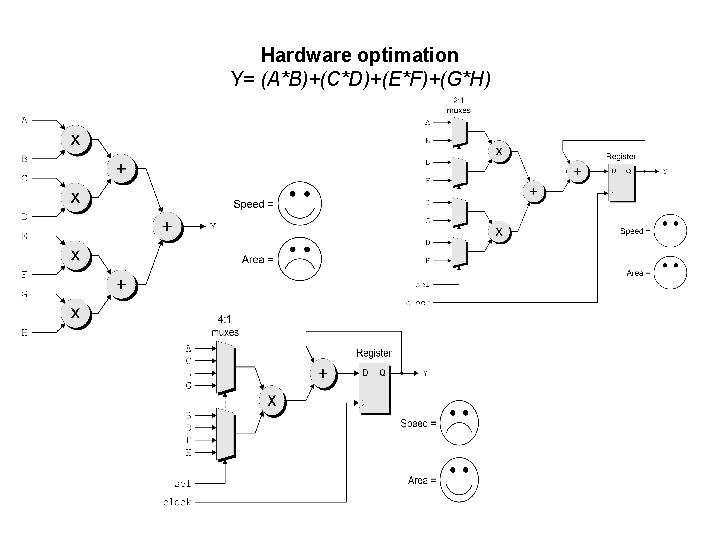

Hardware optimation Y= (A*B)+(C*D)+(E*F)+(G*H)

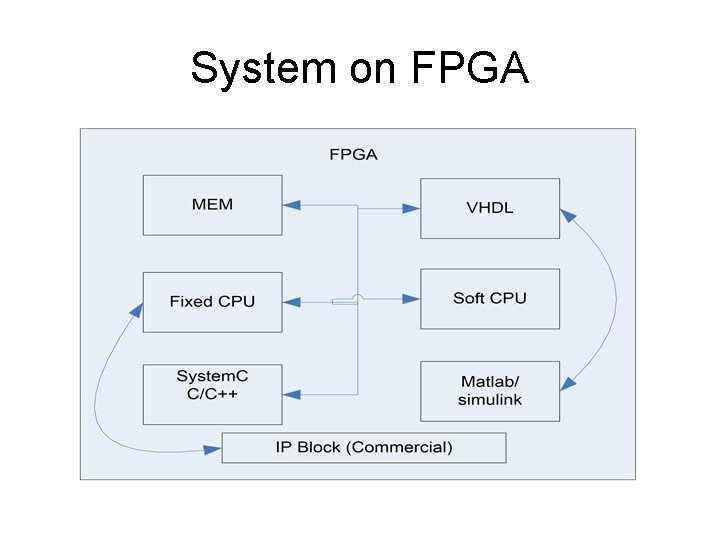

System on FPGA

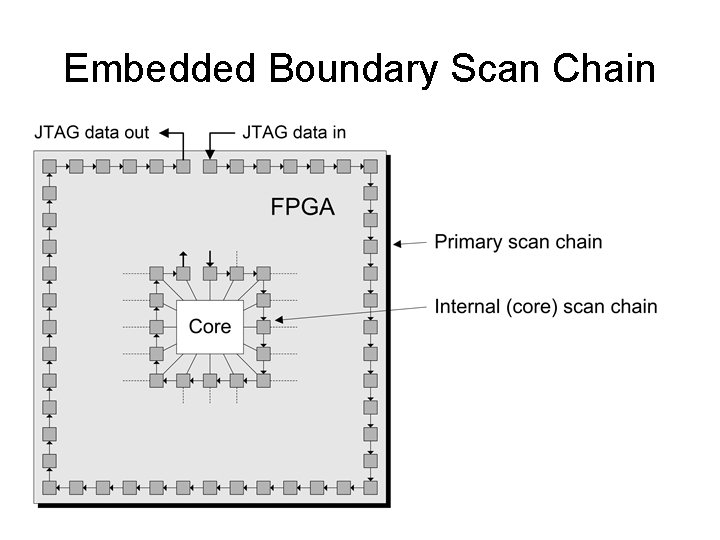

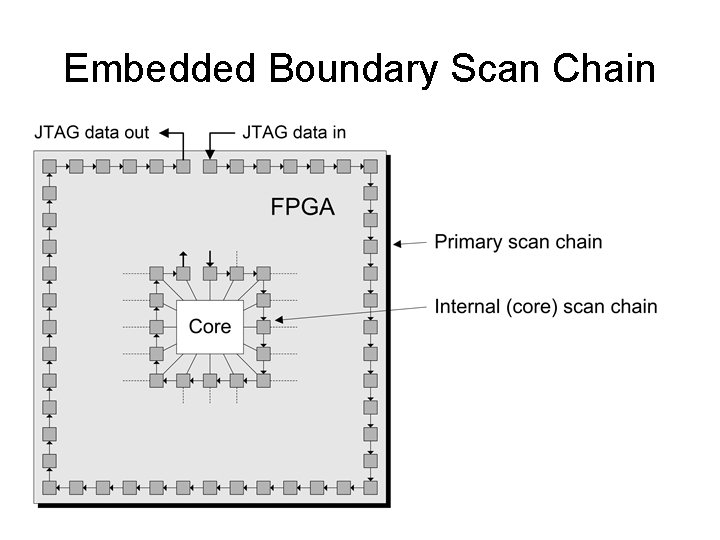

Embedded Boundary Scan Chain

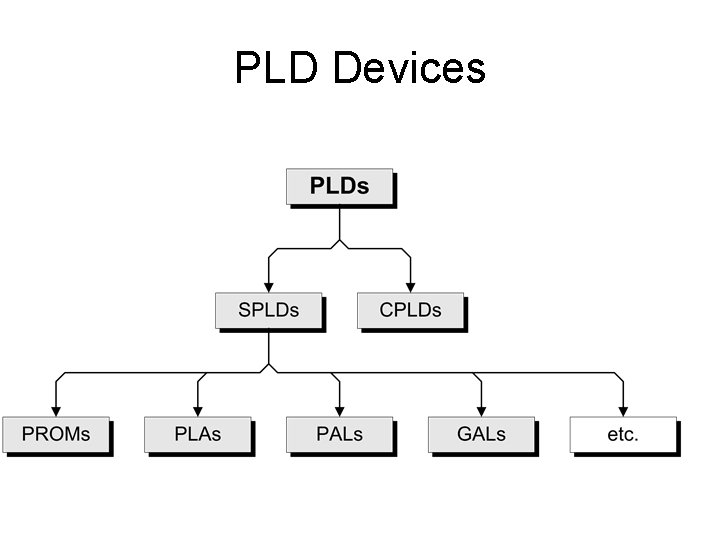

PLD Devices

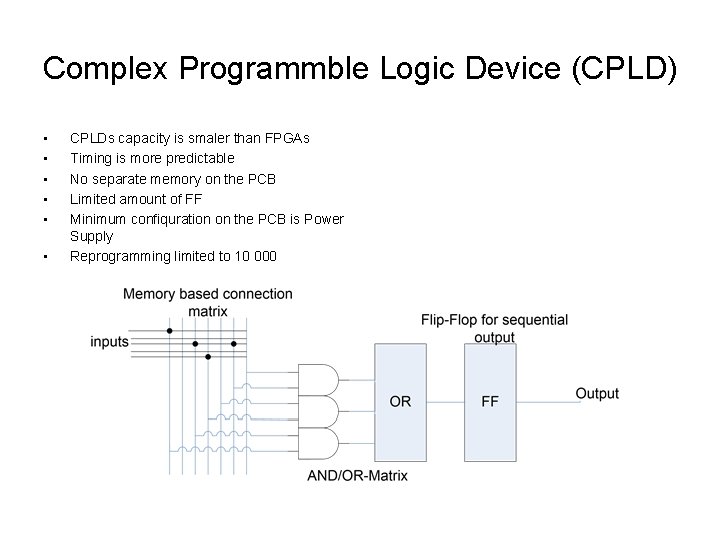

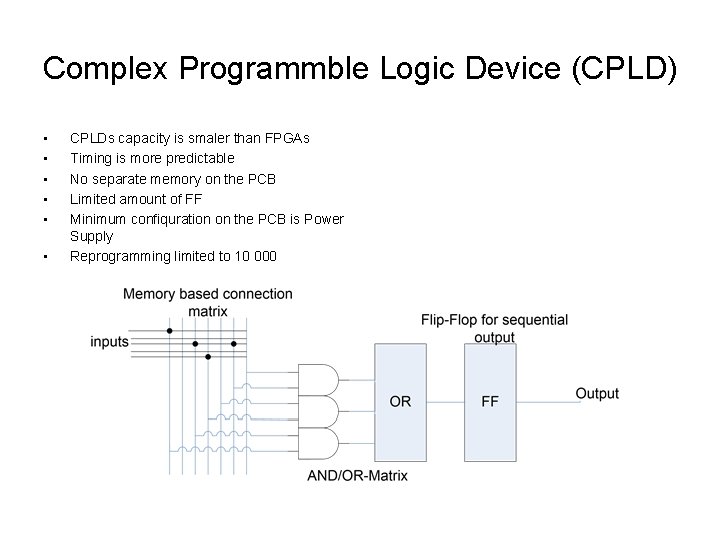

Complex Programmble Logic Device (CPLD) • • • CPLDs capacity is smaler than FPGAs Timing is more predictable No separate memory on the PCB Limited amount of FF Minimum confiquration on the PCB is Power Supply Reprogramming limited to 10 000

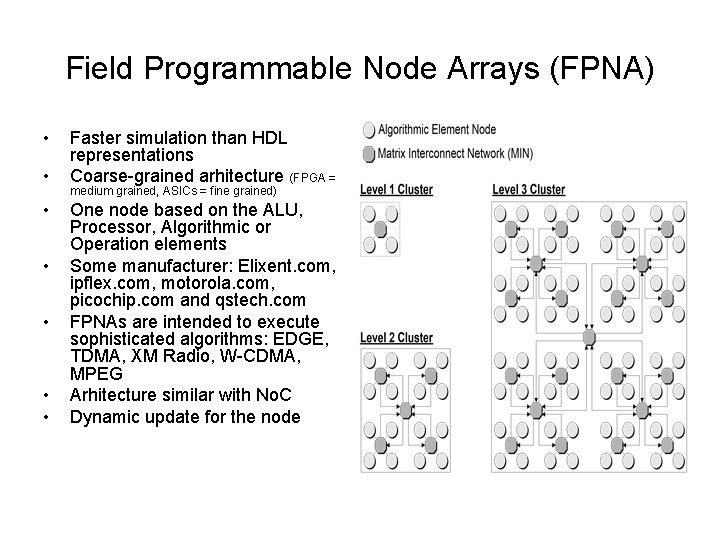

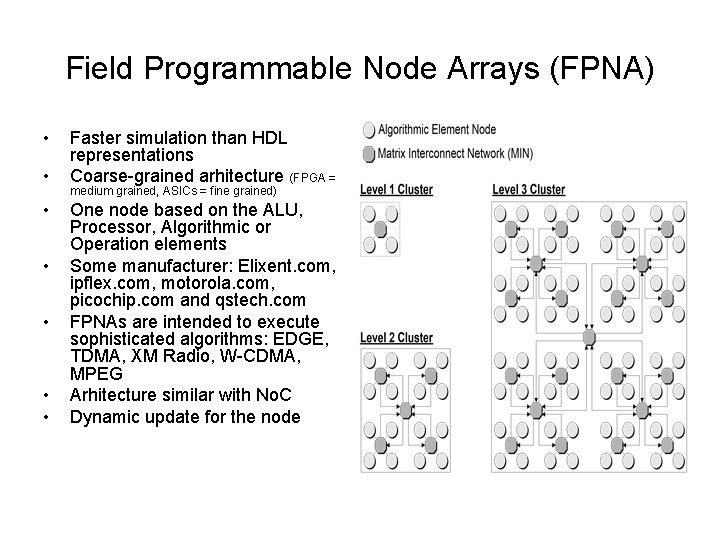

Field Programmable Node Arrays (FPNA) • • Faster simulation than HDL representations Coarse-grained arhitecture (FPGA = medium grained, ASICs = fine grained) One node based on the ALU, Processor, Algorithmic or Operation elements Some manufacturer: Elixent. com, ipflex. com, motorola. com, picochip. com and qstech. com FPNAs are intended to execute sophisticated algorithms: EDGE, TDMA, XM Radio, W-CDMA, MPEG Arhitecture similar with No. C Dynamic update for the node

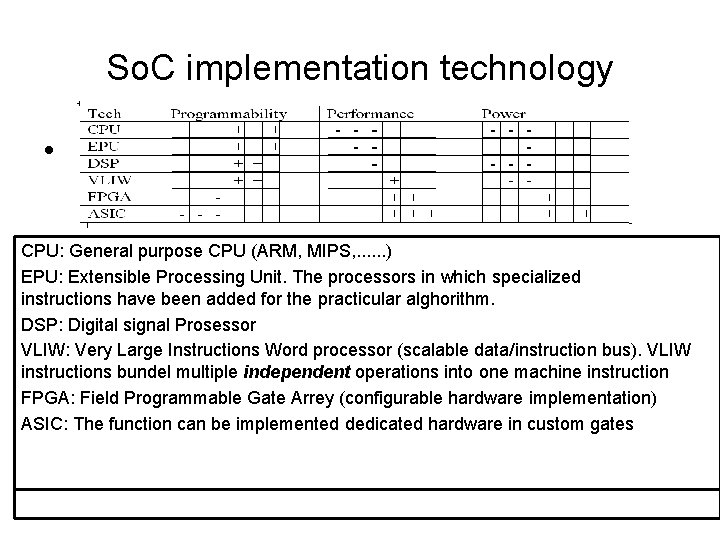

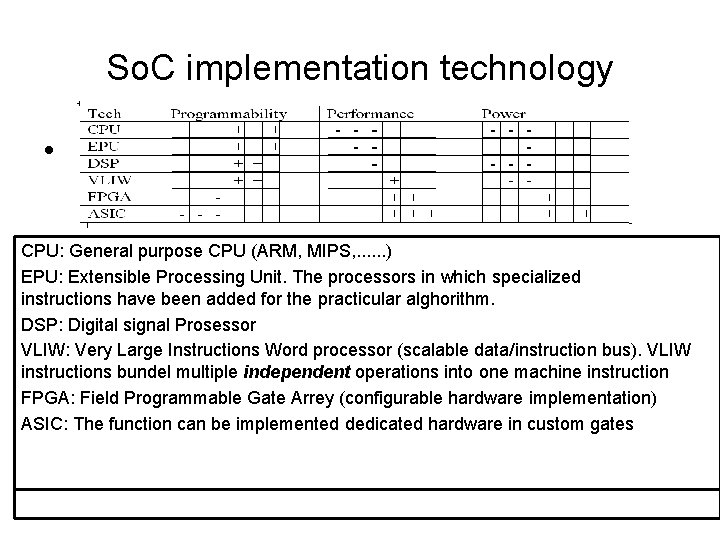

So. C implementation technology • CPU: General purpose CPU (ARM, MIPS, . . . ) EPU: Extensible Processing Unit. The processors in which specialized instructions have been added for the practicular alghorithm. DSP: Digital signal Prosessor VLIW: Very Large Instructions Word processor (scalable data/instruction bus). VLIW instructions bundel multiple independent operations into one machine instruction FPGA: Field Programmable Gate Arrey (configurable hardware implementation) ASIC: The function can be implemented dedicated hardware in custom gates

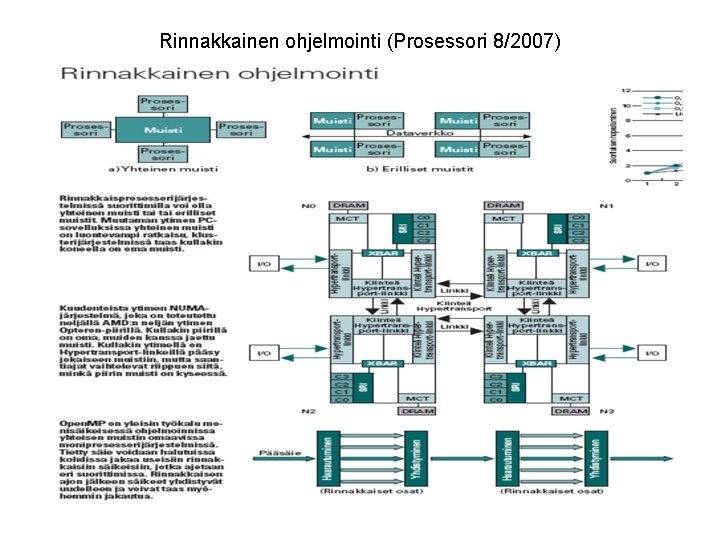

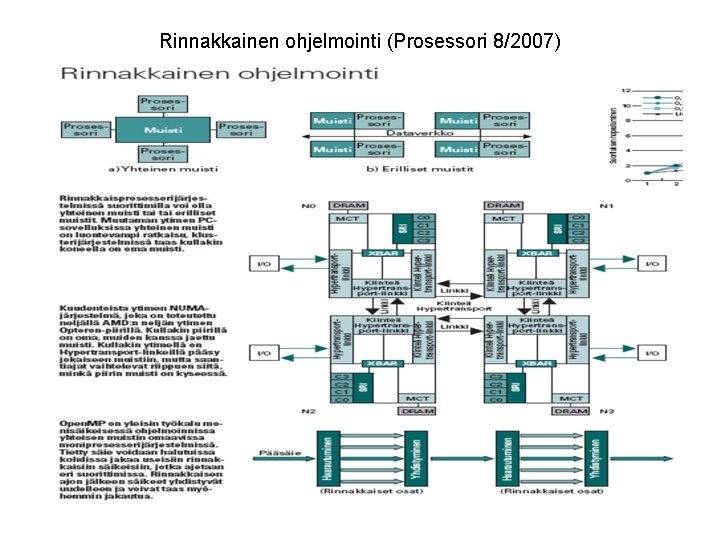

Rinnakkainen ohjelmointi (Prosessori 8/2007)