Moving Arrays 2 Completion of ideas needed for

- Slides: 30

Moving Arrays -- 2 Completion of ideas needed for a general and complete program Final concepts needed for Final DMA , Copyright M. Smith, ECE, University of Calgary, Canada

Tackled today Demonstrating memory to memory DMA ¢ Coding DMA ¢ 2 DMA , Copyright M. Smith, ECE, University of Calgary, Canada 12/14/2021

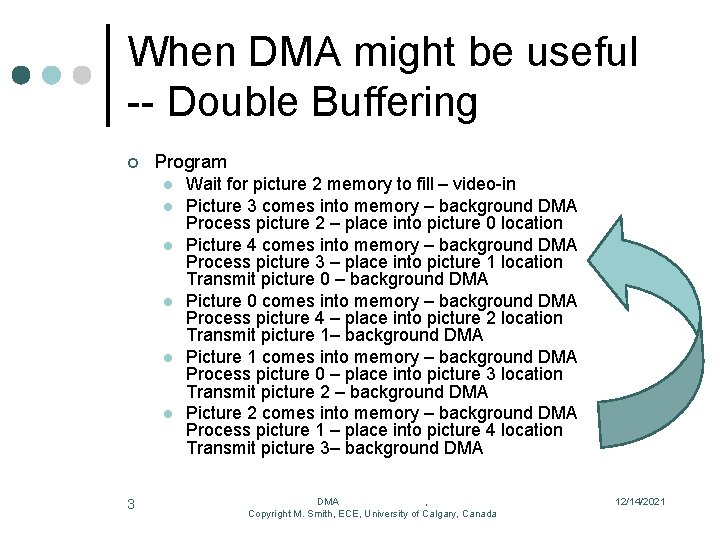

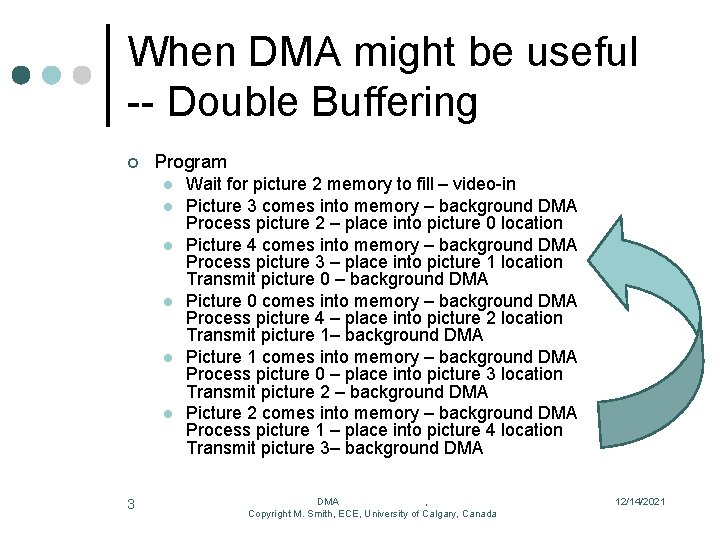

When DMA might be useful -- Double Buffering ¢ Program l l l 3 Wait for picture 2 memory to fill – video-in Picture 3 comes into memory – background DMA Process picture 2 – place into picture 0 location Picture 4 comes into memory – background DMA Process picture 3 – place into picture 1 location Transmit picture 0 – background DMA Picture 0 comes into memory – background DMA Process picture 4 – place into picture 2 location Transmit picture 1– background DMA Picture 1 comes into memory – background DMA Process picture 0 – place into picture 3 location Transmit picture 2 – background DMA Picture 2 comes into memory – background DMA Process picture 1 – place into picture 4 location Transmit picture 3– background DMA , Copyright M. Smith, ECE, University of Calgary, Canada 12/14/2021

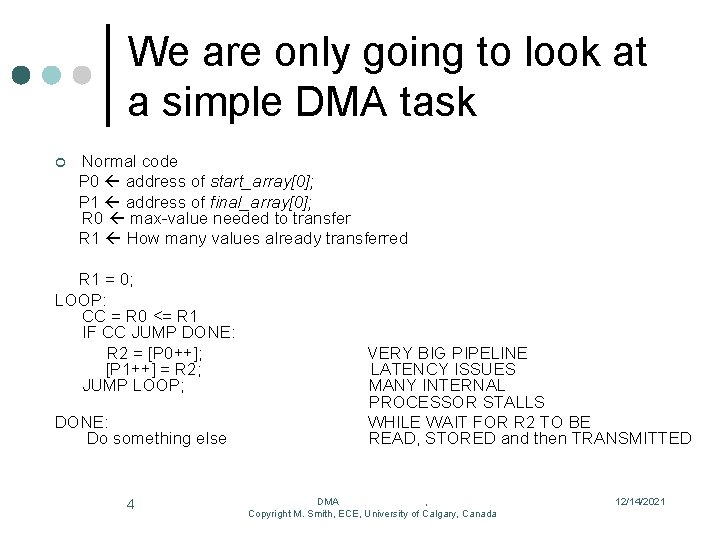

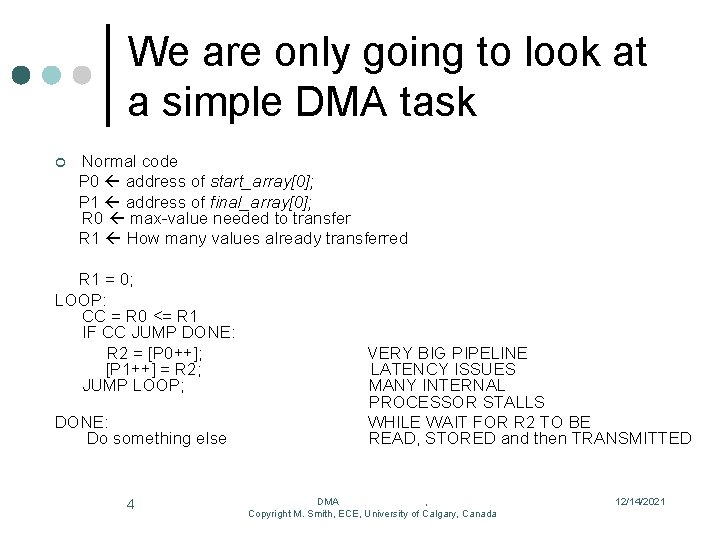

We are only going to look at a simple DMA task ¢ Normal code P 0 address of start_array[0]; P 1 address of final_array[0]; R 0 max-value needed to transfer R 1 How many values already transferred R 1 = 0; LOOP: CC = R 0 <= R 1 IF CC JUMP DONE: R 2 = [P 0++]; [P 1++] = R 2; JUMP LOOP; DONE: Do something else 4 VERY BIG PIPELINE LATENCY ISSUES MANY INTERNAL PROCESSOR STALLS WHILE WAIT FOR R 2 TO BE READ, STORED and then TRANSMITTED DMA , Copyright M. Smith, ECE, University of Calgary, Canada 12/14/2021

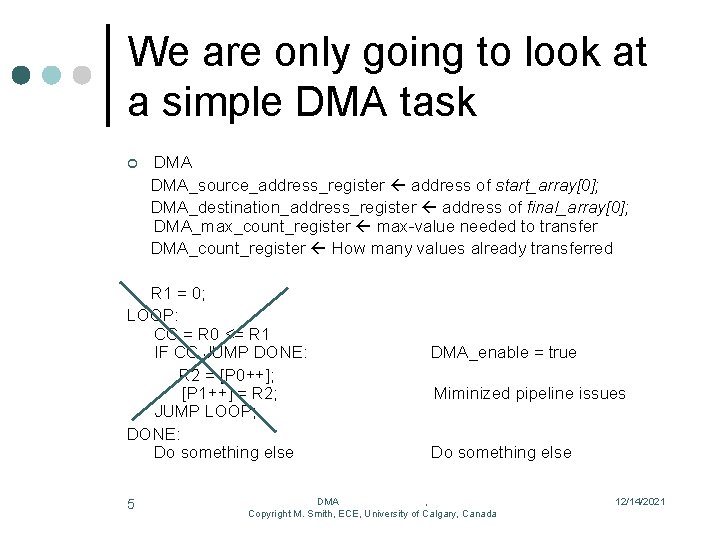

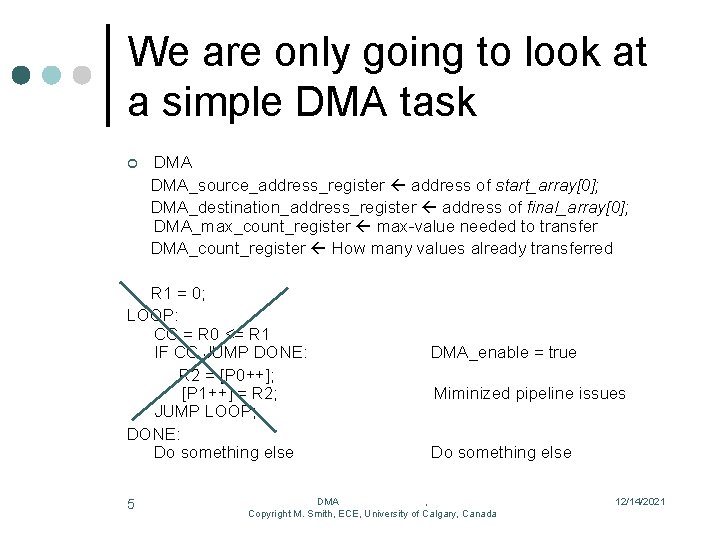

We are only going to look at a simple DMA task ¢ DMA_source_address_register address of start_array[0]; DMA_destination_address_register address of final_array[0]; DMA_max_count_register max-value needed to transfer DMA_count_register How many values already transferred R 1 = 0; LOOP: CC = R 0 <= R 1 IF CC JUMP DONE: R 2 = [P 0++]; [P 1++] = R 2; JUMP LOOP; DONE: Do something else 5 DMA_enable = true Miminized pipeline issues Do something else DMA , Copyright M. Smith, ECE, University of Calgary, Canada 12/14/2021

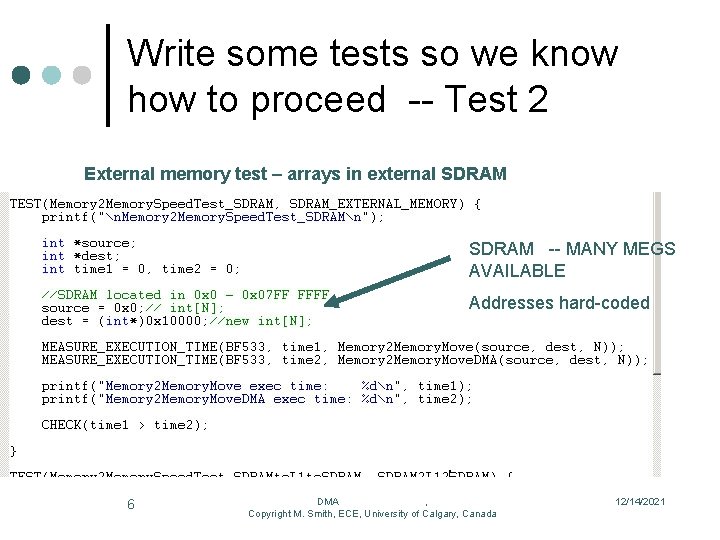

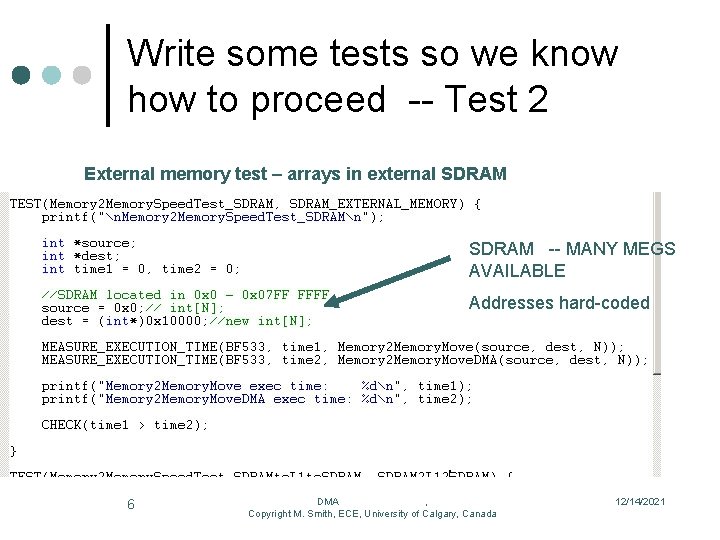

Write some tests so we know how to proceed -- Test 2 External memory test – arrays in external SDRAM -- MANY MEGS AVAILABLE Addresses hard-coded 6 DMA , Copyright M. Smith, ECE, University of Calgary, Canada 12/14/2021

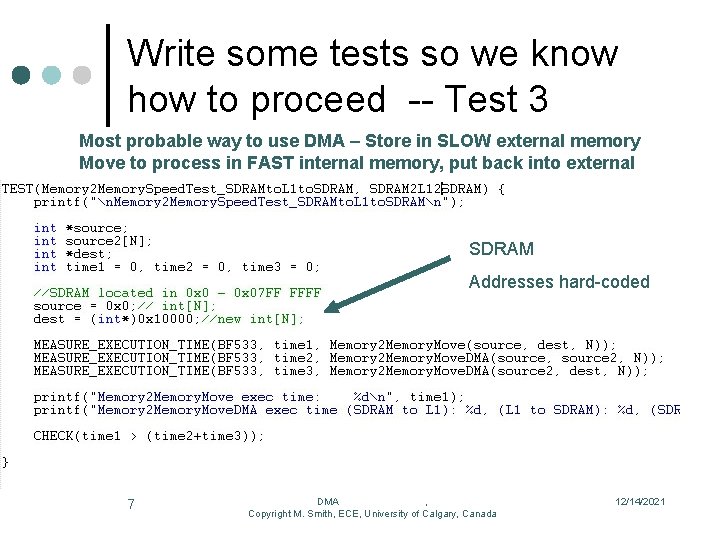

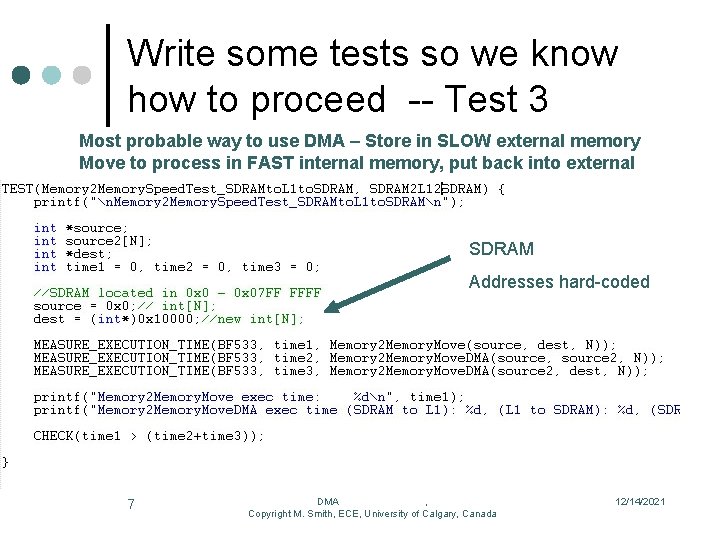

Write some tests so we know how to proceed -- Test 3 Most probable way to use DMA – Store in SLOW external memory Move to process in FAST internal memory, put back into external SDRAM Addresses hard-coded 7 DMA , Copyright M. Smith, ECE, University of Calgary, Canada 12/14/2021

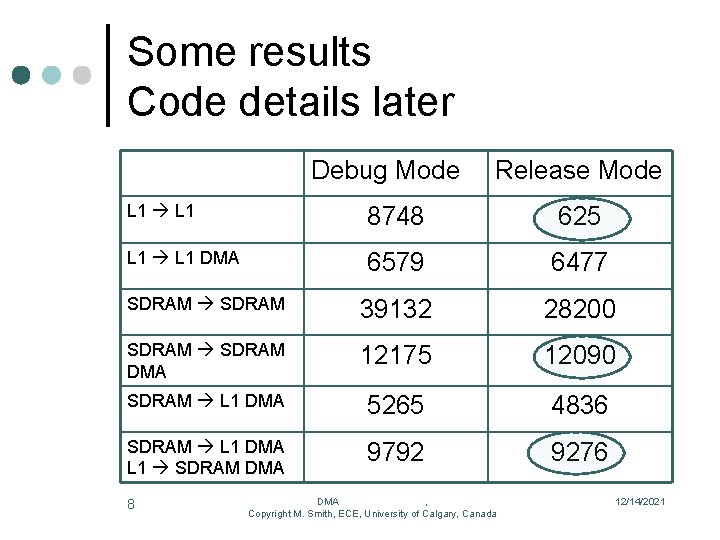

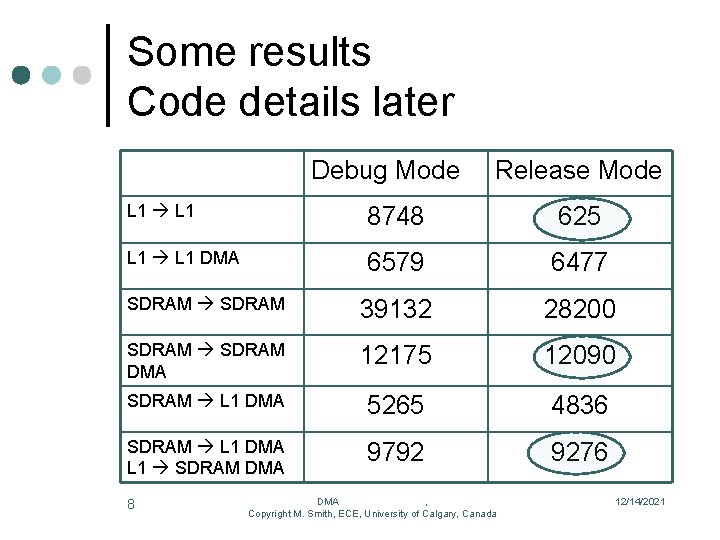

Some results Code details later Debug Mode Release Mode L 1 8748 625 L 1 DMA 6579 6477 SDRAM 39132 28200 SDRAM DMA 12175 12090 SDRAM L 1 DMA 5265 4836 SDRAM L 1 DMA L 1 SDRAM DMA 9792 9276 8 DMA , Copyright M. Smith, ECE, University of Calgary, Canada 12/14/2021

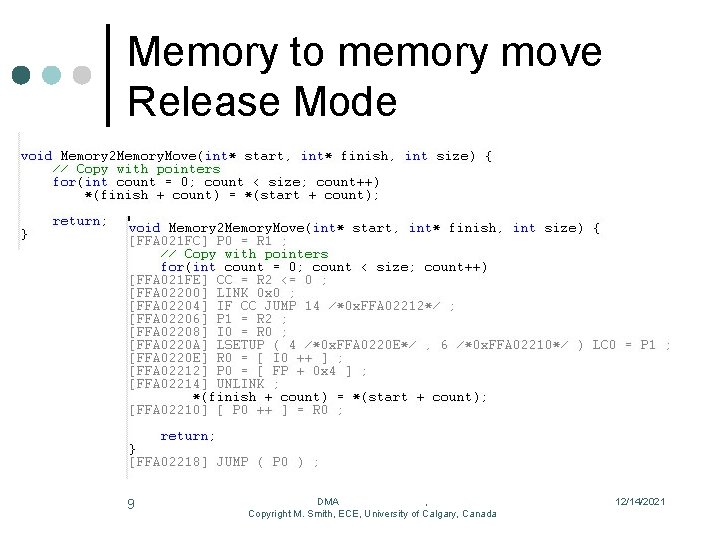

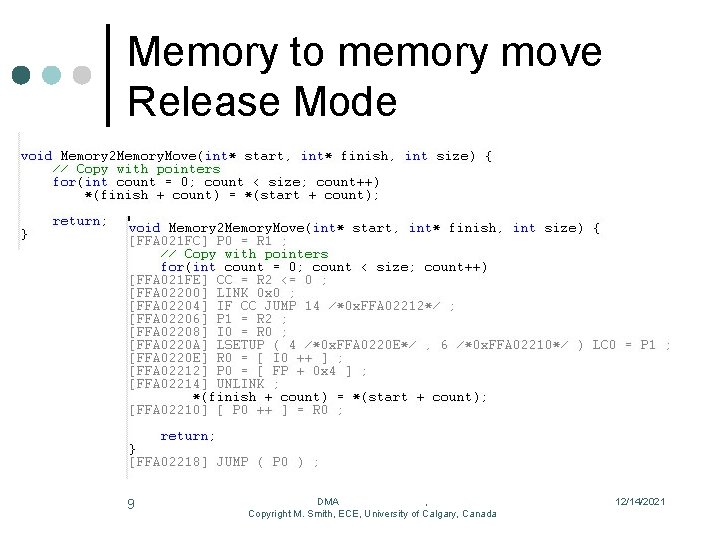

Memory to memory move Release Mode 9 DMA , Copyright M. Smith, ECE, University of Calgary, Canada 12/14/2021

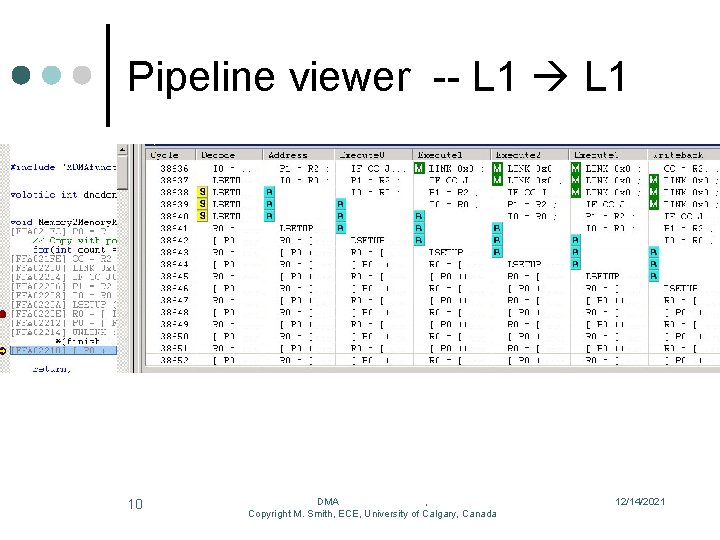

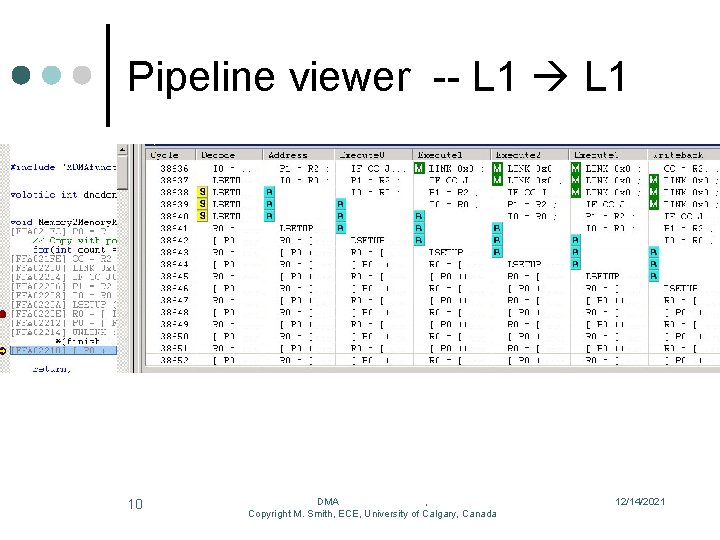

Pipeline viewer -- L 1 10 DMA , Copyright M. Smith, ECE, University of Calgary, Canada 12/14/2021

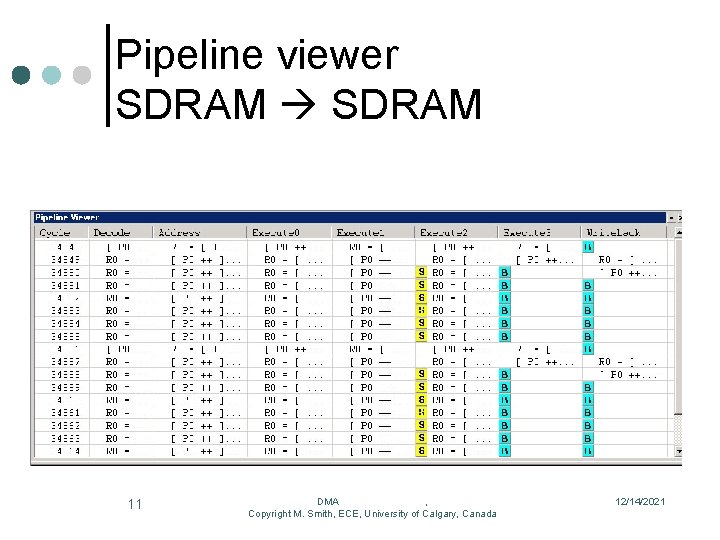

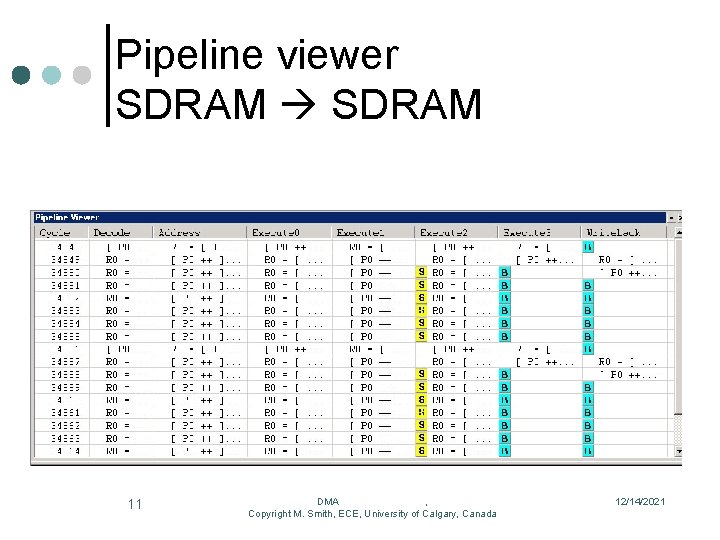

Pipeline viewer SDRAM 11 DMA , Copyright M. Smith, ECE, University of Calgary, Canada 12/14/2021

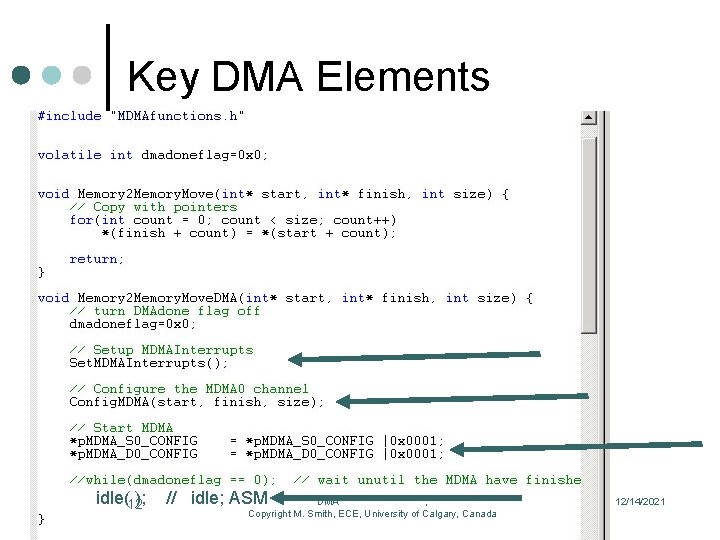

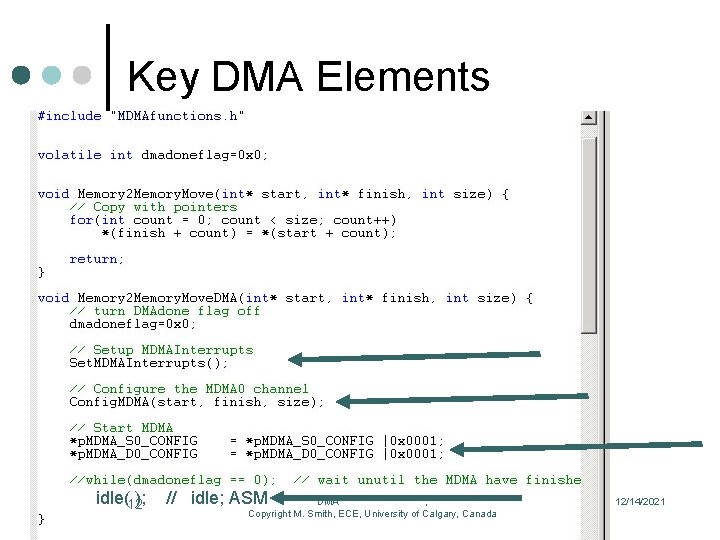

Key DMA Elements idle(12); // idle; ASM DMA , Copyright M. Smith, ECE, University of Calgary, Canada 12/14/2021

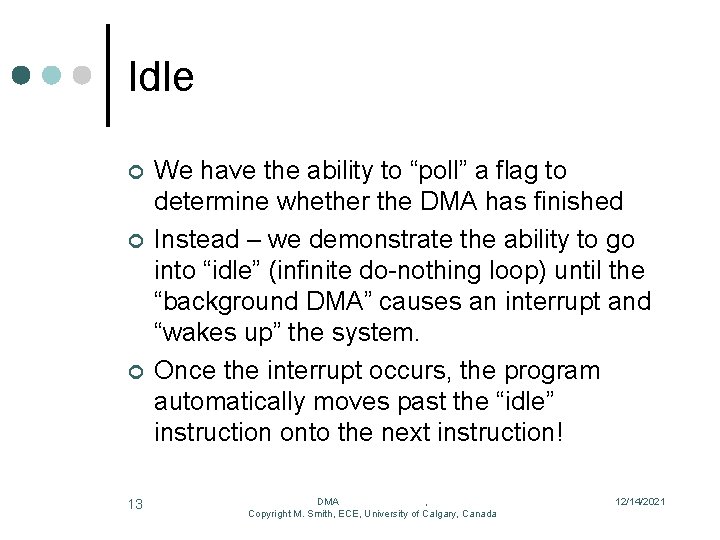

Idle ¢ ¢ ¢ 13 We have the ability to “poll” a flag to determine whether the DMA has finished Instead – we demonstrate the ability to go into “idle” (infinite do-nothing loop) until the “background DMA” causes an interrupt and “wakes up” the system. Once the interrupt occurs, the program automatically moves past the “idle” instruction onto the next instruction! DMA , Copyright M. Smith, ECE, University of Calgary, Canada 12/14/2021

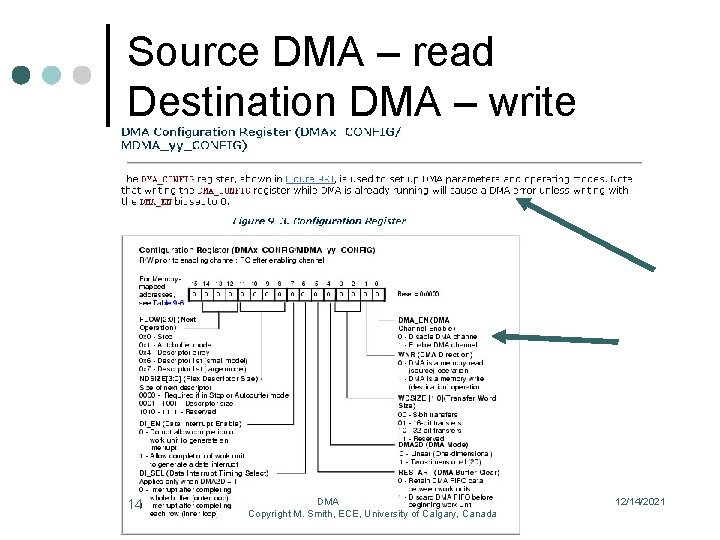

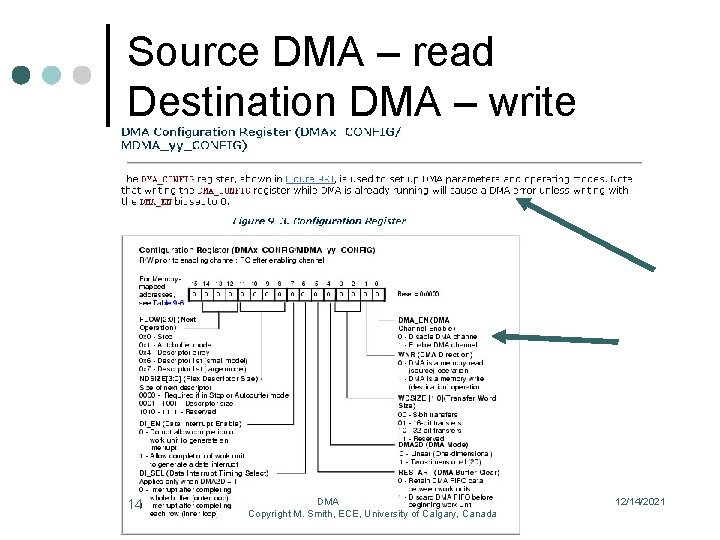

Source DMA – read Destination DMA – write 14 DMA , Copyright M. Smith, ECE, University of Calgary, Canada 12/14/2021

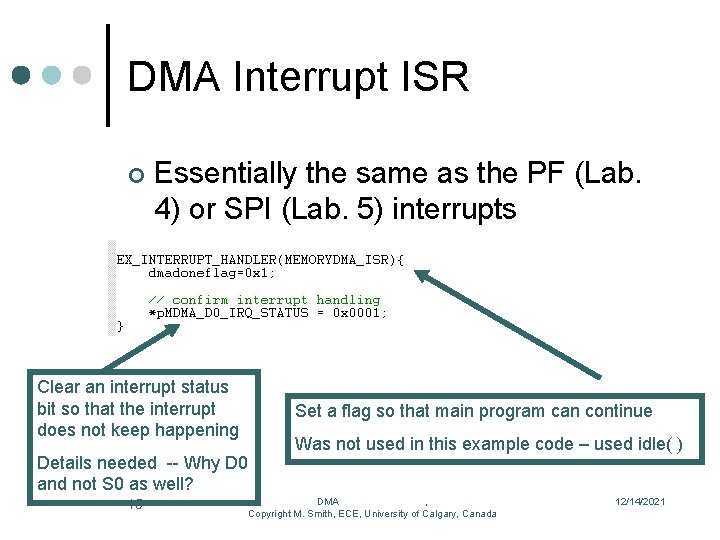

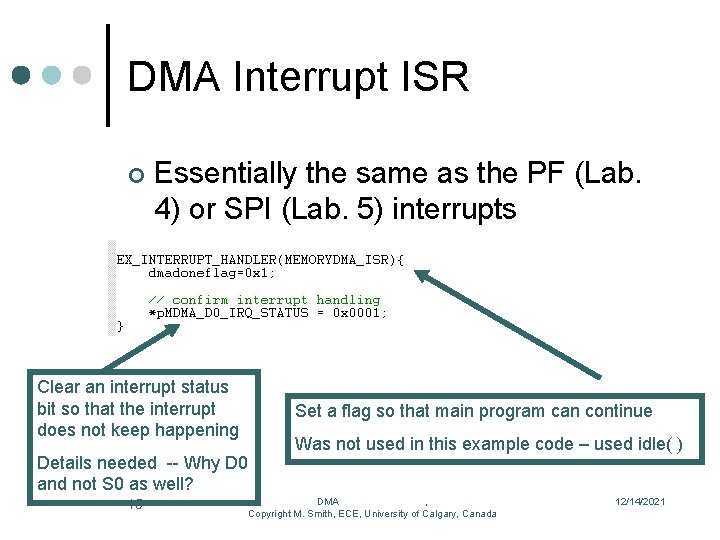

DMA Interrupt ISR ¢ Essentially the same as the PF (Lab. 4) or SPI (Lab. 5) interrupts Clear an interrupt status bit so that the interrupt does not keep happening Set a flag so that main program can continue Details needed -- Why D 0 and not S 0 as well? 15 Was not used in this example code – used idle( ) DMA , Copyright M. Smith, ECE, University of Calgary, Canada 12/14/2021

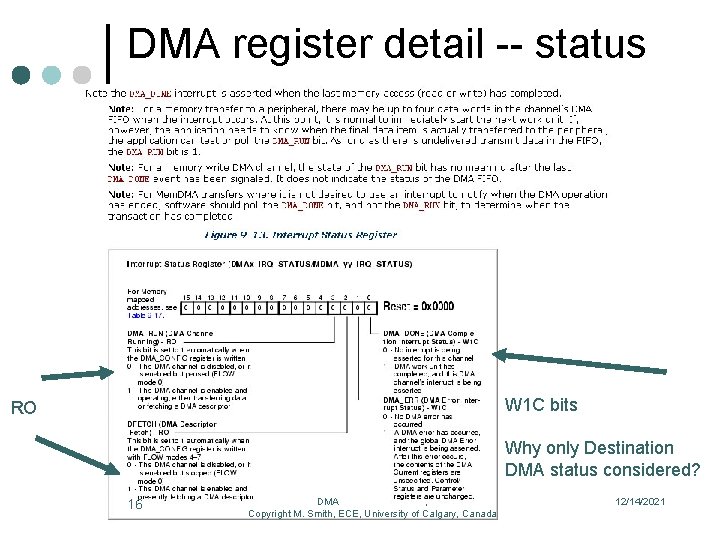

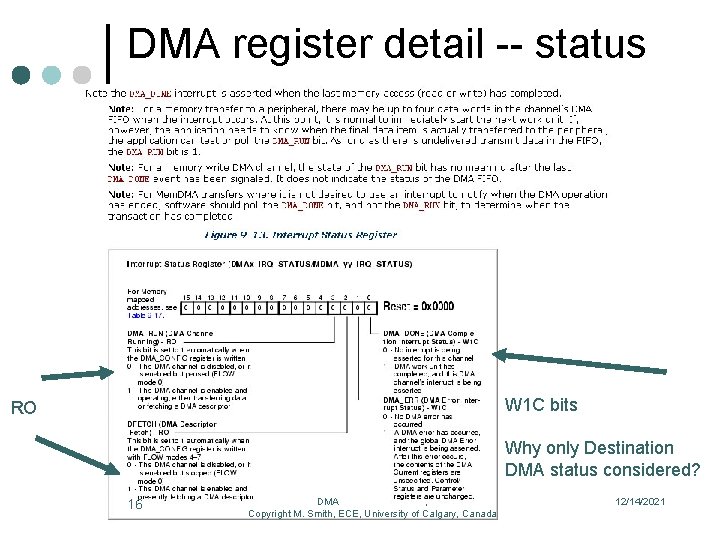

DMA register detail -- status W 1 C bits RO Why only Destination DMA status considered? 16 DMA , Copyright M. Smith, ECE, University of Calgary, Canada 12/14/2021

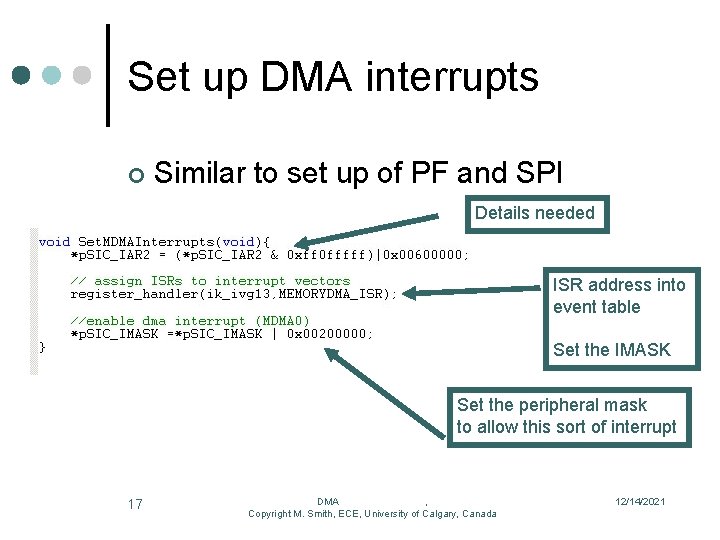

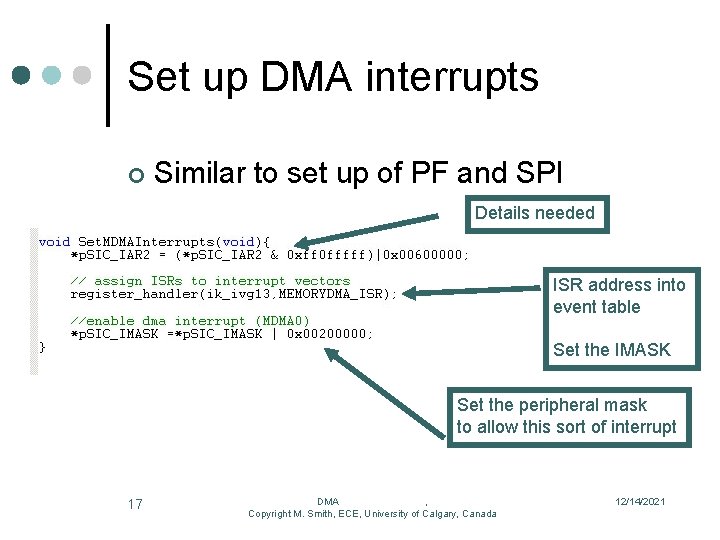

Set up DMA interrupts ¢ Similar to set up of PF and SPI Details needed ISR address into event table Set the IMASK Set the peripheral mask to allow this sort of interrupt 17 DMA , Copyright M. Smith, ECE, University of Calgary, Canada 12/14/2021

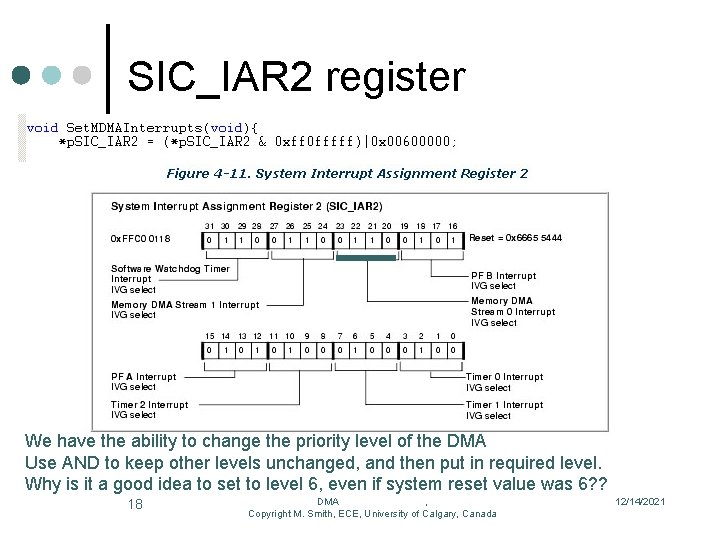

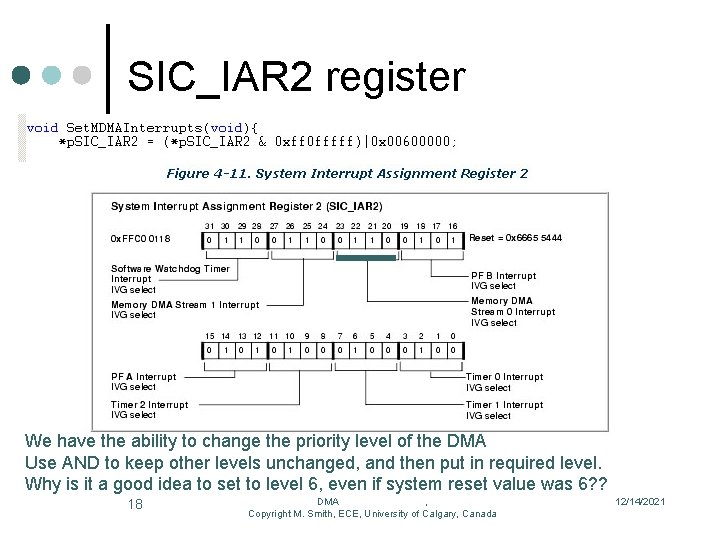

SIC_IAR 2 register We have the ability to change the priority level of the DMA Use AND to keep other levels unchanged, and then put in required level. Why is it a good idea to set to level 6, even if system reset value was 6? ? 18 DMA , Copyright M. Smith, ECE, University of Calgary, Canada 12/14/2021

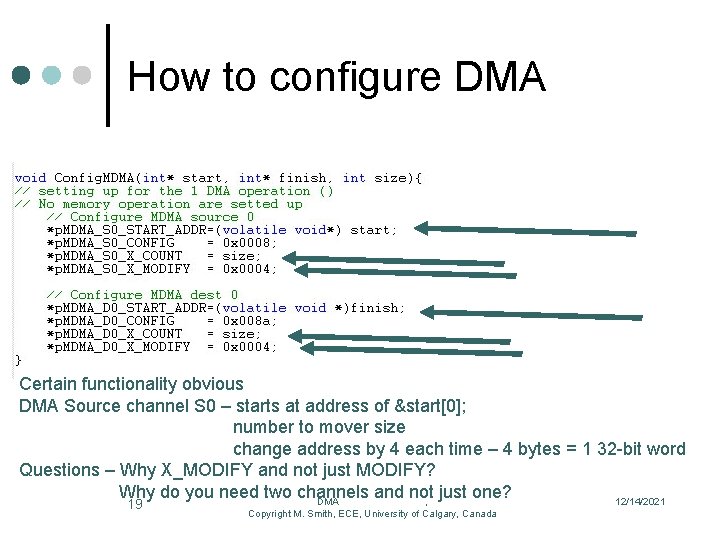

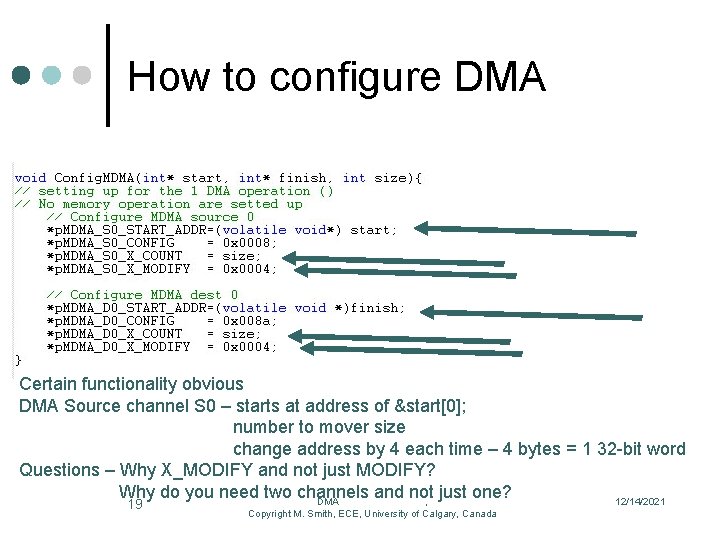

How to configure DMA Certain functionality obvious DMA Source channel S 0 – starts at address of &start[0]; number to mover size change address by 4 each time – 4 bytes = 1 32 -bit word Questions – Why X_MODIFY and not just MODIFY? Why do you need two channels and not, just one? DMA 12/14/2021 19 Copyright M. Smith, ECE, University of Calgary, Canada

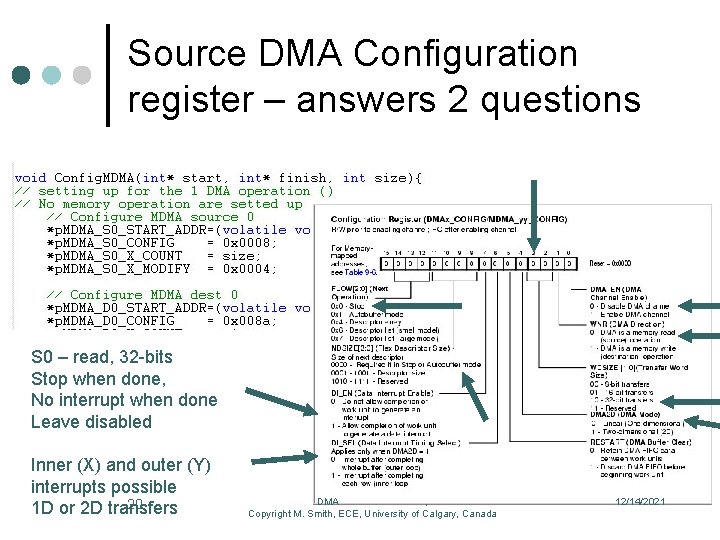

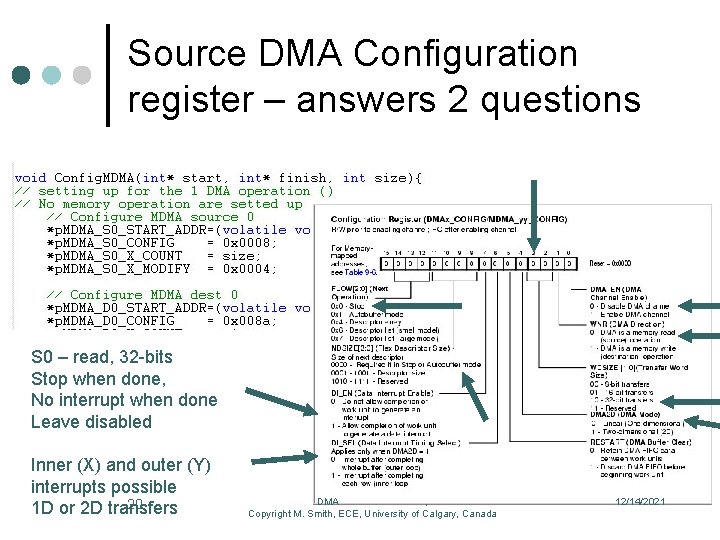

Source DMA Configuration register – answers 2 questions S 0 – read, 32 -bits Stop when done, No interrupt when done Leave disabled Inner (X) and outer (Y) interrupts possible 20 1 D or 2 D transfers DMA , Copyright M. Smith, ECE, University of Calgary, Canada 12/14/2021

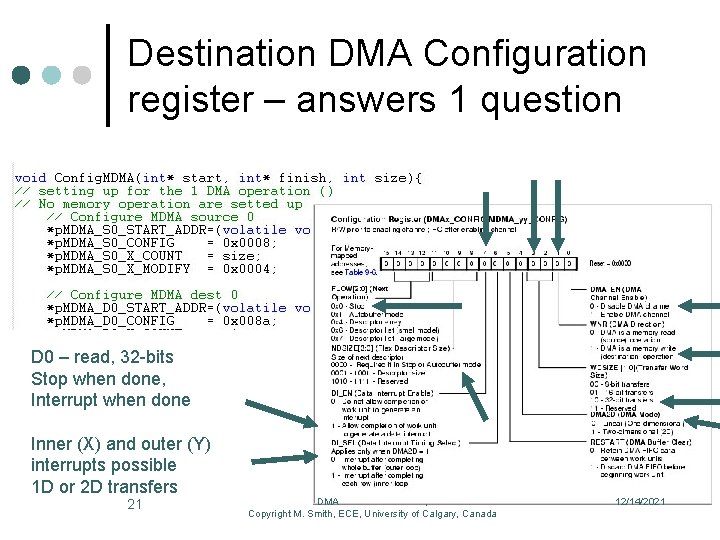

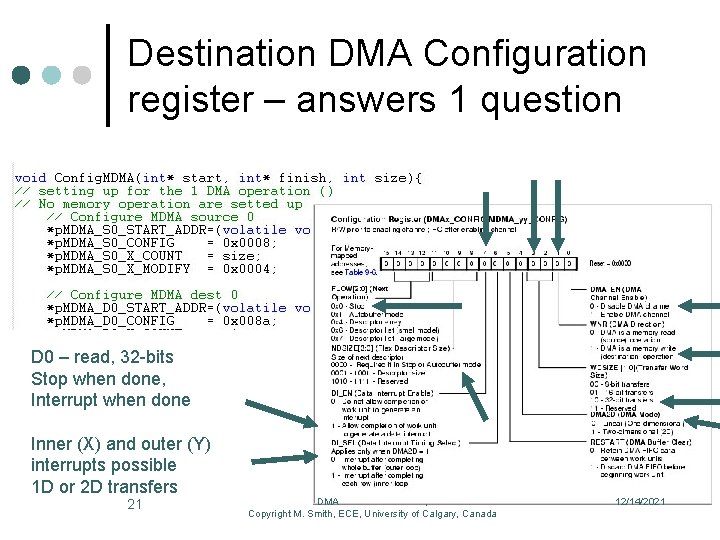

Destination DMA Configuration register – answers 1 question D 0 – read, 32 -bits Stop when done, Interrupt when done Inner (X) and outer (Y) interrupts possible 1 D or 2 D transfers 21 DMA , Copyright M. Smith, ECE, University of Calgary, Canada 12/14/2021

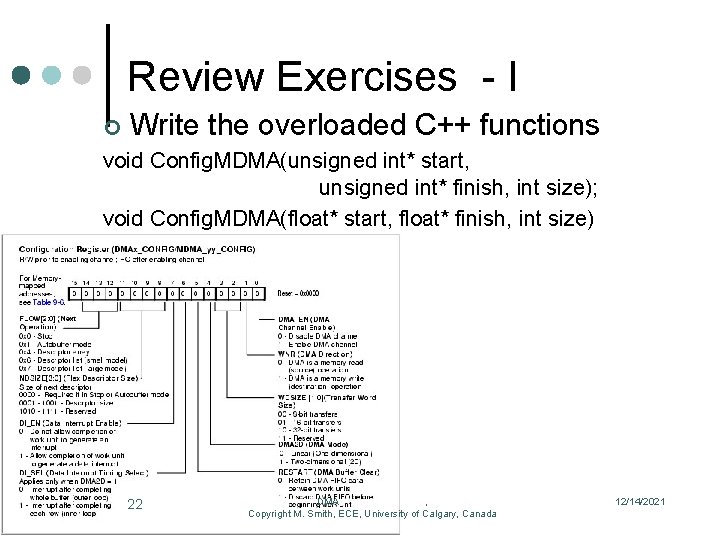

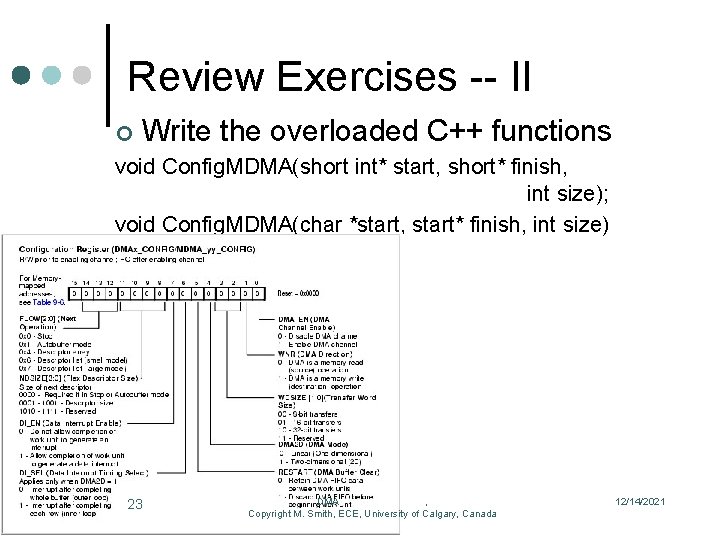

Review Exercises - I ¢ Write the overloaded C++ functions void Config. MDMA(unsigned int* start, unsigned int* finish, int size); void Config. MDMA(float* start, float* finish, int size) 22 DMA , Copyright M. Smith, ECE, University of Calgary, Canada 12/14/2021

Review Exercises -- II ¢ Write the overloaded C++ functions void Config. MDMA(short int* start, short* finish, int size); void Config. MDMA(char *start, start* finish, int size) 23 DMA , Copyright M. Smith, ECE, University of Calgary, Canada 12/14/2021

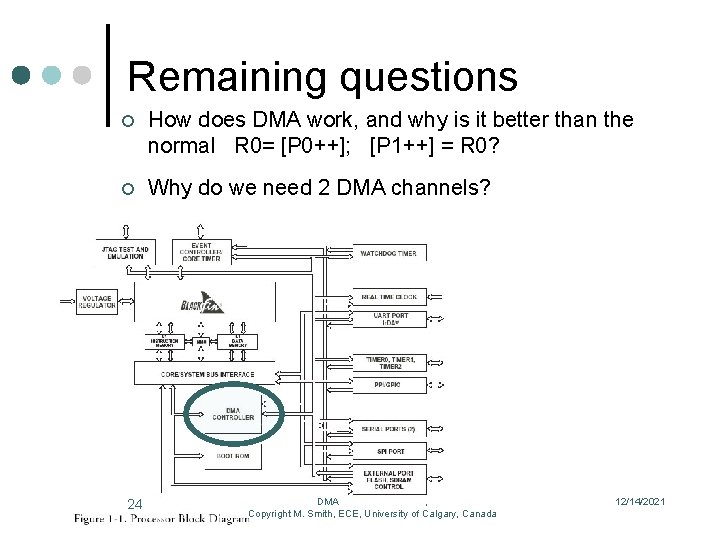

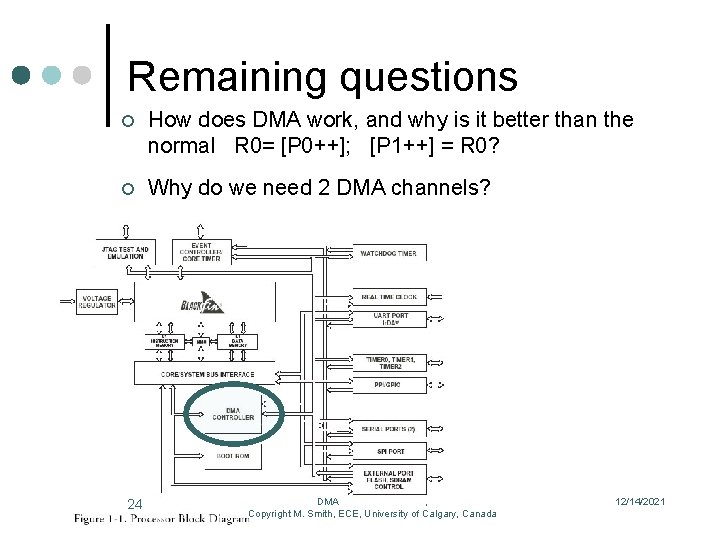

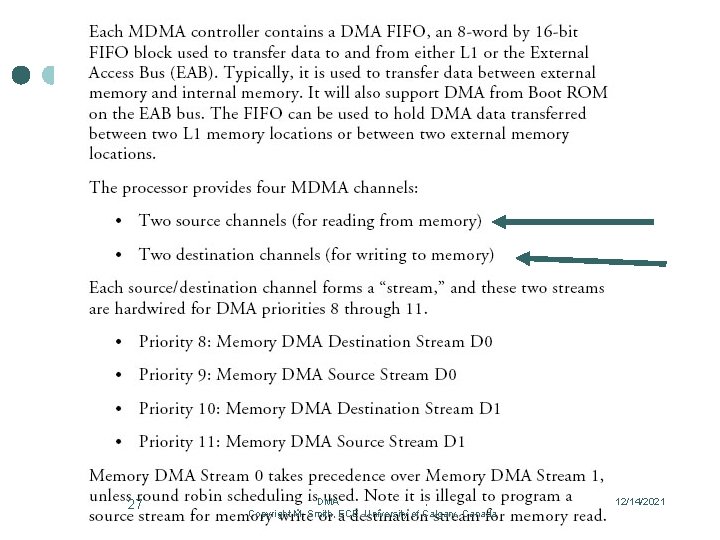

Remaining questions ¢ How does DMA work, and why is it better than the normal R 0= [P 0++]; [P 1++] = R 0? ¢ Why do we need 2 DMA channels? 24 DMA , Copyright M. Smith, ECE, University of Calgary, Canada 12/14/2021

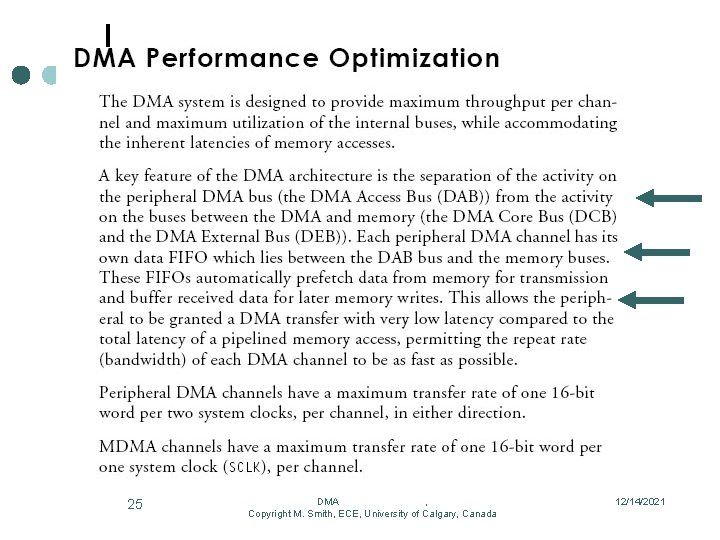

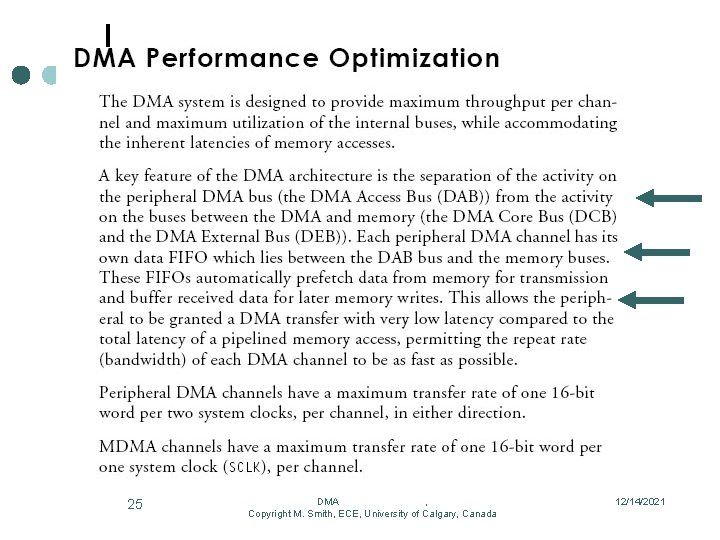

25 DMA , Copyright M. Smith, ECE, University of Calgary, Canada 12/14/2021

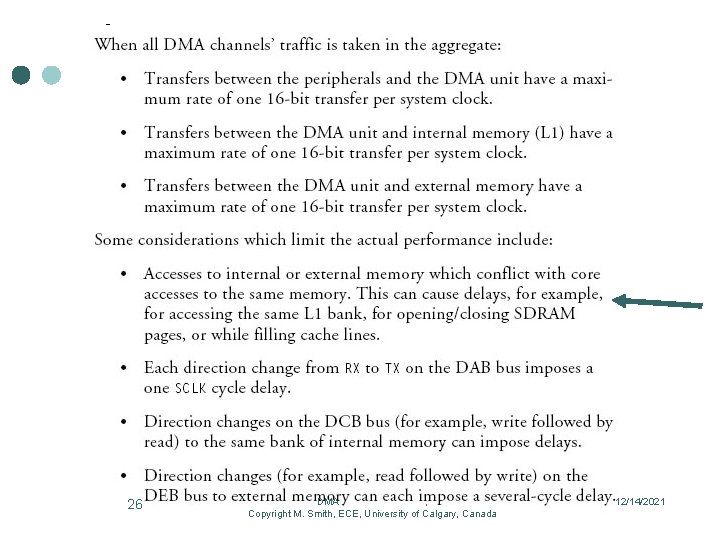

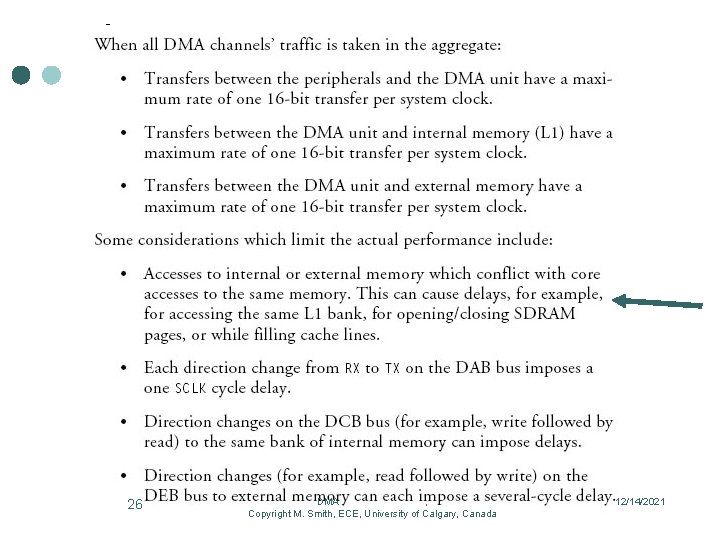

26 DMA , Copyright M. Smith, ECE, University of Calgary, Canada 12/14/2021

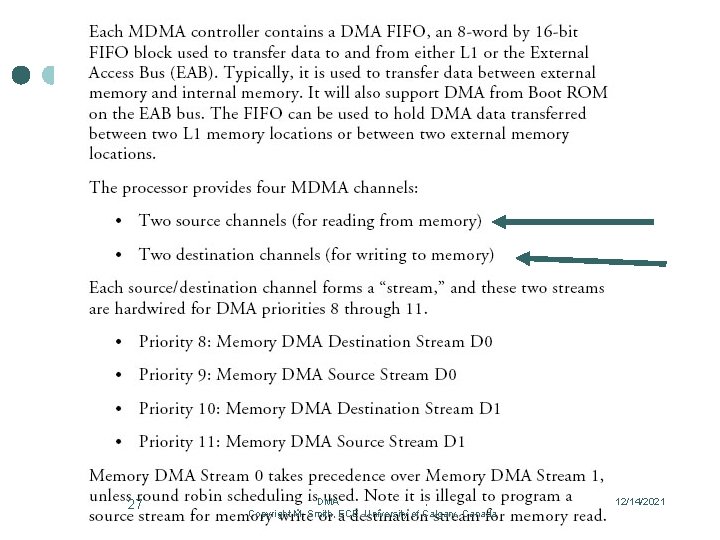

27 DMA , Copyright M. Smith, ECE, University of Calgary, Canada 12/14/2021

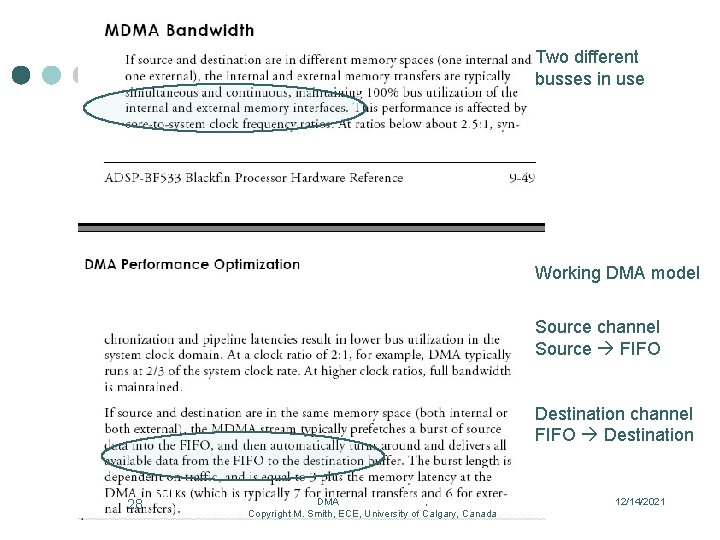

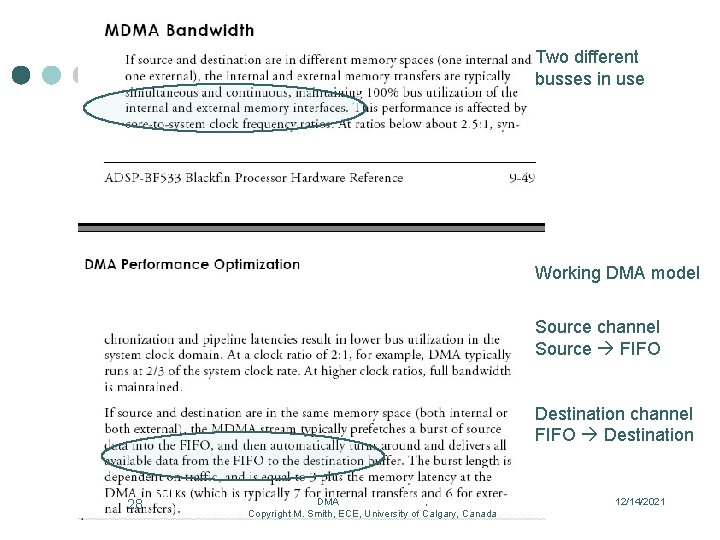

Two different busses in use Working DMA model Source channel Source FIFO Destination channel FIFO Destination 28 DMA , Copyright M. Smith, ECE, University of Calgary, Canada 12/14/2021

Tackled today Demonstrating memory to memory DMA ¢ Coding DMA ¢ 29 DMA , Copyright M. Smith, ECE, University of Calgary, Canada 12/14/2021

¢ Information taken from Analog Devices On-line Manuals with permission http: //www. analog. com/processors/resources/technical. Library/manuals/ ¢ Information furnished by Analog Devices is believed to be accurate and reliable. However, Analog Devices assumes no responsibility for its use or for any infringement of any patent other rights of any third party which may result from its use. No license is granted by implication or otherwise under any patent or patent right of Analog Devices. Copyright Analog Devices, Inc. All rights reserved. 30 DMA , Copyright M. Smith, ECE, University of Calgary, Canada 12/14/2021