MIPS processor continued Branch Instruction Beq has three

MIPS processor continued

Branch Instruction • Beq has three operands, two registers that are compared for equality and a 16 -bit offset used to compute the branch-target address – beq $rs, $rt, offset • opcode (6 bits) rs (5 bits) rt (5 bits) offset (16 bits) – Note that the 16 -bit offset is given in terms of instructions, not bytes and is relative to PC + 4 11/18/2007 7: 39: 42 PM week 13 -1. ppt 2

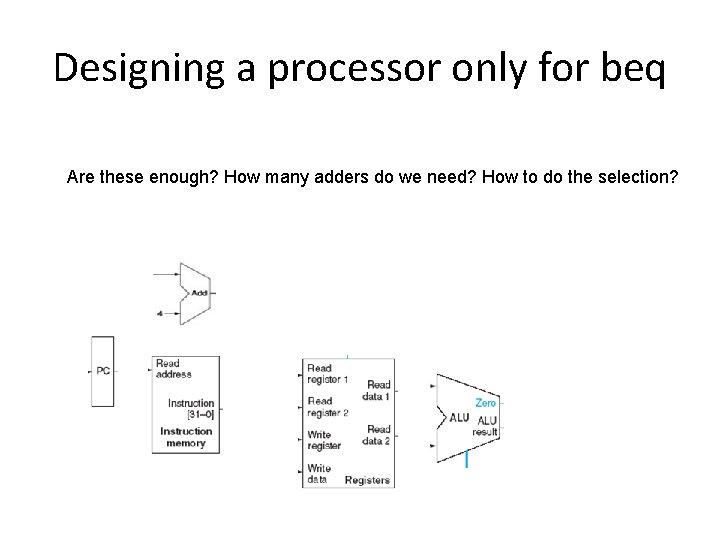

Designing a processor only for beq Are these enough? How many adders do we need? How to do the selection?

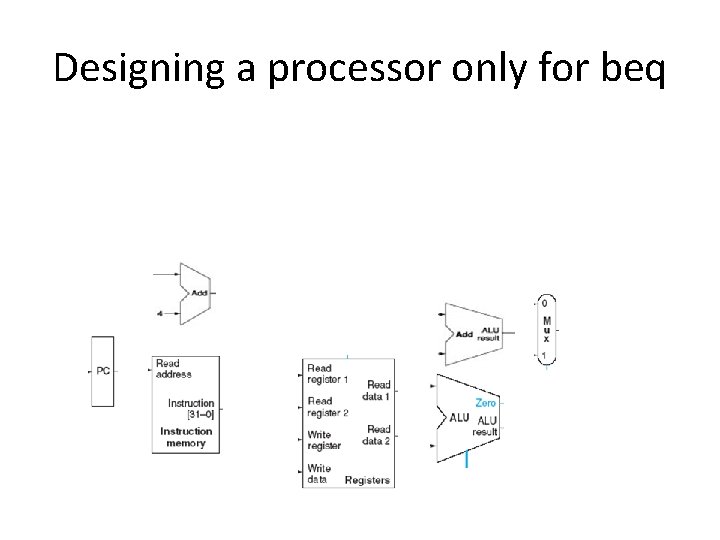

Designing a processor only for beq

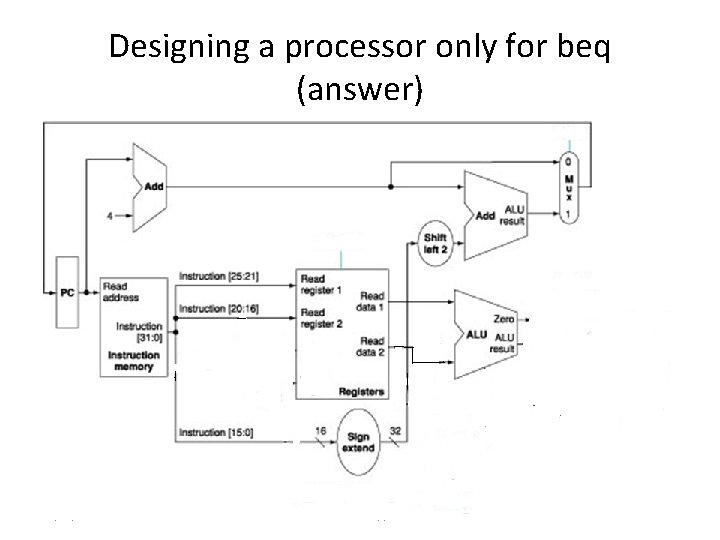

Designing a processor only for beq (answer) 11/18/2007 7: 39: 43 PM week 13 -1. ppt 5

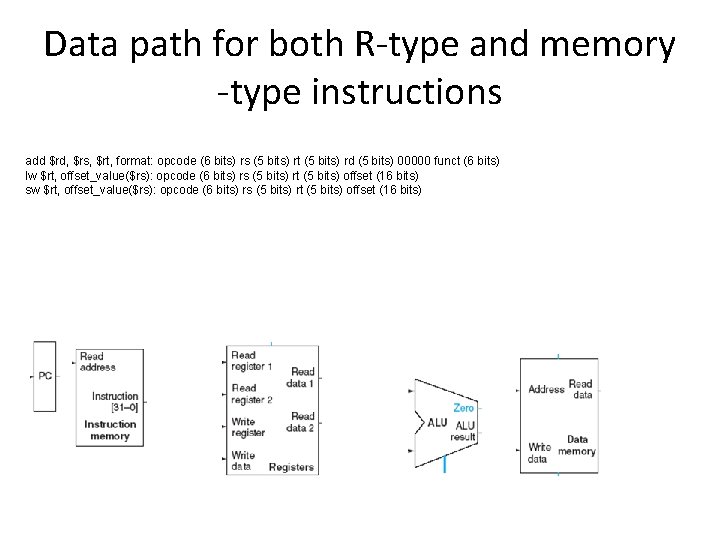

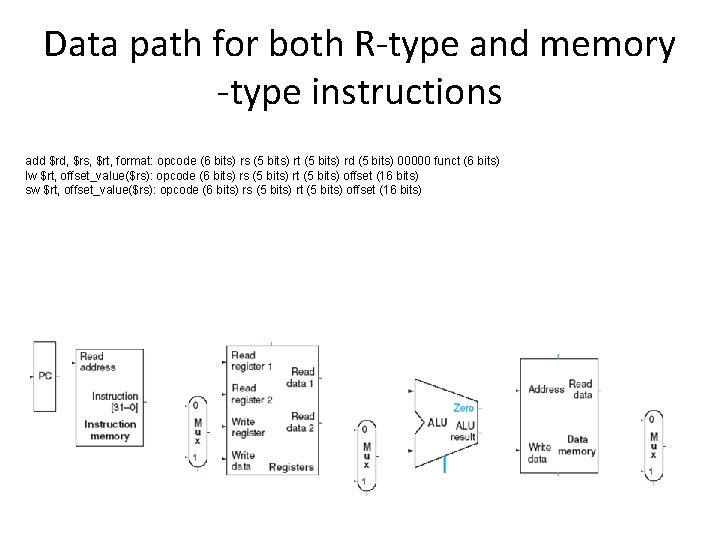

Data path for both R-type and memory -type instructions add $rd, $rs, $rt, format: opcode (6 bits) rs (5 bits) rt (5 bits) rd (5 bits) 00000 funct (6 bits) lw $rt, offset_value($rs): opcode (6 bits) rs (5 bits) rt (5 bits) offset (16 bits) sw $rt, offset_value($rs): opcode (6 bits) rs (5 bits) rt (5 bits) offset (16 bits)

Data path for both R-type and memory -type instructions add $rd, $rs, $rt, format: opcode (6 bits) rs (5 bits) rt (5 bits) rd (5 bits) 00000 funct (6 bits) lw $rt, offset_value($rs): opcode (6 bits) rs (5 bits) rt (5 bits) offset (16 bits) sw $rt, offset_value($rs): opcode (6 bits) rs (5 bits) rt (5 bits) offset (16 bits)

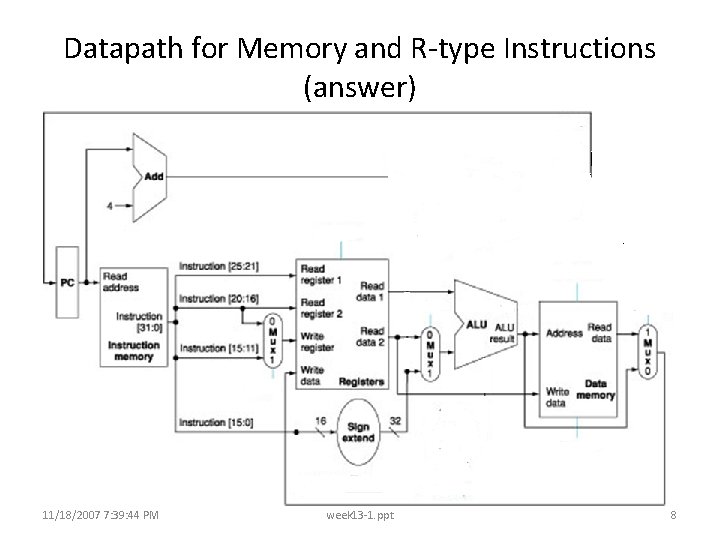

Datapath for Memory and R-type Instructions (answer) 11/18/2007 7: 39: 44 PM week 13 -1. ppt 8

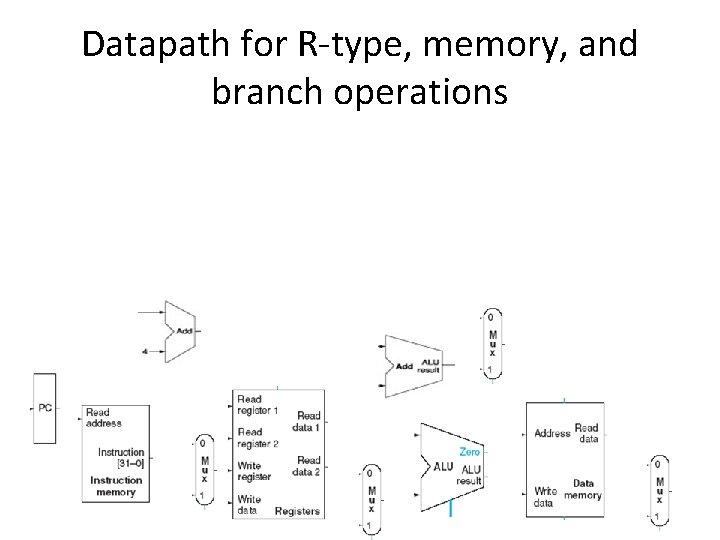

Datapath for R-type, memory, and branch operations

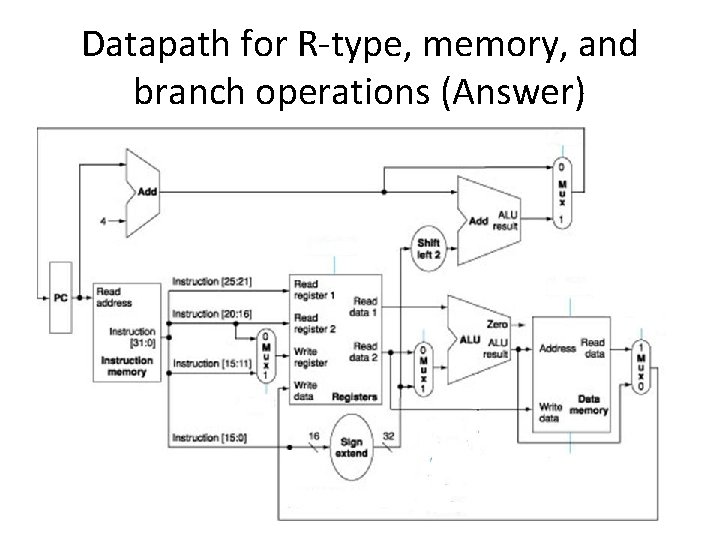

Datapath for R-type, memory, and branch operations (Answer)

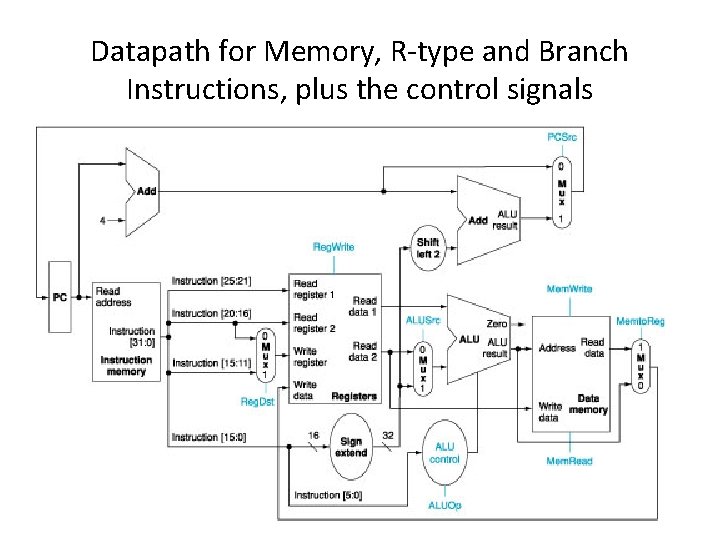

Datapath for Memory, R-type and Branch Instructions, plus the control signals

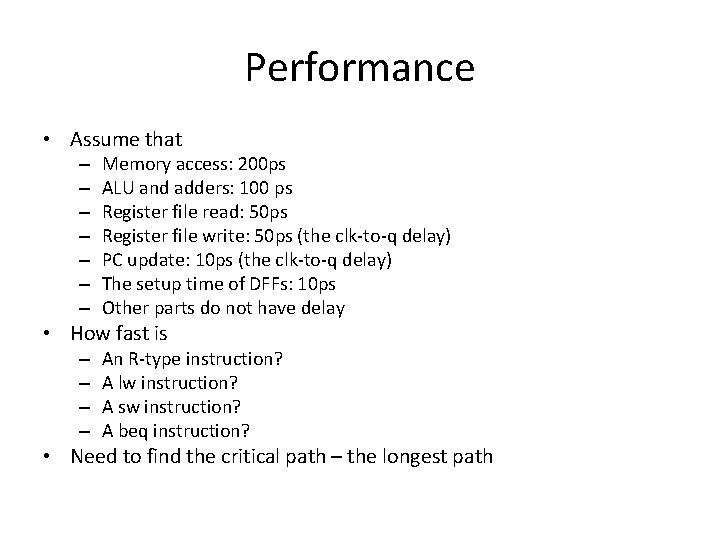

Performance • Assume that – – – – Memory access: 200 ps ALU and adders: 100 ps Register file read: 50 ps Register file write: 50 ps (the clk-to-q delay) PC update: 10 ps (the clk-to-q delay) The setup time of DFFs: 10 ps Other parts do not have delay • How fast is – – An R-type instruction? A lw instruction? A sw instruction? A beq instruction? • Need to find the critical path – the longest path

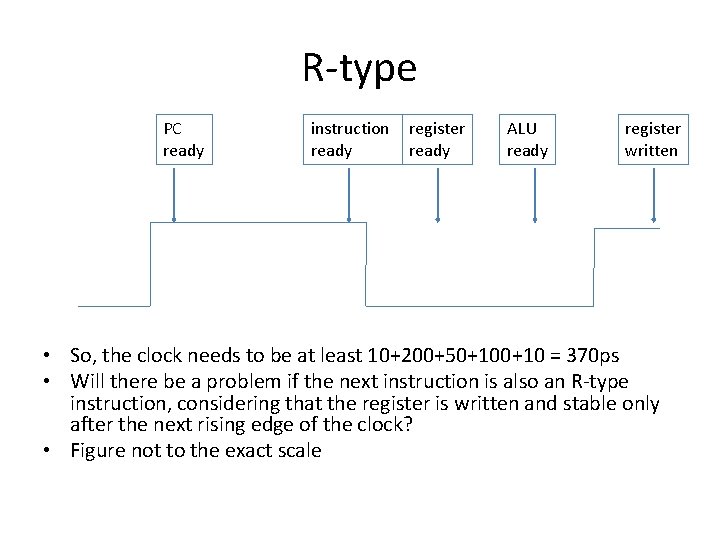

R-type PC ready instruction ready register ready ALU ready register written • So, the clock needs to be at least 10+200+50+10 = 370 ps • Will there be a problem if the next instruction is also an R-type instruction, considering that the register is written and stable only after the next rising edge of the clock? • Figure not to the exact scale

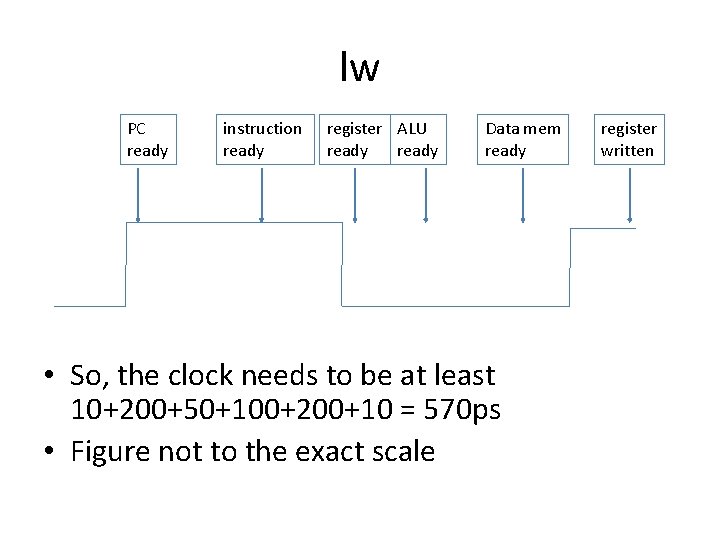

lw PC ready instruction ready register ALU ready Data mem ready • So, the clock needs to be at least 10+200+50+100+200+10 = 570 ps • Figure not to the exact scale register written

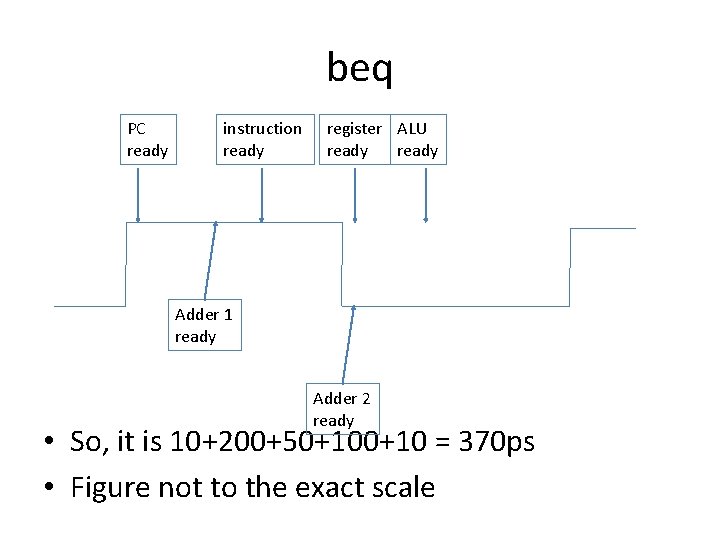

beq PC ready instruction ready register ALU ready Adder 1 ready Adder 2 ready • So, it is 10+200+50+10 = 370 ps • Figure not to the exact scale

Clock cycle • So, how long should the clock cycle be? • Is it efficient?

- Slides: 16