LANL FEM design proposal S Butsyk For LANL

LANL FEM design proposal S. Butsyk For LANL P-25 group

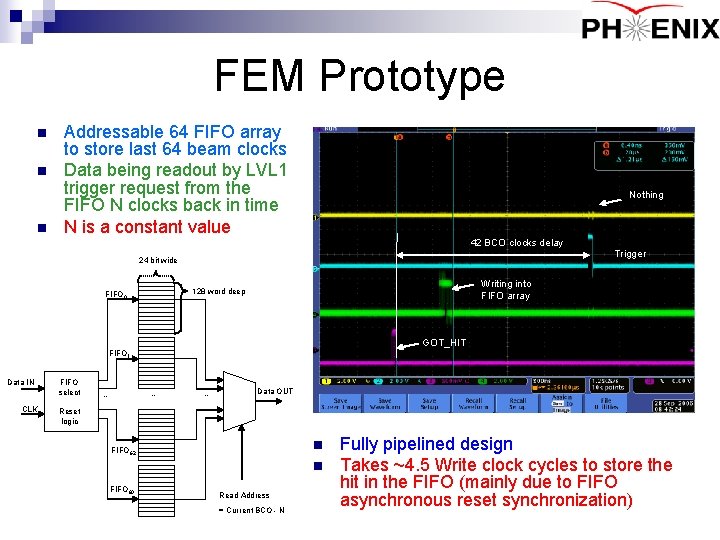

FEM Prototype n n n Addressable 64 FIFO array to store last 64 beam clocks Data being readout by LVL 1 trigger request from the FIFO N clocks back in time N is a constant value Reading from Nothing FIFO array 42 BCO clocks delay 24 bit wide Writing into FIFO array 128 word deep FIFO 0 Trigger GOT_HIT FIFO 1 Data IN CLK FIFO select … … … Data OUT Reset logic n FIFO 62 n FIFO 63 Read Address = Current BCO - N Fully pipelined design Takes ~4. 5 Write clock cycles to store the hit in the FIFO (mainly due to FIFO asynchronous reset synchronization)

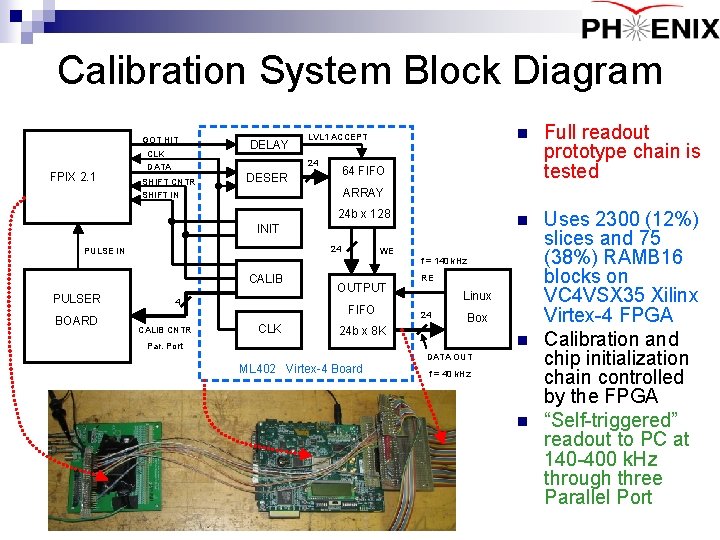

Calibration System Block Diagram GOT HIT FPIX 2. 1 CLK DATA DELAY LVL 1 ACCEPT 24 SHIFT CNTR n Full readout prototype chain is tested n Uses 2300 (12%) slices and 75 (38%) RAMB 16 blocks on VC 4 VSX 35 Xilinx Virtex-4 FPGA Calibration and chip initialization chain controlled by the FPGA “Self-triggered” readout to PC at 140 -400 k. Hz through three Parallel Port 64 FIFO DESER ARRAY SHIFT IN 24 b x 128 INIT 24 PULSE IN WE f = 140 k. Hz CALIB PULSER BOARD 4 CALIB CNTR OUTPUT FIFO CLK 24 b x 8 K RE Linux 24 Box n Par. Port ML 402 Virtex-4 Board DATA OUT f = 40 k. Hz n

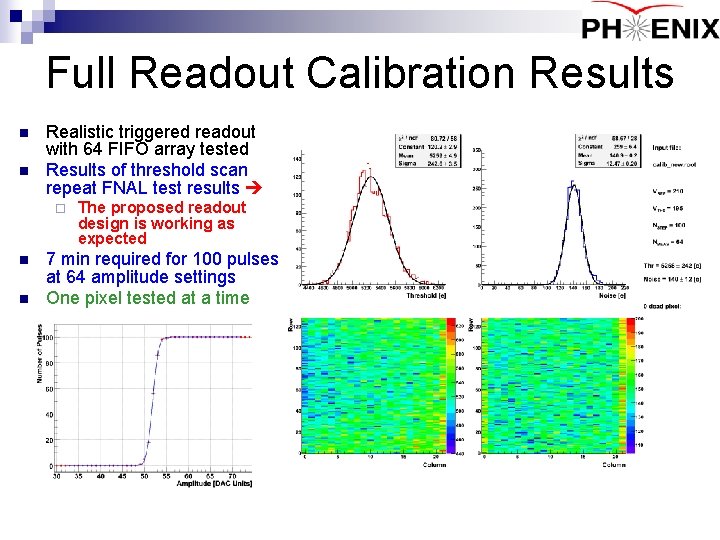

Full Readout Calibration Results n n Realistic triggered readout with 64 FIFO array tested Results of threshold scan repeat FNAL test results ¨ n n The proposed readout design is working as expected 7 min required for 100 pulses at 64 amplitude settings One pixel tested at a time

Next step

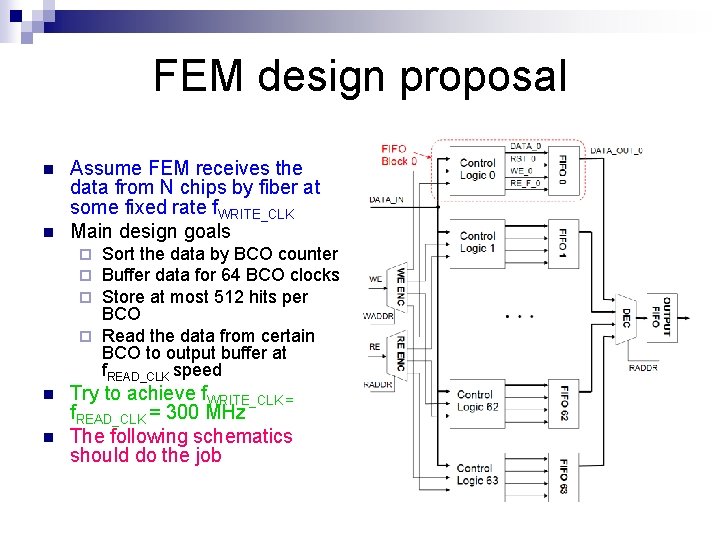

FEM design proposal n n Assume FEM receives the data from N chips by fiber at some fixed rate f. WRITE_CLK Main design goals Sort the data by BCO counter Buffer data for 64 BCO clocks Store at most 512 hits per BCO ¨ Read the data from certain BCO to output buffer at f. READ_CLK speed ¨ ¨ ¨ n n Try to achieve f. WRITE_CLK = f. READ_CLK = 300 MHz The following schematics should do the job

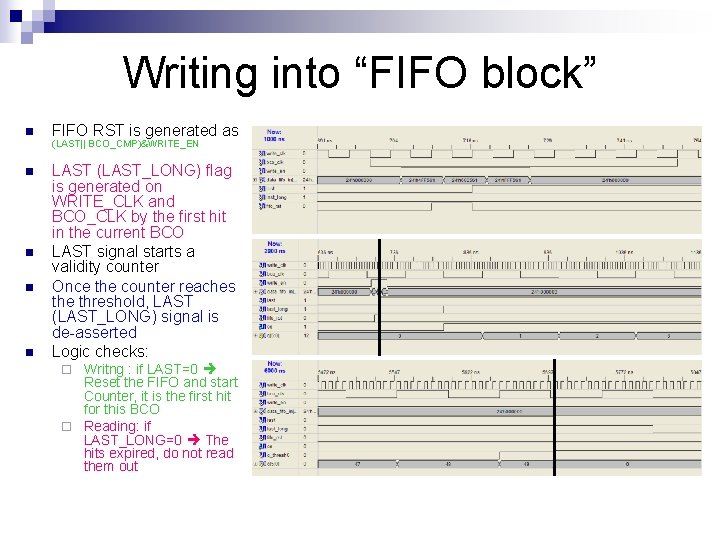

Writing into “FIFO block” n FIFO RST is generated as n LAST (LAST_LONG) flag is generated on WRITE_CLK and BCO_CLK by the first hit in the current BCO LAST signal starts a validity counter Once the counter reaches the threshold, LAST (LAST_LONG) signal is de-asserted Logic checks: n n n (LAST|| BCO_CMP)&WRITE_EN Writng : if LAST=0 Reset the FIFO and start Counter, it is the first hit for this BCO ¨ Reading: if LAST_LONG=0 The hits expired, do not read them out ¨

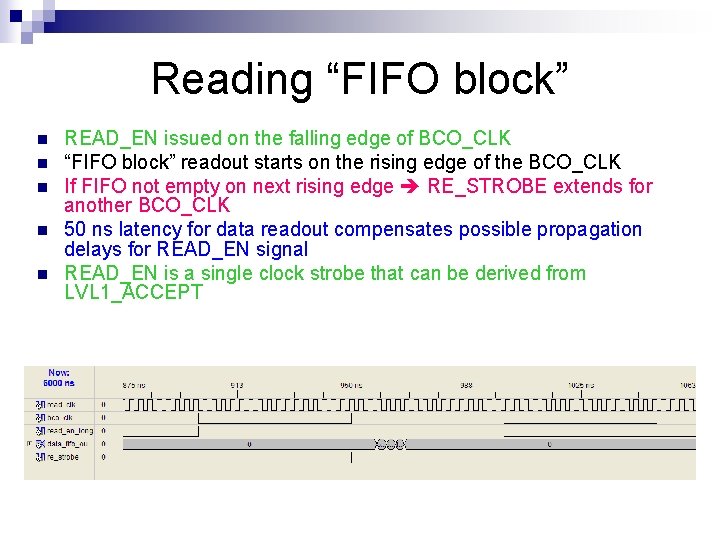

Reading “FIFO block” n n n READ_EN issued on the falling edge of BCO_CLK “FIFO block” readout starts on the rising edge of the BCO_CLK If FIFO not empty on next rising edge RE_STROBE extends for another BCO_CLK 50 ns latency for data readout compensates possible propagation delays for READ_EN signal READ_EN is a single clock strobe that can be derived from LVL 1_ACCEPT

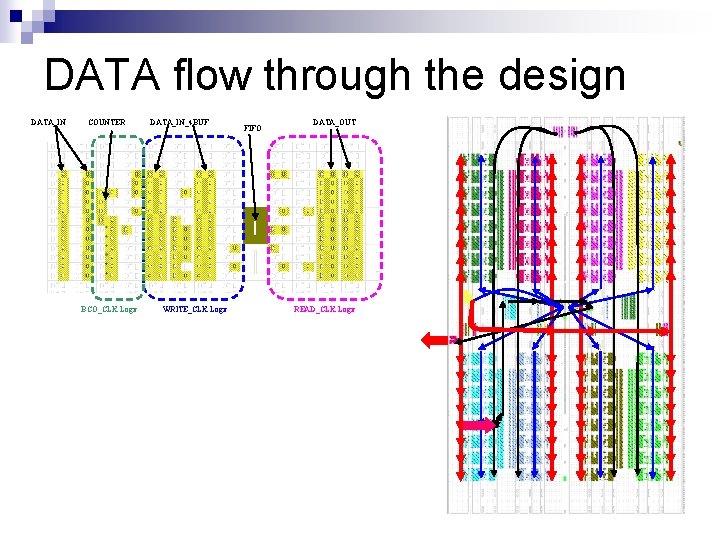

DATA flow through the design DATA_IN COUNTER BCO_CLK Logic DATA_IN_4 BUF WRITE_CLK Logic FIFO DATA_OUT READ_CLK Logic

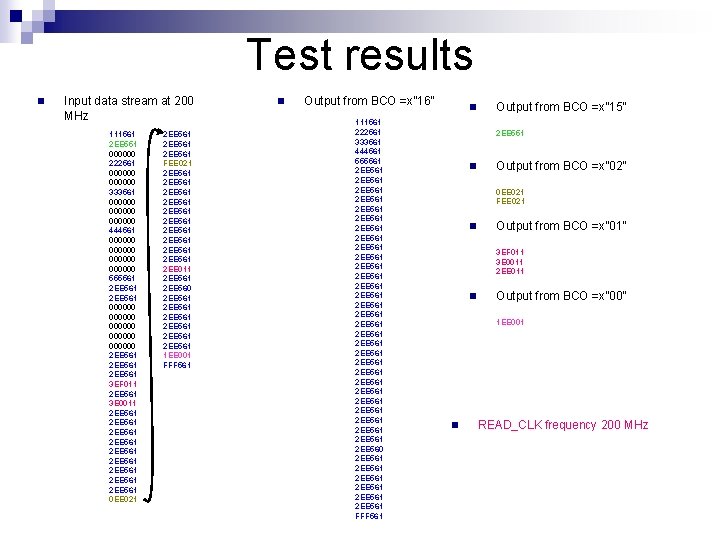

Test results n Input data stream at 200 MHz 111561 2 EE 551 000000 222561 000000 333561 000000 444561 000000 555561 2 EE 561 000000 000000 2 EE 561 3 EF 011 2 EE 561 3 E 0011 2 EE 561 2 EE 561 2 EE 561 0 EE 021 2 EE 561 FEE 021 2 EE 561 2 EE 561 2 EE 561 2 EE 011 2 EE 560 2 EE 561 2 EE 561 1 EE 001 FFF 561 n Output from BCO =x” 16” 111561 222561 333561 444561 555561 2 EE 561 2 EE 561 2 EE 561 2 EE 561 2 EE 561 2 EE 561 2 EE 561 2 EE 560 2 EE 561 2 EE 561 FFF 561 n Output from BCO =x” 15” 2 EE 551 n Output from BCO =x” 02” 0 EE 021 FEE 021 n Output from BCO =x” 01” 3 EF 011 3 E 0011 2 EE 011 n Output from BCO =x” 00” 1 EE 001 n READ_CLK frequency 200 MHz

- Slides: 10