Evaluation of CoverageDriven Random Verification st Robu Low

Evaluation of Coverage-Driven Random Verification st Robu Low ECE er Pow 7502 LSI V S 2015 ECE 7502 – Project Presentation Qing Qin 04/23/2015

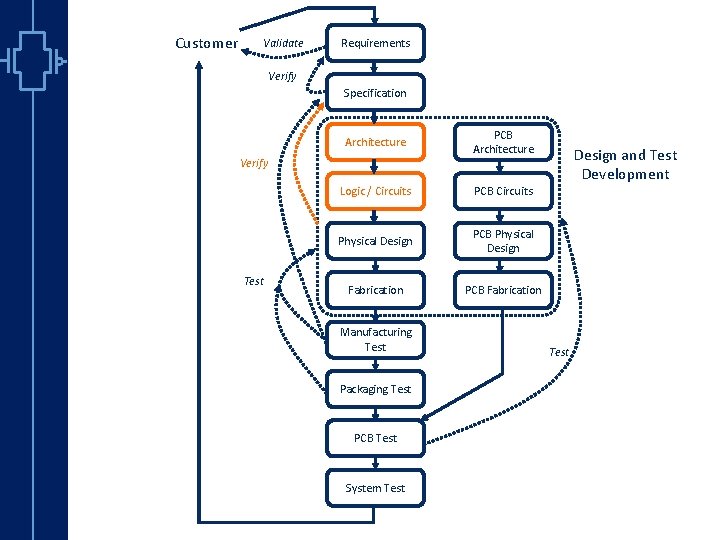

Customer Validate Requirements Verify Specification Architecture PCB Architecture Logic / Circuits PCB Circuits Physical Design PCB Physical Design Fabrication PCB Fabrication Verify Test Manufacturing Test Packaging Test st Robu Low er Pow VLSI PCB Test System Test Design and Test Development Test

Problems st Robu Low er Pow VLSI § How to create a hierarchical testbench that can be shared by different tests? § How to model the DUT to predict the output results for random verification? § What coverage measurements can be used to monitor the verification process? How good are they? § How is functional verification related to manufacturing testing? 3

Hypothesis/Expected Outcome § Layered testbench with modeling capability § Define different coverage metrics and demo how to gather the measurement § Fault modeling in the context of verification Approach st Robu Low er Pow VLSI § Floating-point adder as demo § Literature review 4

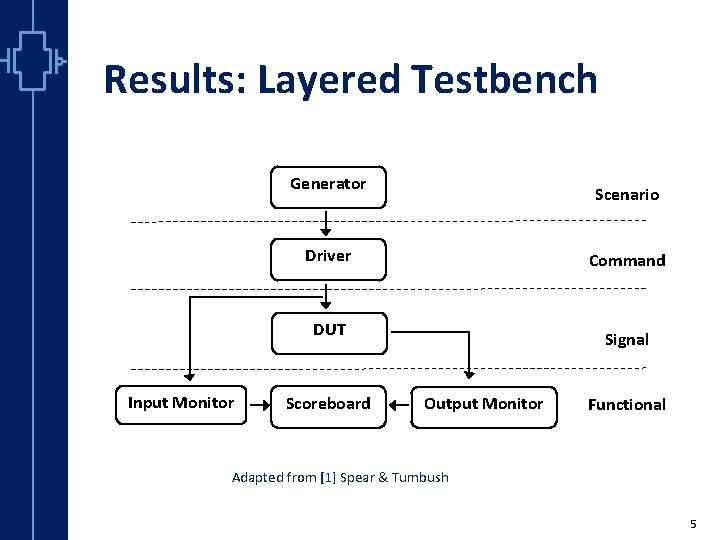

Results: Layered Testbench Generator Scenario Driver Command DUT st Robu Low er Pow VLSI Input Monitor Scoreboard Signal Output Monitor Functional Adapted from [1] Spear & Tumbush 5

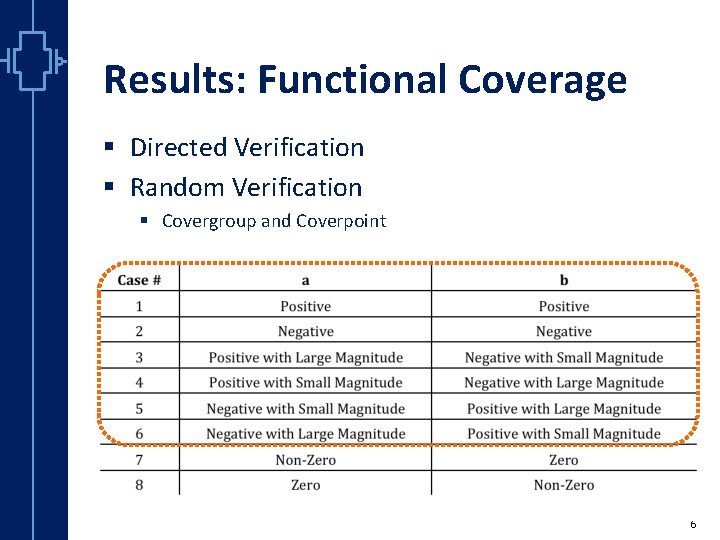

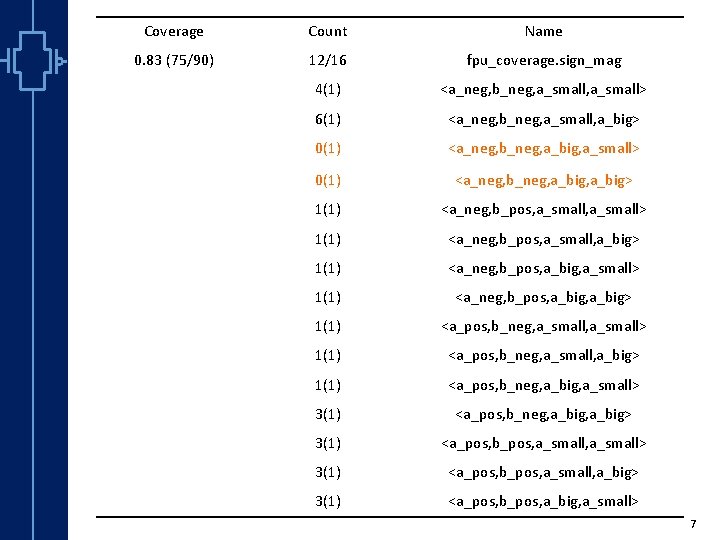

Results: Functional Coverage § Directed Verification § Random Verification § Covergroup and Coverpoint st Robu Low er Pow VLSI 6

st Robu Low er Pow VLSI Coverage Count Name 0. 83 (75/90) 12/16 fpu_coverage. sign_mag 4(1) <a_neg, b_neg, a_small> 6(1) <a_neg, b_neg, a_small, a_big> 0(1) <a_neg, b_neg, a_big, a_small> 0(1) <a_neg, b_neg, a_big> 1(1) <a_neg, b_pos, a_small> 1(1) <a_neg, b_pos, a_small, a_big> 1(1) <a_neg, b_pos, a_big, a_small> 1(1) <a_neg, b_pos, a_big> 1(1) <a_pos, b_neg, a_small> 1(1) <a_pos, b_neg, a_small, a_big> 1(1) <a_pos, b_neg, a_big, a_small> 3(1) <a_pos, b_neg, a_big> 3(1) <a_pos, b_pos, a_small> 3(1) <a_pos, b_pos, a_small, a_big> 3(1) <a_pos, b_pos, a_big, a_small> 7

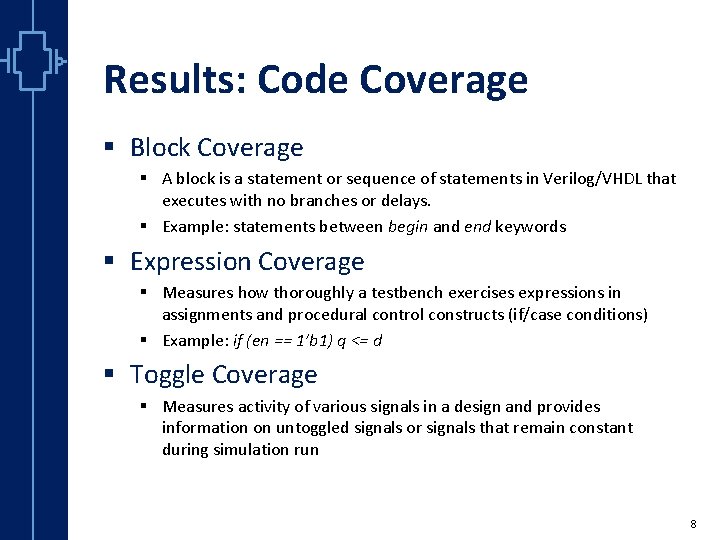

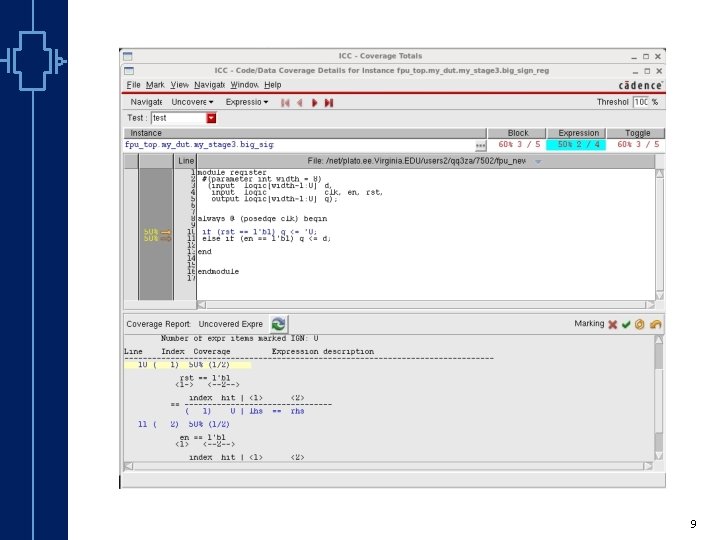

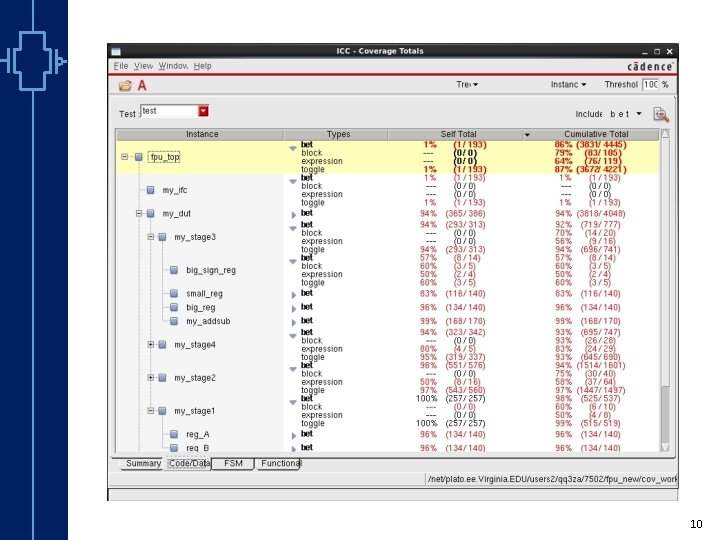

Results: Code Coverage § Block Coverage § A block is a statement or sequence of statements in Verilog/VHDL that executes with no branches or delays. § Example: statements between begin and end keywords § Expression Coverage § Measures how thoroughly a testbench exercises expressions in assignments and procedural control constructs (if/case conditions) § Example: if (en == 1’b 1) q <= d § Toggle Coverage st Robu Low er Pow VLSI § Measures activity of various signals in a design and provides information on untoggled signals or signals that remain constant during simulation run 8

st Robu Low er Pow VLSI 9

st Robu Low er Pow VLSI 10

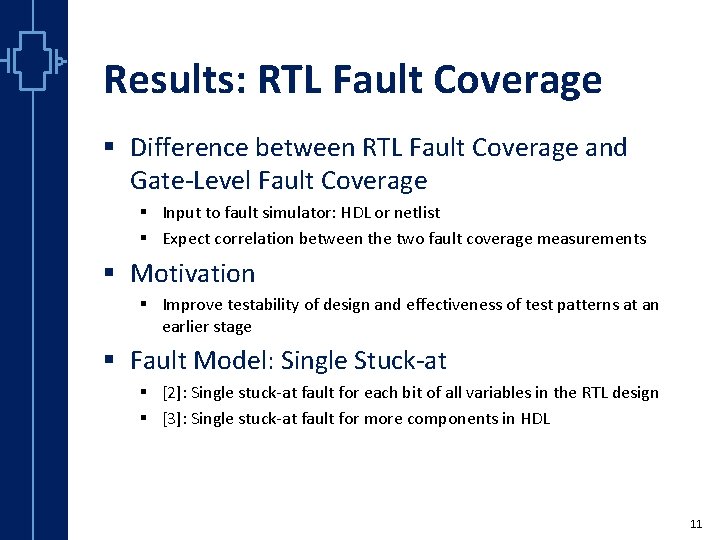

Results: RTL Fault Coverage § Difference between RTL Fault Coverage and Gate-Level Fault Coverage § Input to fault simulator: HDL or netlist § Expect correlation between the two fault coverage measurements § Motivation § Improve testability of design and effectiveness of test patterns at an earlier stage § Fault Model: Single Stuck-at st Robu Low er Pow VLSI § [2]: Single stuck-at fault for each bit of all variables in the RTL design § [3]: Single stuck-at fault for more components in HDL 11

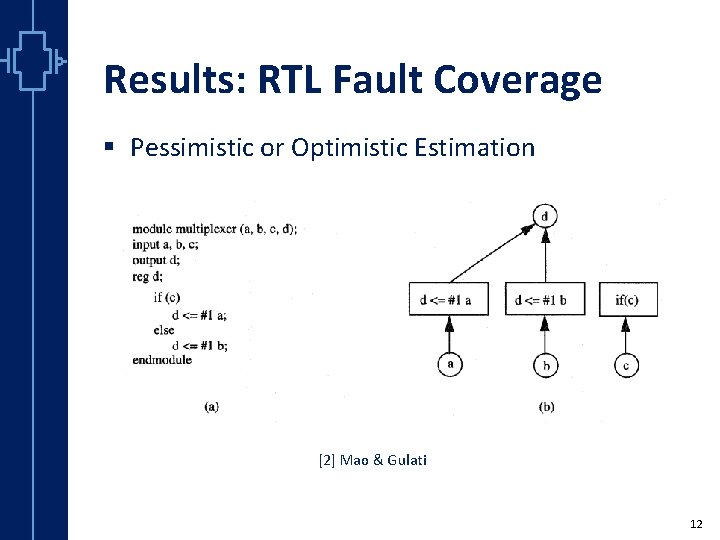

Results: RTL Fault Coverage § Pessimistic or Optimistic Estimation st Robu Low er Pow VLSI [2] Mao & Gulati 12

![Results: RTL Fault Coverage st Robu Low er Pow VLSI [2] Mao & Gulati Results: RTL Fault Coverage st Robu Low er Pow VLSI [2] Mao & Gulati](http://slidetodoc.com/presentation_image_h2/817a2c6b90c1ab65a22091ac58165a03/image-13.jpg)

Results: RTL Fault Coverage st Robu Low er Pow VLSI [2] Mao & Gulati 13

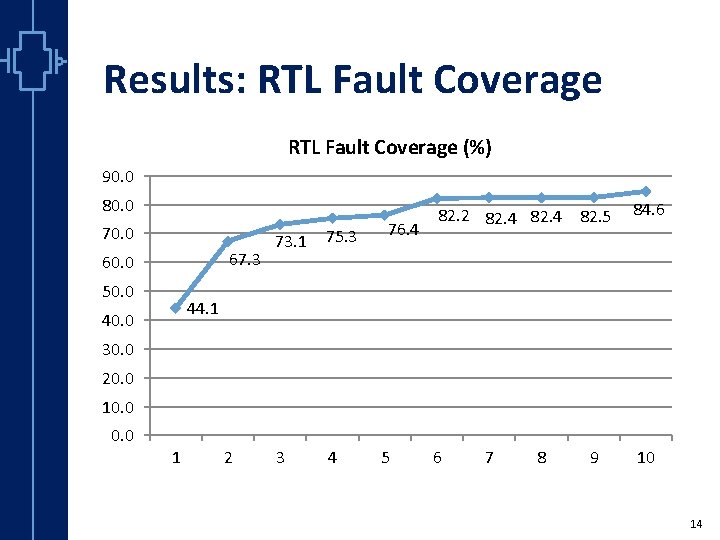

Results: RTL Fault Coverage (%) 90. 0 80. 0 70. 0 67. 3 60. 0 50. 0 73. 1 75. 3 3 4 76. 4 82. 2 82. 4 82. 5 84. 6 6 10 44. 1 40. 0 30. 0 20. 0 st Robu Low er Pow VLSI 10. 0 1 2 5 7 8 9 14

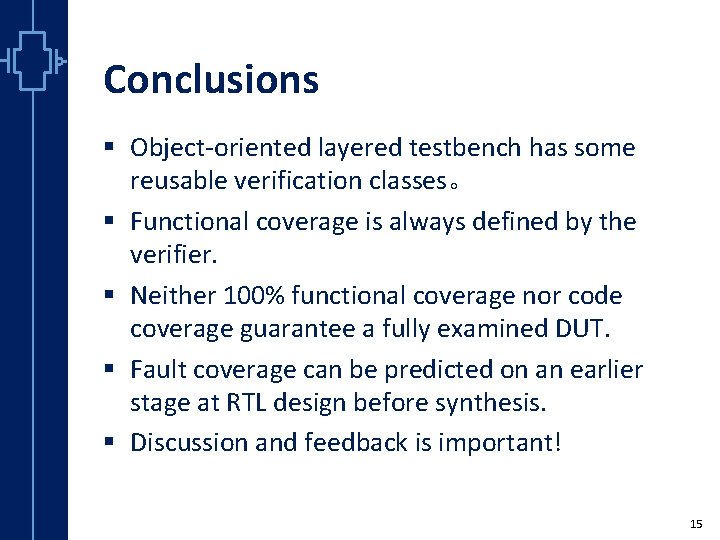

Conclusions st Robu Low er Pow VLSI § Object-oriented layered testbench has some reusable verification classes。 § Functional coverage is always defined by the verifier. § Neither 100% functional coverage nor code coverage guarantee a fully examined DUT. § Fault coverage can be predicted on an earlier stage at RTL design before synthesis. § Discussion and feedback is important! 15

![References st Robu Low er Pow VLSI [1] C. Spear and G. Tumbush, System. References st Robu Low er Pow VLSI [1] C. Spear and G. Tumbush, System.](http://slidetodoc.com/presentation_image_h2/817a2c6b90c1ab65a22091ac58165a03/image-16.jpg)

References st Robu Low er Pow VLSI [1] C. Spear and G. Tumbush, System. Verilog for Verification. New York, NY: Springer 2012 [2] Mao, W. ; Gulati, R. K. , "Improving gate level fault coverage by RTL fault grading, " Test Conference, 1996. Proceedings. , International , vol. , no. , pp. 150, 159, 20 -25 Oct 1996 [3] Karunaratne, M. ; Sagahayroon, A. ; Prodhuturi, S. , "RTL fault modeling, " Circuits and Systems, 2005. 48 th Midwest Symposium on , vol. , no. , pp. 1717, 1720 Vol. 2, 7 -10 Aug. 2005 16

- Slides: 16