EECE 320 Digital Systems Design Lecture 20 Sequential

- Slides: 9

EECE 320 Digital Systems Design Lecture 20: Sequential Logic Design Principles Ali Chehab EECE 320 L 20: Combinational Logic design Practices 1 Chehab, AUB, 2003

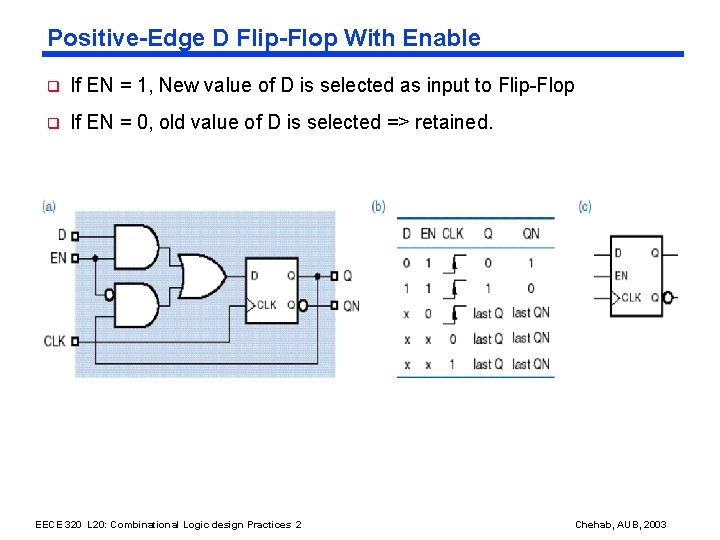

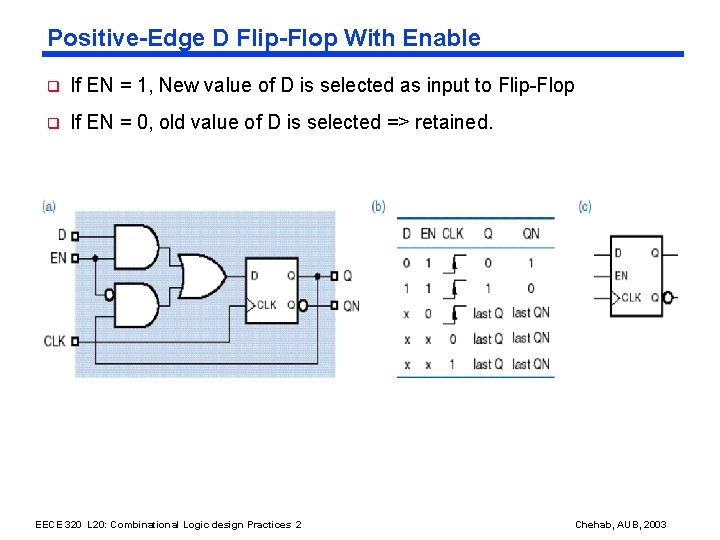

Positive-Edge D Flip-Flop With Enable q If EN = 1, New value of D is selected as input to Flip-Flop q If EN = 0, old value of D is selected => retained. EECE 320 L 20: Combinational Logic design Practices 2 Chehab, AUB, 2003

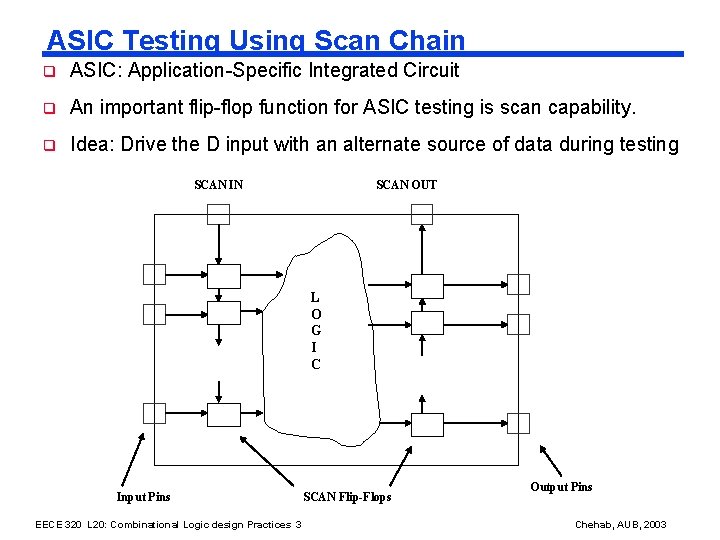

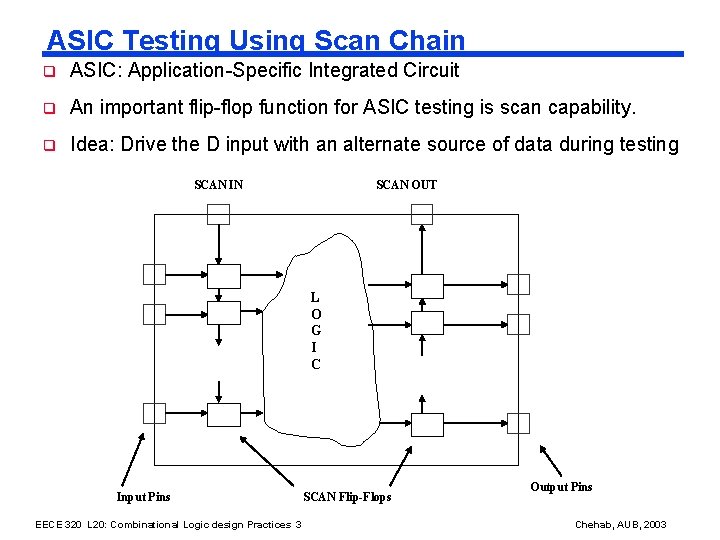

ASIC Testing Using Scan Chain q ASIC: Application-Specific Integrated Circuit q An important flip-flop function for ASIC testing is scan capability. q Idea: Drive the D input with an alternate source of data during testing SCAN IN SCAN OUT L O G I C Input Pins EECE 320 L 20: Combinational Logic design Practices 3 SCAN Flip-Flops Output Pins Chehab, AUB, 2003

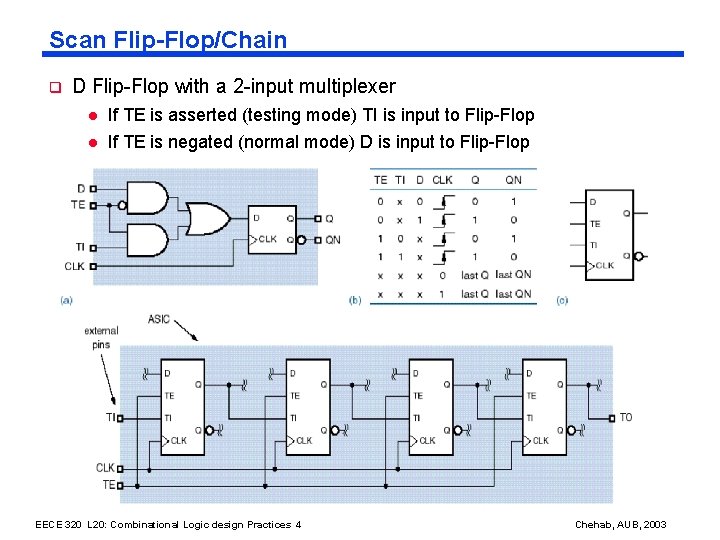

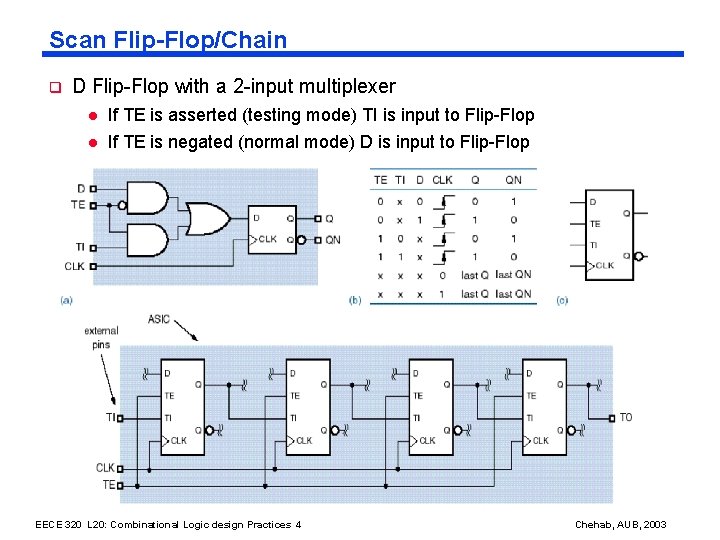

Scan Flip-Flop/Chain q D Flip-Flop with a 2 -input multiplexer l l If TE is asserted (testing mode) TI is input to Flip-Flop If TE is negated (normal mode) D is input to Flip-Flop EECE 320 L 20: Combinational Logic design Practices 4 Chehab, AUB, 2003

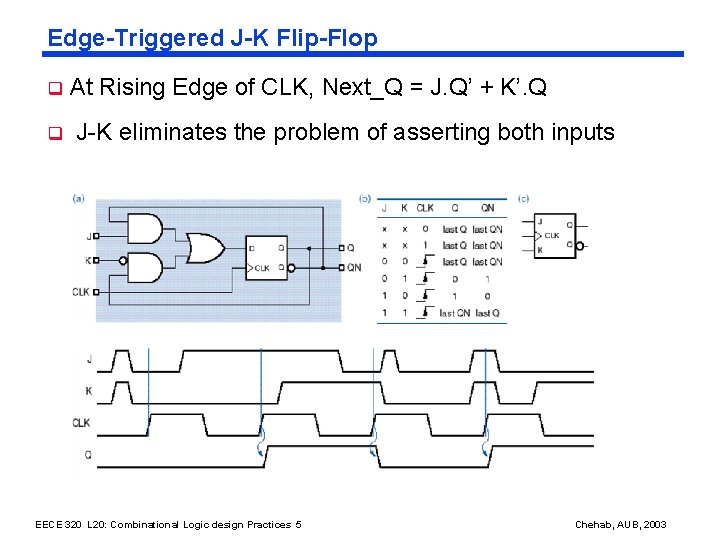

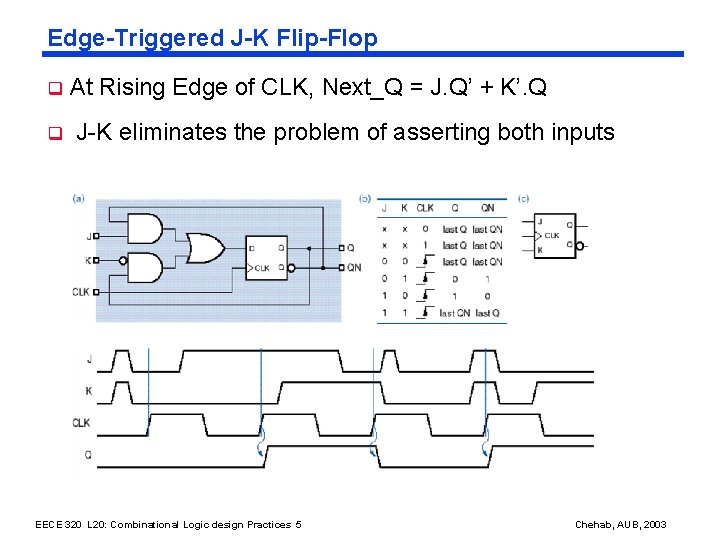

Edge-Triggered J-K Flip-Flop q q At Rising Edge of CLK, Next_Q = J. Q’ + K’. Q J-K eliminates the problem of asserting both inputs EECE 320 L 20: Combinational Logic design Practices 5 Chehab, AUB, 2003

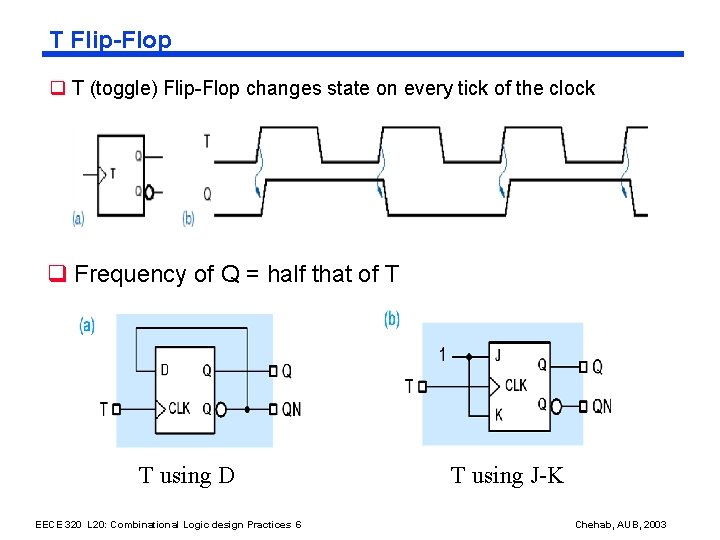

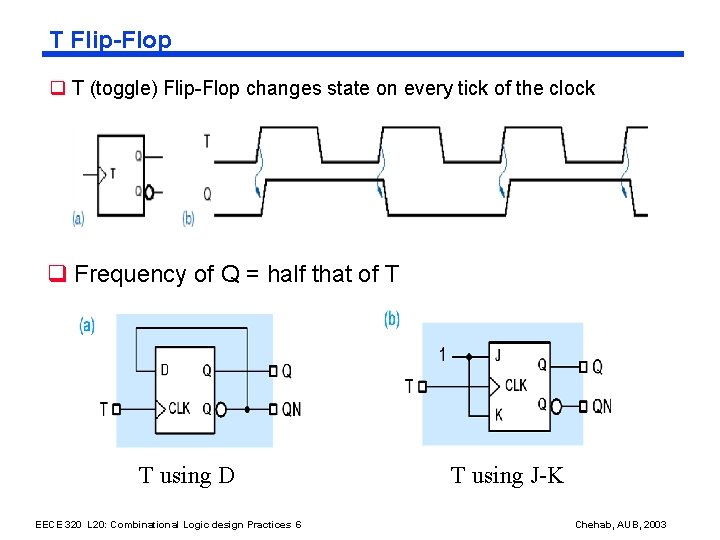

T Flip-Flop q T (toggle) Flip-Flop changes state on every tick of the clock q Frequency of Q = half that of T T using D EECE 320 L 20: Combinational Logic design Practices 6 T using J-K Chehab, AUB, 2003

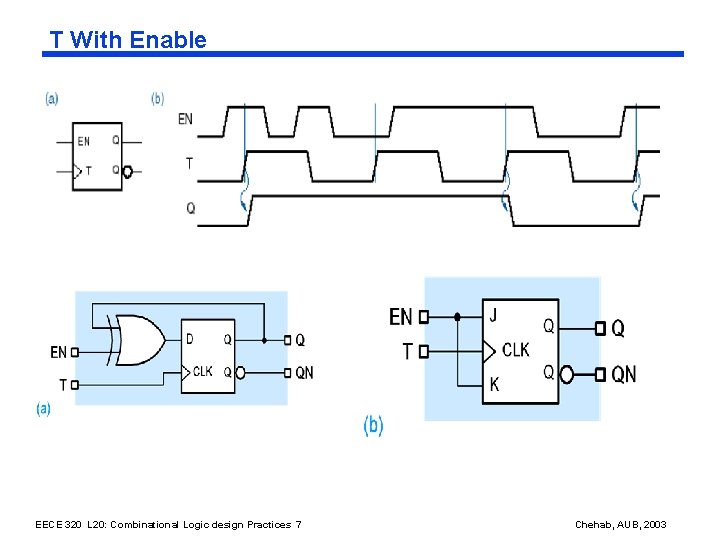

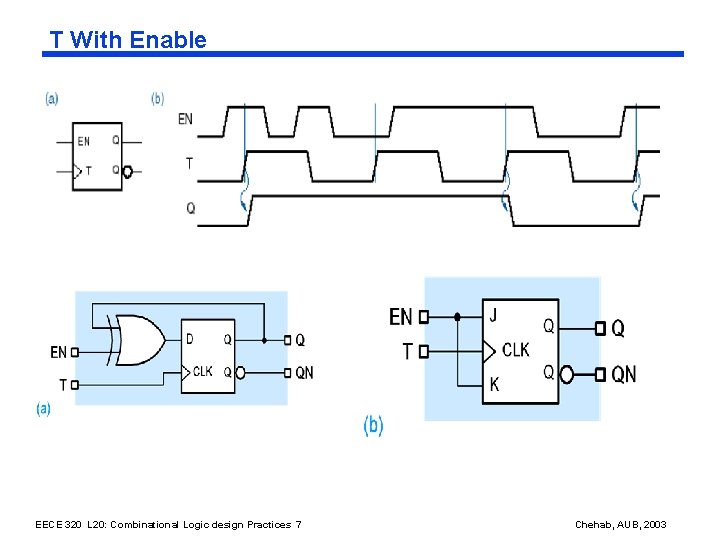

T With Enable EECE 320 L 20: Combinational Logic design Practices 7 Chehab, AUB, 2003

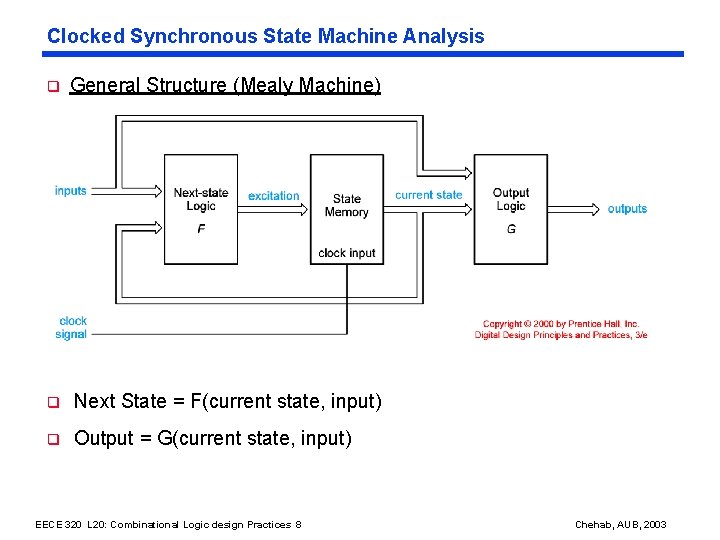

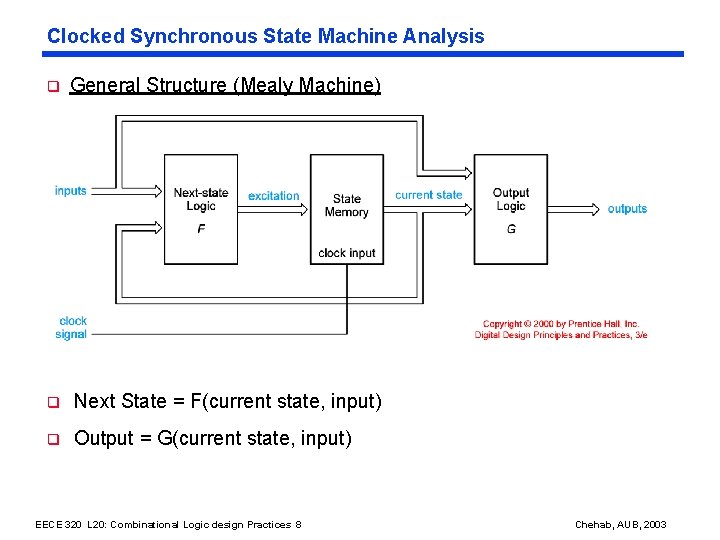

Clocked Synchronous State Machine Analysis q General Structure (Mealy Machine) q Next State = F(current state, input) q Output = G(current state, input) EECE 320 L 20: Combinational Logic design Practices 8 Chehab, AUB, 2003

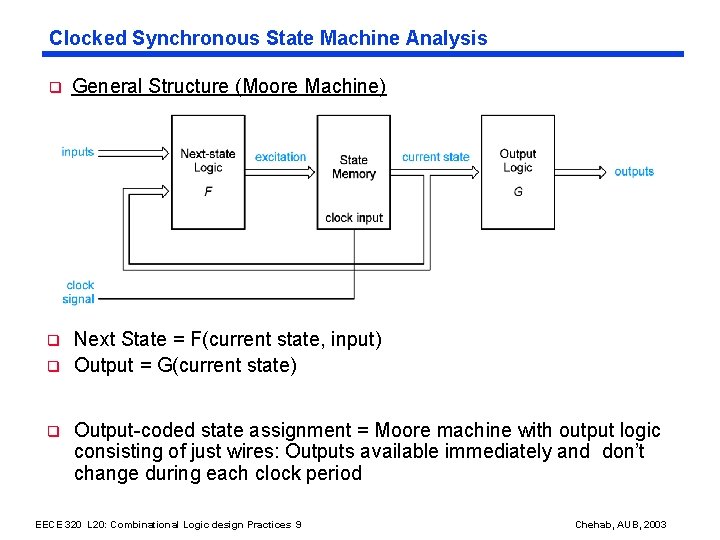

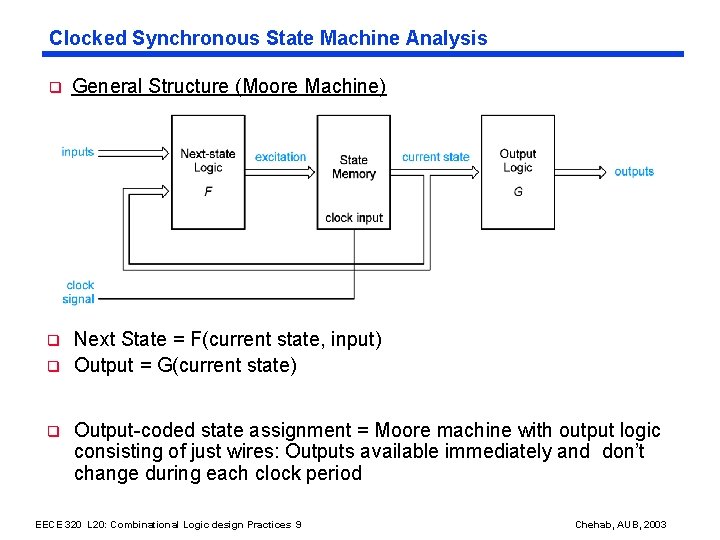

Clocked Synchronous State Machine Analysis q General Structure (Moore Machine) q Next State = F(current state, input) Output = G(current state) q q Output-coded state assignment = Moore machine with output logic consisting of just wires: Outputs available immediately and don’t change during each clock period EECE 320 L 20: Combinational Logic design Practices 9 Chehab, AUB, 2003