ECE 463563 Fall 20 Prof Rotenberg Simulation Example

ECE 463/563 Fall’ 20 Prof. Rotenberg Simulation Example: L 1 + L 2 cache, both with WBWA write policy. Manually simulate the address trace on the following memory hierarchy. Initially, the cache(s) are empty (no valid blocks in cache(s)). Evictions are always performed before bringing in blocks (important detail if simulating multiple levels of cache).

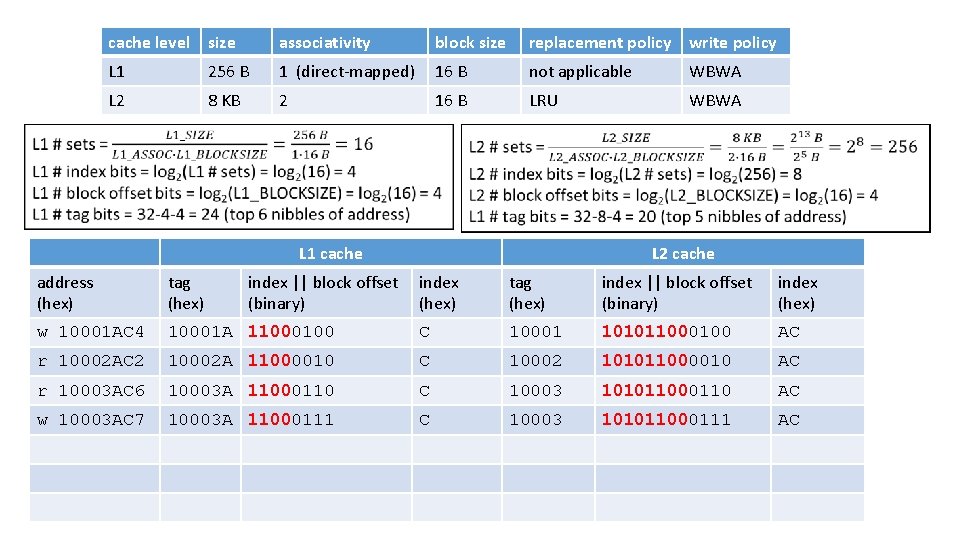

cache level size associativity block size replacement policy write policy L 1 256 B 1 (direct-mapped) 16 B not applicable WBWA L 2 8 KB 2 16 B LRU WBWA L 1 cache address (hex) tag (hex) w 10001 AC 4 10001 A 11000100 r 10002 AC 2 L 2 cache index || block offset index (binary) (hex) tag (hex) index || block offset (binary) index (hex) C 10001 101011000100 AC 10002 A 11000010 C 10002 101011000010 AC r 10003 AC 6 10003 A 11000110 C 10003 101011000110 AC w 10003 AC 7 10003 A 11000111 C 10003 101011000111 AC

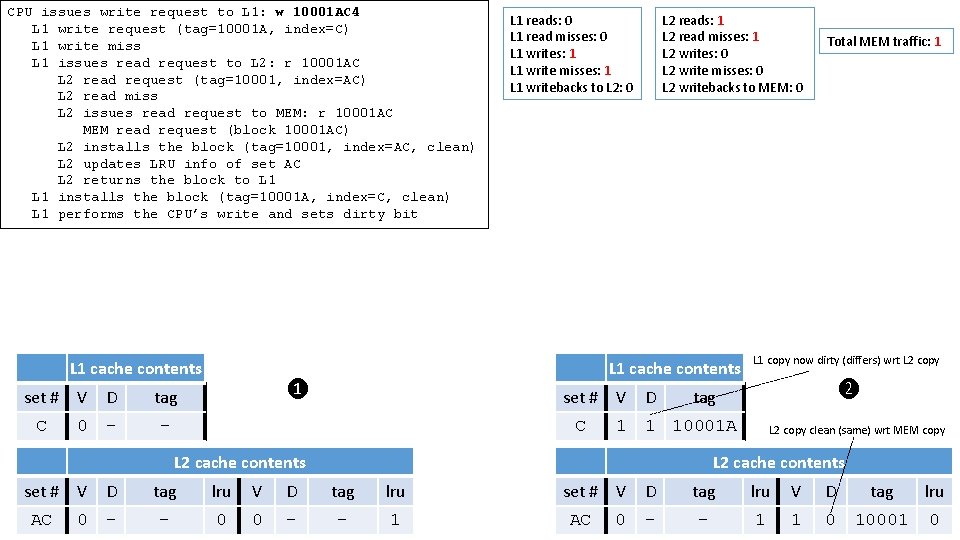

CPU issues write request to L 1: w 10001 AC 4 L 1 write request (tag=10001 A, index=C) L 1 write miss L 1 issues read request to L 2: r 10001 AC L 2 read request (tag=10001, index=AC) L 2 read miss L 2 issues read request to MEM: r 10001 AC MEM read request (block 10001 AC) L 2 installs the block (tag=10001, index=AC, clean) L 2 updates LRU info of set AC L 2 returns the block to L 1 installs the block (tag=10001 A, index=C, clean) L 1 performs the CPU’s write and sets dirty bit L 1 cache contents set # V C 0 D tag - - L 2 reads: 1 L 2 read misses: 1 L 2 writes: 0 L 2 write misses: 0 L 2 writebacks to MEM: 0 L 1 reads: 0 L 1 read misses: 0 L 1 writes: 1 L 1 write misses: 1 L 1 writebacks to L 2: 0 L 1 cache contents ❶ set # V C 1 D AC 0 L 1 copy now dirty (differs) wrt L 2 copy ❷ tag 1 10001 A L 2 copy clean (same) wrt MEM copy L 2 cache contents set # V Total MEM traffic: 1 D tag lru V D tag lru - - 0 0 - - 1 set # V AC 0 D tag lru V D tag lru - - 1 1 0 10001 0

CPU issues read request to L 1: r 10002 AC 2 L 1 read request (tag=10002 A, index=C) L 1 read miss, dirty victim block 10001 AC L 1 issues write request to L 2: w 10001 AC L 2 write request (tag=10001, index=AC) L 2 write hit ❸ L 2 updates LRU info of set AC L 2 performs L 1’s write and sets dirty bit L 1 issues read request to L 2: r 10002 AC L 2 read request (tag=10002, index=AC) L 2 read miss L 2 issues read request to MEM: r 10002 AC MEM read request (block 10002 AC) L 2 installs the block (tag=10002, index=AC, clean) L 2 updates LRU info of set AC L 2 returns the block to L 1 installs the block (tag=10002 A, index=C, clean) L 1 returns the requested byte(s) to CPU L 1 cache contents set # V C 1 D AC 0 L 1 copy now clean (same) wrt L 2 copy ❸ tag 0 10001 A L 2 copy now dirty (differs) wrt MEM copy L 2 cache contents set # V AC 0 D tag lru V D tag lru - - 1 10001 0 set # V 1 10001 A C 1 D ❹ tag 0 10002 A L 2 cache contents set # V Total MEM traffic: 2 L 1 cache contents ❷ tag L 2 reads: 2 L 2 read misses: 2 L 2 writes: 1 L 2 write misses: 0 L 2 writebacks to MEM: 0 L 1 reads: 1 L 1 read misses: 1 L 1 writebacks to L 2: 1 L 2 cache contents D tag lru V D tag lru - - 1 1 0 10001 0 set # V AC 1 D tag lru V D tag lru 0 10002 0 1 1 10001 1

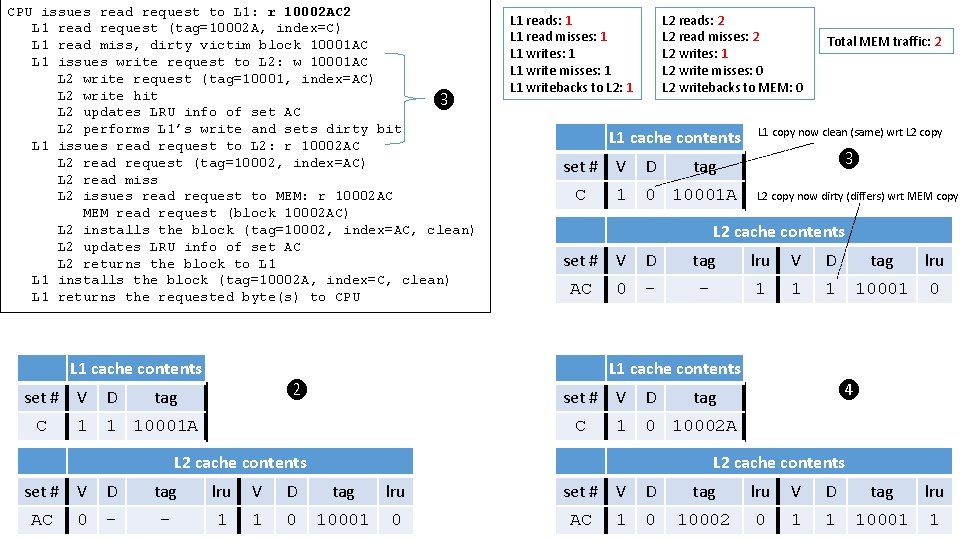

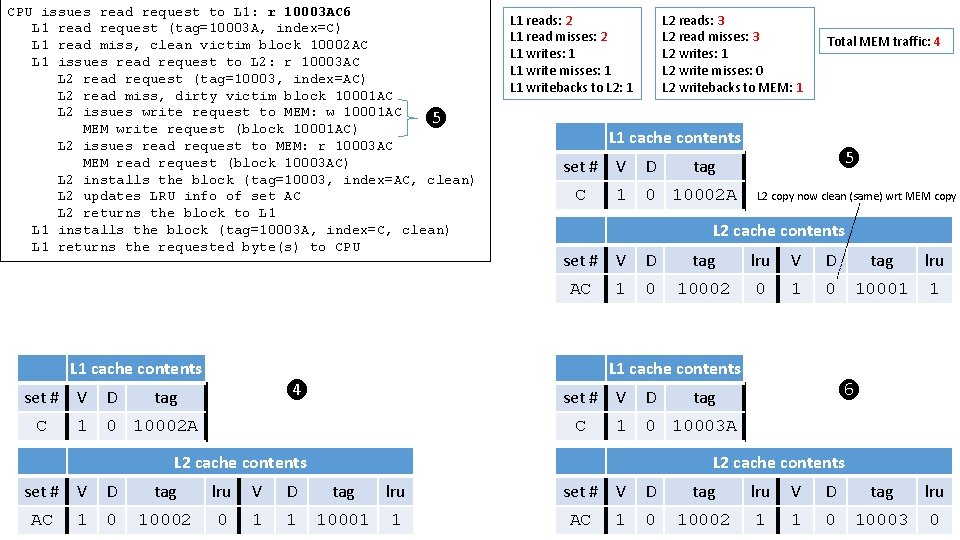

CPU issues read request to L 1: r 10003 AC 6 L 1 read request (tag=10003 A, index=C) L 1 read miss, clean victim block 10002 AC L 1 issues read request to L 2: r 10003 AC L 2 read request (tag=10003, index=AC) L 2 read miss, dirty victim block 10001 AC L 2 issues write request to MEM: w 10001 AC ❺ MEM write request (block 10001 AC) L 2 issues read request to MEM: r 10003 AC MEM read request (block 10003 AC) L 2 installs the block (tag=10003, index=AC, clean) L 2 updates LRU info of set AC L 2 returns the block to L 1 installs the block (tag=10003 A, index=C, clean) L 1 returns the requested byte(s) to CPU set # V C 1 D 0 10002 A AC 1 L 2 copy now clean (same) wrt MEM copy L 2 cache contents set # V 1 D tag lru V D tag lru 0 10002 0 10001 1 set # V 0 10002 A C 1 D ❻ tag 0 10003 A L 2 cache contents set # V ❺ tag L 1 cache contents ❹ tag Total MEM traffic: 4 L 1 cache contents AC L 1 cache contents L 2 reads: 3 L 2 read misses: 3 L 2 writes: 1 L 2 write misses: 0 L 2 writebacks to MEM: 1 L 1 reads: 2 L 1 read misses: 2 L 1 writes: 1 L 1 write misses: 1 L 1 writebacks to L 2: 1 L 2 cache contents D tag lru V D tag lru 0 10002 0 1 1 10001 1 set # V AC 1 D tag lru V D tag lru 0 10002 1 1 0 10003 0

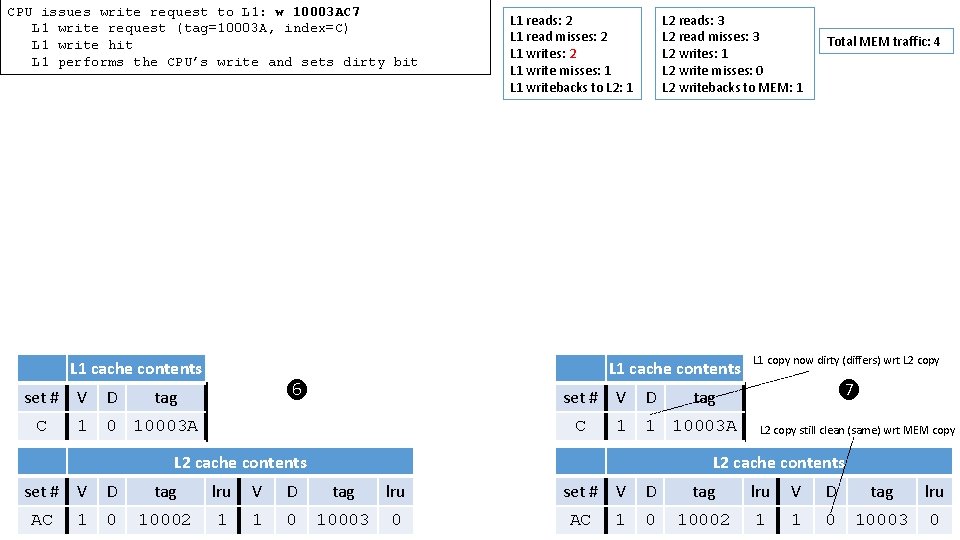

CPU issues write request to L 1: w 10003 AC 7 L 1 write request (tag=10003 A, index=C) L 1 write hit L 1 performs the CPU’s write and sets dirty bit L 1 cache contents set # V C 1 D L 1 cache contents ❻ tag L 2 reads: 3 L 2 read misses: 3 L 2 writes: 1 L 2 write misses: 0 L 2 writebacks to MEM: 1 L 1 reads: 2 L 1 read misses: 2 L 1 write misses: 1 L 1 writebacks to L 2: 1 set # V 0 10003 A C 1 D set # V AC 1 L 1 copy now dirty (differs) wrt L 2 copy ❼ tag 1 10003 A L 2 cache contents Total MEM traffic: 4 L 2 copy still clean (same) wrt MEM copy L 2 cache contents D tag lru V D tag lru 0 10002 1 1 0 10003 0 set # V AC 1 D tag lru V D tag lru 0 10002 1 1 0 10003 0

- Slides: 6