UNIVERSITATEA POLITEHNICA DIN TIMIOARA FACULTATEA DE ELECTRONIC I

- Slides: 12

UNIVERSITATEA “POLITEHNICA” DIN TIMIŞOARA FACULTATEA DE ELECTRONICĂ ŞI TELECOMUNICAŢII DEPARTAMENTUL DE ELECTRONICĂ APLICATĂ Acceleration Sensor SPI Emulator Thesis adviser: Associate Professor Ph. D. Eng. JIVEŢ Ioan TIMIŞOARA 2010 Author: MIHĂILESCU Andrei-Bogdan

Acknowledgement The present diploma project has been developed in the period 15 th September 2009 - 30 th June 2010 as a research project in collaboration with “Politehnica” University Timişoara, „e. Austria” Research Institute Timişoara and “Bee. Speed Automatizări” Timişoara (as a subcontractor for TRW, CIAT department, from Koblenz, Germany). 2 © TRW Automotive Inc. 2009

Presentation Overview 1. Why this project? 2. Architecture overview 3. Sensor 4. CPLD 5. Microcontroller 6. Big Picture 7. Questions 3 © TRW Automotive Inc. 2009

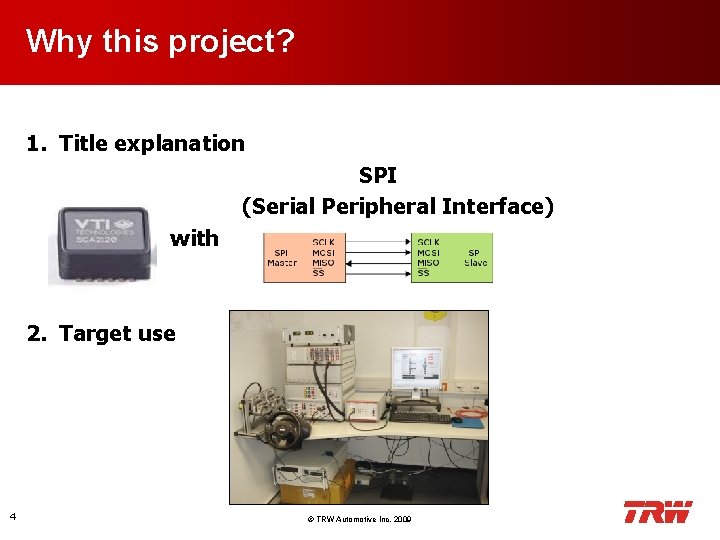

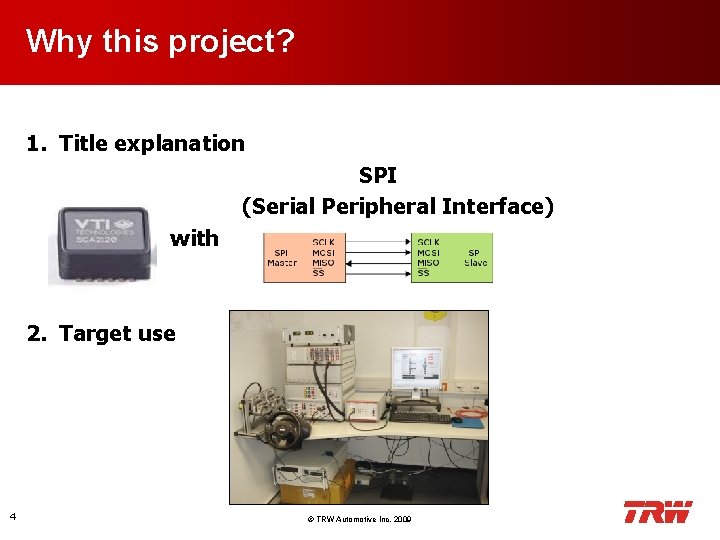

Why this project? 1. Title explanation SPI (Serial Peripheral Interface) with 2. Target use 4 © TRW Automotive Inc. 2009

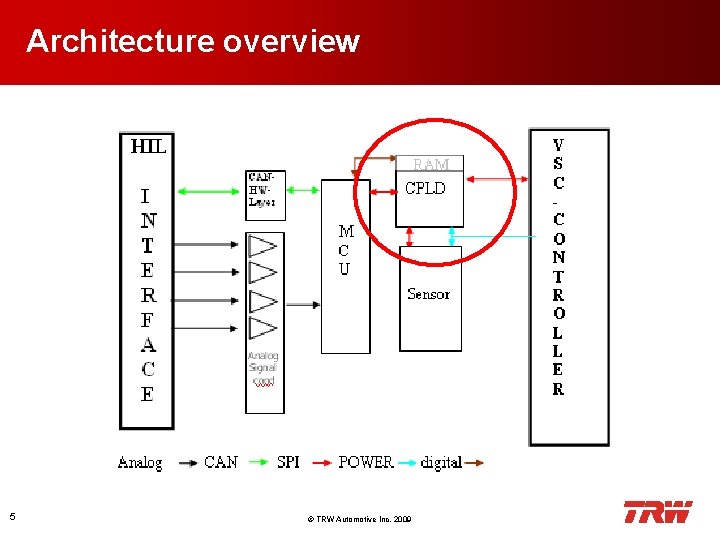

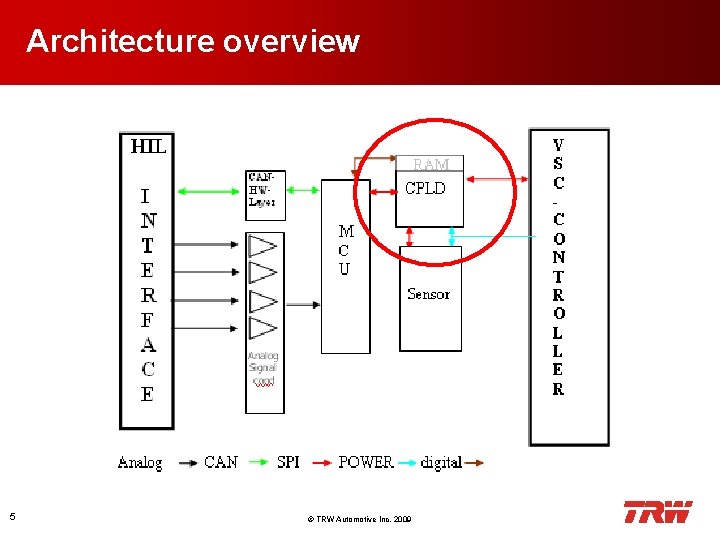

Architecture overview 5 © TRW Automotive Inc. 2009

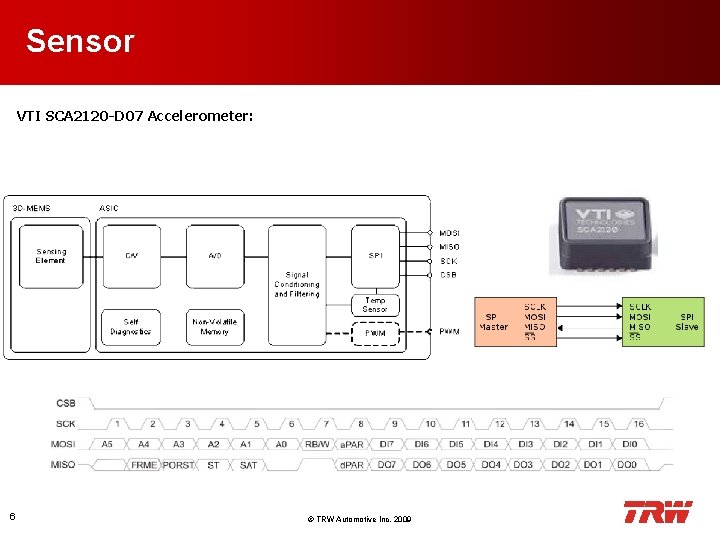

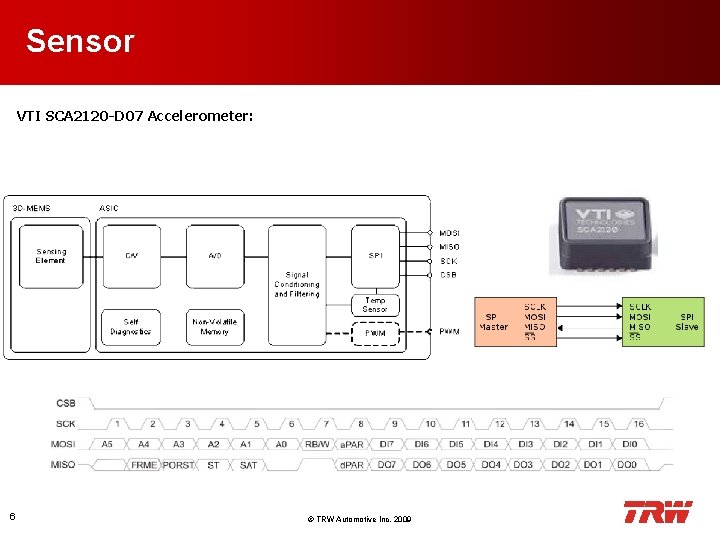

Sensor VTI SCA 2120 -D 07 Accelerometer: 6 © TRW Automotive Inc. 2009

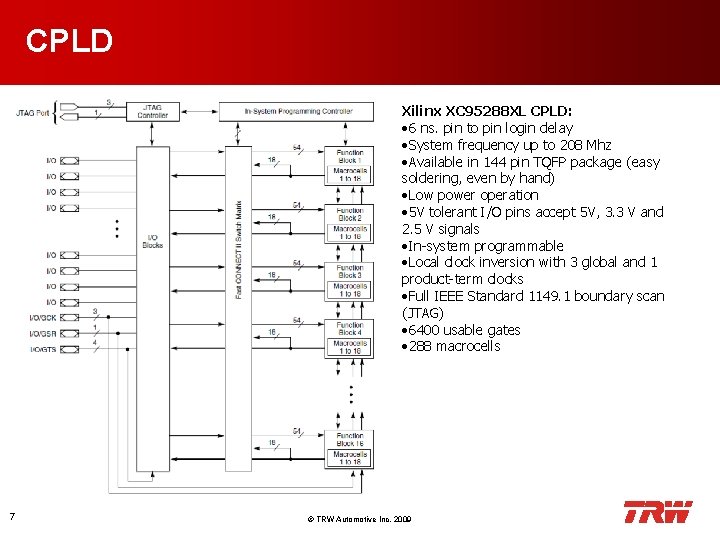

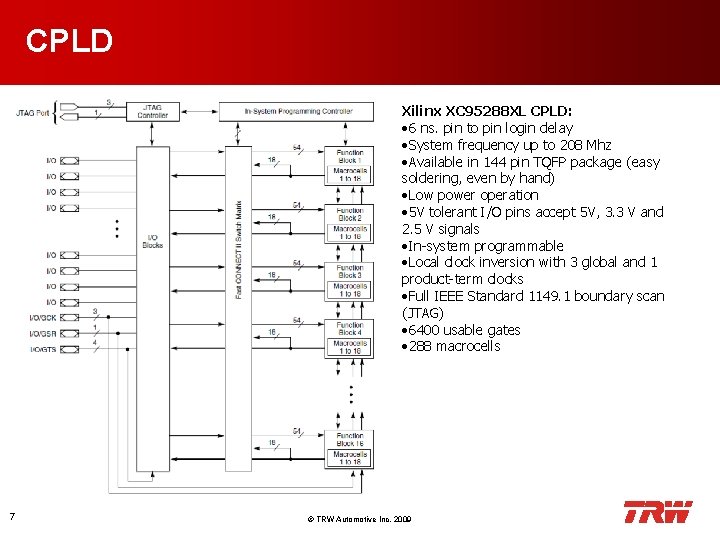

CPLD Xilinx XC 95288 XL CPLD: • 6 ns. pin to pin login delay • System frequency up to 208 Mhz • Available in 144 pin TQFP package (easy soldering, even by hand) • Low power operation • 5 V tolerant I/O pins accept 5 V, 3. 3 V and 2. 5 V signals • In-system programmable • Local clock inversion with 3 global and 1 product-term clocks • Full IEEE Standard 1149. 1 boundary scan (JTAG) • 6400 usable gates • 288 macrocells 7 © TRW Automotive Inc. 2009

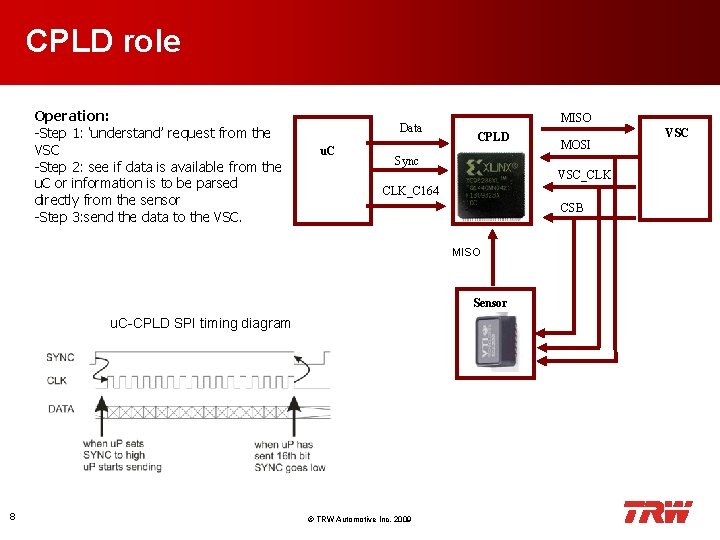

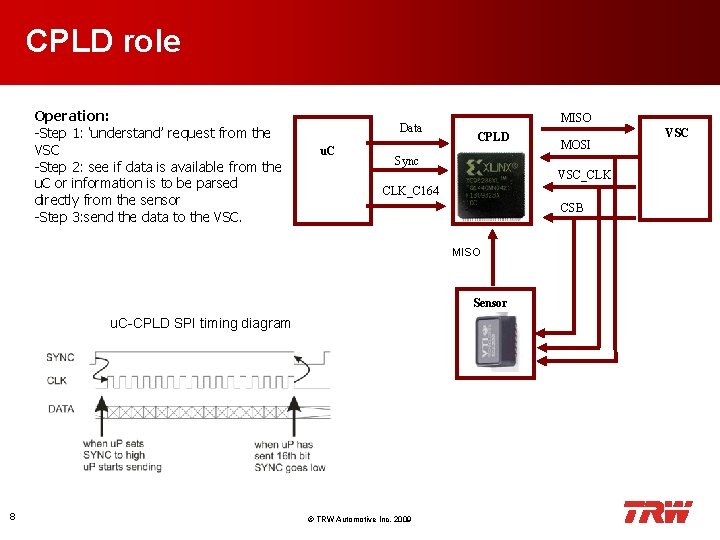

CPLD role Operation: -Step 1: ‘understand’ request from the VSC -Step 2: see if data is available from the u. C or information is to be parsed directly from the sensor -Step 3: send the data to the VSC. Data u. C MISO CPLD Sync VSC_CLK CLK_C 164 CSB MISO Sensor u. C-CPLD SPI timing diagram 8 MOSI © TRW Automotive Inc. 2009 VSC

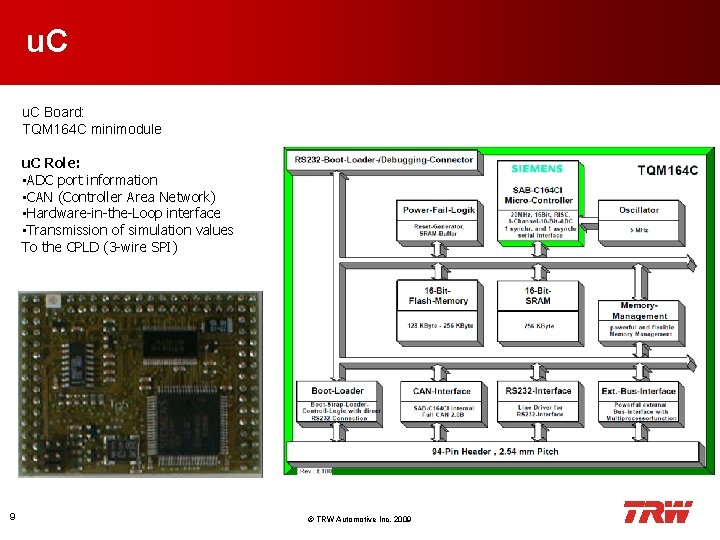

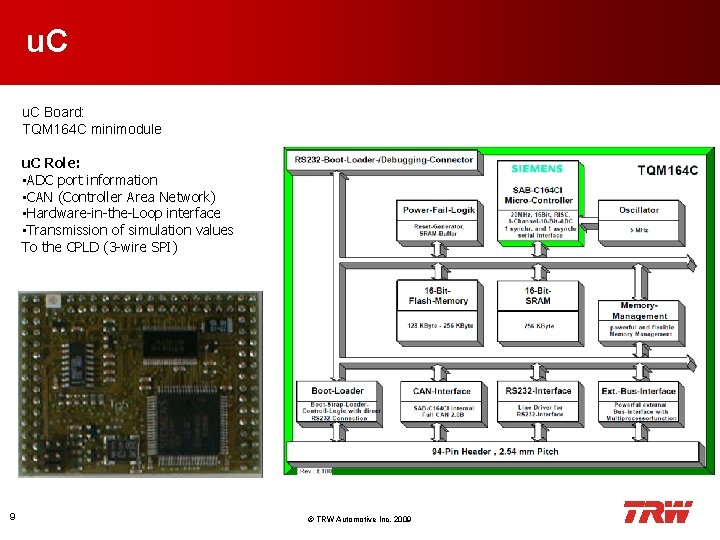

u. C Board: TQM 164 C minimodule u. C Role: • ADC port information • CAN (Controller Area Network) • Hardware-in-the-Loop interface • Transmission of simulation values To the CPLD (3 -wire SPI) 9 © TRW Automotive Inc. 2009

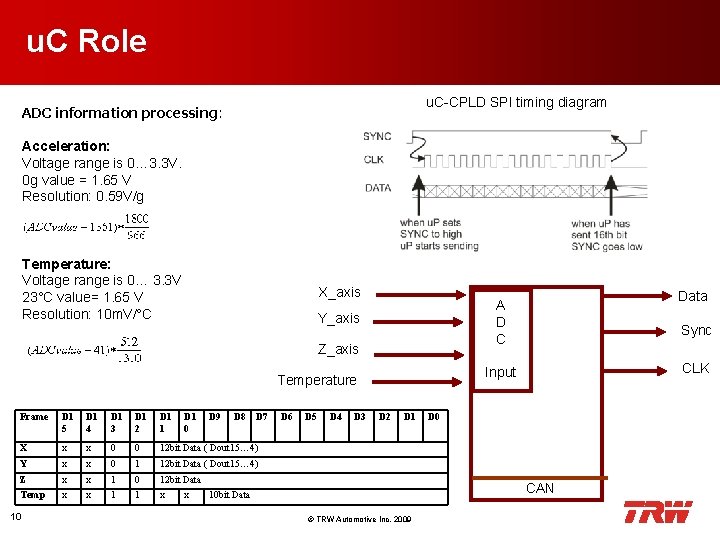

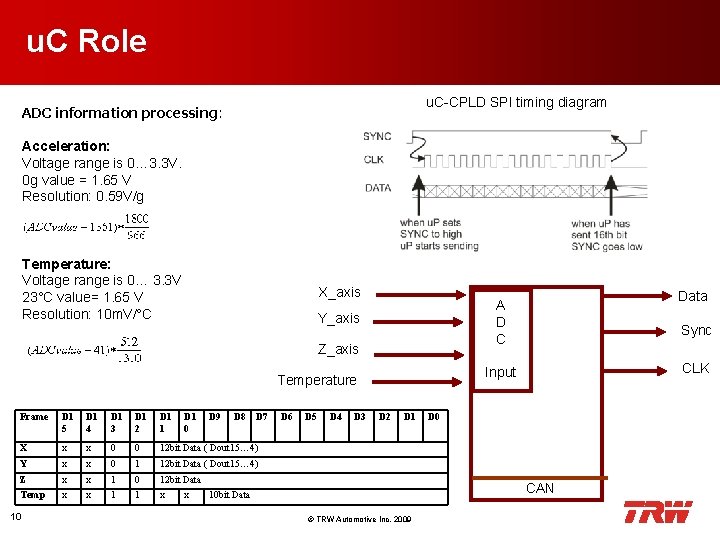

u. C Role u. C-CPLD SPI timing diagram ADC information processing: Acceleration: Voltage range is 0… 3. 3 V. 0 g value = 1. 65 V Resolution: 0. 59 V/g Temperature: Voltage range is 0… 3. 3 V 23°C value= 1. 65 V Resolution: 10 m. V/°C X_axis Y_axis Z_axis D 1 5 D 1 4 D 1 3 D 1 2 D 1 1 X x x 0 0 12 bit Data ( Dout 15… 4) Y x x 0 1 12 bit Data ( Dout 15… 4) Z x x 1 0 12 bit Data Temp x x 1 1 x 10 D 1 0 x D 9 D 8 D 7 D 6 D 5 D 4 D 3 Sync CLK Input Temperature Frame Data A D C D 2 D 1 D 0 CAN 10 bit Data © TRW Automotive Inc. 2009

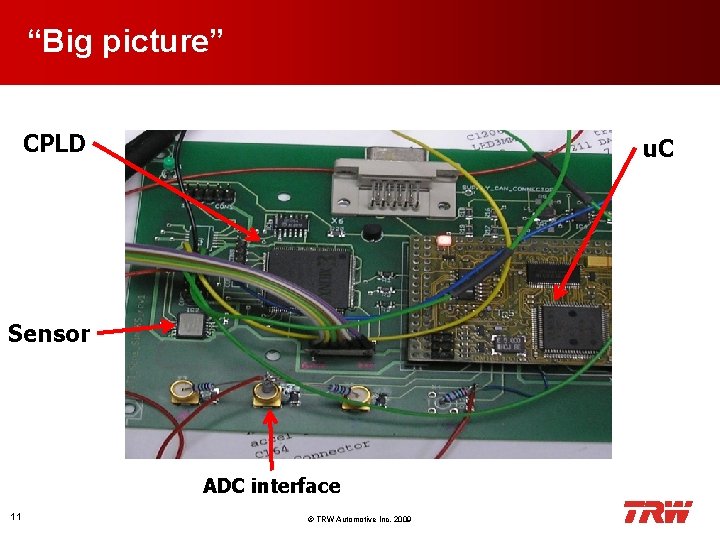

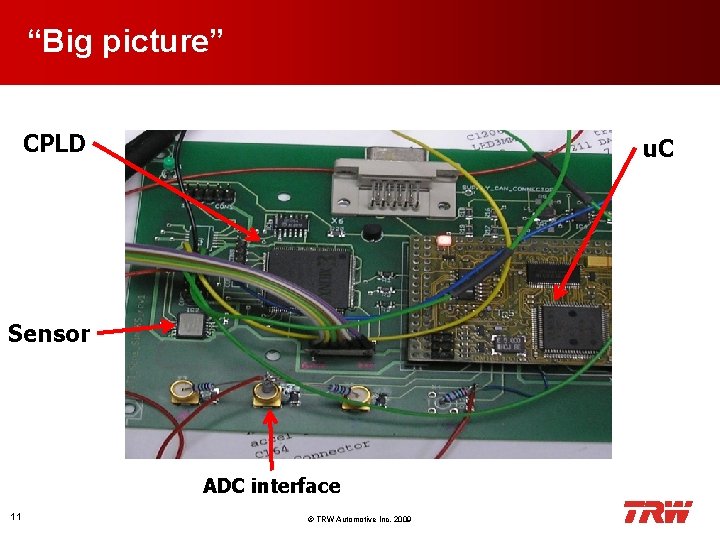

“Big picture” CPLD u. C Sensor ADC interface 11 © TRW Automotive Inc. 2009

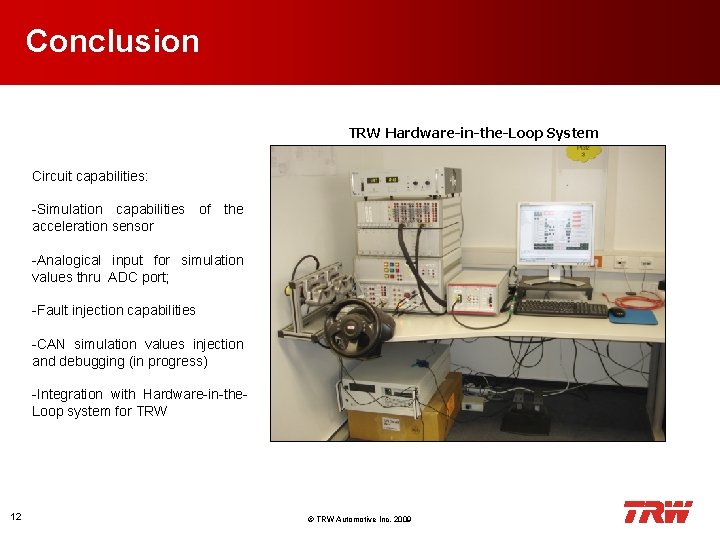

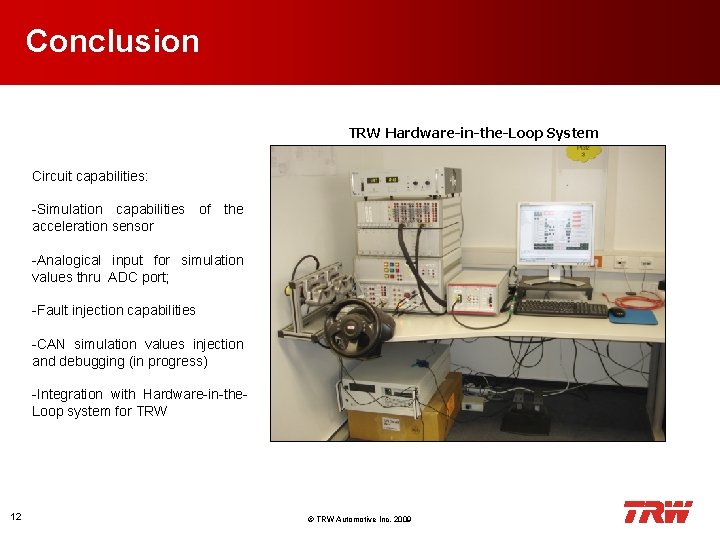

Conclusion TRW Hardware-in-the-Loop System Circuit capabilities: -Simulation capabilities of the acceleration sensor -Analogical input for simulation values thru ADC port; -Fault injection capabilities -CAN simulation values injection and debugging (in progress) -Integration with Hardware-in-the. Loop system for TRW 12 © TRW Automotive Inc. 2009