The electronics system of the TOTEM T 1

- Slides: 2

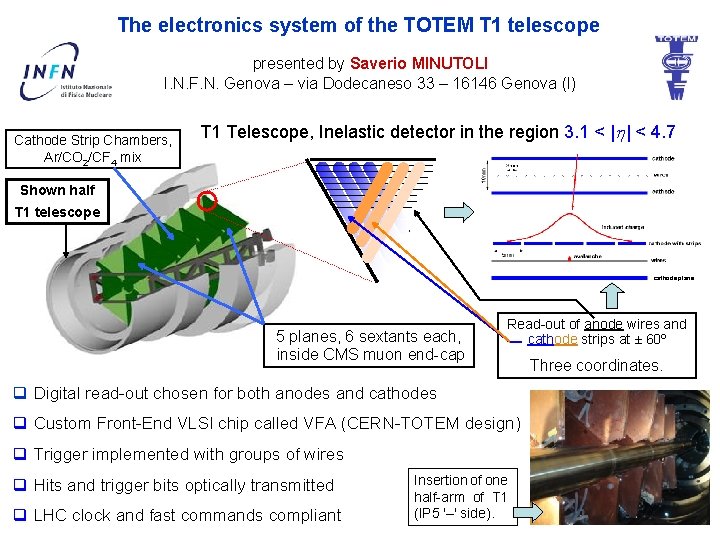

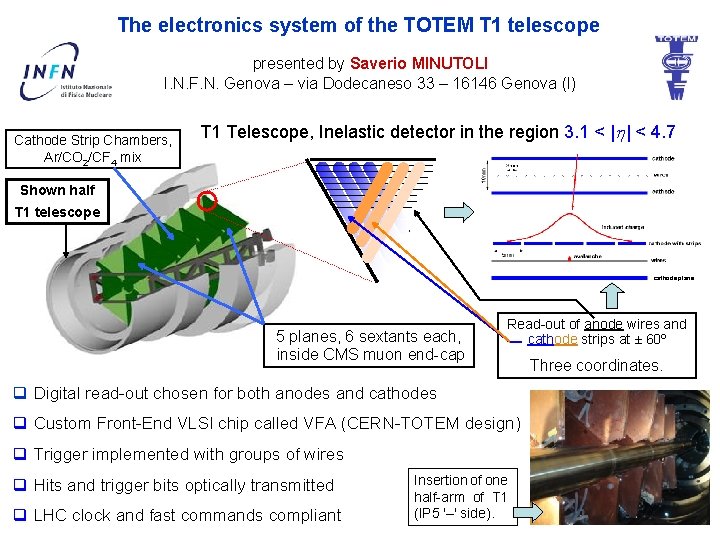

The electronics system of the TOTEM T 1 telescope presented by Saverio MINUTOLI I. N. F. N. Genova – via Dodecaneso 33 – 16146 Genova (I) Cathode Strip Chambers, Ar/CO 2/CF 4 mix T 1 Telescope, Inelastic detector in the region 3. 1 < |h| < 4. 7 Shown half T 1 telescope cathode plane 5 planes, 6 sextants each, inside CMS muon end-cap Read-out of anode wires and cathode strips at ± 60º q Digital read-out chosen for both anodes and cathodes q Custom Front-End VLSI chip called VFA (CERN-TOTEM design) q Trigger implemented with groups of wires q Hits and trigger bits optically transmitted q LHC clock and fast commands compliant Insertion of one half-arm of T 1 (IP 5 '–' side). Three coordinates.

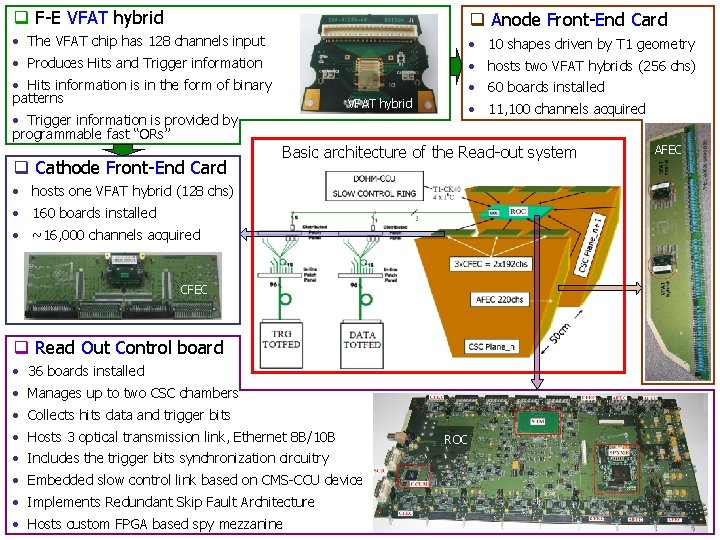

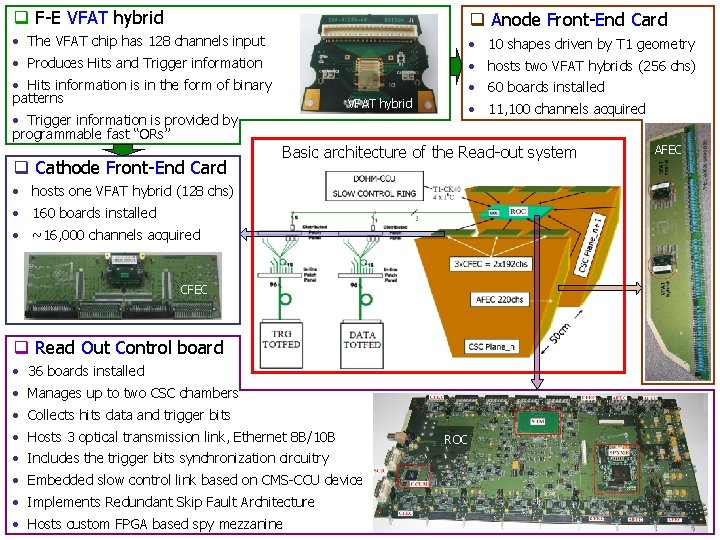

q F-E VFAT hybrid q Anode Front-End Card • The VFAT chip has 128 channels input • 10 shapes driven by T 1 geometry • Produces Hits and Trigger information • hosts two VFAT hybrids (256 chs) • Hits information is in the form of binary patterns • 60 boards installed VFAT hybrid • 11, 100 channels acquired • Trigger information is provided by programmable fast “ORs” q Cathode Front-End Card Basic architecture of the Read-out system • hosts one VFAT hybrid (128 chs) • 160 boards installed • ~16, 000 channels acquired CFEC q Read Out Control board • 36 boards installed • Manages up to two CSC chambers • Collects hits data and trigger bits • Hosts 3 optical transmission link, Ethernet 8 B/10 B • Includes the trigger bits synchronization circuitry • Embedded slow control link based on CMS-CCU device • Implements Redundant Skip Fault Architecture • Hosts custom FPGA based spy mezzanine ROC AFEC