Superscalars Dynamic Multiple issue processors Yogesh Reddy Kondareddy

- Slides: 13

Superscalars (Dynamic Multiple issue processors) Yogesh Reddy Kondareddy 1

A quick review… • Pipelining: Divide datapath into nearly equal tasks, to be performed serially and requiring non-overlapping resources. • One instruction is executed per clock period. • Throughput = Number of instructions executed in a clock period = 1 • CPI = 1 2

Instruction level parallelism (ILP) • Pipelining exploits the potential parallelism among instructions. This parallelism is called Instruction level parallelism (ILP). • Two methods to increase ILP: a) Increase the depth of pipelining b) Replicate the internal components of the computer so that it can launch multiple instructions in every pipeline stage. Consider the Automobile Assembly line example taught in the class. . 3

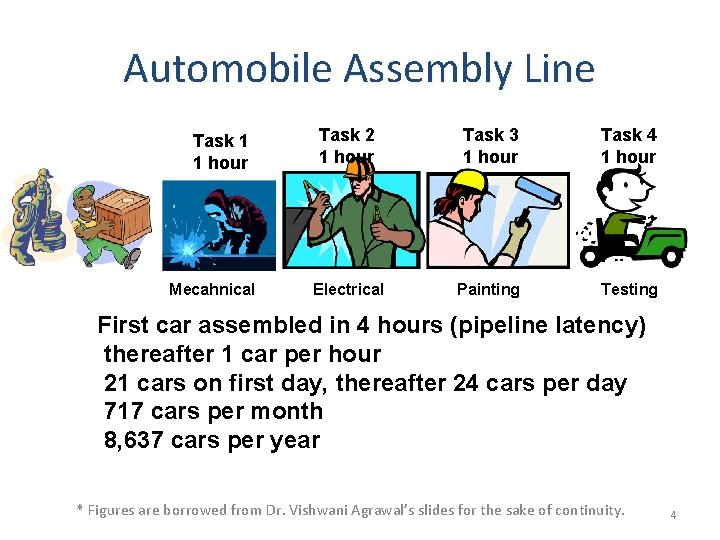

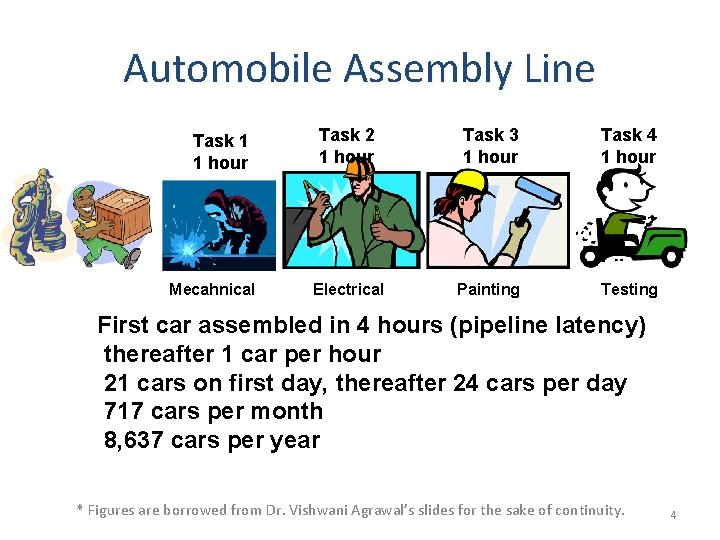

Automobile Assembly Line Task 1 1 hour Mecahnical Task 2 1 hour Task 3 1 hour Task 4 1 hour Electrical Painting Testing First car assembled in 4 hours (pipeline latency) thereafter 1 car per hour 21 cars on first day, thereafter 24 cars per day 717 cars per month 8, 637 cars per year * Figures are borrowed from Dr. Vishwani Agrawal’s slides for the sake of continuity. 4

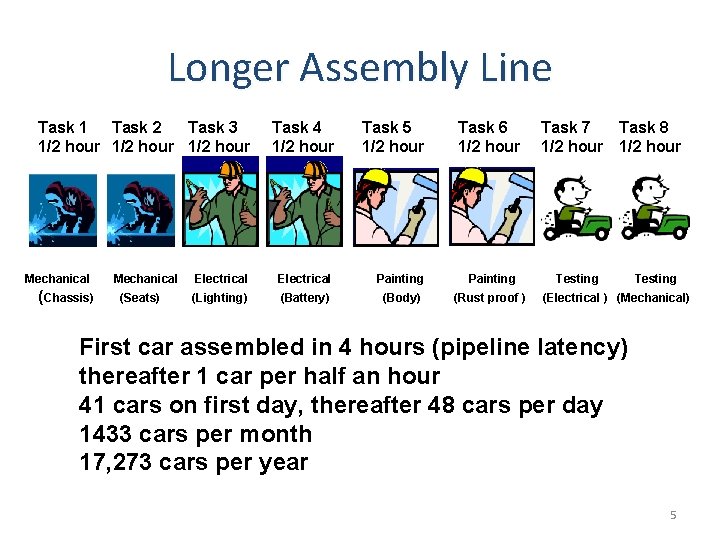

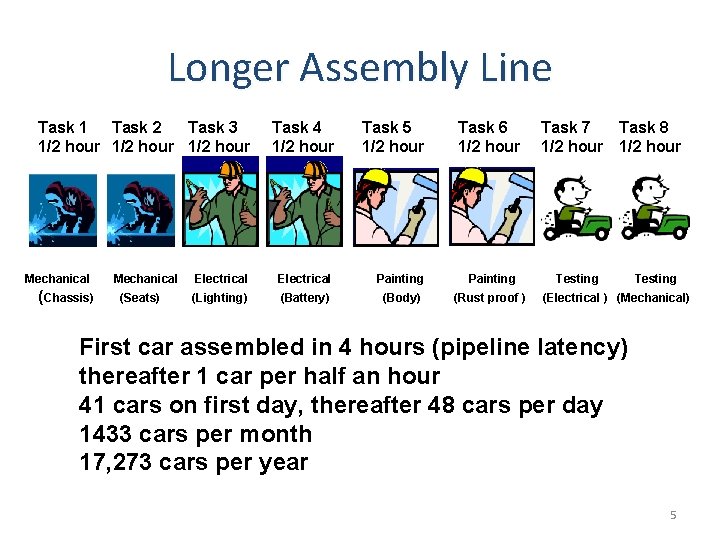

Longer Assembly Line Task 1 Task 2 Task 3 1/2 hour Mechanical (Chassis) Mechanical (Seats) Task 4 1/2 hour Task 5 1/2 hour Task 6 1/2 hour Electrical Painting (Lighting) (Battery) (Body) (Rust proof ) Task 7 Task 8 1/2 hour Testing (Electrical ) (Mechanical) First car assembled in 4 hours (pipeline latency) thereafter 1 car per half an hour 41 cars on first day, thereafter 48 cars per day 1433 cars per month 17, 273 cars per year 5

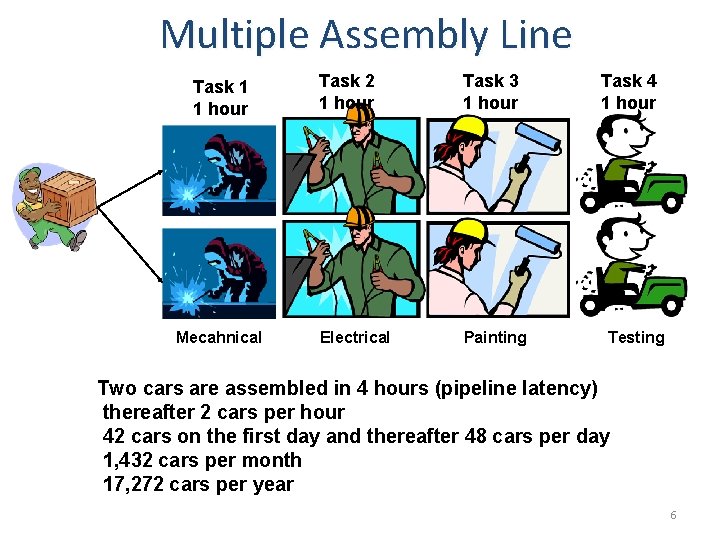

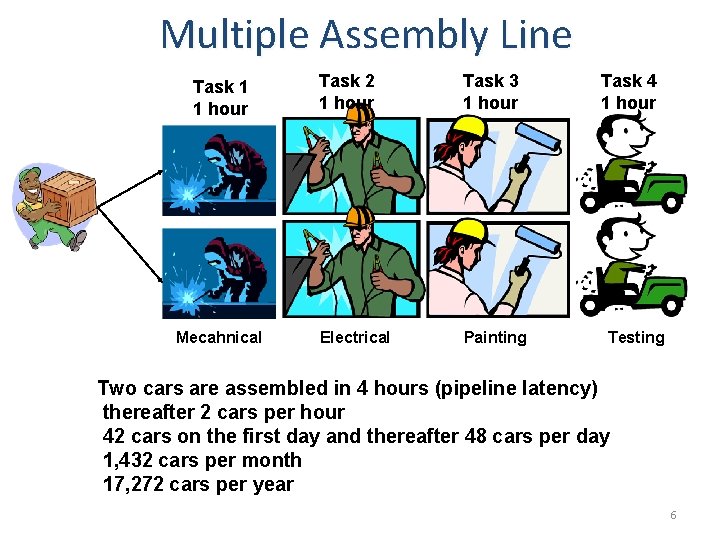

Multiple Assembly Line Task 1 1 hour Mecahnical Task 2 1 hour Task 3 1 hour Electrical Painting Task 4 1 hour Testing Two cars are assembled in 4 hours (pipeline latency) thereafter 2 cars per hour 42 cars on the first day and thereafter 48 cars per day 1, 432 cars per month 17, 272 cars per year 6

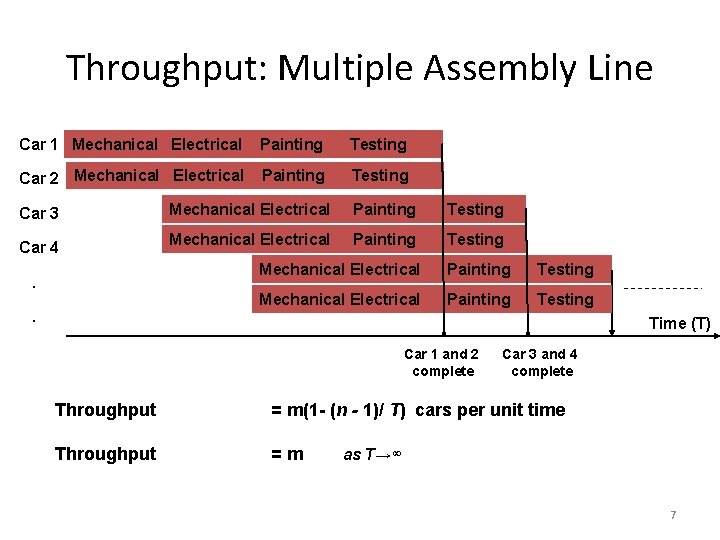

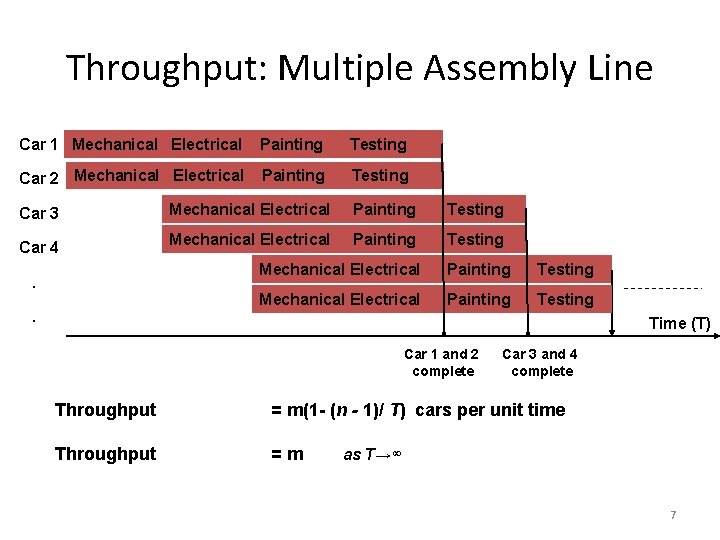

Throughput: Multiple Assembly Line Car 1 Mechanical Electrical Painting Testing Car 2 Mechanical Electrical Painting Testing Car 3 Car 4. . Mechanical Electrical Painting Testing Time (T) Car 1 and 2 complete Car 3 and 4 complete Throughput = m(1 - (n - 1)/ T) cars per unit time Throughput =m as T→∞ 7

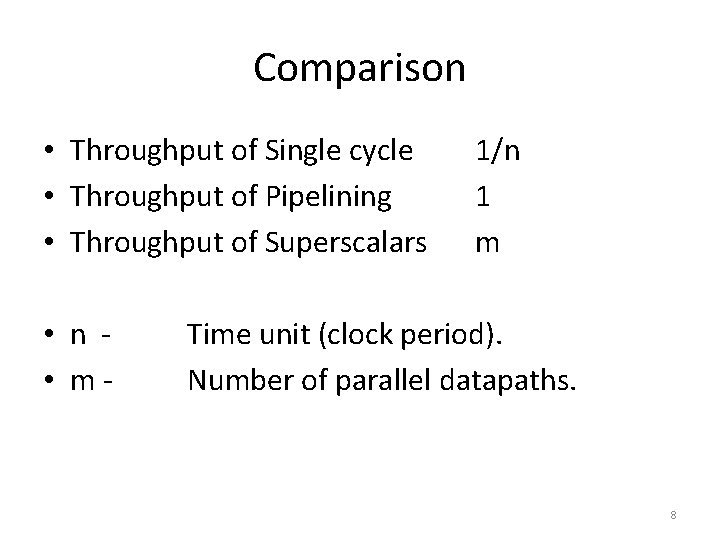

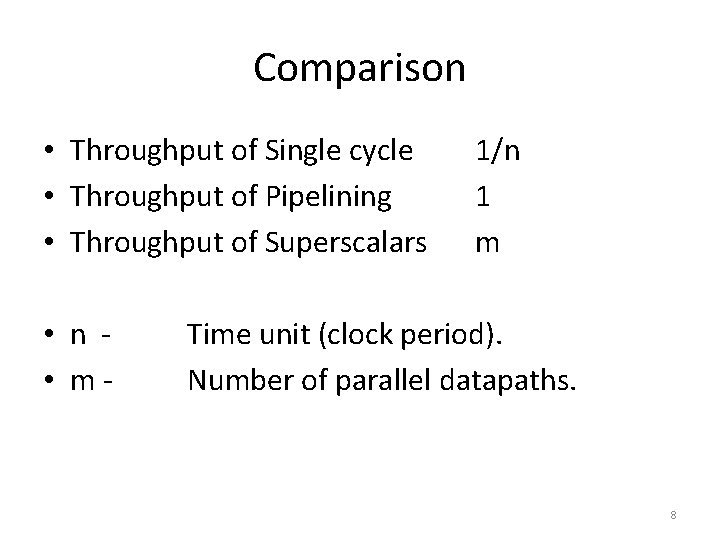

Comparison • Throughput of Single cycle • Throughput of Pipelining • Throughput of Superscalars • n • m- 1/n 1 m Time unit (clock period). Number of parallel datapaths. 8

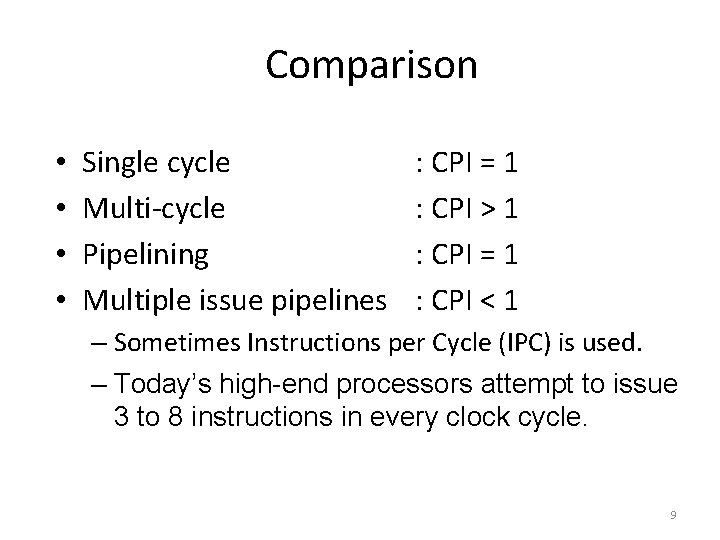

Comparison • • Single cycle Multi-cycle Pipelining Multiple issue pipelines : CPI = 1 : CPI > 1 : CPI = 1 : CPI < 1 – Sometimes Instructions per Cycle (IPC) is used. – Today’s high-end processors attempt to issue 3 to 8 instructions in every clock cycle. 9

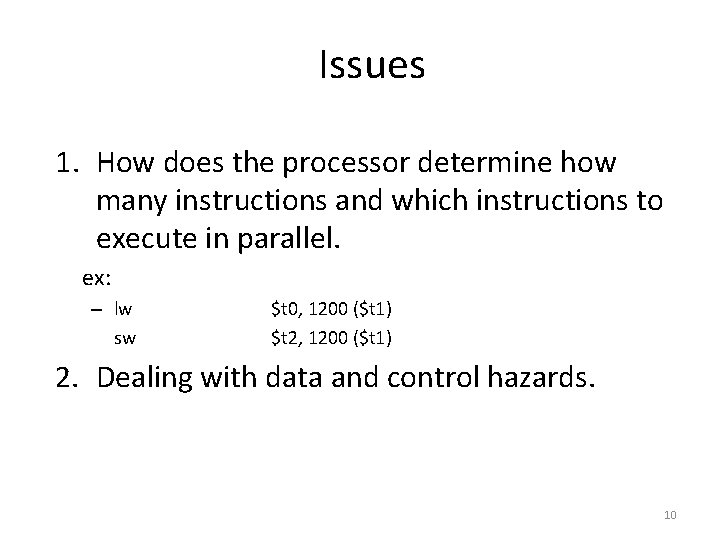

Issues 1. How does the processor determine how many instructions and which instructions to execute in parallel. ex: – lw sw $t 0, 1200 ($t 1) $t 2, 1200 ($t 1) 2. Dealing with data and control hazards. 10

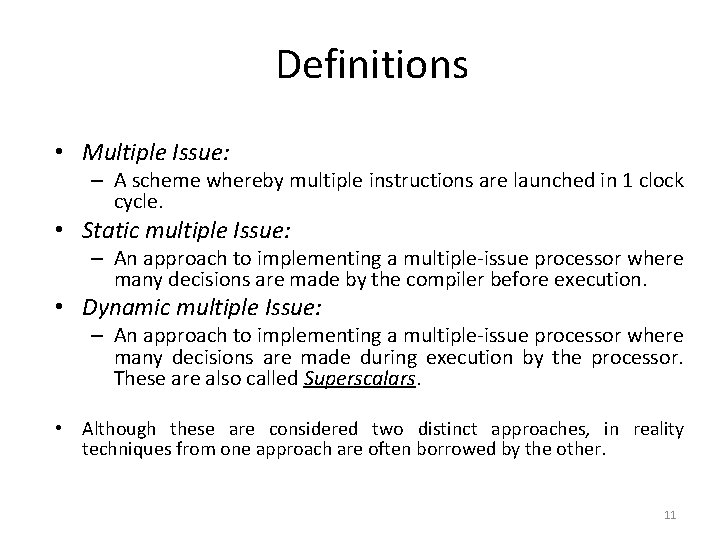

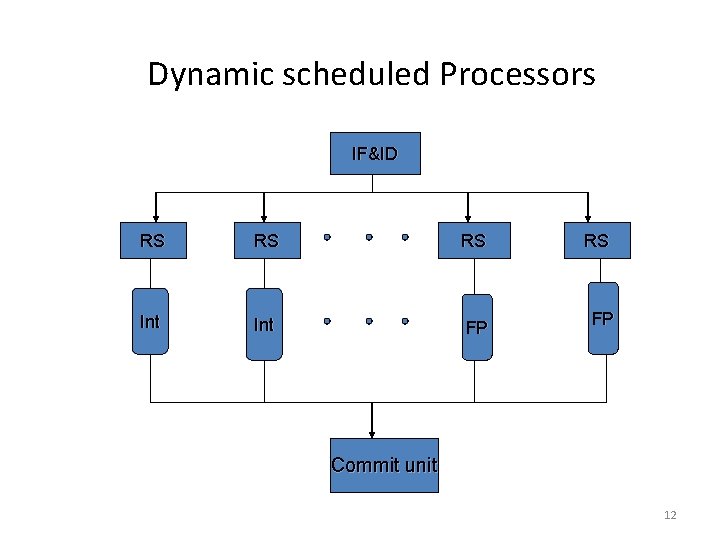

Definitions • Multiple Issue: – A scheme whereby multiple instructions are launched in 1 clock cycle. • Static multiple Issue: – An approach to implementing a multiple-issue processor where many decisions are made by the compiler before execution. • Dynamic multiple Issue: – An approach to implementing a multiple-issue processor where many decisions are made during execution by the processor. These are also called Superscalars. • Although these are considered two distinct approaches, in reality techniques from one approach are often borrowed by the other. 11

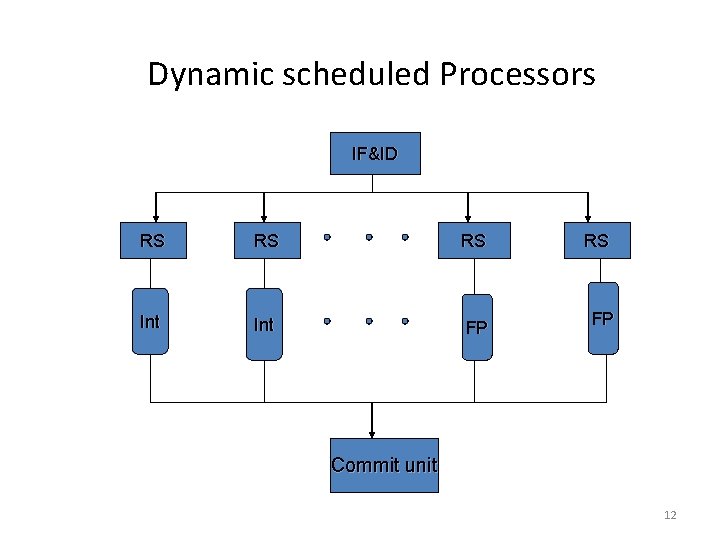

Dynamic scheduled Processors IF&ID RS RS Int FP FP Commit unit 12

References • Computer Organization & Design: The Hardware/Software Interface, 3 rd Ed. , D. A. Patterson & J. L. Hennessy, Morgan Kaufmann Publishers (Elsevier), 2005. • Computer architecture : a quantitative approach / David A. Patterson, John L. Hennessy ; with a contribution by David Goldberg. • http: //en. wikipedia. org/wiki/Superscalar. 13