Review SYSC 5603 ELG 6163 Digital Signal Processing

- Slides: 11

Review SYSC 5603 (ELG 6163) Digital Signal Processing Microprocessors, Software and Applications Miodrag Bolic 1

Lecture 2 • Real-time signal processing • Stream, block and vector processing • Parameters • • • Throughput; Range and precision of numbers; Data-dependent execution, Precedence relations within the algorithm, Global versus local communication of data; Random versus regular sequencing of data addresses; What are VLIW and RISC architectures What is the difference between CISC, RISC and VLIW What is Harvard architecture? Why the implementation of FIR filter takes a lot of time on RISC processors? What is the overhead? 2

Lecture 3 • Understand simple datapaths TMS 320 C 10 and ADSP -21 x • Understanding of basic features of DSP processors: · · Datapath configured for DSP Specialized instruction set Multiple memory banks and busses Specialized addressing modes: circular buffering, zero-overhead looping · Specialized peripherals • Difference between four generations of DSP processors • FIR filtering steps on ADSP -21 x • Basic characteristics of Blackfin processor 3

Lecture 4 • Understand basic assembly functions of TMS 320 C 6 x PDSPs • Architecture: datapath, instruction packing • What is linear assembly? What are Intrisic C functions? • What is the code optimization procedure? Describe the steps for assembly optimization 4

Lecture 5 • Understanding of Altera FPGA’a logic elements and Xilinx FPGA CLBs. • Altera and Xilinx memory blocks • Altera DSP blocks – how one can implement an FIR filter using DSP blocks • Design flow 5

Lecture 6 • Fixed-point representation • Fixed-point arithmetic • Simulation methods – why does one need range estimation? Why the statistics about each variable is needed? • Analytical methods – requires knowledge of formulae and derivations: · Coefficient quantization · Overflow & quantization in arithmetic operations - scaling to prevent overflow - quantization noise statistical modeling - limit cycle oscillations 6

Lecture 7 • • • Algorithm Representations and Iteration Bound Parallelism and Pipelining Retiming Unfolding Folding 7

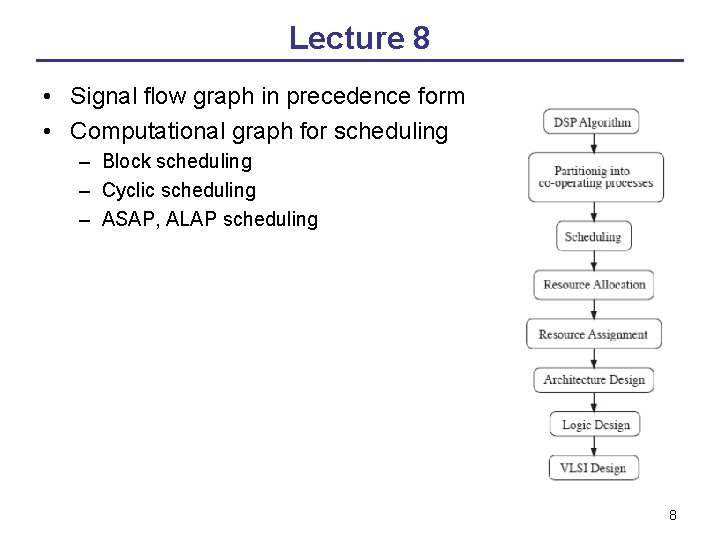

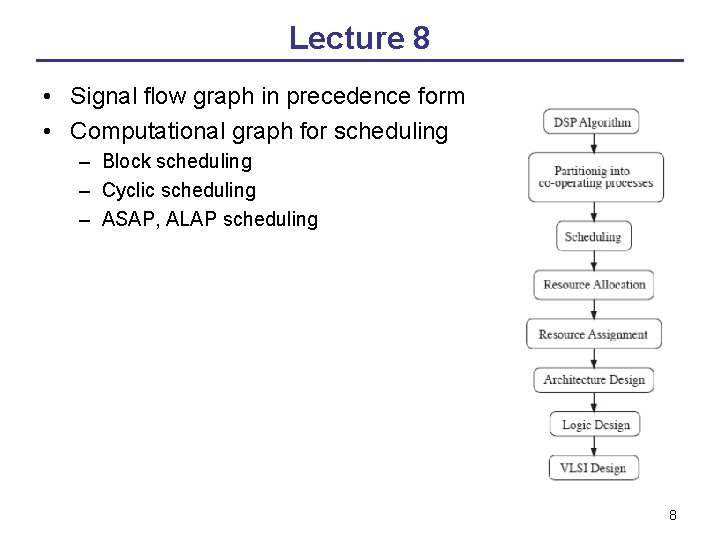

Lecture 8 • Signal flow graph in precedence form • Computational graph for scheduling – Block scheduling – Cyclic scheduling – ASAP, ALAP scheduling 8

Lecture 9 • Convolution – Fast convolution - Cook-Toom algorithm – Overlap and save • FIR filters – – Structures Polyphase FIR filters Parallel polyphase FIR Decimated FIR • Distributed arithmetic 9

Lecture 10 • FFT Introduction • Some FFT algorithms • FFT on PDSP – example of the program in C and Goertzel’s algorithm • FFT floating to fixed-point conversion • Hardware implementation of FFT – pipelined inmplementations 10

Lecture 11 • • IIR filters Pipelining Parallelism Lattice structure 11