Peer Instruction 5 LC3 Assembly Language CS 270

Peer Instruction #5: LC-3 Assembly Language CS 270, Spring Semester 2016 1

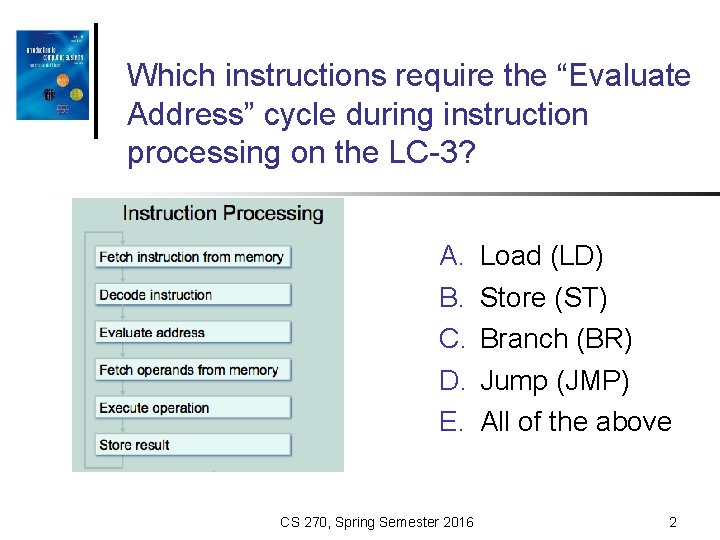

Which instructions require the “Evaluate Address” cycle during instruction processing on the LC-3? A. B. C. D. E. CS 270, Spring Semester 2016 Load (LD) Store (ST) Branch (BR) Jump (JMP) All of the above 2

What is the address space (number of locations), addressability (number of bits), and number of registers on the LC 3. A. B. C. D. E. 216, 8, 8 216, 16 216, 32, 16 232, 8 None of the above LC-3 Architecture CS 270, Spring Semester 2016 3

Translate the LC-3 instruction 0 x 4840 into LC-3 assembly code: A. B. C. D. E. JSR Label (Label at PC + 0 x 3 F) JSR Label (Label at PC + 0 x 40) JSRR R 3 JSRR R 1 None of the above LC-3 Instruction CS 270, Spring Semester 2016 4

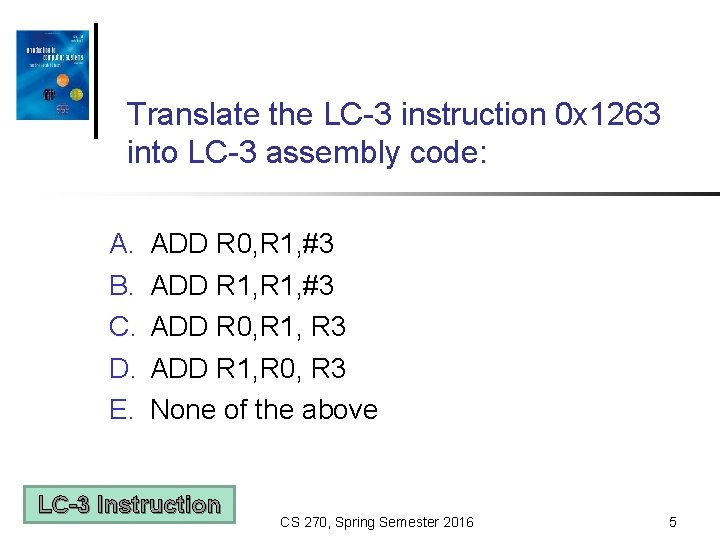

Translate the LC-3 instruction 0 x 1263 into LC-3 assembly code: A. B. C. D. E. ADD R 0, R 1, #3 ADD R 0, R 1, R 3 ADD R 1, R 0, R 3 None of the above LC-3 Instruction CS 270, Spring Semester 2016 5

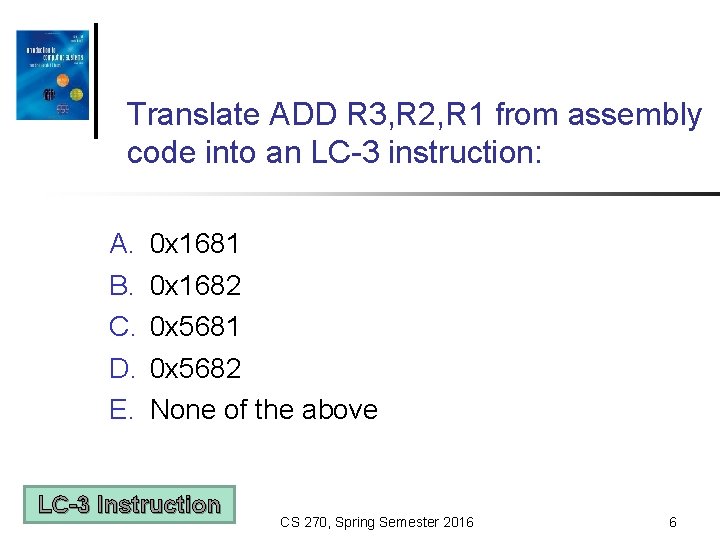

Translate ADD R 3, R 2, R 1 from assembly code into an LC-3 instruction: A. B. C. D. E. 0 x 1681 0 x 1682 0 x 5681 0 x 5682 None of the above LC-3 Instruction CS 270, Spring Semester 2016 6

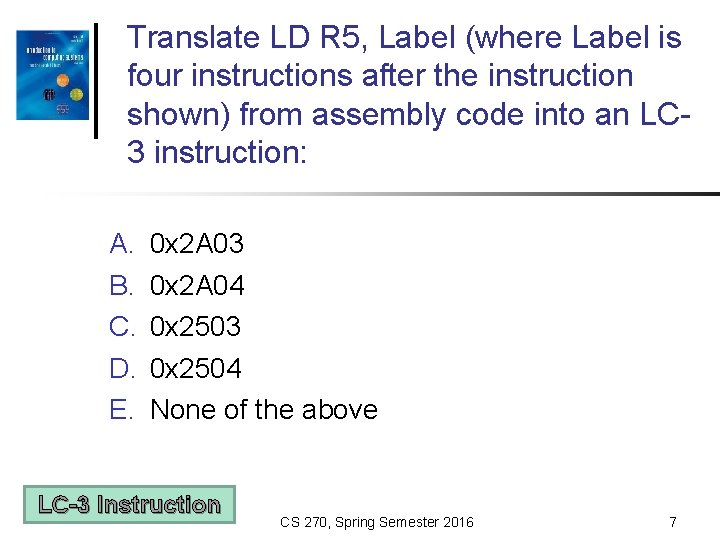

Translate LD R 5, Label (where Label is four instructions after the instruction shown) from assembly code into an LC 3 instruction: A. B. C. D. E. 0 x 2 A 03 0 x 2 A 04 0 x 2503 0 x 2504 None of the above LC-3 Instruction CS 270, Spring Semester 2016 7

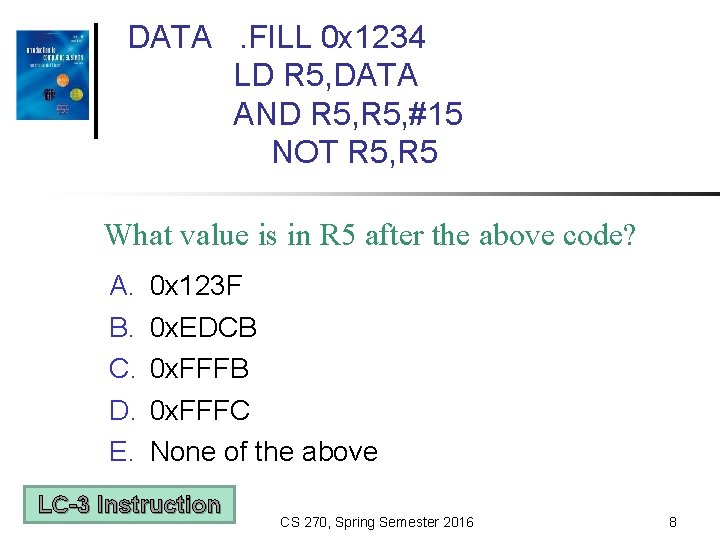

DATA. FILL 0 x 1234 LD R 5, DATA AND R 5, #15 NOT R 5, R 5 What value is in R 5 after the above code? A. B. C. D. E. 0 x 123 F 0 x. EDCB 0 x. FFFC None of the above LC-3 Instruction CS 270, Spring Semester 2016 8

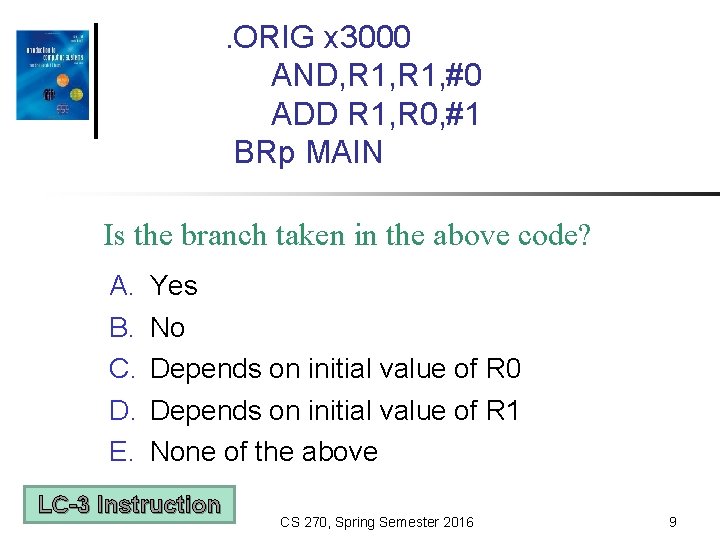

. ORIG x 3000 AND, R 1, #0 ADD R 1, R 0, #1 BRp MAIN Is the branch taken in the above code? A. B. C. D. E. Yes No Depends on initial value of R 0 Depends on initial value of R 1 None of the above LC-3 Instruction CS 270, Spring Semester 2016 9

- Slides: 9