Lect 10 Stimulus Response Applying input stimulus to

- Slides: 14

Lect 10 - Stimulus & Response • • • Applying input stimulus to a design Creating clock signals Other waveforms Synchronizing inputs Using text I/O EE 694 v-Verification-Lect 10 -1 -

Stimulus • The purpose of writing testbenches is to apply stimulus signals to a design and observe the response of the design to those signals • The response is then compared to both the value and timing expected • Greatest challenge with stimulus is making sure they have values and timing that represents what the physical design will see in the environment EE 694 v-Verification-Lect 10 -2 -

Applying Stimulus • Generating stimulus is the process of providing input signals, both the value and the timing, to a design • Inputs vary from very simple to complex • Inputs have relationships that establish specific states in the design under test EE 694 v-Verification-Lect 10 -3 -

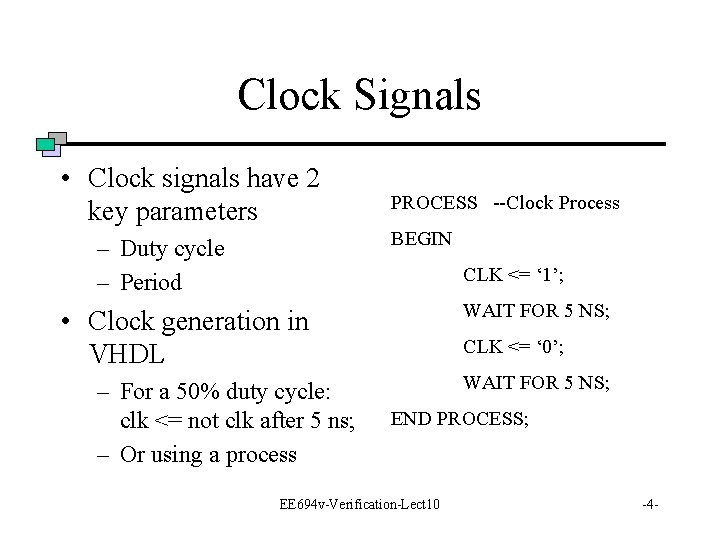

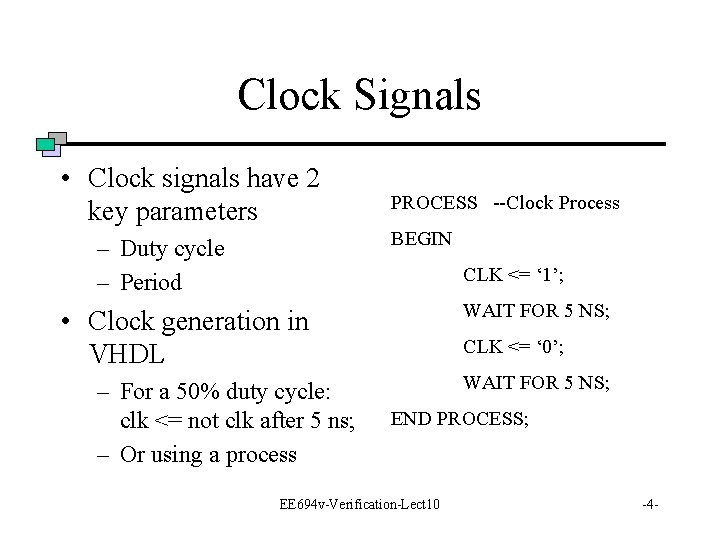

Clock Signals • Clock signals have 2 key parameters PROCESS --Clock Process BEGIN – Duty cycle – Period CLK <= ‘ 1’; WAIT FOR 5 NS; • Clock generation in VHDL – For a 50% duty cycle: clk <= not clk after 5 ns; – Or using a process CLK <= ‘ 0’; WAIT FOR 5 NS; END PROCESS; EE 694 v-Verification-Lect 10 -4 -

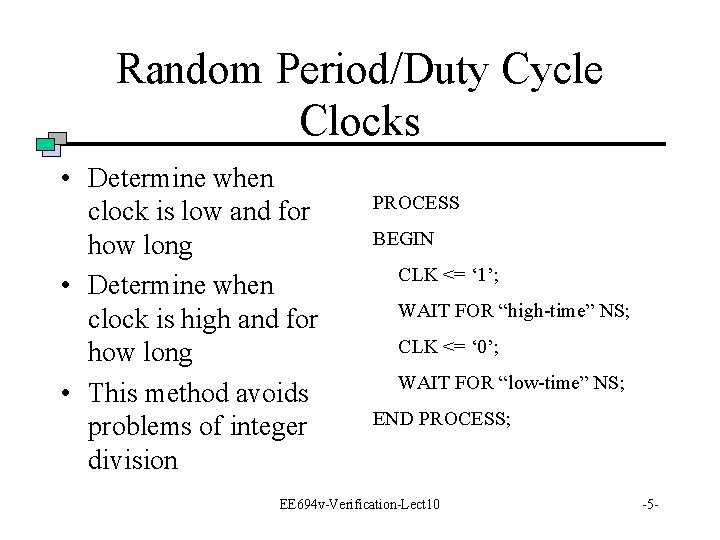

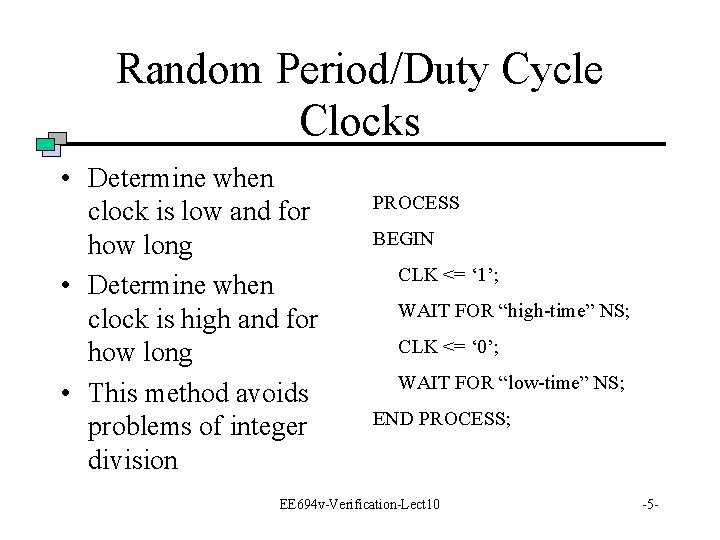

Random Period/Duty Cycle Clocks • Determine when clock is low and for how long • Determine when clock is high and for how long • This method avoids problems of integer division PROCESS BEGIN CLK <= ‘ 1’; WAIT FOR “high-time” NS; CLK <= ‘ 0’; WAIT FOR “low-time” NS; END PROCESS; EE 694 v-Verification-Lect 10 -5 -

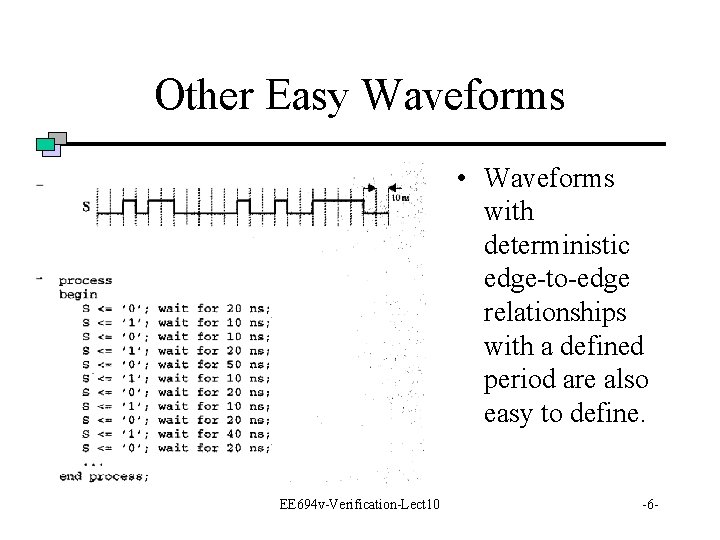

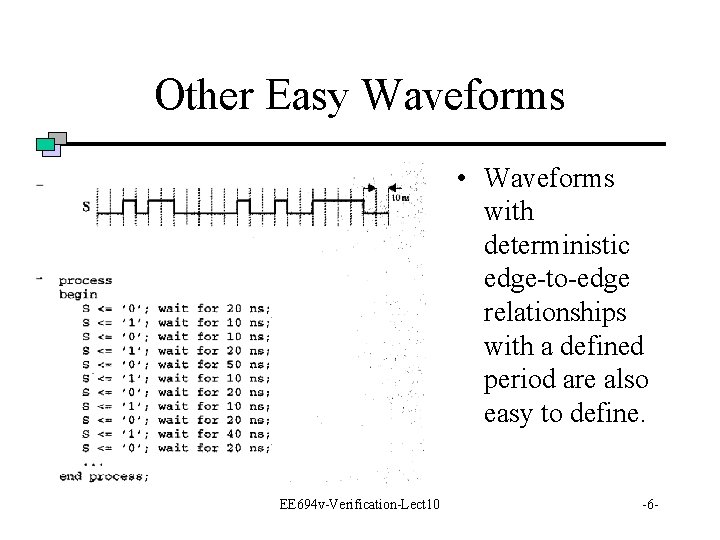

Other Easy Waveforms • Waveforms with deterministic edge-to-edge relationships with a defined period are also easy to define. EE 694 v-Verification-Lect 10 -6 -

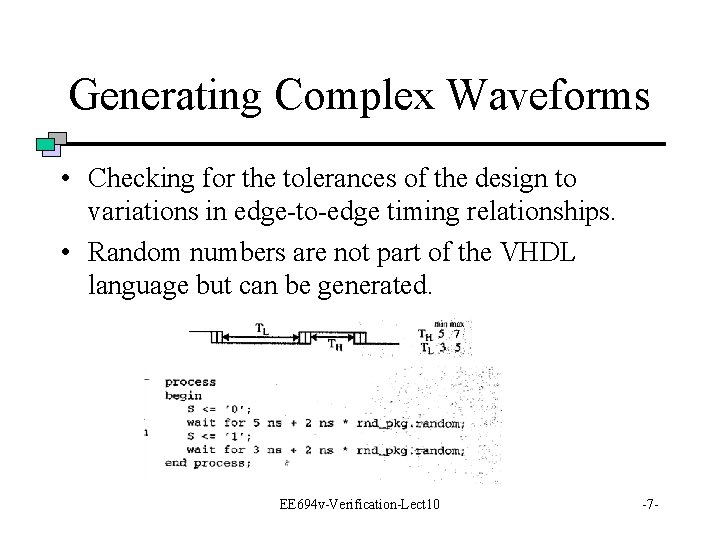

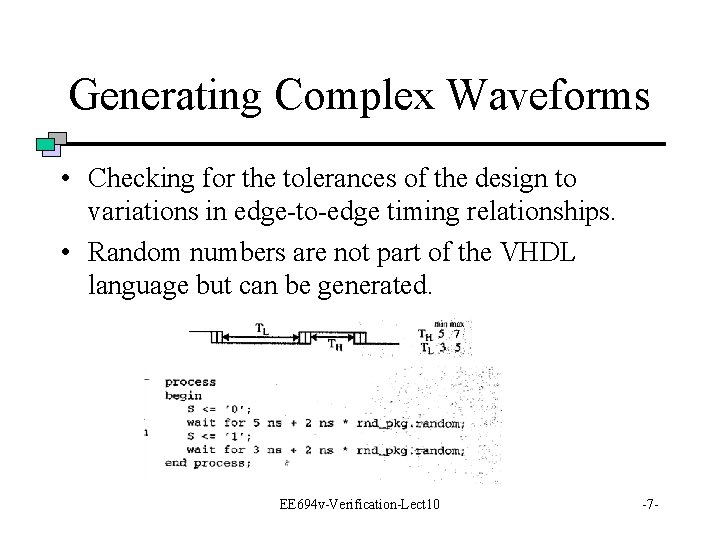

Generating Complex Waveforms • Checking for the tolerances of the design to variations in edge-to-edge timing relationships. • Random numbers are not part of the VHDL language but can be generated. EE 694 v-Verification-Lect 10 -7 -

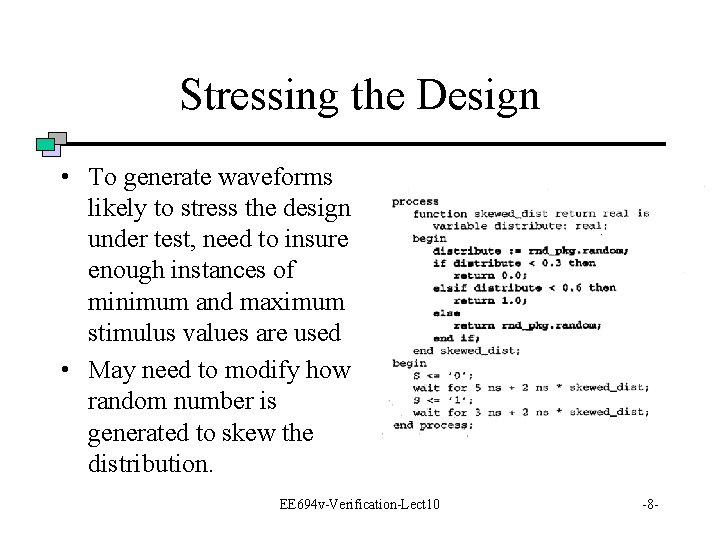

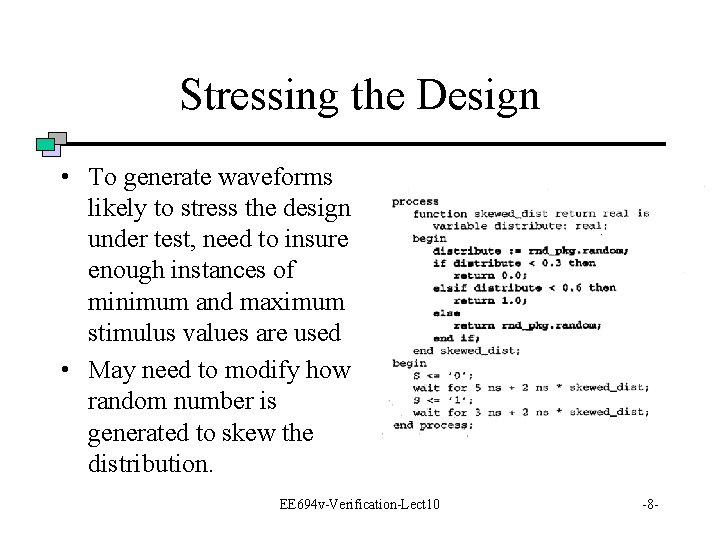

Stressing the Design • To generate waveforms likely to stress the design under test, need to insure enough instances of minimum and maximum stimulus values are used • May need to modify how random number is generated to skew the distribution. EE 694 v-Verification-Lect 10 -8 -

Generating Synchronized Waveforms • Stimulus is never composed of a single signal (even if the design is very small) • Must align edges of inputs (or don’t align) such that it mimics the real environment and the operation of the device under test. EE 694 v-Verification-Lect 10 -9 -

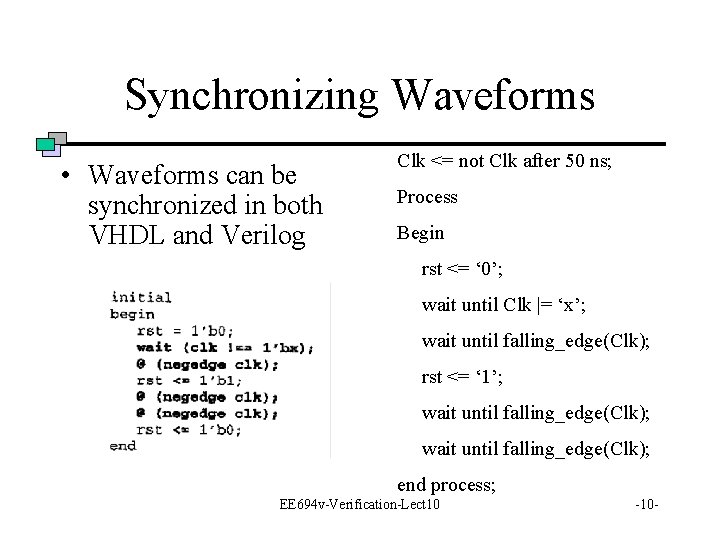

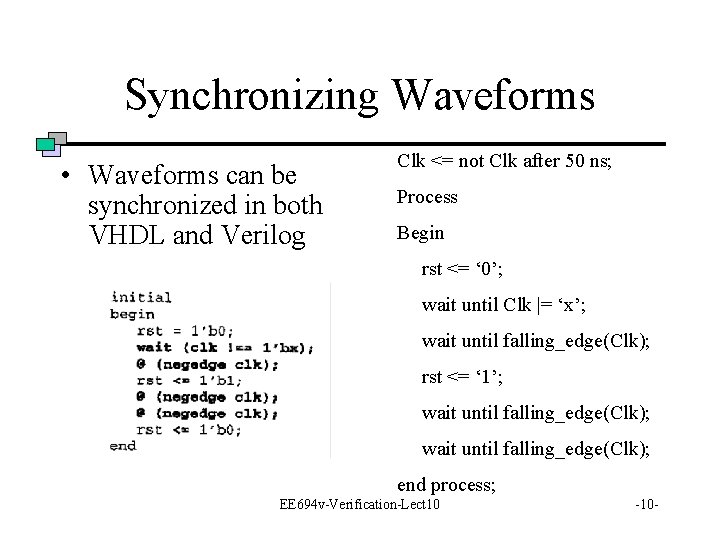

Synchronizing Waveforms • Waveforms can be synchronized in both VHDL and Verilog Clk <= not Clk after 50 ns; Process Begin rst <= ‘ 0’; wait until Clk |= ‘x’; wait until falling_edge(Clk); rst <= ‘ 1’; wait until falling_edge(Clk); end process; EE 694 v-Verification-Lect 10 -10 -

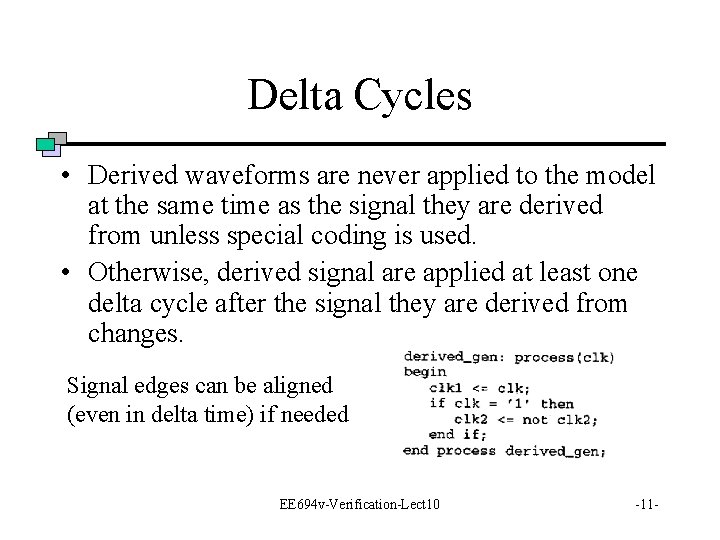

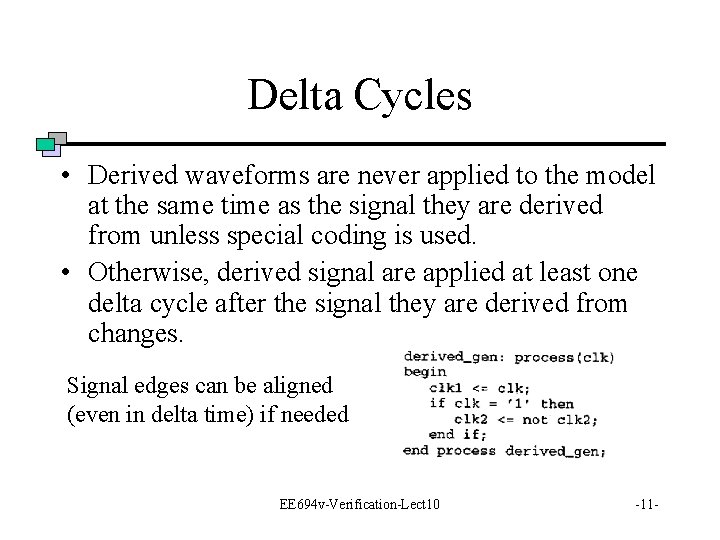

Delta Cycles • Derived waveforms are never applied to the model at the same time as the signal they are derived from unless special coding is used. • Otherwise, derived signal are applied at least one delta cycle after the signal they are derived from changes. Signal edges can be aligned (even in delta time) if needed EE 694 v-Verification-Lect 10 -11 -

Synchronizing Inputs • The interface specification for the application of inputs will never specify signal-to-signal synchronization as exactly zero. • Delays in real interfaces are going to be varied • Clocks may synchronize inputs or multiple inputs to a design • If inputs are synchronized and if the portion of the design that synchronizes them is not part of the design under test, the inputs need to be synchronized by the testbench. EE 694 v-Verification-Lect 10 -12 -

Using Files for Input Data • An excellent approach to a verification effort is transaction based verification where each set of vectors is a transaction. • In VHDL the text I/O features of the language can be used such that the value of input vectors are stored in a file • Stimulus signal values are read from this file • Values are read using text I/O and assigned to signals • Also possible to include the correct response in the file along with the inputs EE 694 v-Verification-Lect 10 -13 -

Using Files (cont. ) • Allows for easy modifications to both the stimulus and the expected response as no recompile if needed. Also, it becomes very easy to add or modify the stimulus vectors/expected result. • So it is easy to add more test transactions. • Text I/O is very different in the 1987 and the 1993 versions of the language. Both are line I/O orientated philosophy. EE 694 v-Verification-Lect 10 -14 -