Ernest Cachia University of Malta RealTime System Development

- Slides: 10

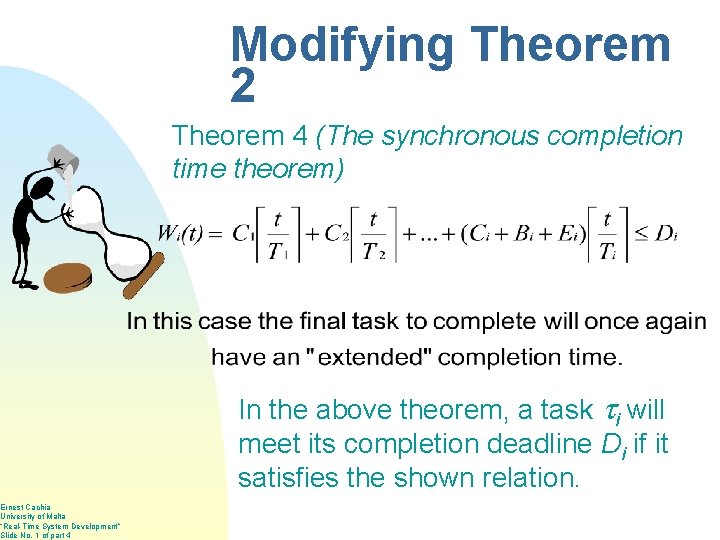

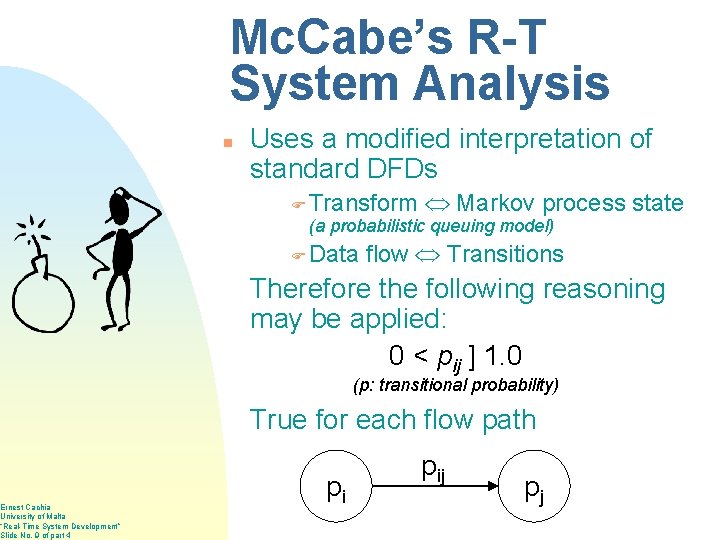

Ernest Cachia University of Malta “Real-Time System Development” Slide No. 1 of part 4 Modifying Theorem 2 Theorem 4 (The synchronous completion time theorem) In the above theorem, a task i will meet its completion deadline Di if it satisfies the shown relation.

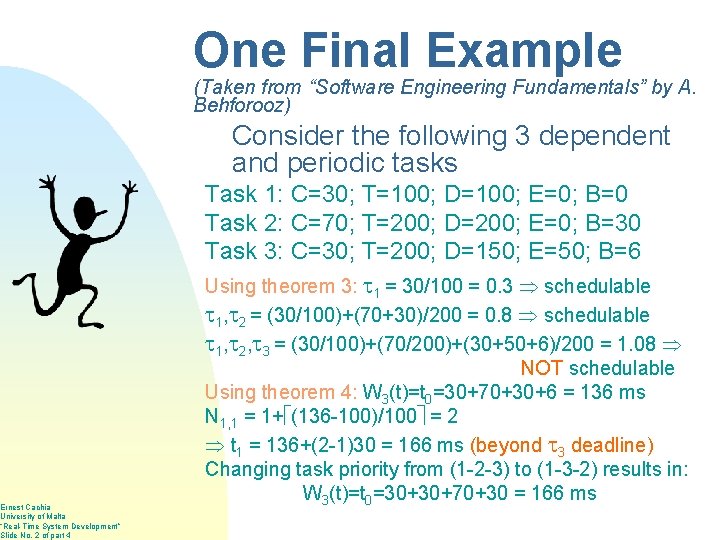

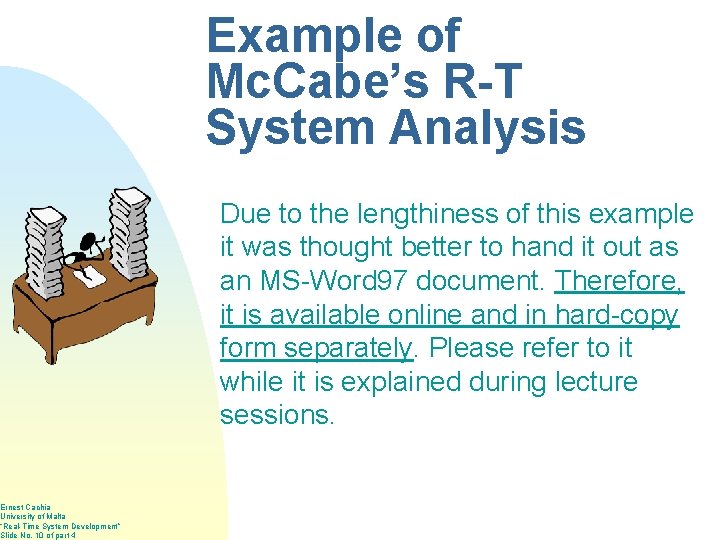

Ernest Cachia University of Malta “Real-Time System Development” Slide No. 2 of part 4 One Final Example (Taken from “Software Engineering Fundamentals” by A. Behforooz) Consider the following 3 dependent and periodic tasks Task 1: C=30; T=100; D=100; E=0; B=0 Task 2: C=70; T=200; D=200; E=0; B=30 Task 3: C=30; T=200; D=150; E=50; B=6 Using theorem 3: 1 = 30/100 = 0. 3 schedulable 1, 2 = (30/100)+(70+30)/200 = 0. 8 schedulable 1, 2, 3 = (30/100)+(70/200)+(30+50+6)/200 = 1. 08 NOT schedulable Using theorem 4: W 3(t)=t 0=30+70+30+6 = 136 ms N 1, 1 = 1+ (136 -100)/100 = 2 t 1 = 136+(2 -1)30 = 166 ms (beyond 3 deadline) Changing task priority from (1 -2 -3) to (1 -3 -2) results in: W 3(t)=t 0=30+30+70+30 = 166 ms

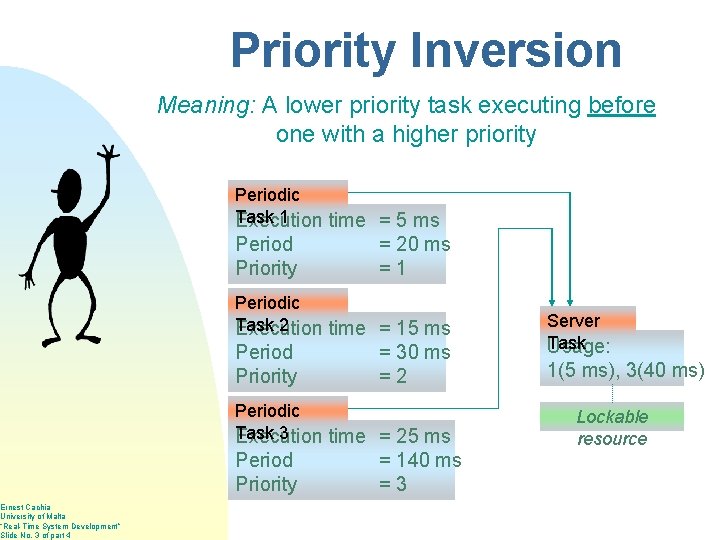

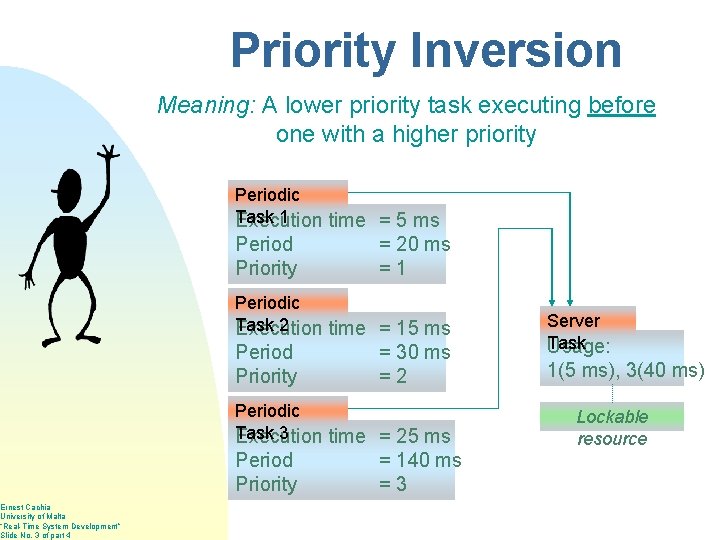

Ernest Cachia University of Malta “Real-Time System Development” Slide No. 3 of part 4 Priority Inversion Meaning: A lower priority task executing before one with a higher priority Periodic Task 1 Execution time = 5 ms Period Priority = 20 ms =1 Periodic Task 2 Execution time = 15 ms Period Priority = 30 ms =2 Periodic Task 3 Execution time = 25 ms Period Priority = 140 ms =3 Server Task Usage: 1(5 ms), 3(40 ms) Lockable resource

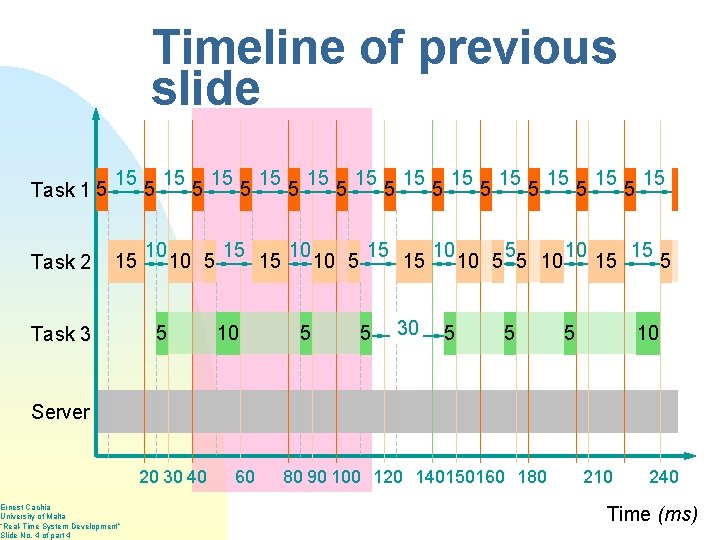

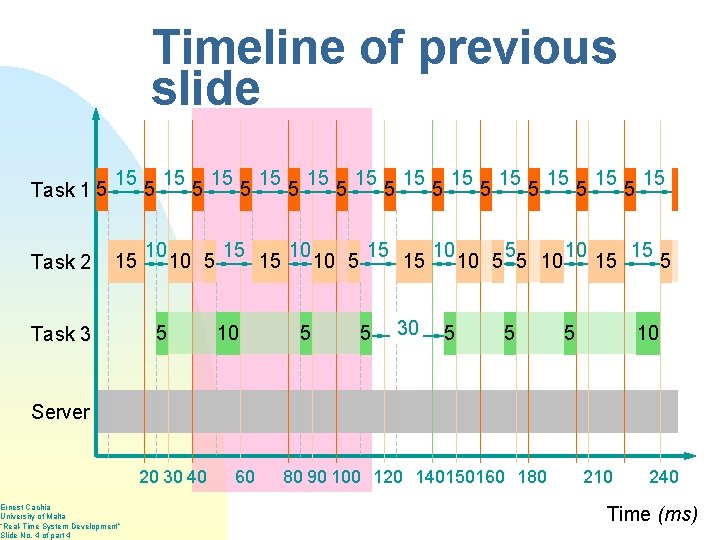

Timeline of previous slide Task 1 5 Task 2 15 15 Task 3 5 15 10 5 5 5 15 10 15 15 10 5 5 15 15 30 5 15 10 5 5 15 5 10 15 10 5 5 10 15 5 10 Server Ernest Cachia University of Malta “Real-Time System Development” Slide No. 4 of part 4 20 30 40 60 80 90 100 120 140150160 180 210 240 Time (ms)

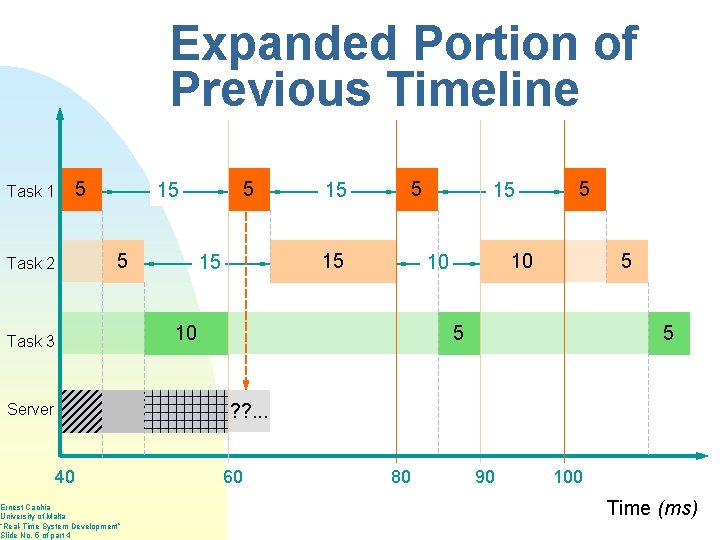

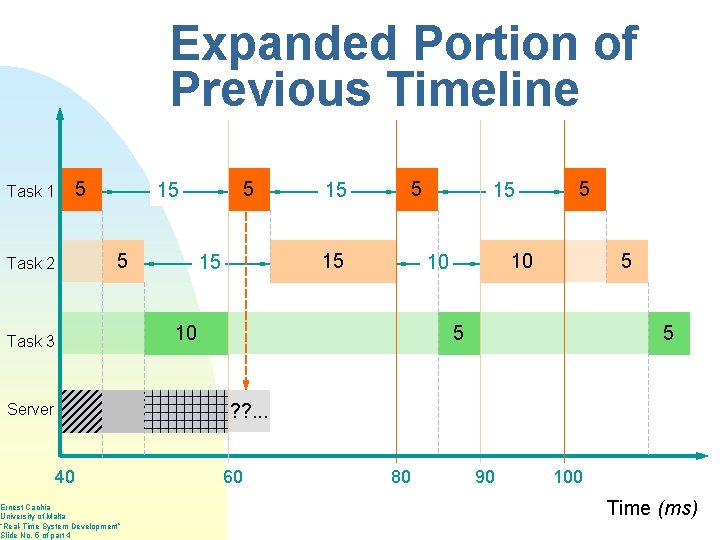

Expanded Portion of Previous Timeline 5 Task 1 5 Task 2 5 15 15 15 5 10 10 10 Task 3 15 5 ? ? . . . Server 40 Ernest Cachia University of Malta “Real-Time System Development” Slide No. 5 of part 4 60 80 90 100 Time (ms)

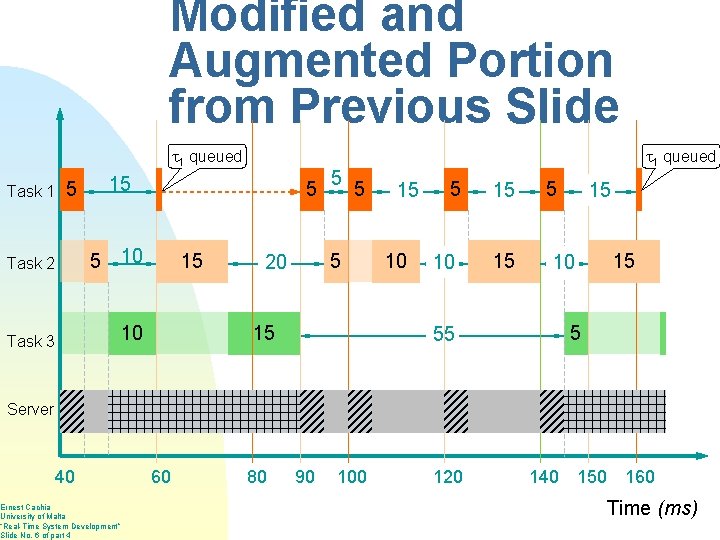

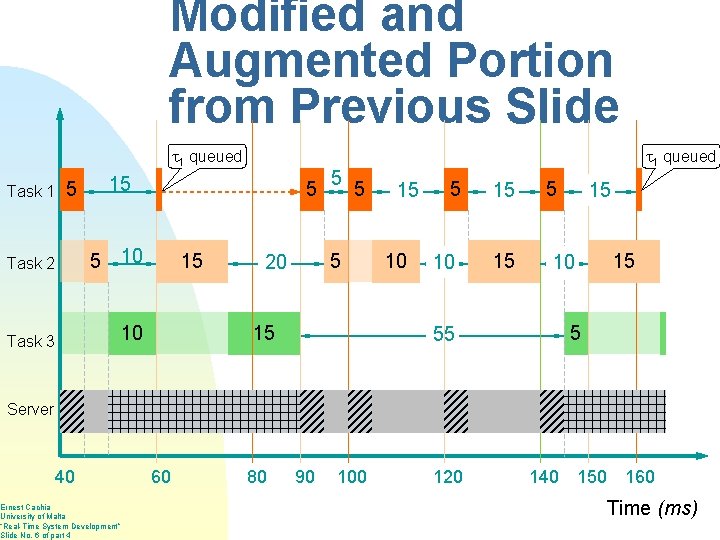

Modified and Augmented Portion from Previous Slide 1 queued Task 1 5 15 Task 2 5 10 Task 3 10 5 15 5 1 queued 5 5 20 15 15 10 55 15 15 10 15 5 Server 40 Ernest Cachia University of Malta “Real-Time System Development” Slide No. 6 of part 4 60 80 90 100 120 140 150 160 Time (ms)

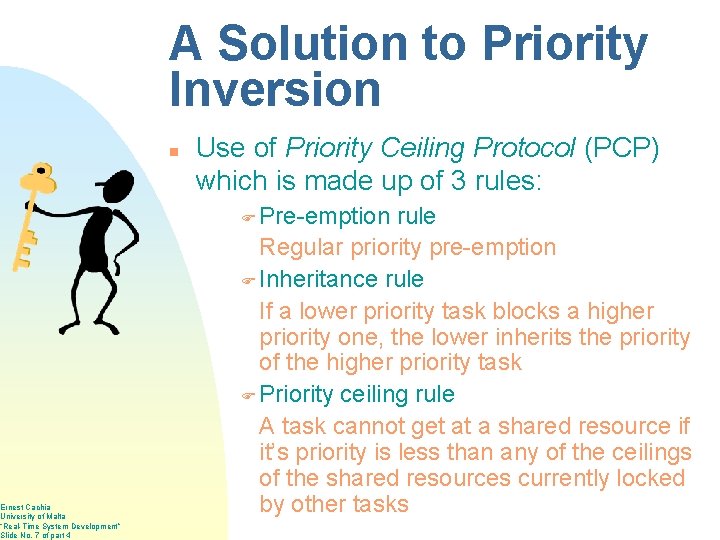

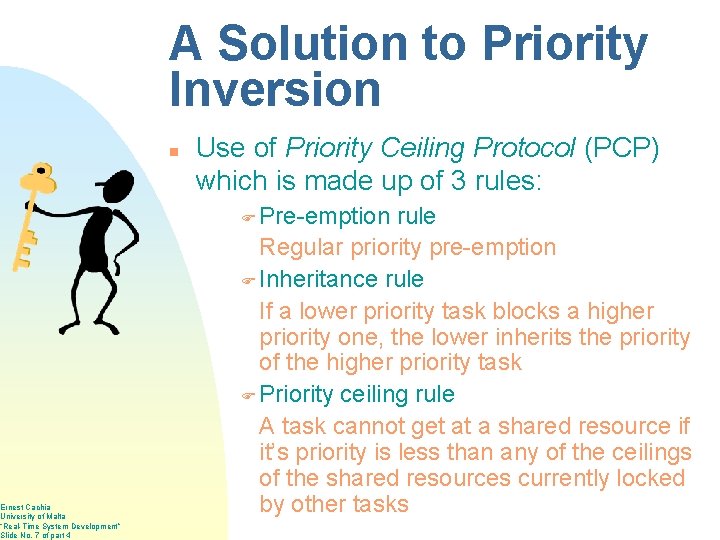

Ernest Cachia University of Malta “Real-Time System Development” Slide No. 7 of part 4 A Solution to Priority Inversion n Use of Priority Ceiling Protocol (PCP) which is made up of 3 rules: F Pre-emption rule Regular priority pre-emption F Inheritance rule If a lower priority task blocks a higher priority one, the lower inherits the priority of the higher priority task F Priority ceiling rule A task cannot get at a shared resource if it’s priority is less than any of the ceilings of the shared resources currently locked by other tasks

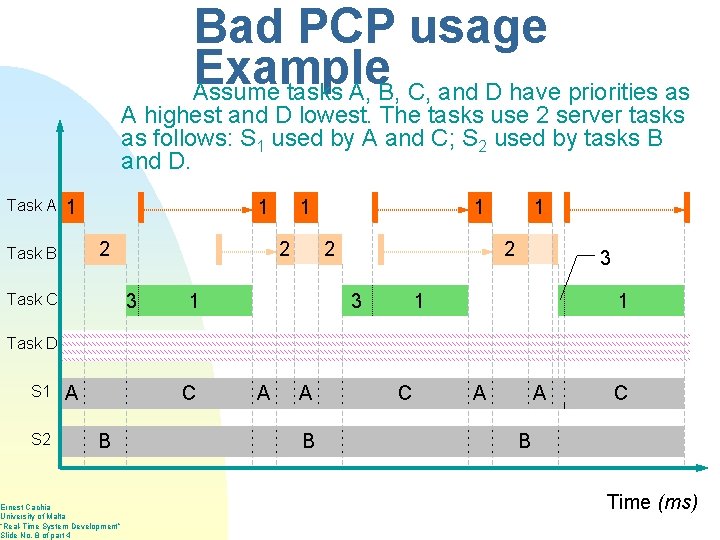

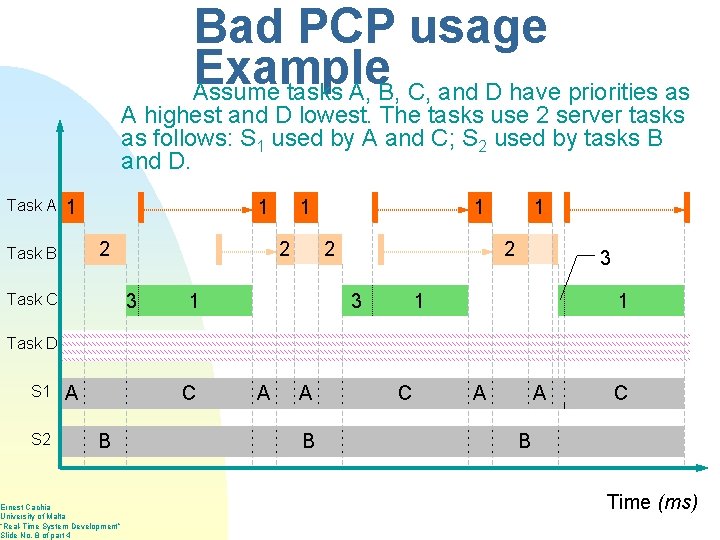

Bad PCP usage Example Assume tasks A, B, C, and D have priorities as A highest and D lowest. The tasks use 2 server tasks as follows: S 1 used by A and C; S 2 used by tasks B and D. Task A 1 1 2 Task B 2 3 Task C 1 1 2 3 3 1 1 Task D S 1 S 2 A C B Ernest Cachia University of Malta “Real-Time System Development” Slide No. 8 of part 4 A A B C A A C B Time (ms)

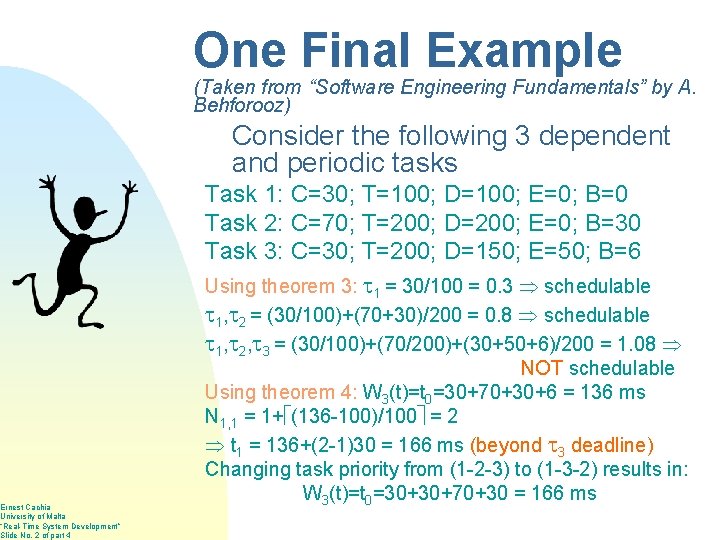

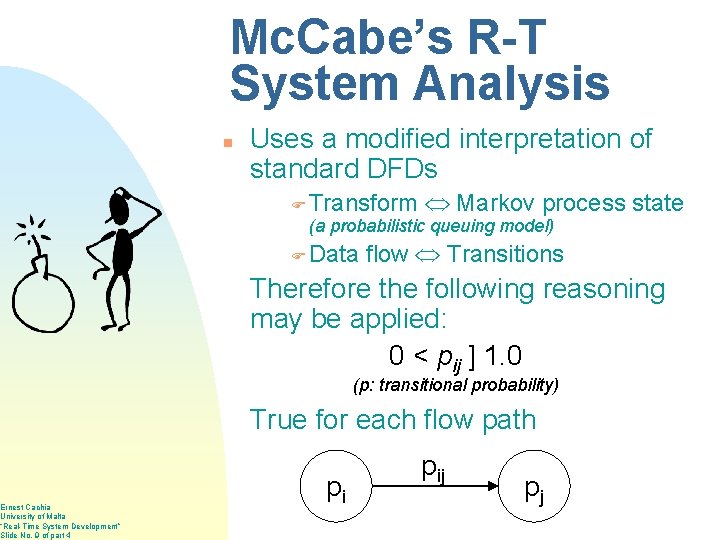

Ernest Cachia University of Malta “Real-Time System Development” Slide No. 9 of part 4 Mc. Cabe’s R-T System Analysis n Uses a modified interpretation of standard DFDs F Transform Markov process state (a probabilistic queuing model) F Data flow Transitions Therefore the following reasoning may be applied: 0 < pij ] 1. 0 (p: transitional probability) True for each flow path pi pij pj

Ernest Cachia University of Malta “Real-Time System Development” Slide No. 10 of part 4 Example of Mc. Cabe’s R-T System Analysis Due to the lengthiness of this example it was thought better to hand it out as an MS-Word 97 document. Therefore, it is available online and in hard-copy form separately. Please refer to it while it is explained during lecture sessions.