Computer Architecture Homework 1 Veton Kpuska Problem 2

Computer Architecture Homework #1 Veton Këpuska

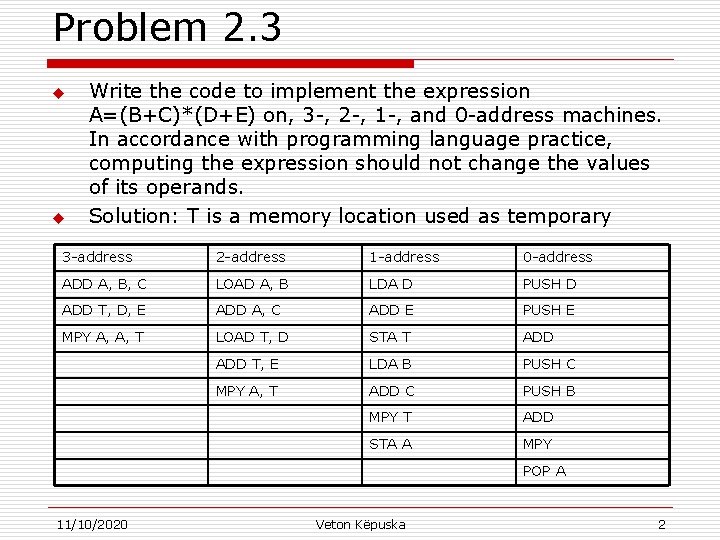

Problem 2. 3 u u Write the code to implement the expression A=(B+C)*(D+E) on, 3 -, 2 -, 1 -, and 0 -address machines. In accordance with programming language practice, computing the expression should not change the values of its operands. Solution: T is a memory location used as temporary 3 -address 2 -address 1 -address 0 -address ADD A, B, C LOAD A, B LDA D PUSH D ADD T, D, E ADD A, C ADD E PUSH E MPY A, A, T LOAD T, D STA T ADD T, E LDA B PUSH C MPY A, T ADD C PUSH B MPY T ADD STA A MPY POP A 11/10/2020 Veton Këpuska 2

Problem 2. 4 u u Write SRC code to implement the expression in Exercise 2. 3 Solution: n Assume that operands and results are stored in memory addresses that can be accessed with direct addressing. Also assume that ARC has a multiply instruction, mpy, that uses format 6. ld r 0, B ld r 1, C add r 0, r 1 ld r 1, D ld r 2, E add r 1, r 2 mpy r 0, r 1 st r 0, A 11/10/2020 # # # # r 0←M[b] r 1←M[c] r 0←r 0+r 1 r 1←M[d] r 2←M[e] r 1←r 1+r 2 r 0←r 0+r 1 r 0→M[a] Veton Këpuska (B+C) (D+E) (B+C)*(D+E) A=(B+C)*(D+E) 3

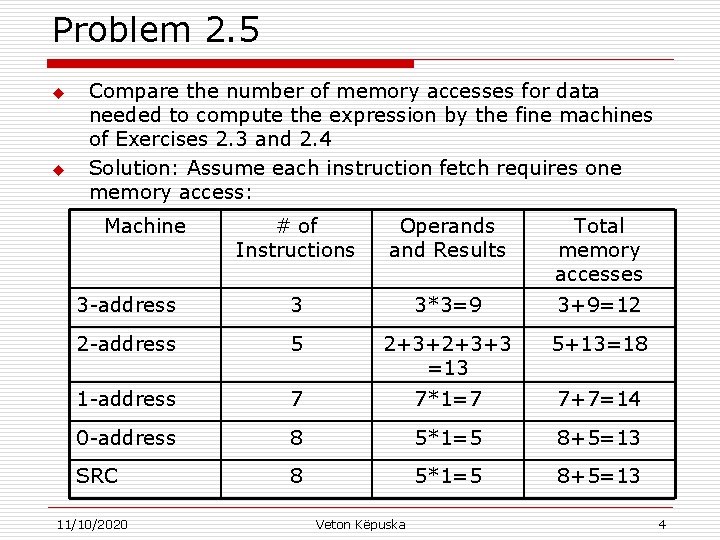

Problem 2. 5 u u Compare the number of memory accesses for data needed to compute the expression by the fine machines of Exercises 2. 3 and 2. 4 Solution: Assume each instruction fetch requires one memory access: Machine # of Instructions Operands and Results Total memory accesses 3 -address 3 3*3=9 3+9=12 2 -address 5 2+3+3 =13 5+13=18 1 -address 7 7*1=7 7+7=14 0 -address 8 5*1=5 8+5=13 SRC 8 5*1=5 8+5=13 11/10/2020 Veton Këpuska 4

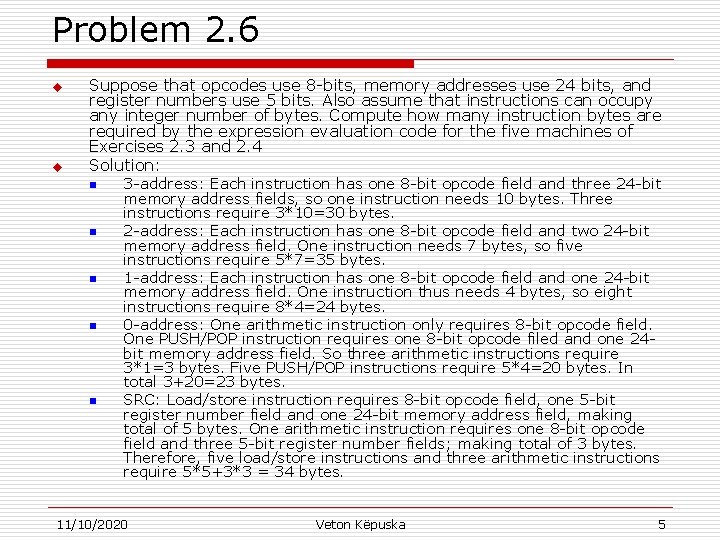

Problem 2. 6 u u Suppose that opcodes use 8 -bits, memory addresses use 24 bits, and register numbers use 5 bits. Also assume that instructions can occupy any integer number of bytes. Compute how many instruction bytes are required by the expression evaluation code for the five machines of Exercises 2. 3 and 2. 4 Solution: n n n 3 -address: Each instruction has one 8 -bit opcode field and three 24 -bit memory address fields, so one instruction needs 10 bytes. Three instructions require 3*10=30 bytes. 2 -address: Each instruction has one 8 -bit opcode field and two 24 -bit memory address field. One instruction needs 7 bytes, so five instructions require 5*7=35 bytes. 1 -address: Each instruction has one 8 -bit opcode field and one 24 -bit memory address field. One instruction thus needs 4 bytes, so eight instructions require 8*4=24 bytes. 0 -address: One arithmetic instruction only requires 8 -bit opcode field. One PUSH/POP instruction requires one 8 -bit opcode filed and one 24 bit memory address field. So three arithmetic instructions require 3*1=3 bytes. Five PUSH/POP instructions require 5*4=20 bytes. In total 3+20=23 bytes. SRC: Load/store instruction requires 8 -bit opcode field, one 5 -bit register number field and one 24 -bit memory address field, making total of 5 bytes. One arithmetic instruction requires one 8 -bit opcode field and three 5 -bit register number fields; making total of 3 bytes. Therefore, five load/store instructions and three arithmetic instructions require 5*5+3*3 = 34 bytes. 11/10/2020 Veton Këpuska 5

- Slides: 5