Attribute predefined attribute userdefined attribute low high left

Attribute (속성) : 신호 대한 동작이나 상태 표현을 위한 특성으로 미리 정의된 속성(predefined attribute)과 사용자 정의 속성(userdefined attribute) 이 있다. 표현형식 : 신호이름’ 속성이름 종류 : low, high, left, right, pos, val, succ, pred, leftof, rightof, active, last_active, event, last_value, delayed, quit, stable, transaction… 사용 예> Event 속성: CLK’EVENT 로 표현, CLK에 EVENT가 발생하면 참값 clk’event and clk=‘ 1’ clk’event and clk=‘ 0’ -- 클럭이 상승엣지인 경우… -- 클럭이 하강엣지인 경우…

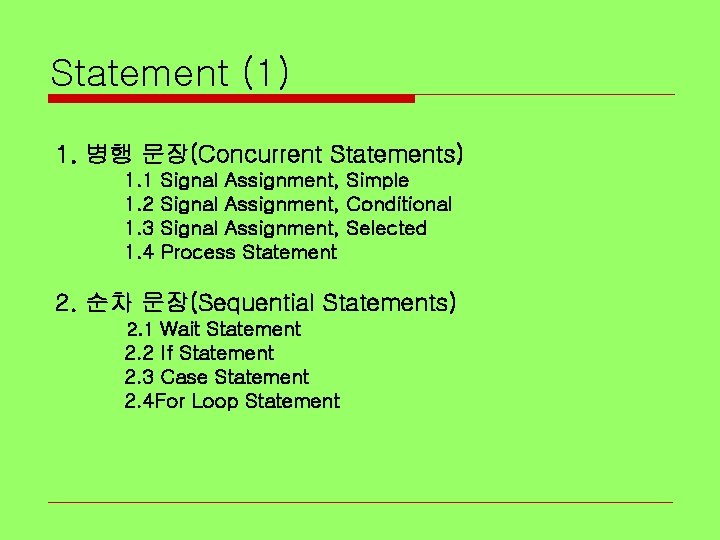

Statement (1) 1. 병행 문장(Concurrent Statements) 1. 1 1. 2 1. 3 1. 4 Signal Assignment, Simple Signal Assignment, Conditional Signal Assignment, Selected Process Statement 2. 순차 문장(Sequential Statements) 2. 1 Wait Statement 2. 2 If Statement 2. 3 Case Statement 2. 4 For Loop Statement

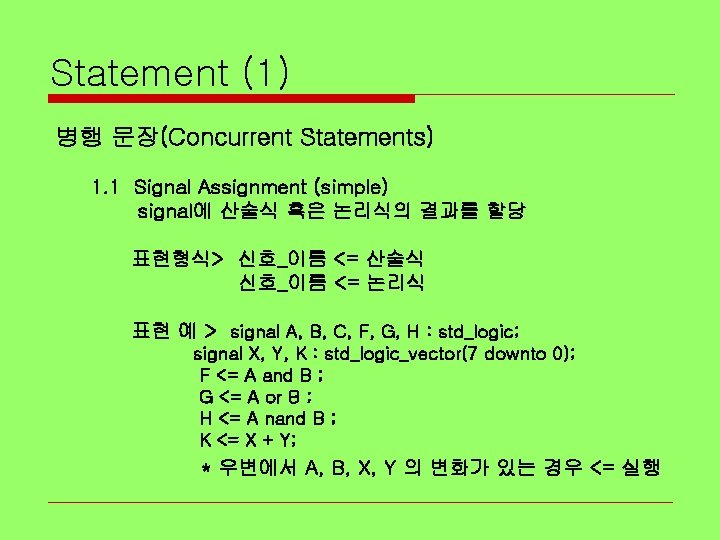

Statement (1) 병행 문장(Concurrent Statements) 1. 1 Signal Assignment (simple) signal에 산술식 혹은 논리식의 결과를 할당 표현형식> 신호_이름 <= 산술식 신호_이름 <= 논리식 표현 예 > signal A, B, C, F, G, H : std_logic; signal X, Y, K : std_logic_vector(7 downto 0); F <= A and B ; G <= A or B ; H <= A nand B ; K <= X + Y; * 우변에서 A, B, X, Y 의 변화가 있는 경우 <= 실행

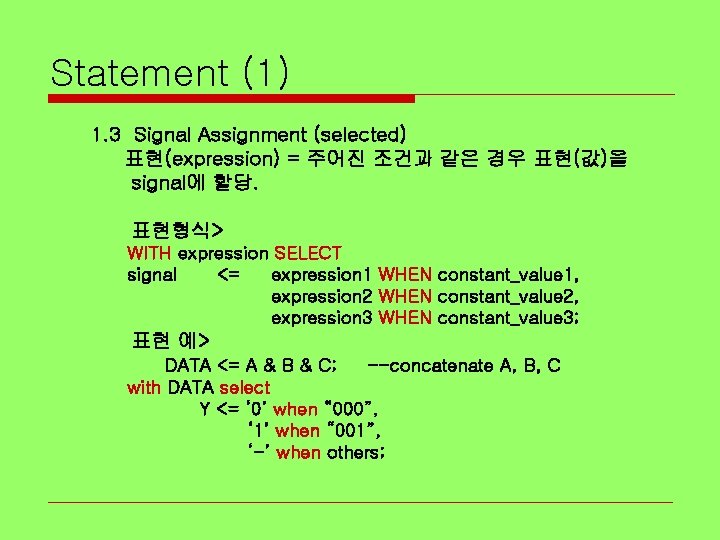

Statement (1) 1. 3 Signal Assignment (selected) 표현(expression) = 주어진 조건과 같은 경우 표현(값)을 signal에 할당. 표현형식> WITH expression SELECT signal <= expression 1 WHEN constant_value 1, expression 2 WHEN constant_value 2, expression 3 WHEN constant_value 3; 표현 예> DATA <= A & B & C; --concatenate A, B, C with DATA select Y <= ‘ 0’ when “ 000”, ‘ 1’ when “ 001”, ‘-’ when others;

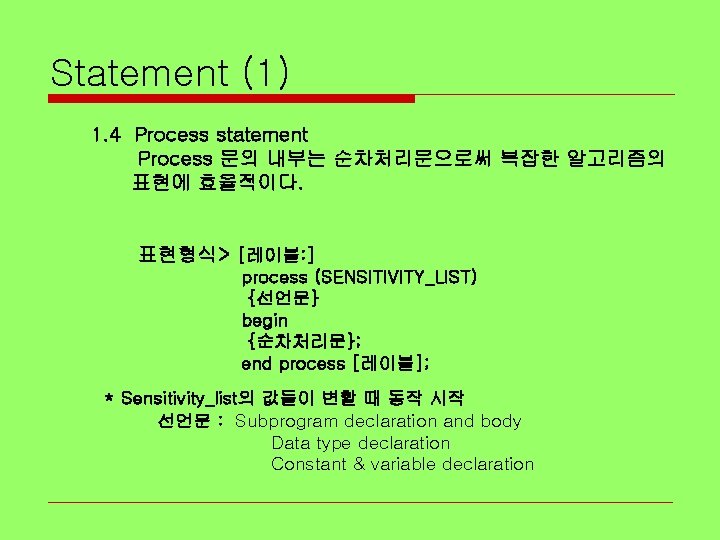

Statement (1) 1. 4 Process statement Process 문의 내부는 순차처리문으로써 복잡한 알고리즘의 표현에 효율적이다. 표현형식> [레이블: ] process (SENSITIVITY_LIST) {선언문} begin {순차처리문}; end process [레이블]; * Sensitivity_list의 값들이 변할 때 동작 시작 선언문 : Subprogram declaration and body Data type declaration Constant & variable declaration

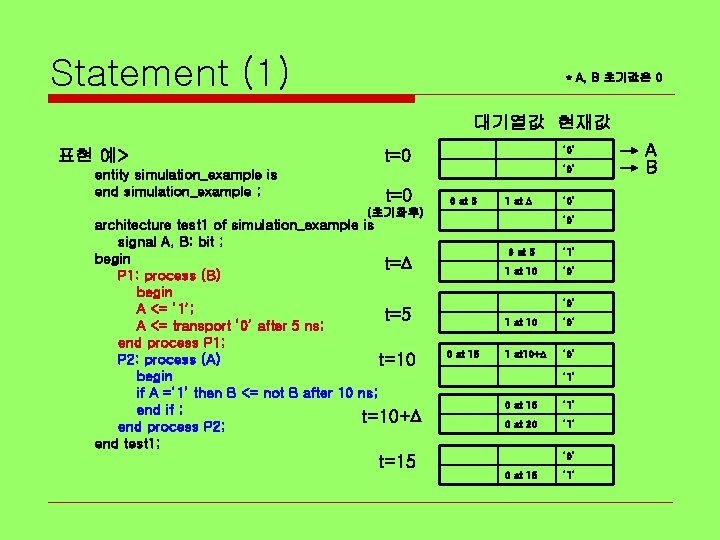

Statement (1) * A, B 초기값은 0 대기열값 현재값 표현 예> entity simulation_example is end simulation_example ; ‘ 0’ t=0 ‘ 0’ 0 at 5 1 at ∆ (초기화후) architecture test 1 of simulation_example is signal A, B: bit ; begin t=∆ P 1: process (B) begin A <= ‘ 1’; t=5 A <= transport ‘ 0’ after 5 ns; end process P 1; P 2: process (A) t=10 begin if A =‘ 1’ then B <= not B after 10 ns; end if ; t=10+∆ end process P 2; end test 1; t=15 ‘ 0’ 0 at 5 ‘ 1’ 1 at 10 ‘ 0’ 0 at 15 1 at 10 ‘ 0’ 1 at 10+∆ ‘ 0’ ‘ 1’ 0 at 15 ‘ 1’ 0 at 20 ‘ 1’ ‘ 0’ 0 at 15 ‘ 1’ A B

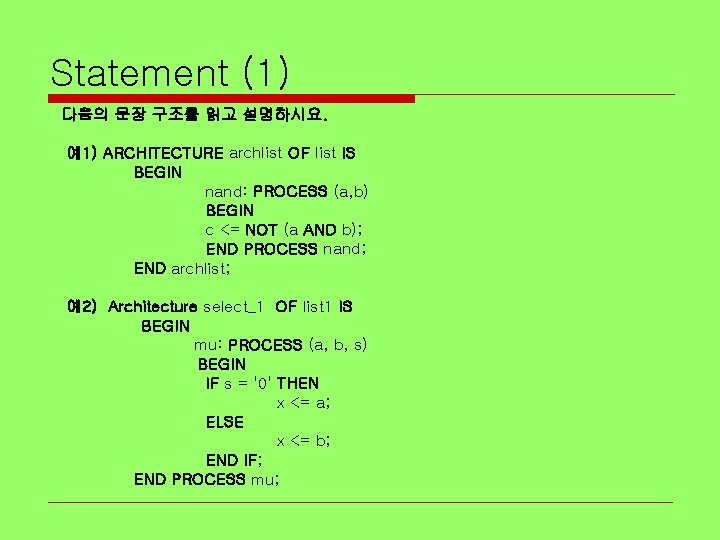

Statement (1) 다음의 문장 구조를 읽고 설명하시요. 예1) ARCHITECTURE archlist OF list IS BEGIN nand: PROCESS (a, b) BEGIN c <= NOT (a AND b); END PROCESS nand; END archlist; 예2) Architecture select_1 OF list 1 IS BEGIN mu: PROCESS (a, b, s) BEGIN IF s = '0' THEN x <= a; ELSE x <= b; END IF; END PROCESS mu;

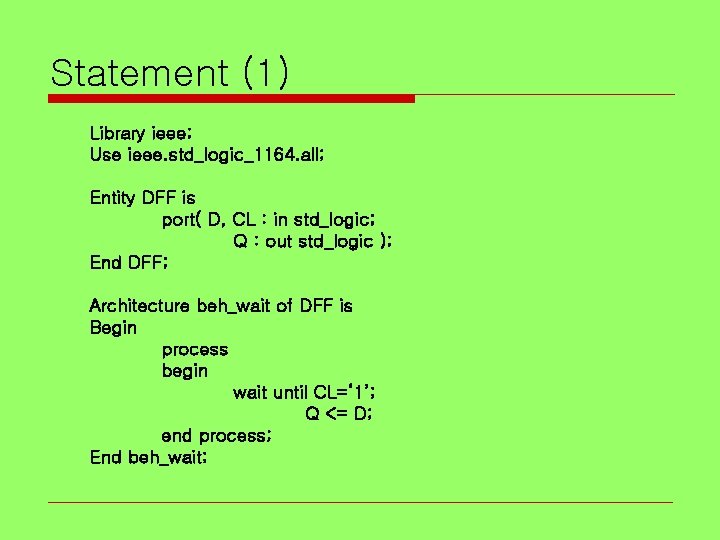

Statement (1) Library ieee; Use ieee. std_logic_1164. all; Entity DFF is port( D, CL : in std_logic; Q : out std_logic ); End DFF; Architecture beh_wait of DFF is Begin process begin wait until CL=‘ 1’; Q <= D; end process; End beh_wait;

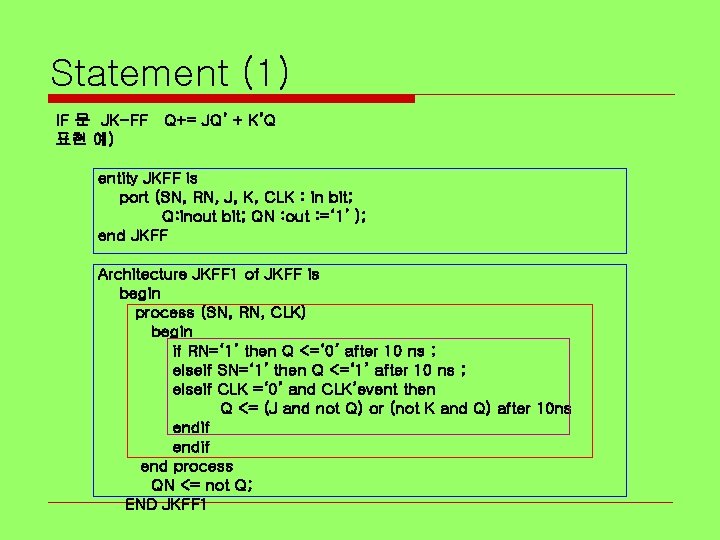

Statement (1) IF 문 JK-FF Q+= JQ’ + K’Q 표현 예) entity JKFF is port (SN, RN, J, K, CLK : in bit; Q: inout bit; QN : out : =‘ 1’ ); end JKFF Architecture JKFF 1 of JKFF is begin process (SN, RN, CLK) begin if RN=‘ 1’ then Q <=‘ 0’ after 10 ns ; elseif SN=‘ 1’ then Q <=‘ 1’ after 10 ns ; elseif CLK =‘ 0’ and CLK’event then Q <= (J and not Q) or (not K and Q) after 10 ns endif end process QN <= not Q; END JKFF 1

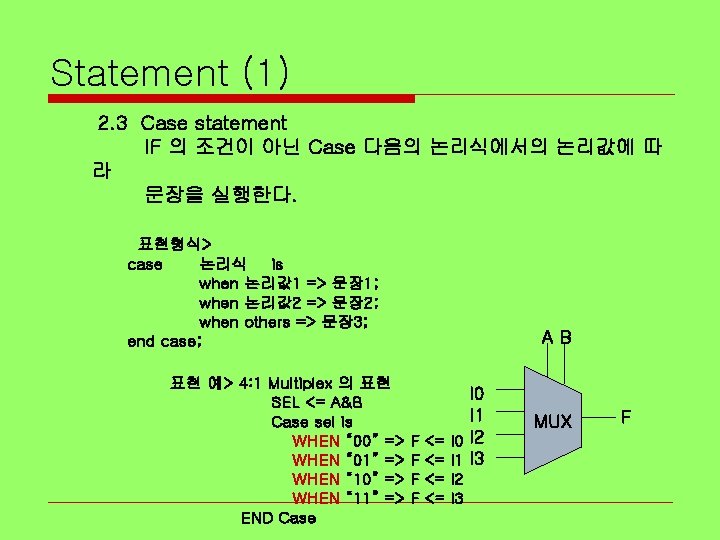

Statement (1) 2. 3 Case statement IF 의 조건이 아닌 Case 다음의 논리식에서의 논리값에 따 라 문장을 실행한다. 표현형식> case 논리식 is when 논리값 1 => 문장 1; when 논리값 2 => 문장 2; when others => 문장 3; end case; 표현 예> 4: 1 Multiplex 의 표현 SEL <= A&B Case sel is WHEN “ 00” => WHEN “ 01” => WHEN “ 10” => WHEN “ 11” => END Case AB I 0 I 1 F <= I 0 I 2 F <= I 1 I 3 F <= I 2 F <= I 3 MUX F

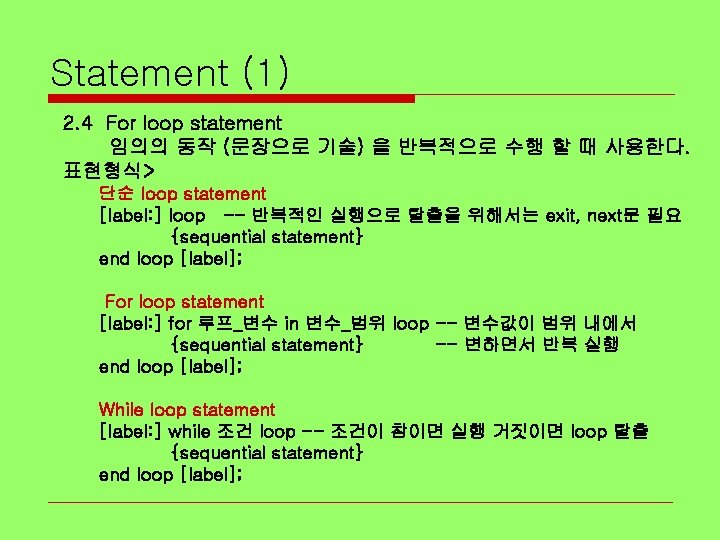

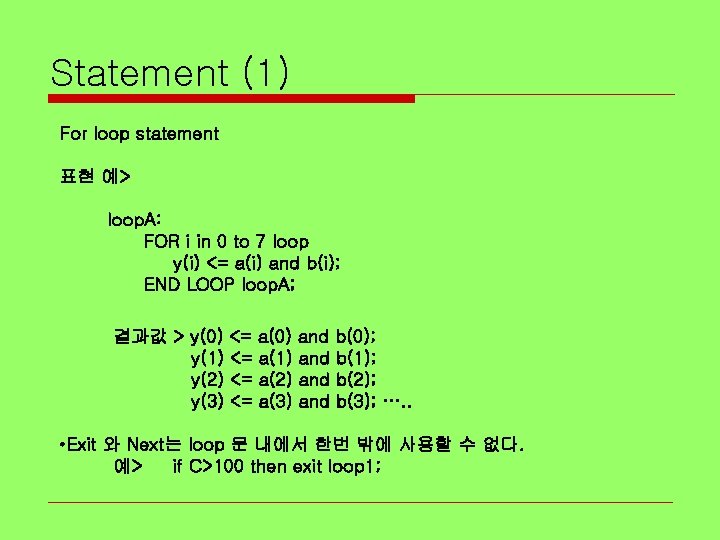

Statement (1) 2. 4 For loop statement 임의의 동작 (문장으로 기술) 을 반복적으로 수행 할 때 사용한다. 표현형식> 단순 loop statement [label: ] loop -- 반복적인 실행으로 탈출을 위해서는 exit, next문 필요 {sequential statement} end loop [label]; For loop statement [label: ] for 루프_변수 in 변수_범위 loop -- 변수값이 범위 내에서 {sequential statement} -- 변하면서 반복 실행 end loop [label]; While loop statement [label: ] while 조건 loop -- 조건이 참이면 실행 거짓이면 loop 탈출 {sequential statement} end loop [label];

Statement (1) For loop statement 표현 예> loop. A: FOR i in 0 to 7 loop y(i) <= a(i) and b(i); END LOOP loop. A; 결과값 > y(0) <= a(0) and b(0); y(1) <= a(1) and b(1); y(2) <= a(2) and b(2); y(3) <= a(3) and b(3); …. . • Exit 와 Next는 loop 문 내에서 한번 밖에 사용할 수 없다. 예> if C>100 then exit loop 1;

- Slides: 17