Zasada dziaania komputera Architektura systemu komputerowego O tym

- Slides: 15

Zasada działania komputera

Architektura systemu komputerowego O tym w jaki sposób komputer wykonuje program i uzyskuje dostęp do pamięci i danych, decyduje architektura systemu komputerowego. Określa ona sposób połączenia między jego trzema podstawowymi składnikami: -Procesorem -Pamięcią -Urządzeniami wejścia – wyjścia Ze względu na sposób organizacji pamięci oraz wykonywania programu wyróżnia się komputery o: -Architekturze von Neumanna -Architekturze harwardzkiej -Architekturze mieszanej

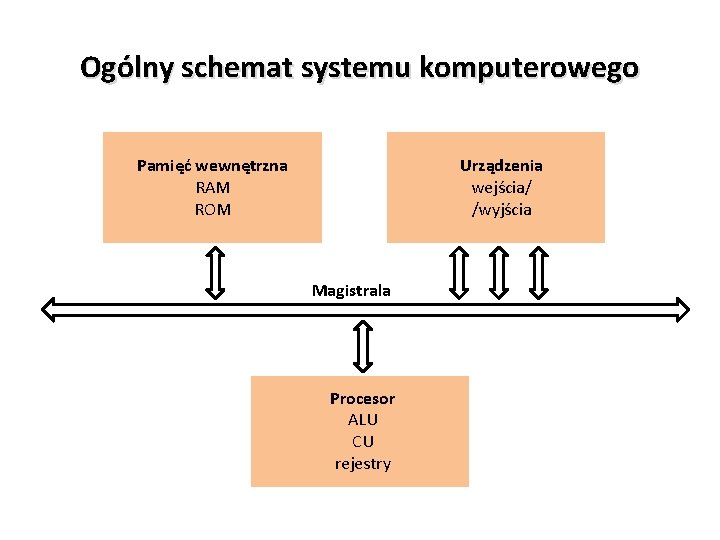

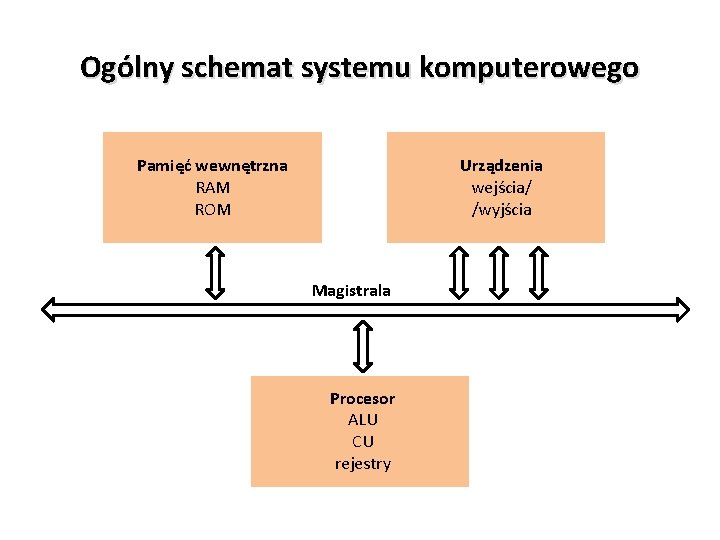

Ogólny schemat systemu komputerowego Pamięć wewnętrzna RAM ROM Urządzenia wejścia/ /wyjścia Magistrala Procesor ALU CU rejestry

Ogólny schemat systemu komputerowego Procesor Jest głównym elementem komputera, który odpowiada za przetwarzanie danych. W jego skład wchodzą następujące elementy: • jednostka arytmetyczno-logiczna ALU (Aritmetic Logical Unit) • jednostka sterująca CU (Central Unit) • zespół rejestrów Jednostka sterująca pobiera dane z pamięci i dostarcza do ALU. W ALU realizowane są operacje na liczbach dwójkowych. W rejestrach przechowywane są adresy wybranych miejsc w pamięci oraz dane i wyniki obliczeń.

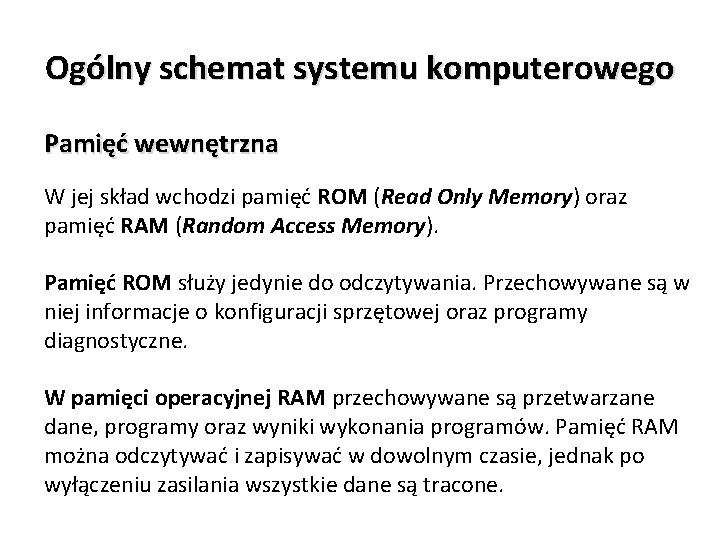

Ogólny schemat systemu komputerowego Pamięć wewnętrzna W jej skład wchodzi pamięć ROM (Read Only Memory) oraz pamięć RAM (Random Access Memory). Pamięć ROM służy jedynie do odczytywania. Przechowywane są w niej informacje o konfiguracji sprzętowej oraz programy diagnostyczne. W pamięci operacyjnej RAM przechowywane są przetwarzane dane, programy oraz wyniki wykonania programów. Pamięć RAM można odczytywać i zapisywać w dowolnym czasie, jednak po wyłączeniu zasilania wszystkie dane są tracone.

Ogólny schemat systemu komputerowego Magistrala Zespół linii służących do przesyłania danych, adresów i sygnałów między procesorem, pamięcią i urządzeniami wejścia-wyjścia. Szybkość pracy magistrali zależy od jej typu oraz zastosowania. Rodzaje magistral systemowych: Magistrala FSB, Magistrala DMI, Magistrala QPI, Magistrala Hyper Transport.

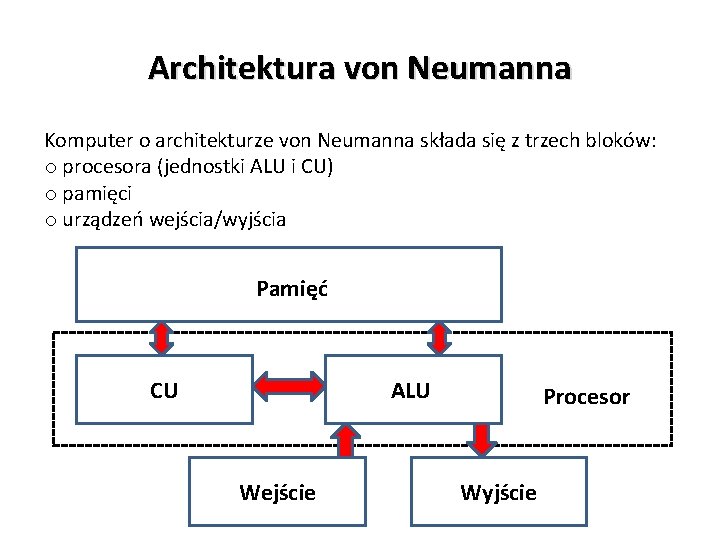

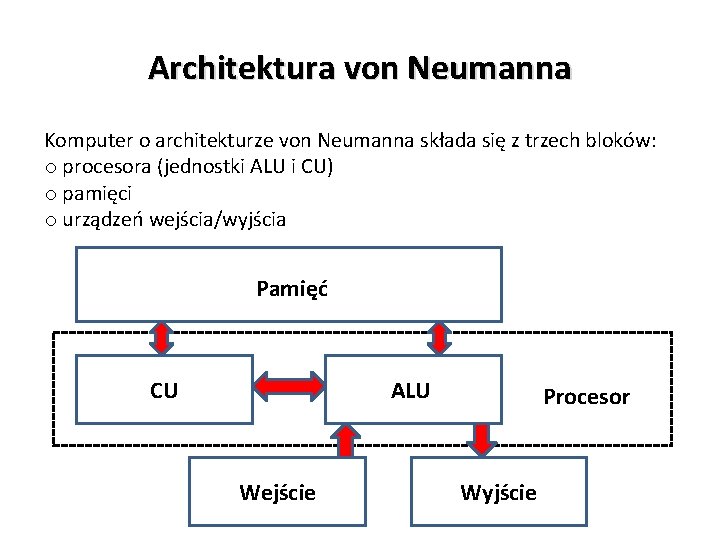

Architektura von Neumanna Komputer o architekturze von Neumanna składa się z trzech bloków: o procesora (jednostki ALU i CU) o pamięci o urządzeń wejścia/wyjścia Pamięć CU ALU Wejście Procesor Wyjście

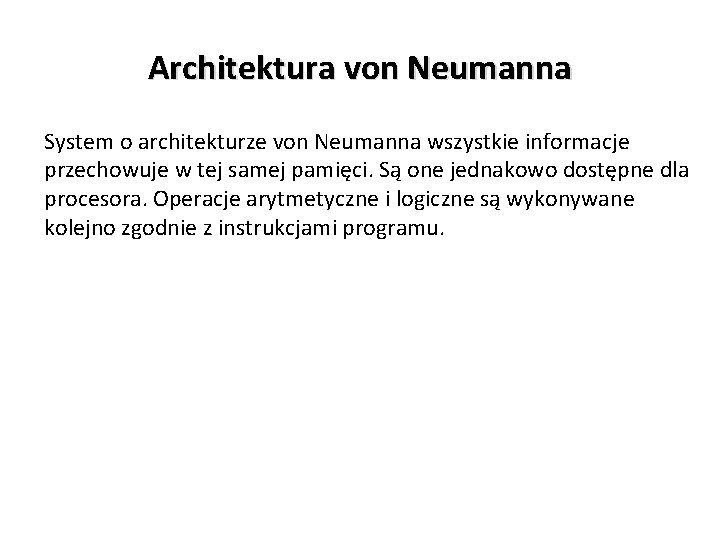

Architektura von Neumanna System o architekturze von Neumanna wszystkie informacje przechowuje w tej samej pamięci. Są one jednakowo dostępne dla procesora. Operacje arytmetyczne i logiczne są wykonywane kolejno zgodnie z instrukcjami programu.

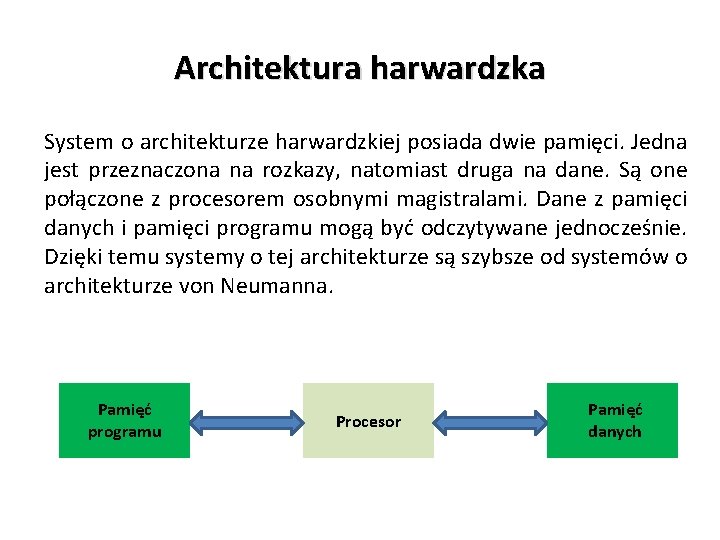

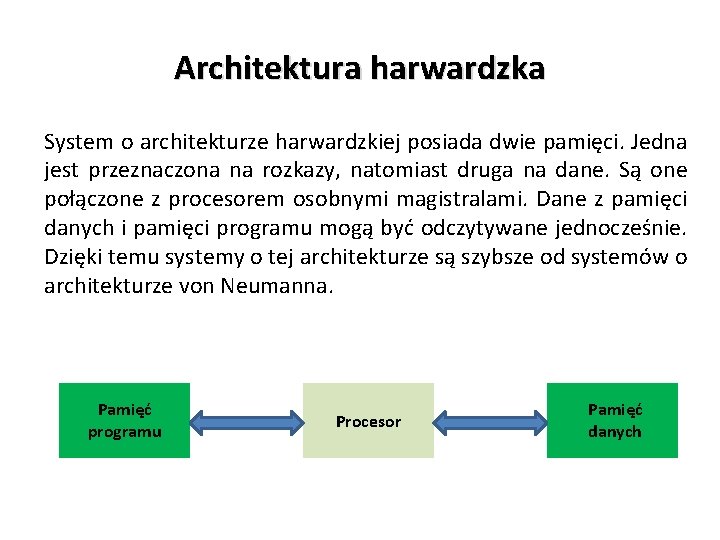

Architektura harwardzka System o architekturze harwardzkiej posiada dwie pamięci. Jedna jest przeznaczona na rozkazy, natomiast druga na dane. Są one połączone z procesorem osobnymi magistralami. Dane z pamięci danych i pamięci programu mogą być odczytywane jednocześnie. Dzięki temu systemy o tej architekturze są szybsze od systemów o architekturze von Neumanna. Pamięć programu Procesor Pamięć danych

Architektura mieszana Łączy w sobie cechy architektury von Neumanna z architekturą harwardzką. Często jest nazwana zmodyfikowaną architekturą harwardzką. W tej architekturze pamięci danych i rozkazów są rozdzielone, ale wykorzystują one wspólną magistralę danych i adresową.

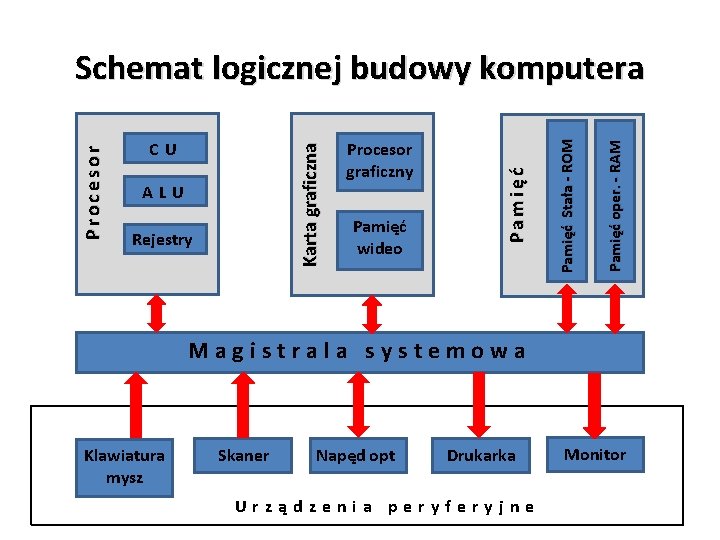

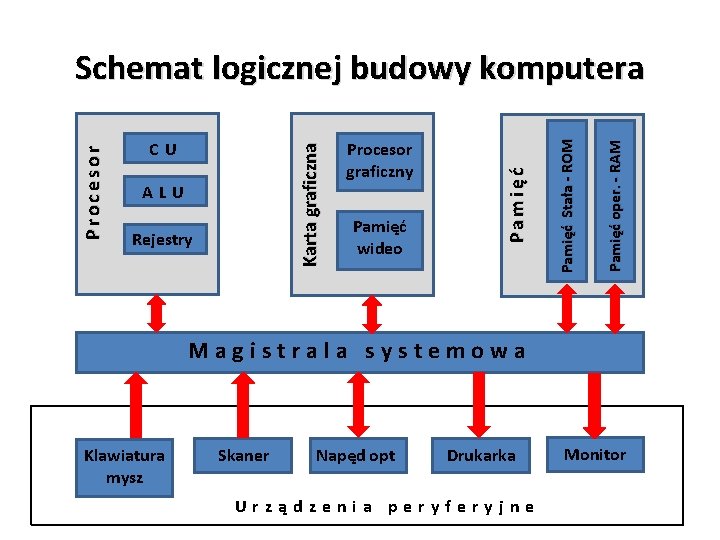

Pamięć wideo Pamięć oper. - RAM Rejestry Pamięć Stała - ROM ALU Procesor graficzny Pamięć CU Karta graficzna Procesor Schemat logicznej budowy komputera Magistrala systemowa Klawiatura mysz Skaner Napęd opt Drukarka Urządzenia peryferyjne Monitor

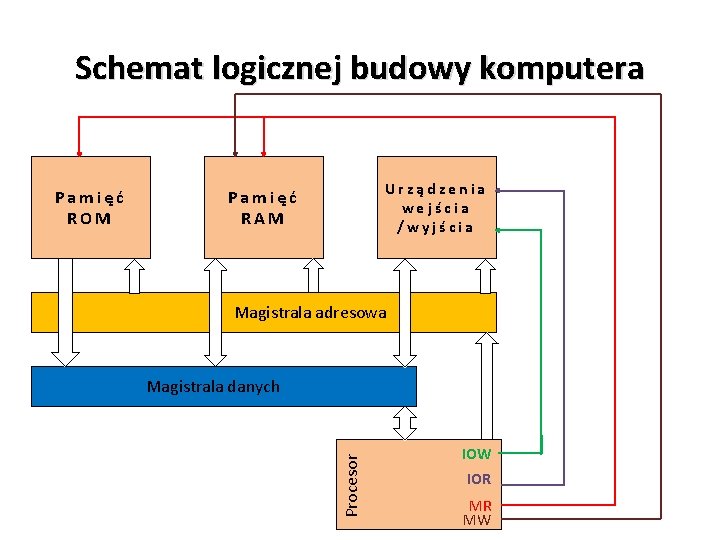

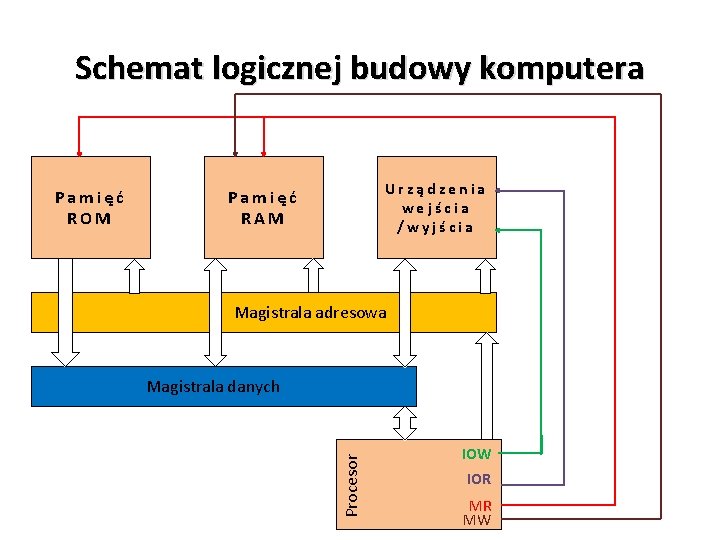

Schemat logicznej budowy komputera Komputer składa się z procesora, pamięci wewnętrznej oraz zewnętrznych urządzeń wejścia – wyjścia (urządzenia peryferyjne). Elementy te łączą się ze sobą za pomocą magistrali systemowej. Współpraca procesora z pamięcią oraz urządzeniami wejścia – wyjścia odbywa się poprzez szynę danych i szynę adresową. Procesor wysyła sygnały sterujące, które umożliwiają odczyt lub zapis z poszczególnych urządzeń. Można wyróżnić następujące sygnały sterujące: MR (Memory Read), MW (Memory Write), IOR (Input/Output Read), IOW (Input/Output Write).

Schemat logicznej budowy komputera Urządzenia wejścia /wyjścia Pamięć RAM Magistrala adresowa Magistrala danych Procesor Pamięć ROM IOW IOR MR MW

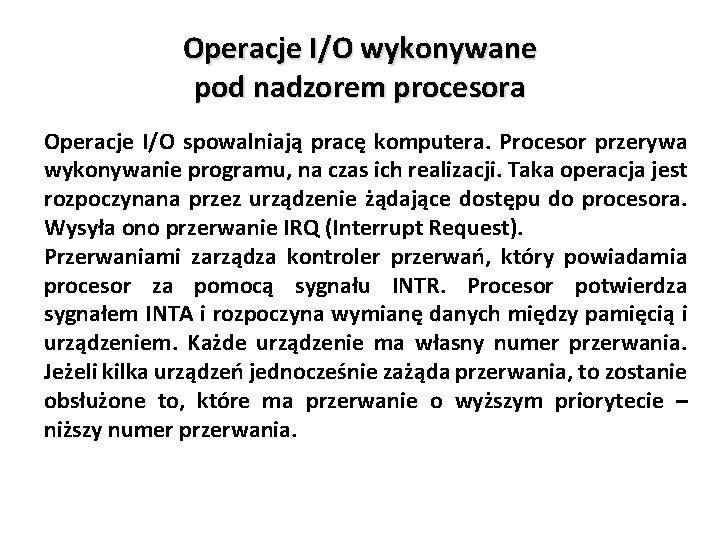

Operacje I/O wykonywane pod nadzorem procesora Operacje I/O spowalniają pracę komputera. Procesor przerywa wykonywanie programu, na czas ich realizacji. Taka operacja jest rozpoczynana przez urządzenie żądające dostępu do procesora. Wysyła ono przerwanie IRQ (Interrupt Request). Przerwaniami zarządza kontroler przerwań, który powiadamia procesor za pomocą sygnału INTR. Procesor potwierdza sygnałem INTA i rozpoczyna wymianę danych między pamięcią i urządzeniem. Każde urządzenie ma własny numer przerwania. Jeżeli kilka urządzeń jednocześnie zażąda przerwania, to zostanie obsłużone to, które ma przerwanie o wyższym priorytecie – niższy numer przerwania.

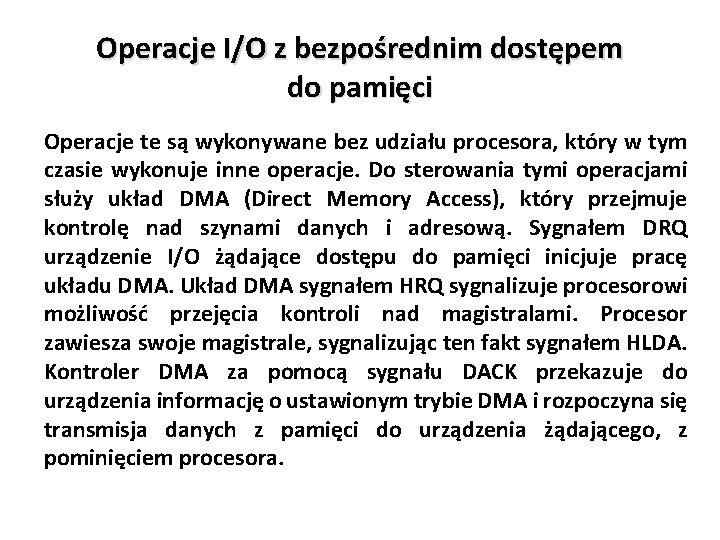

Operacje I/O z bezpośrednim dostępem do pamięci Operacje te są wykonywane bez udziału procesora, który w tym czasie wykonuje inne operacje. Do sterowania tymi operacjami służy układ DMA (Direct Memory Access), który przejmuje kontrolę nad szynami danych i adresową. Sygnałem DRQ urządzenie I/O żądające dostępu do pamięci inicjuje pracę układu DMA. Układ DMA sygnałem HRQ sygnalizuje procesorowi możliwość przejęcia kontroli nad magistralami. Procesor zawiesza swoje magistrale, sygnalizując ten fakt sygnałem HLDA. Kontroler DMA za pomocą sygnału DACK przekazuje do urządzenia informację o ustawionym trybie DMA i rozpoczyna się transmisja danych z pamięci do urządzenia żądającego, z pominięciem procesora.