Xilinx V 4 Single Event Effects SEE HighSpeed

- Slides: 8

Xilinx V 4 Single Event Effects (SEE) High-Speed Testing Melanie D. Berg/MEI – Principal Investigator mdberg@pop 500. gsfc. nasa. gov Hak Kim, Mark Friendlich/MEI Ray Ladbury, Ken La. Bel/NASA Steve Buchner/QSS This work was sponsored by the NASA Electronic Parts and Packaging (NEPP) Program

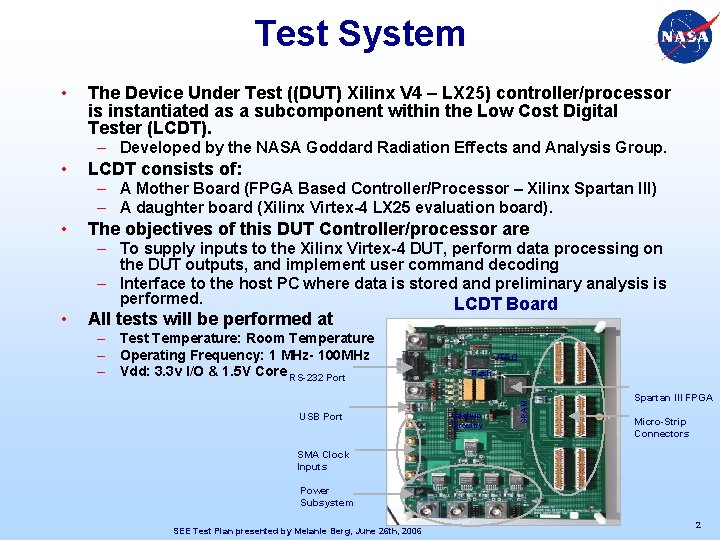

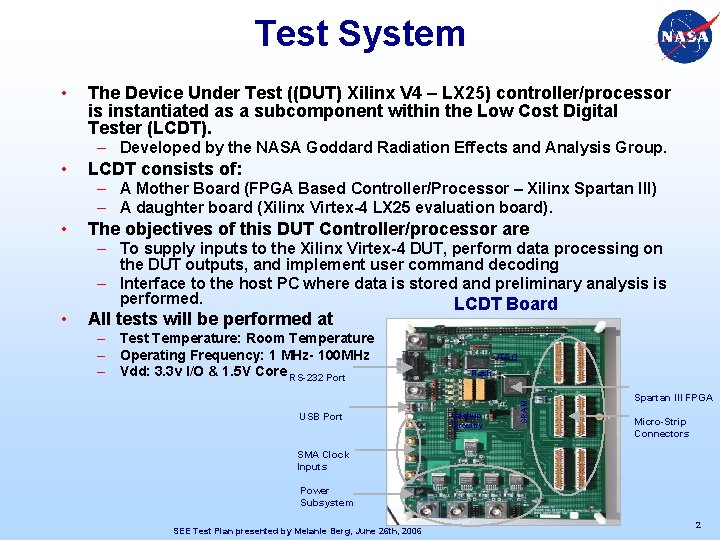

Test System • The Device Under Test ((DUT) Xilinx V 4 – LX 25) controller/processor is instantiated as a subcomponent within the Low Cost Digital Tester (LCDT). – Developed by the NASA Goddard Radiation Effects and Analysis Group. • LCDT consists of: – A Mother Board (FPGA Based Controller/Processor – Xilinx Spartan III) – A daughter board (Xilinx Virtex-4 LX 25 evaluation board). • The objectives of this DUT Controller/processor are – To supply inputs to the Xilinx Virtex-4 DUT, perform data processing on the DUT outputs, and implement user command decoding – Interface to the host PC where data is stored and preliminary analysis is performed. LCDT Board All tests will be performed at – Test Temperature: Room Temperature – Operating Frequency: 1 MHz- 100 MHz – Vdd: 3. 3 v I/O & 1. 5 V Core RS-232 Port USB Port JTAG Flash Latchup Circuitry SRAM • Spartan III FPGA Micro-Strip Connectors SMA Clock Inputs Power Subsystem SEE Test Plan presented by Melanie Berg, June 26 th, 2006 2

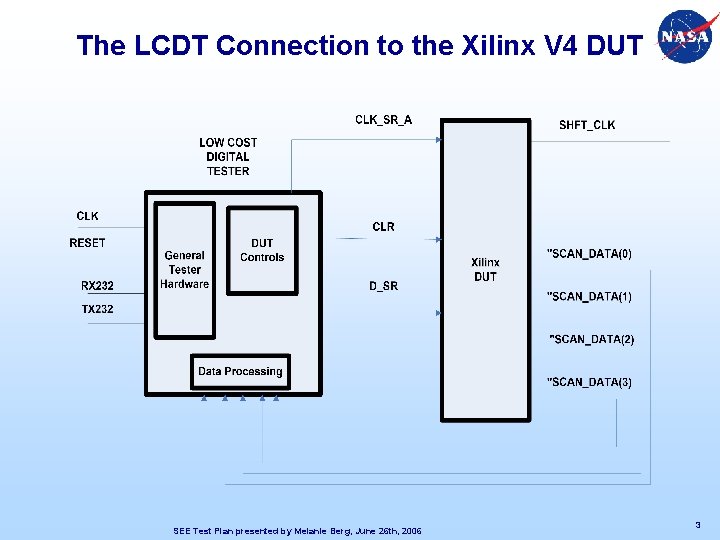

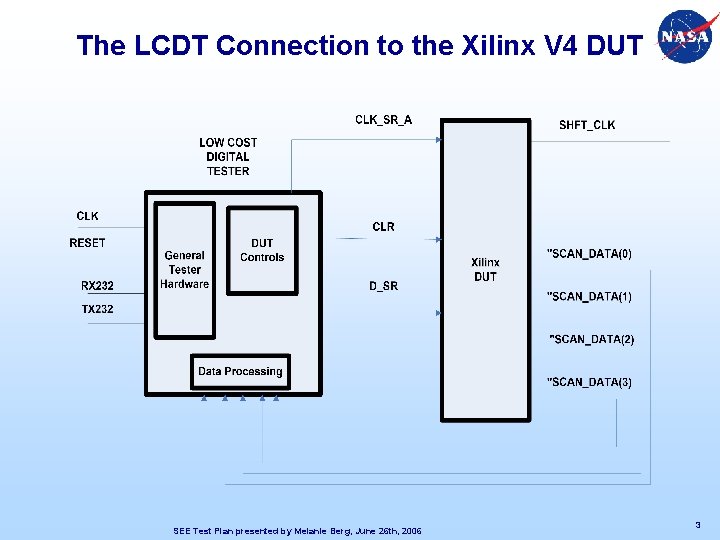

The LCDT Connection to the Xilinx V 4 DUT SEE Test Plan presented by Melanie Berg, June 26 th, 2006 3

Test Facility – Heavy Ion • Facility: – Texas A&M University (TAMU) Cyclotron Single Event Effects Test Facility, 40 Me. V/amu tune). • Flux: – 1. 0 x 104 to 2. 0 x 105 particles/cm 2/s • Fluence: – All tests will be run to 1 x 107 p/cm 2 or until destructive or functional events occurred. • Linear Energy Transfers (LET) : – 1. 2 to approximately 21 Me. V*cm 2/mg • Initial Test Date: June 28 th 2006 SEE Test Plan presented by Melanie Berg, June 26 th, 2006 4

Device Under Test Specifics • 8 bit Select Map Configuration and Scrubbing is implemented and controlled by the LCDT • Currently readback functionality is not completed – will be added to the testbed by the end of August • Edge Triggered Flip Flop (DFF) Shift Registers are implemented as the DUT functionality – Variable number of combinatorial logic between DFFs (Single Event Transient Analysis – SET) – Data capture and output are fully synchronous SEE Test Plan presented by Melanie Berg, June 26 th, 2006 5

Initial Test Plan • Single Event Latch-up monitoring • Scrubbing will be active simultaneously with the shift register logic • The following are controlled by user commands sent to the LCDT – Variable scrubbing frequencies (6 MHz to 50 MHz) continuous vs. sporadic (i. e. once every n ms) – Shift Register Architecture will be tested with and without different levels of Triple Mode Redundancy (TMR) – Data Pattern variation (static 1, static 0, and alternating) – Frequency variation (1 MHz to 100 MHz) – currently limited by interface from Mother to Evaluation Daughter board SEE Test Plan presented by Melanie Berg, June 26 th, 2006 6

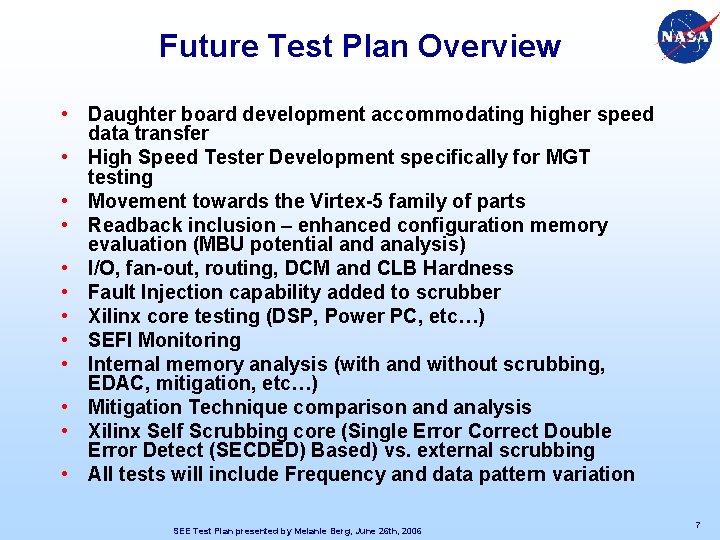

Future Test Plan Overview • Daughter board development accommodating higher speed data transfer • High Speed Tester Development specifically for MGT testing • Movement towards the Virtex-5 family of parts • Readback inclusion – enhanced configuration memory evaluation (MBU potential and analysis) • I/O, fan-out, routing, DCM and CLB Hardness • Fault Injection capability added to scrubber • Xilinx core testing (DSP, Power PC, etc…) • SEFI Monitoring • Internal memory analysis (with and without scrubbing, EDAC, mitigation, etc…) • Mitigation Technique comparison and analysis • Xilinx Self Scrubbing core (Single Error Correct Double Error Detect (SECDED) Based) vs. external scrubbing • All tests will include Frequency and data pattern variation SEE Test Plan presented by Melanie Berg, June 26 th, 2006 7

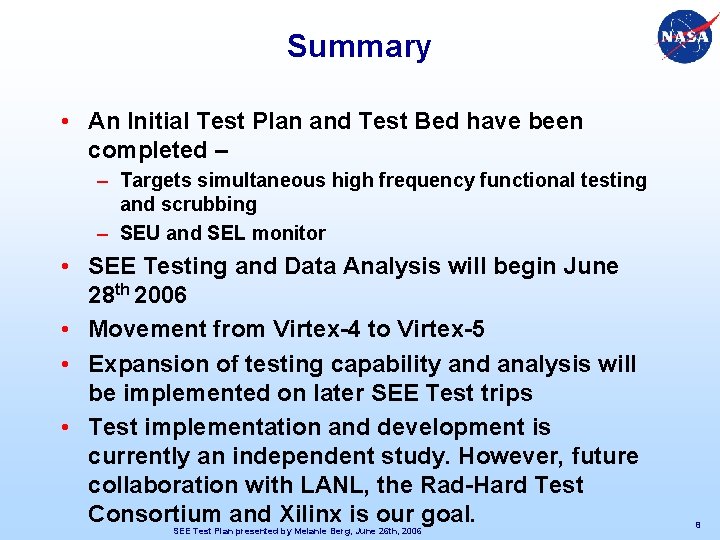

Summary • An Initial Test Plan and Test Bed have been completed – – Targets simultaneous high frequency functional testing and scrubbing – SEU and SEL monitor • SEE Testing and Data Analysis will begin June 28 th 2006 • Movement from Virtex-4 to Virtex-5 • Expansion of testing capability and analysis will be implemented on later SEE Test trips • Test implementation and development is currently an independent study. However, future collaboration with LANL, the Rad-Hard Test Consortium and Xilinx is our goal. SEE Test Plan presented by Melanie Berg, June 26 th, 2006 8