Xilinx Programmable Logic Development Systems Alliance Series version

Xilinx Programmable Logic Development Systems Alliance Series version 3

Award Winning Design Solutions w The industry’s fastest runtimes — 2 to 10 X faster than the competition w The industry’s highest performance — 15 to 25 % faster clock rates than the competition w The industry’s leading devices — V 2600 E and V 3200 E, V 405 EM and V 812 EM, 2 S 200, Virtex-II w The industry’s most powerful design flows — Fast and efficient design methodologies for up to 10 Million gates w The industry’s most productive partnerships — Partners with Over 30 of the industry’s most successful companies ® www. xilinx. com

The Industry’s Fastest Runtimes Deliver the Fastest Time To Market Runtime w Ultra fast place and route runtimes — XCV 100: 3 -5 minutes (100, 000 system gates) — XCV 1000: 30 -45 minutes (1 M system gates!) — Real PCI design 64/66 in XCV 300: ~ 5 minutes – Consumes ~ 12% of XCV 300 BG 432 w Even faster than our previous release — From 10% to 100% for < 1 M gates — From 2 X to 10 X for > 1 M gates ® www. xilinx. com

The Industry’s Best Performance Accelerating Time To Market Performance w Clock speeds >160 MHz when targeting Virtex-E w I/O performance >622 Mbps when targeting Virtex-E w For existing designs, performance will increase by 10% to 15% from place and route algorithm improvements — Approximately a speed grade — For Virtex, Virtex-E, Spartan-II devices only ® www. xilinx. com

The Industry’s Leading Devices Device Technology w Extending the lead with Virtex-E — V 2600 E and V 3200 E w Unequalled memory and logic with the Extended Memory (EM) family — V 405 EM and V 812 EM w Awesome value for high-volume applications — The new Spartan-II family 2 S 200 device w Reinventing the FPGA, again with Virtex-II ® www. xilinx. com

The Industry’s Most Powerful Design Flows w Incremental synthesis / layout with high-level floorplanning w Efficient methodology for teams using modular design w Advanced debug capabilities using Chip. Scope ILA w Powerful HDL source archive; efficiently manages all design files ® www. xilinx. com

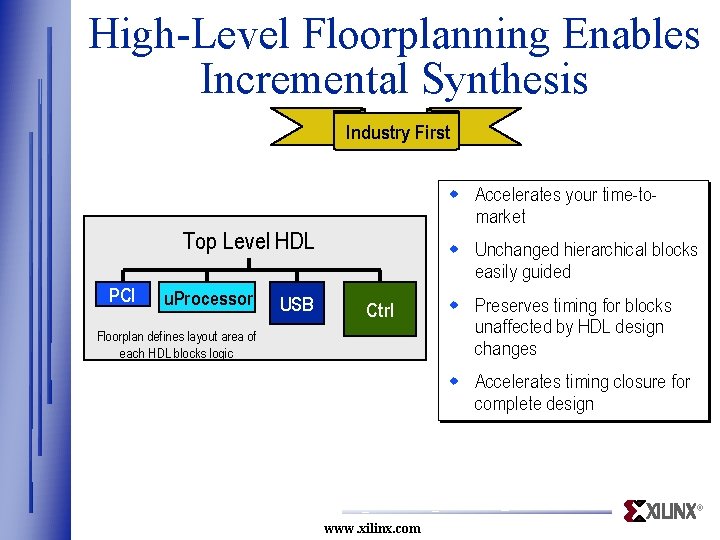

High-Level Floorplanning Enables Incremental Synthesis Industry First w Accelerates your time-tomarket Top Level HDL PCI u. Processor USB w Unchanged hierarchical blocks easily guided Ctrl Floorplan defines layout area of each HDL blocks logic w Preserves timing for blocks unaffected by HDL design changes w Accelerates timing closure for complete design ® www. xilinx. com

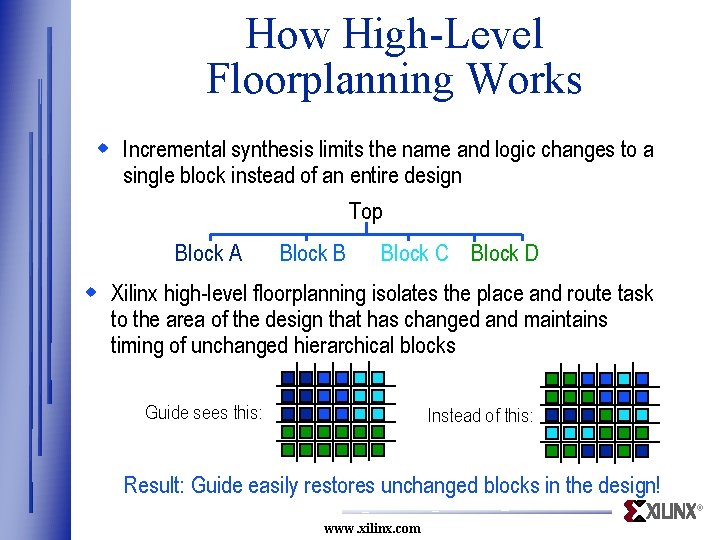

How High-Level Floorplanning Works w Incremental synthesis limits the name and logic changes to a single block instead of an entire design Top Block A Block B Block C Block D w Xilinx high-level floorplanning isolates the place and route task to the area of the design that has changed and maintains timing of unchanged hierarchical blocks Guide sees this: Instead of this: Result: Guide easily restores unchanged blocks in the design! ® www. xilinx. com

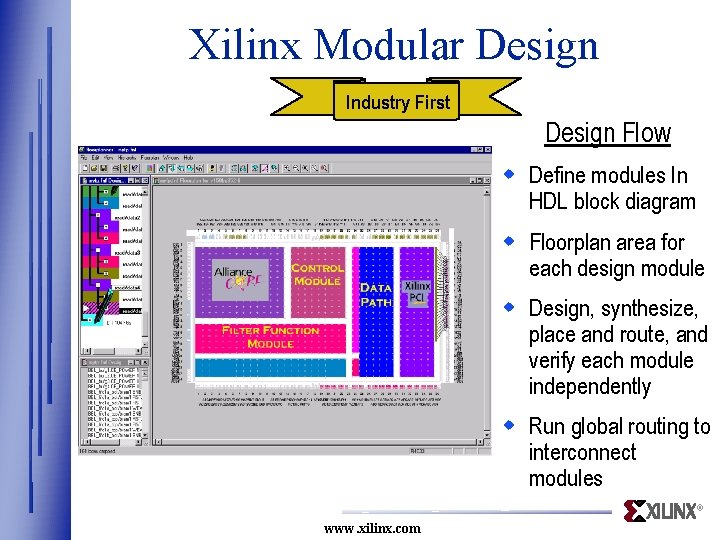

Xilinx Modular Design Industry First Design Flow w Define modules In HDL block diagram w Floorplan area for each design module w Design, synthesize, place and route, and verify each module independently w Run global routing to interconnect modules ® www. xilinx. com

Xilinx Modular Design Enabling Autonomous Team Design w Improves high-density design flows — Faster time-to-market by enabling multiple designers to work on the design of a single device — Changes task from high-density device design to high-performance module design w Improves high-density design performance — Enables more accurate / aggressive timing estimates during synthesis! — Guaranteed module timing w Enables a more robust incremental design flow — Changes in HDL are retained within a module ® www. xilinx. com

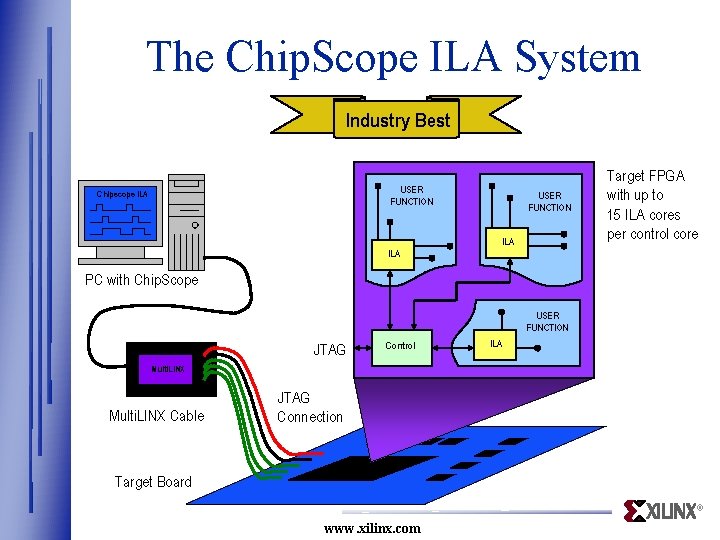

The Chip. Scope ILA System Industry Best USER FUNCTION Chipscope ILA USER FUNCTION ILA Target FPGA with up to 15 ILA cores per control core ILA PC with Chip. Scope USER FUNCTION JTAG Control ILA Multi. LINX Cable JTAG Connection Target Board ® www. xilinx. com

Advanced Debug Capabilities Using Chip. Scope ILA w Solves the debug bottleneck by — Enabling in-system analysis of any internal FPGA signal — While running at full system speed — Easing analysis of any package pins (BGA) w Chip. Scope ILA — — — Enabled by powerful capture and control ILA cores Silicon based solution enables analysis at system speeds Extensive memory enables comprehensive data capture Unique design / flow enables flexible trigger conditions ILA PROBE enables ILA modification without re-layout ® www. xilinx. com

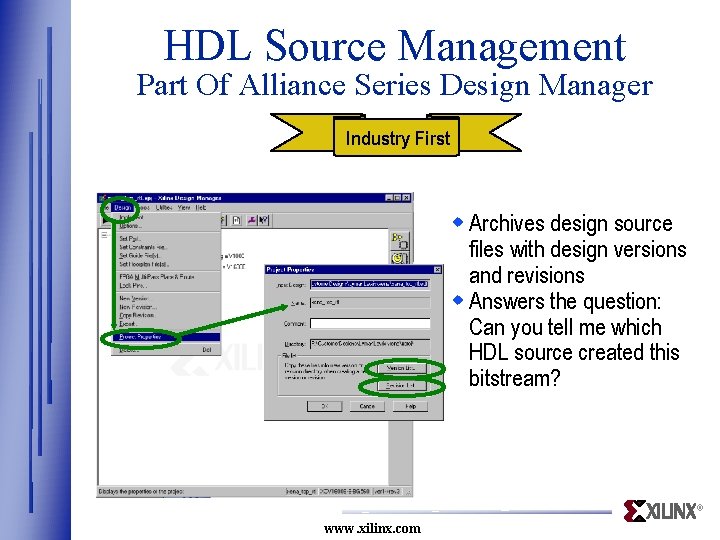

HDL Source Management Part Of Alliance Series Design Manager Industry First w Archives design source files with design versions and revisions w Answers the question: Can you tell me which HDL source created this bitstream? ® www. xilinx. com

The Industry’s Best Partnerships w Xilinx EDA Alliance program delivers the most advanced design flows / best quality of results — Incremental design with Exemplar, Synopsys, and Synplicity — Board level verification using STAMP and LMG Smart. Models w OEM with Synopsys delivers Xilinx exclusive B. L. I. S. (Block Level Incremental Synthesis) — Included in Synopsys FPGA Compiler II and FPGA Express (part of Foundation Series solutions) w OEM with MTI enabling VITAL accelerated simulation (and secure IP? ) ® www. xilinx. com

Xilinx Software Vision w Help our customers succeed with their Xilinx design — Focus on runtime, design speed, and software before silicon w Improve our customers design flows — Make Xilinx design flows easier than all others — Improve integration with third party EDA vendors — Drive EDA Alliance partner innovation “Xilinx software vision is to enhance our customers ability to take advantage of the time to market benefits of using Xilinx logic devices. ” Rich Sevcik, Sr. VP ISSG ® www. xilinx. com

Benchmark Information v 3. 1 i vs. Quartus ®

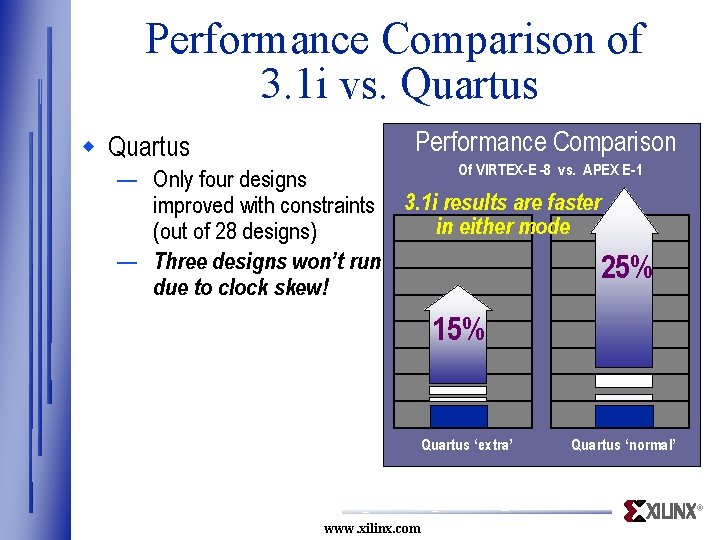

Performance Comparison of 3. 1 i vs. Quartus w Quartus Performance Comparison Of VIRTEX-E -8 vs. APEX E-1 — Only four designs improved with constraints 3. 1 i results are faster in either mode (out of 28 designs) — Three designs won’t run 25% due to clock skew! 15% Quartus ‘extra’ Quartus ‘normal’ ® www. xilinx. com

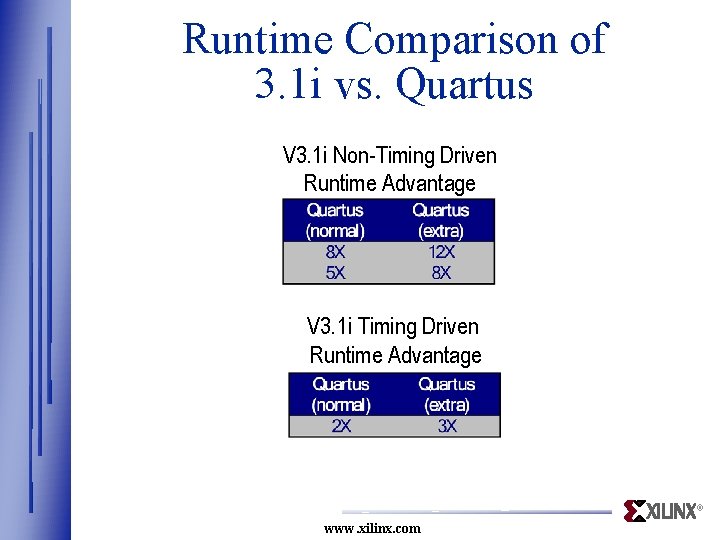

Runtime Comparison of 3. 1 i vs. Quartus V 3. 1 i Non-Timing Driven Runtime Advantage V 3. 1 i Timing Driven Runtime Advantage ® www. xilinx. com

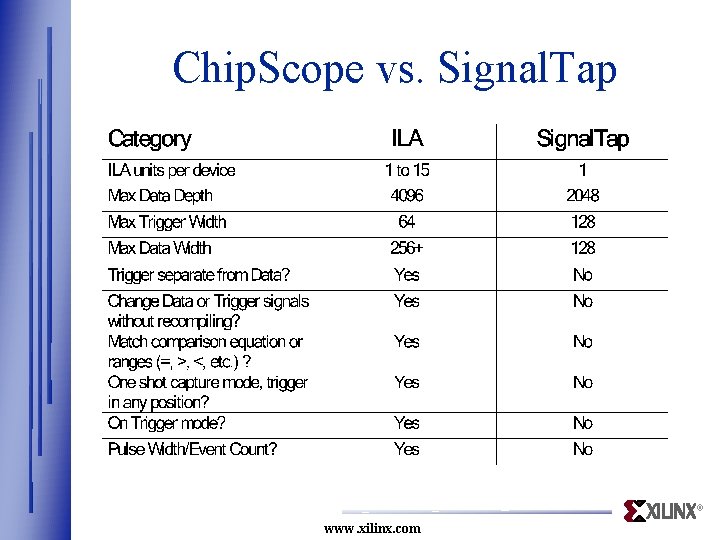

Chip. Scope vs. Signal. Tap ® www. xilinx. com

Chip. Scope ILA vs. ASIC tools w Embedded logic analysis is not efficient or easily accomplished in an ASIC — Must be fabricated onto the die during the prototype cycle w Can’t be changed once implemented — ASIC prototypes must be re-spun to remove or change logic analysis cores ® www. xilinx. com

- Slides: 20