XILINX CPLDs The Total ISP Solution Building CPLDs

XILINX CPLDs The Total ISP Solution

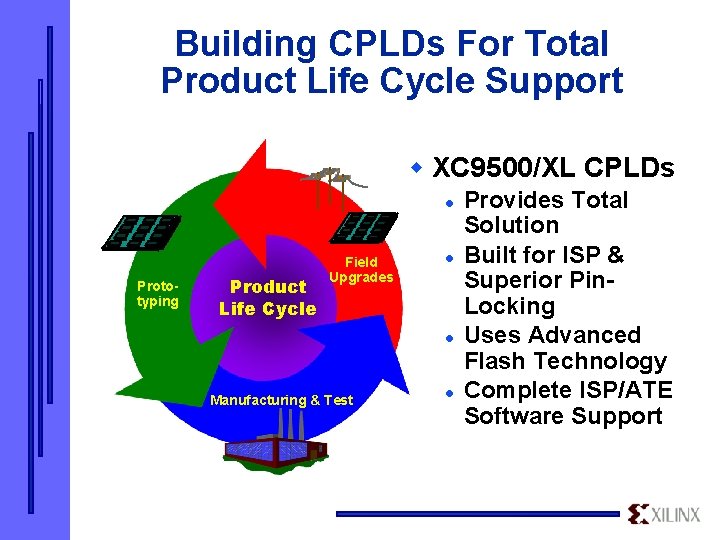

Building CPLDs For Total Product Life Cycle Support w XC 9500/XL CPLDs l Prototyping Product Life Cycle Field Upgrades l l Manufacturing & Test l Provides Total Solution Built for ISP & Superior Pin. Locking Uses Advanced Flash Technology Complete ISP/ATE Software Support

XC 9500/XL CPLDs Key Features w Flexible ISP architecture with superior pinlocking l l XC 9500: 5 v family XC 9500 XL: 3. 3 v family w High performance: 4 ns pin-to-pin (XL) w Full IEEE 1149. 1 JTAG w 5 v/3. 3 v/2. 5 v I/O compatibility w Highest reprogramming reliability w Space-efficient packaging w Low cost

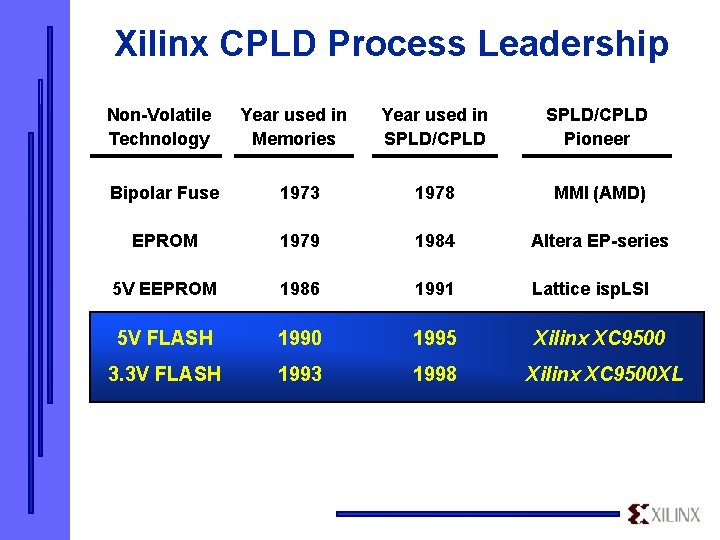

Xilinx CPLD Process Leadership Non-Volatile Technology Year used in Memories Year used in SPLD/CPLD Pioneer Bipolar Fuse 1973 1978 MMI (AMD) EPROM 1979 1984 Altera EP-series 5 V EEPROM 1986 1991 Lattice isp. LSI 5 V FLASH 1990 1995 Xilinx XC 9500 3. 3 V FLASH 1993 1998 Xilinx XC 9500 XL

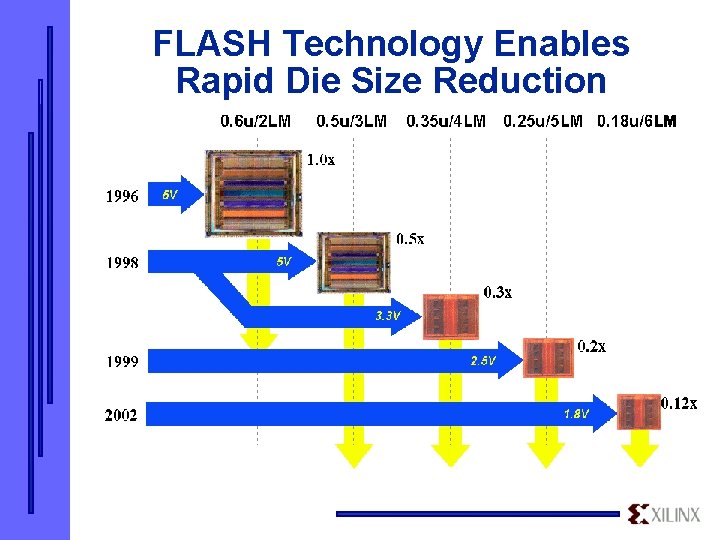

FLASH Technology Enables Rapid Die Size Reduction

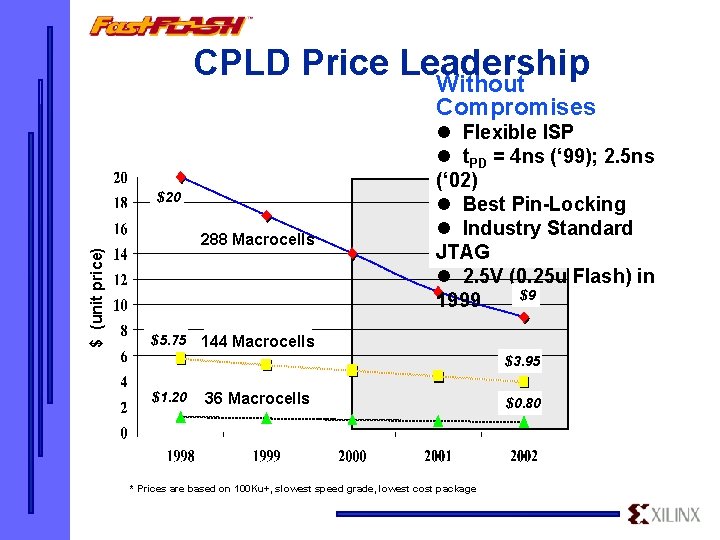

CPLD Price Leadership Without Compromises $ (unit price) $20 288 Macrocells $5. 75 l Flexible ISP l t. PD = 4 ns (‘ 99); 2. 5 ns (‘ 02) l Best Pin-Locking l Industry Standard JTAG l 2. 5 V (0. 25 u Flash) in $9 1999 144 Macrocells $3. 95 $1. 20 36 Macrocells * Prices are based on 100 Ku+, slowest speed grade, lowest cost package $0. 80

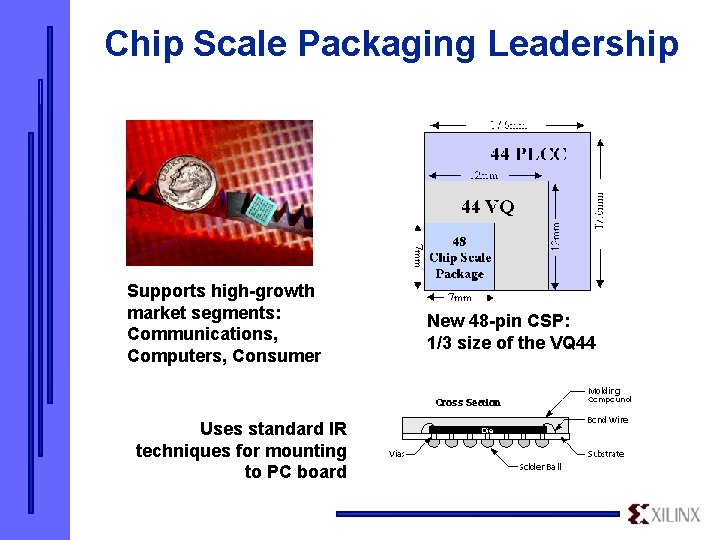

Chip Scale Packaging Leadership Supports high-growth market segments: Communications, Computers, Consumer Uses standard IR techniques for mounting to PC board New 48 -pin CSP: 1/3 size of the VQ 44

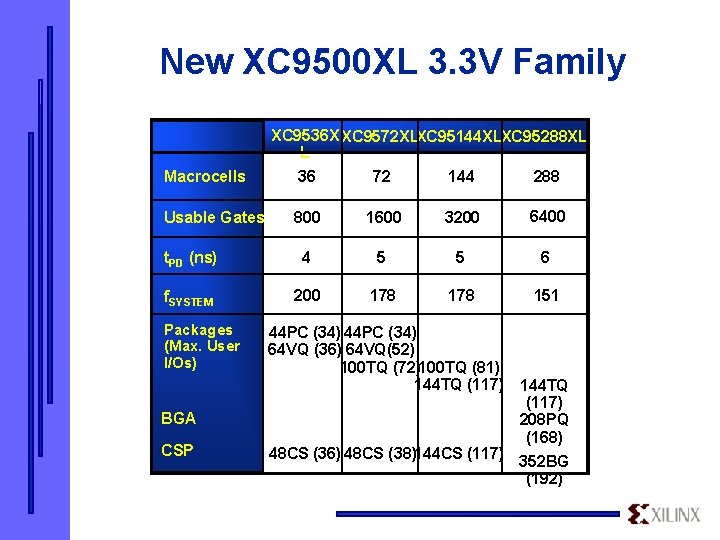

New XC 9500 XL 3. 3 V Family Macrocells XC 9536 X XC 9572 XLXC 95144 XLXC 95288 XL L 288 36 72 144 800 1600 3200 6400 t. PD (ns) 4 5 5 6 f. SYSTEM 200 178 151 Usable Gates Packages (Max. User I/Os) BGA CSP 44 PC (34) 64 VQ (36) 64 VQ(52) 100 TQ (72)100 TQ (81) 144 TQ (117) 208 PQ (168) 48 CS (36) 48 CS (38)144 CS (117) 352 BG (192)

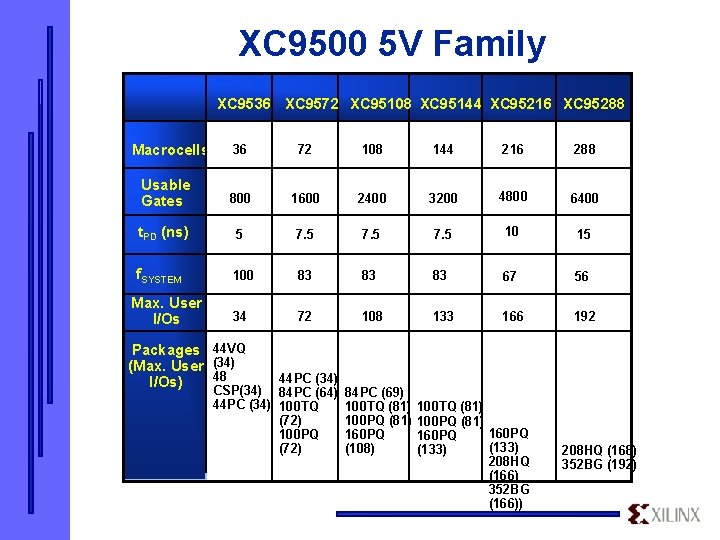

XC 9500 5 V Family XC 9536 XC 9572 XC 95108 XC 95144 XC 95216 XC 95288 Macrocells 36 72 108 144 216 288 Usable Gates 800 1600 2400 3200 4800 6400 t. PD (ns) 5 7. 5 10 15 f. SYSTEM 100 83 83 83 67 56 34 72 108 133 166 192 Max. User I/Os Packages 44 VQ (Max. User (34) 48 I/Os) 44 PC (34) CSP(34) 84 PC (64) 44 PC (34) 100 TQ (72) 100 PQ (72) 84 PC (69) 100 TQ (81) 100 PQ (81) 160 PQ (108) 100 TQ (81) 100 PQ (81) 160 PQ (133) 208 HQ (166) 352 BG (166)) 208 HQ (168) 352 BG (192)

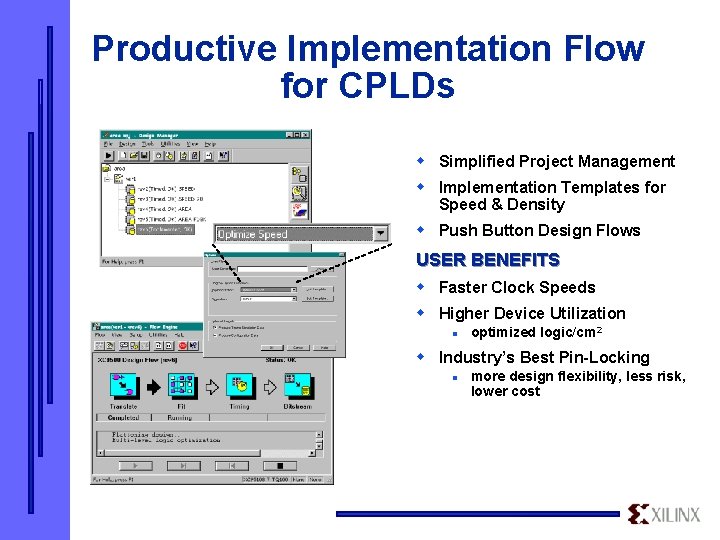

Productive Implementation Flow for CPLDs w Simplified Project Management w Implementation Templates for Speed & Density w Push Button Design Flows USER BENEFITS w Faster Clock Speeds w Higher Device Utilization l optimized logic/cm 2 w Industry’s Best Pin-Locking l more design flexibility, less risk, lower cost

What’s New In V 1. 5 CPLDs w Evolutionary Logic Algorithms for XC 9500 5 V CPLDs l higher clock frequencies, improved density & faster runtimes w Full Support of XC 9500 XL 3. 3 V CPLDs l Includes “Advance” speed grades for fastest XC 9500 XL devices w Improved Timing Driven CPLD Fitting w JTAG Programmer now supports: l XC 9500/XL CPLDs, Virtex, XC 4000 E/X/XL, XC 5200, SPARTAN/XL FPGAs w XC 9500/9500 XL support in Logi. BLOX w Alliance. CORE CPLD based IP

XILINX CPLDs The total ISP solution w Complete support of customer’s Product Life Cycle w Industry’s best pin-locking CPLD at lowest price w Multiple software solutions to choose from w Based on leadership FLASH technology

- Slides: 12