Xilinx CPLDs and FPGAs Module M 3 CPLDs

- Slides: 28

Xilinx CPLDs and FPGAs Module M 3

CPLDs and FPGAs XC 9500 CPLD XC 4000 FPGA Spartan II FPGA Virtex FPGA

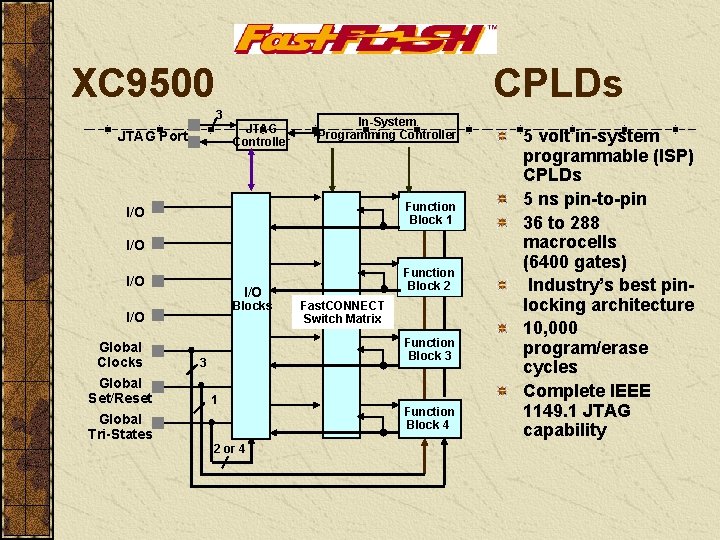

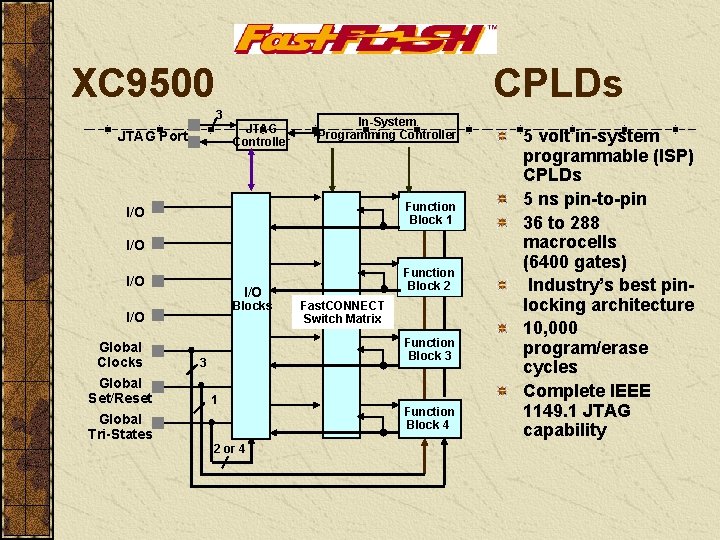

XC 9500 CPLDs 3 JTAG Controller JTAG Port In-System Programming Controller Function Block 1 I/O I/O Blocks I/O Global Clocks Global Set/Reset Global Tri-States Function Block 2 Fast. CONNECT Switch Matrix Function Block 3 3 1 2 or 4 Function Block 4 5 volt in-system programmable (ISP) CPLDs 5 ns pin-to-pin 36 to 288 macrocells (6400 gates) Industry’s best pinlocking architecture 10, 000 program/erase cycles Complete IEEE 1149. 1 JTAG capability

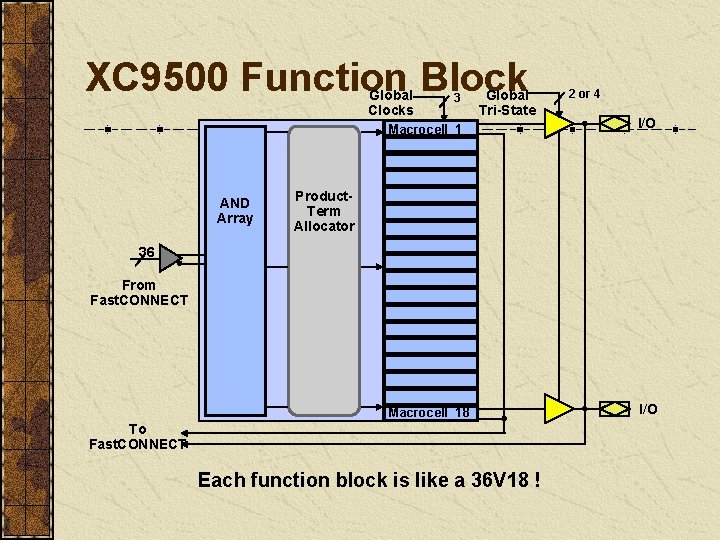

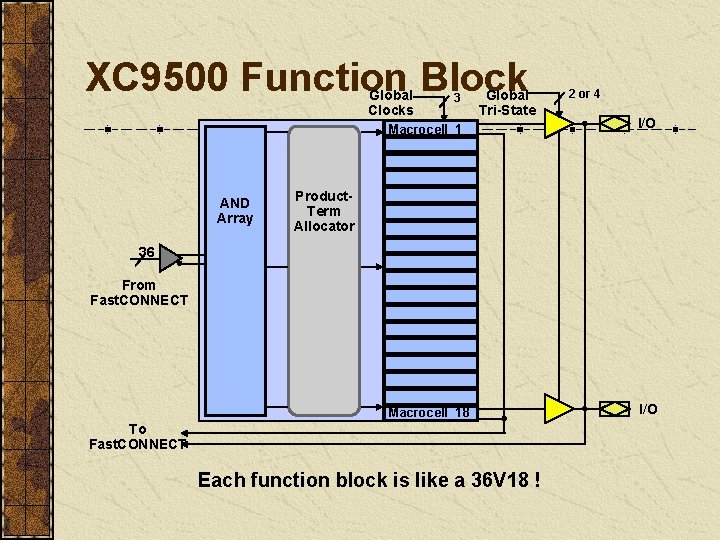

XC 9500 Function Block Global Clocks AND Array 3 Global Tri-State 2 or 4 Macrocell 1 I/O Macrocell 18 I/O Product. Term Allocator 36 From Fast. CONNECT To Fast. CONNECT Each function block is like a 36 V 18 !

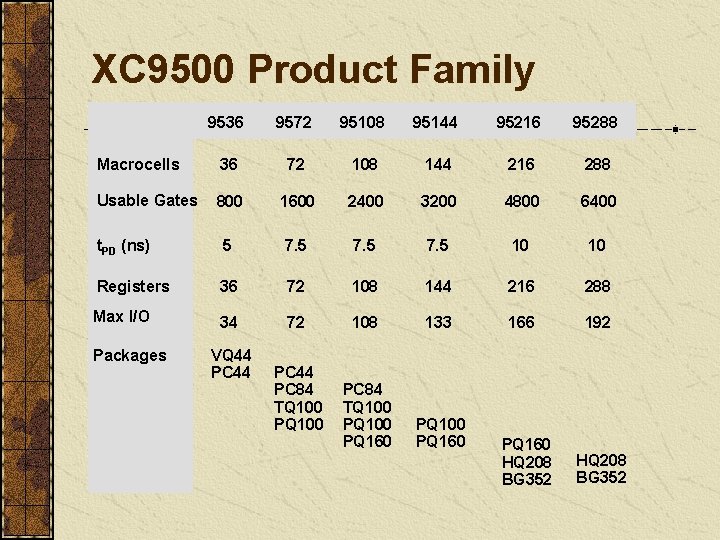

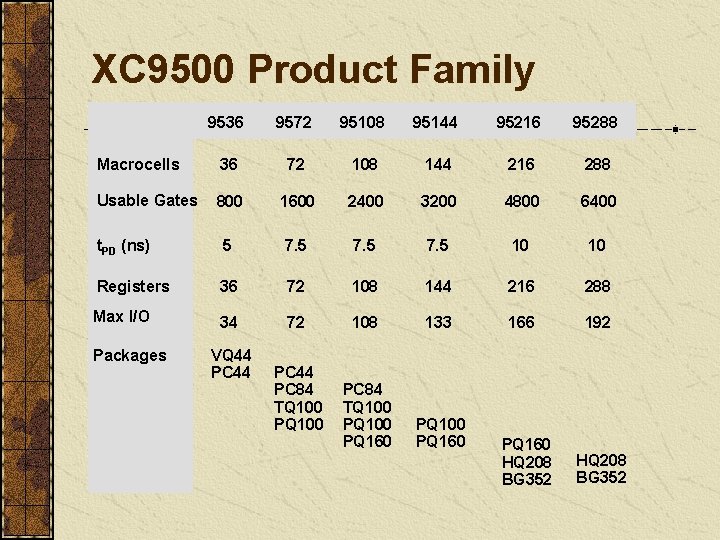

XC 9500 Product Family 9536 9572 95108 95144 95216 95288 Macrocells 36 72 108 144 216 288 Usable Gates 800 1600 2400 3200 4800 6400 t. PD (ns) 5 7. 5 10 10 Registers 36 72 108 144 216 288 Max I/O 34 72 108 133 166 192 PC 84 TQ 100 PQ 160 PQ 100 PQ 160 Packages VQ 44 PC 84 TQ 100 PQ 160 HQ 208 BG 352

CPLDs and FPGAs XC 9500 CPLD XC 4000 FPGA Spartan II FPGA Virtex FPGA

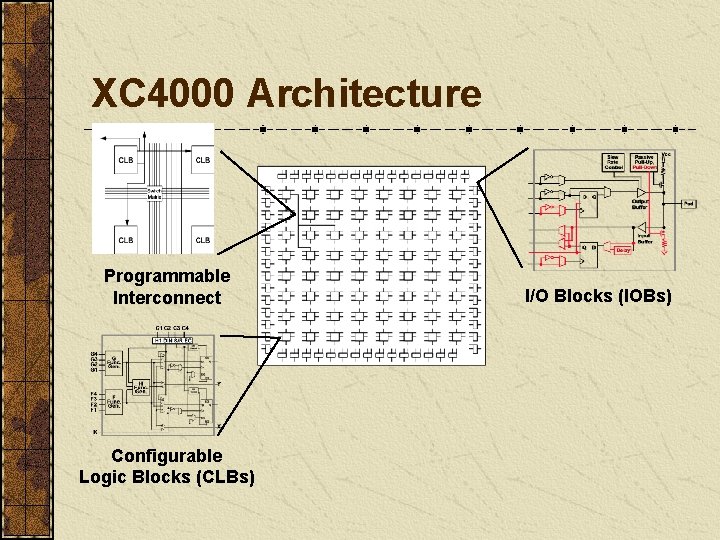

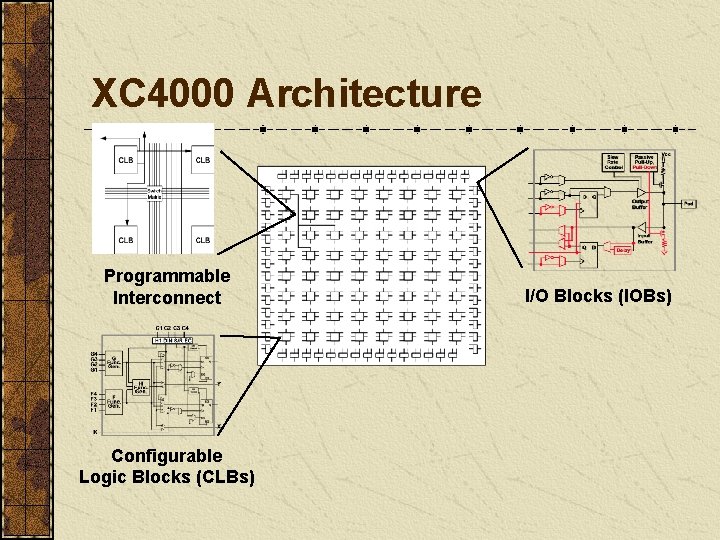

XC 4000 Architecture Programmable Interconnect Configurable Logic Blocks (CLBs) I/O Blocks (IOBs)

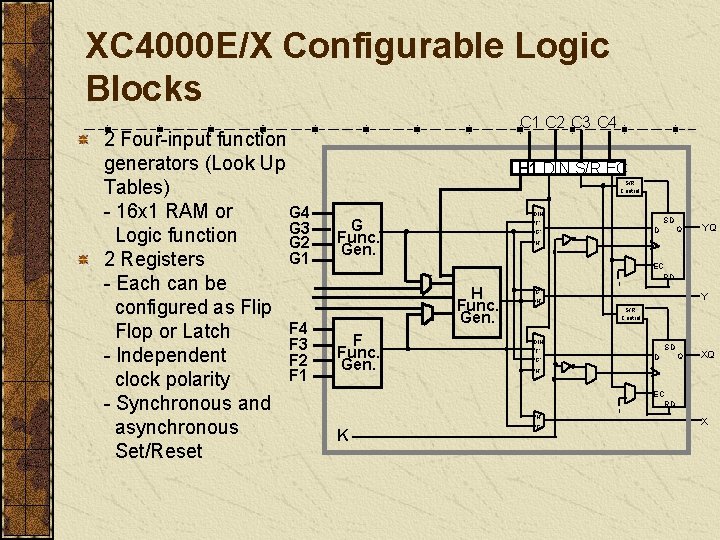

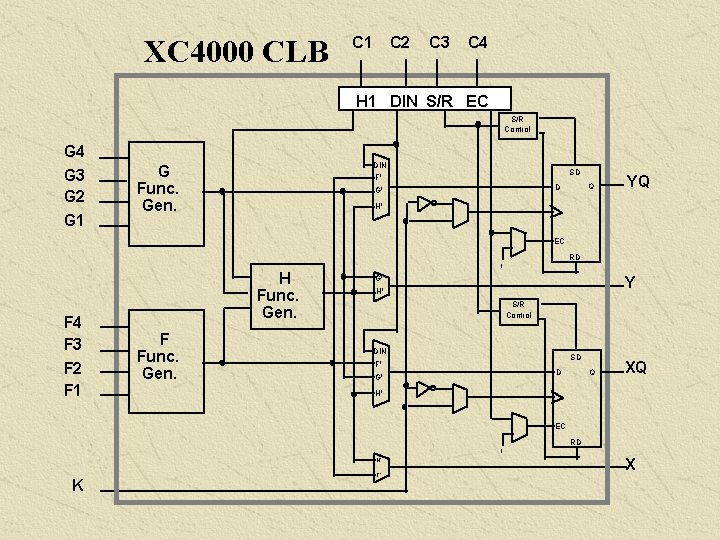

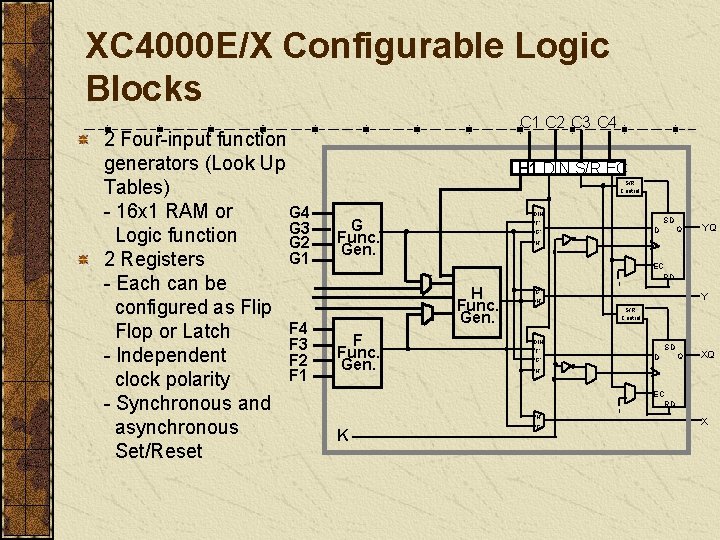

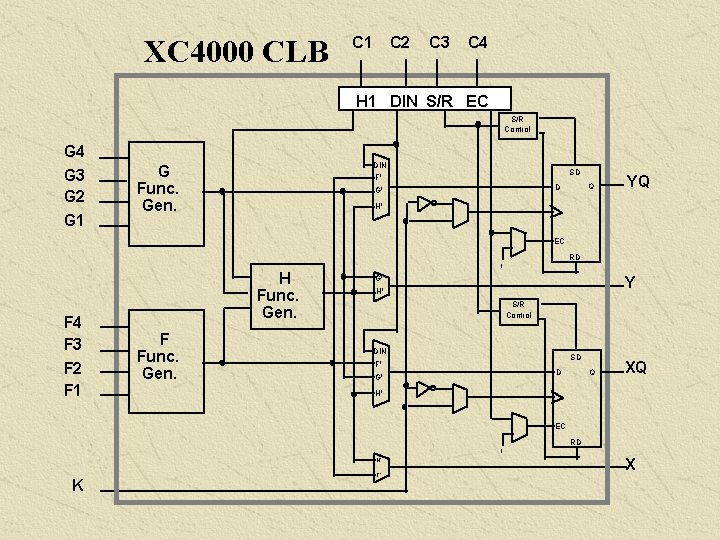

XC 4000 E/X Configurable Logic Blocks 2 Four-input function generators (Look Up Tables) G 4 - 16 x 1 RAM or G 3 Logic function G 2 G 1 2 Registers - Each can be configured as Flip F 4 Flop or Latch F 3 - Independent F 2 F 1 clock polarity - Synchronous and asynchronous Set/Reset C 1 C 2 C 3 C 4 H 1 DIN S/R EC S/R Control DIN G Func. Gen. YQ 1 EC RD G' H' Y S/R Control DIN SD F' G' D Q XQ H' H' K Q D H' H Func. Gen. F Func. Gen. SD F' G' F' 1 EC RD X

XC 4000 CLB C 2 C 1 C 3 C 4 H 1 DIN S/R EC S/R Control G 4 G 3 G 2 G 1 DIN G Func. Gen. SD F' Q D G' YQ H' EC RD 1 F 4 F 3 F 2 F 1 H Func. Gen. F Func. Gen. Y G' H' S/R Control DIN SD F' Q D G' XQ H' EC RD 1 H' K F' X

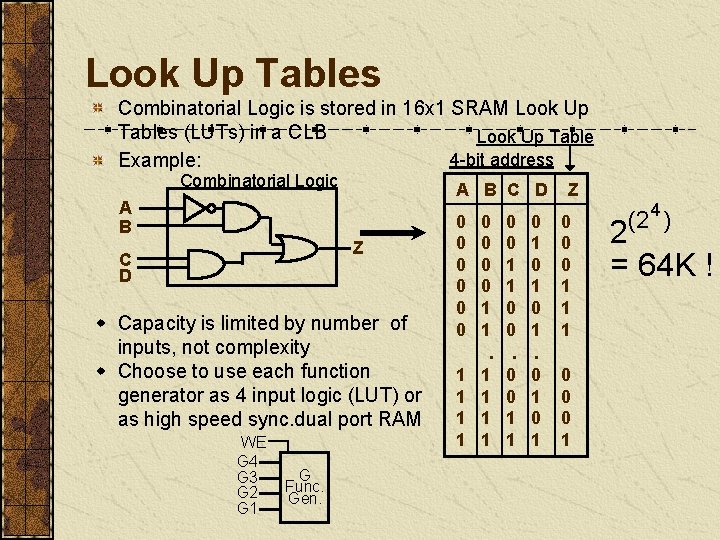

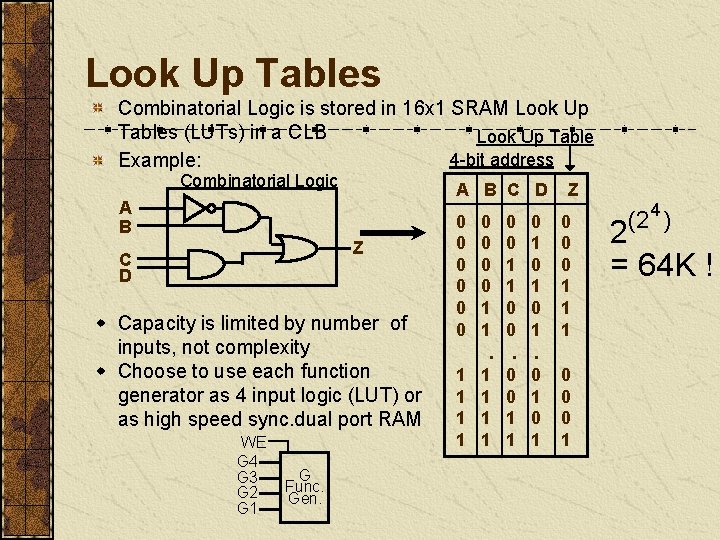

Look Up Tables Combinatorial Logic is stored in 16 x 1 SRAM Look Up Tables (LUTs) in a CLB Look Up Table 4 -bit address Example: Combinatorial Logic A B C D A B Z C D w Capacity is limited by number of inputs, not complexity w Choose to use each function generator as 4 input logic (LUT) or as high speed sync. dual port RAM WE G 4 G 3 G 2 G 1 G Func. Gen. 0 0 0 0 0 1 1 0 0 0 1 0 1 Z 0 0 0 1 1 1 . . . 1 1 1 1 0 0 1 1 0 1 0 0 0 1 4 2(2 ) = 64 K !

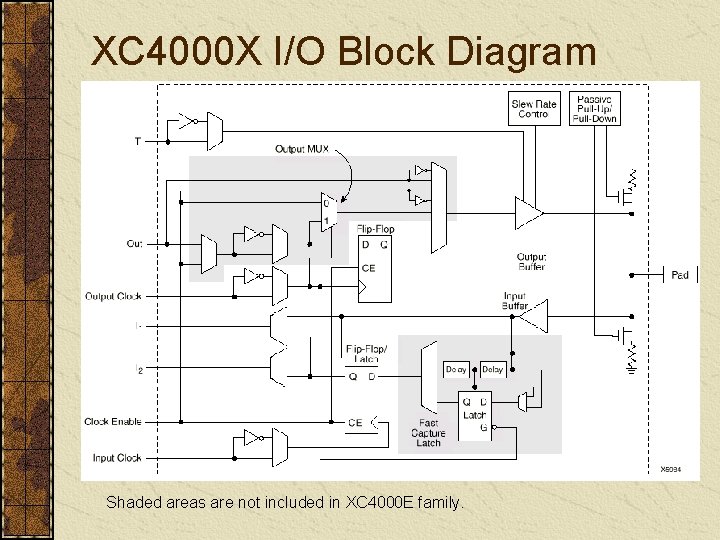

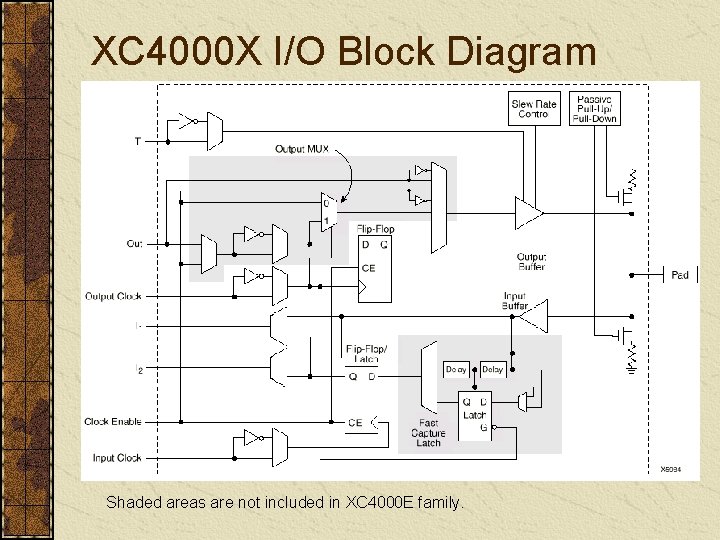

XC 4000 X I/O Block Diagram Shaded areas are not included in XC 4000 E family.

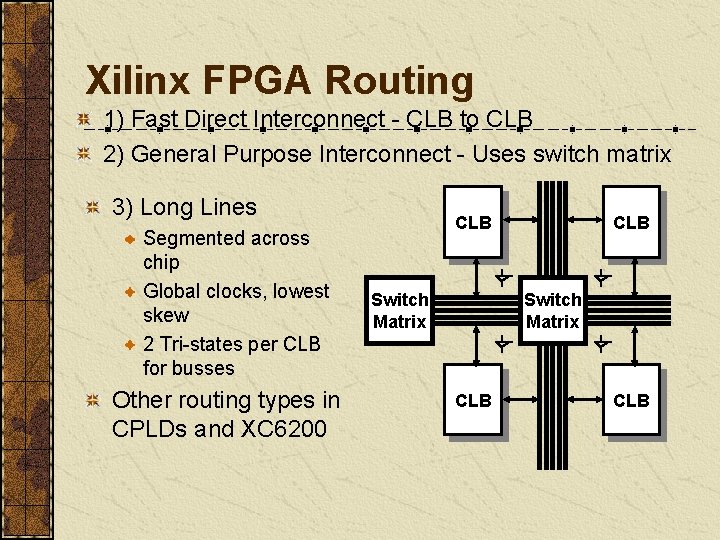

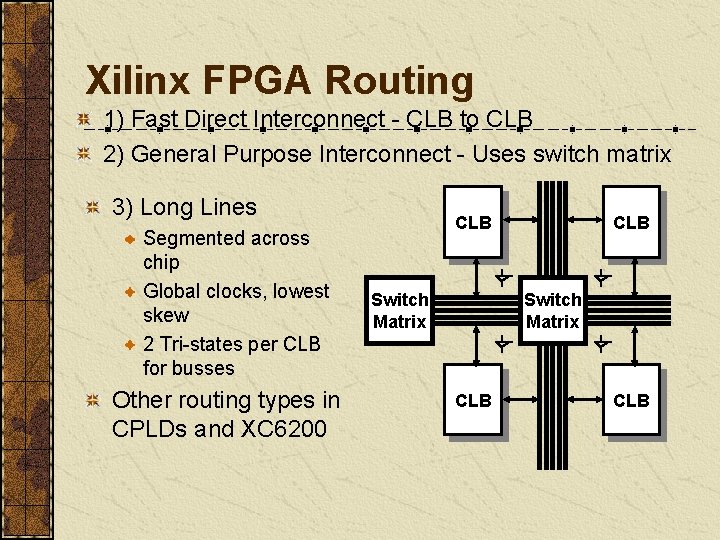

Xilinx FPGA Routing 1) Fast Direct Interconnect - CLB to CLB 2) General Purpose Interconnect - Uses switch matrix 3) Long Lines Segmented across chip Global clocks, lowest skew 2 Tri-states per CLB for busses Other routing types in CPLDs and XC 6200 CLB Switch Matrix CLB

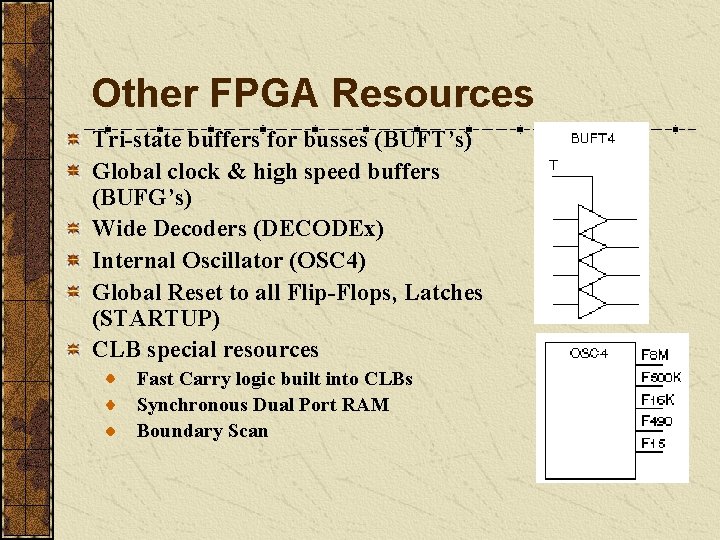

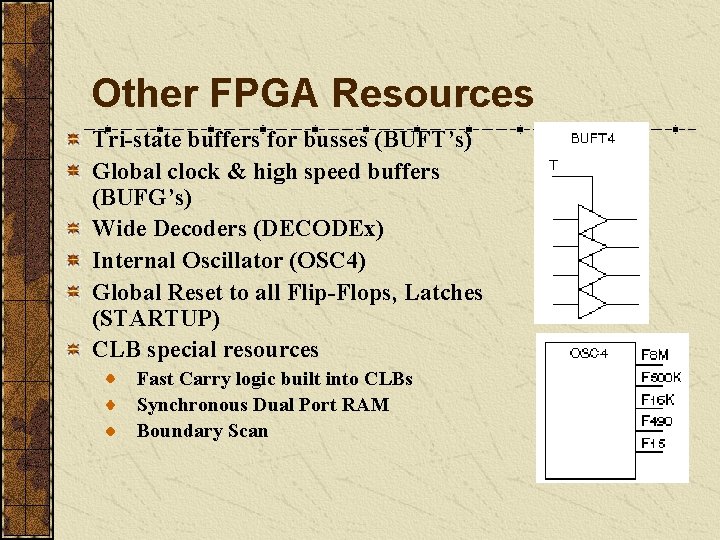

Other FPGA Resources Tri-state buffers for busses (BUFT’s) Global clock & high speed buffers (BUFG’s) Wide Decoders (DECODEx) Internal Oscillator (OSC 4) Global Reset to all Flip-Flops, Latches (STARTUP) CLB special resources Fast Carry logic built into CLBs Synchronous Dual Port RAM Boundary Scan

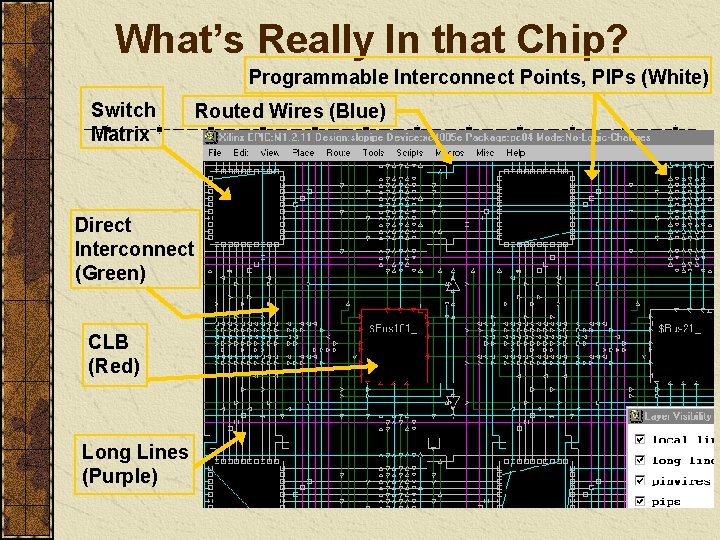

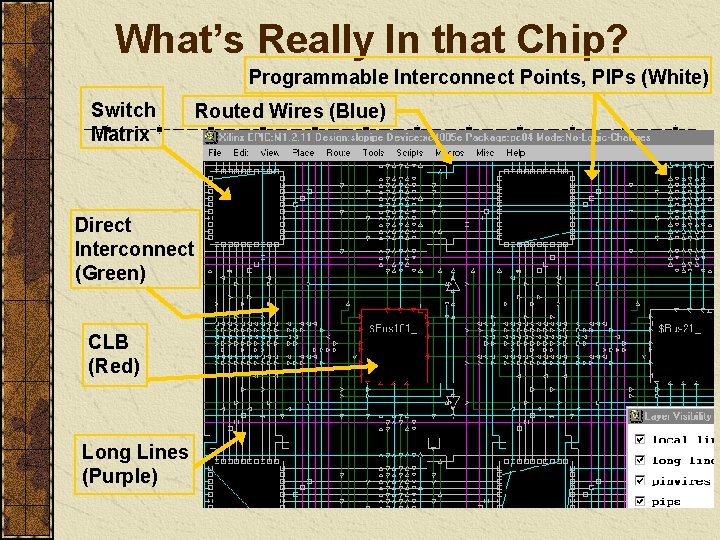

What’s Really In that Chip? Programmable Interconnect Points, PIPs (White) Switch Matrix Direct Interconnect (Green) CLB (Red) Long Lines (Purple) Routed Wires (Blue)

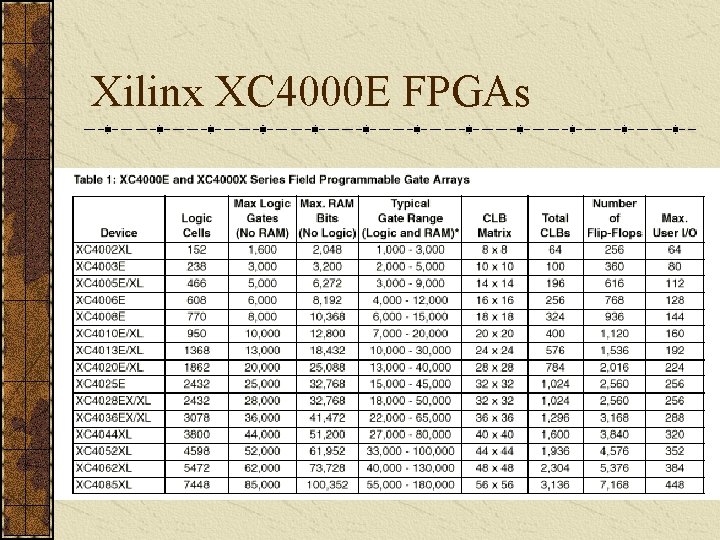

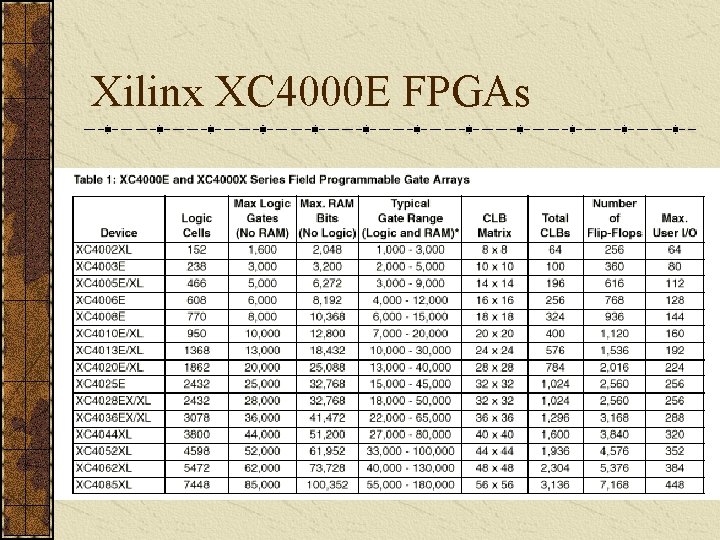

Xilinx XC 4000 E FPGAs

CPLDs and FPGAs XC 9500 CPLD XC 4000 FPGA Spartan II FPGA Virtex FPGA

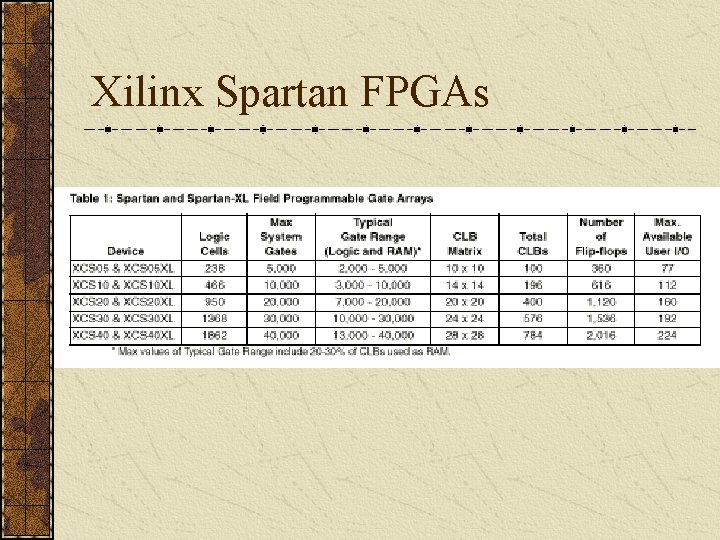

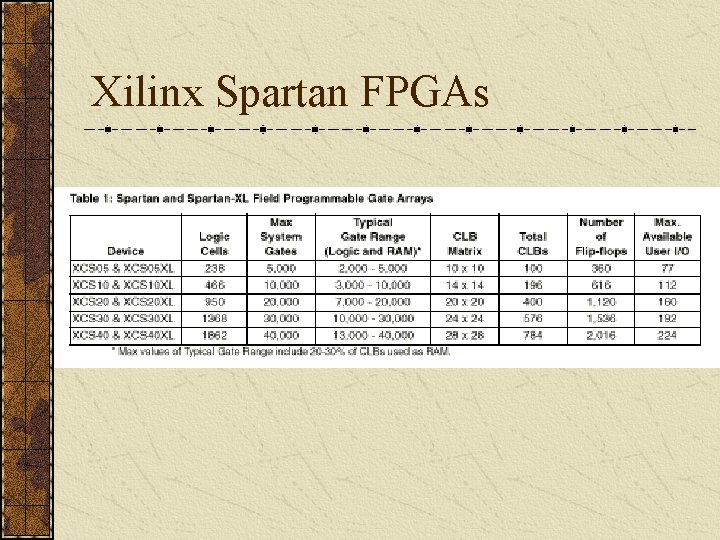

Xilinx Spartan FPGAs

CPLDs and FPGAs XC 9500 CPLD XC 4000 FPGA Spartan II FPGA Virtex FPGA

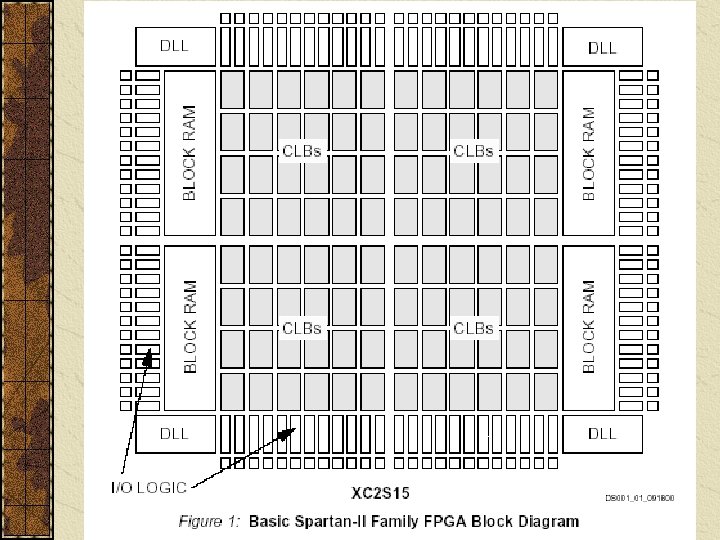

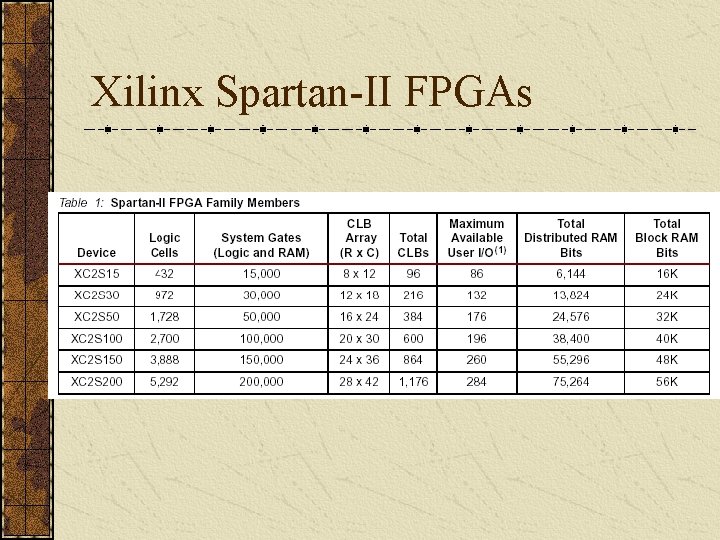

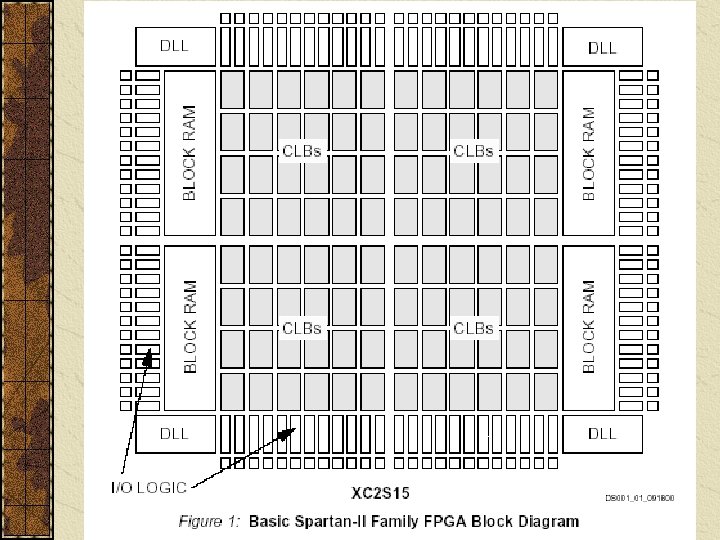

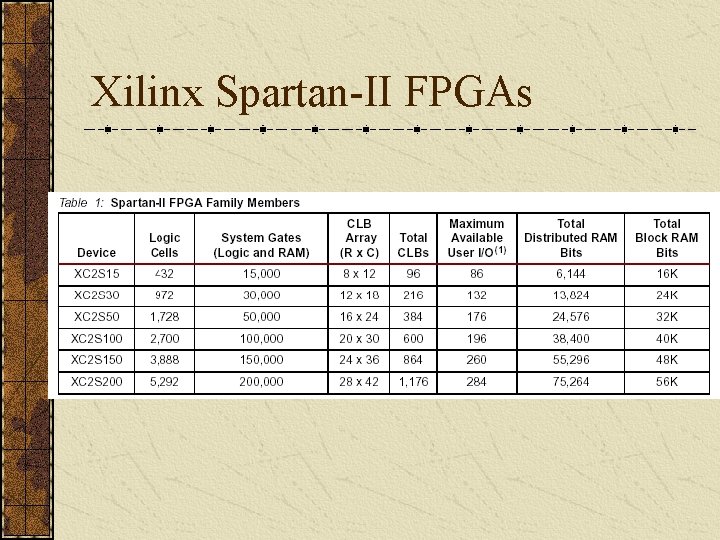

Xilinx Spartan-II FPGAs

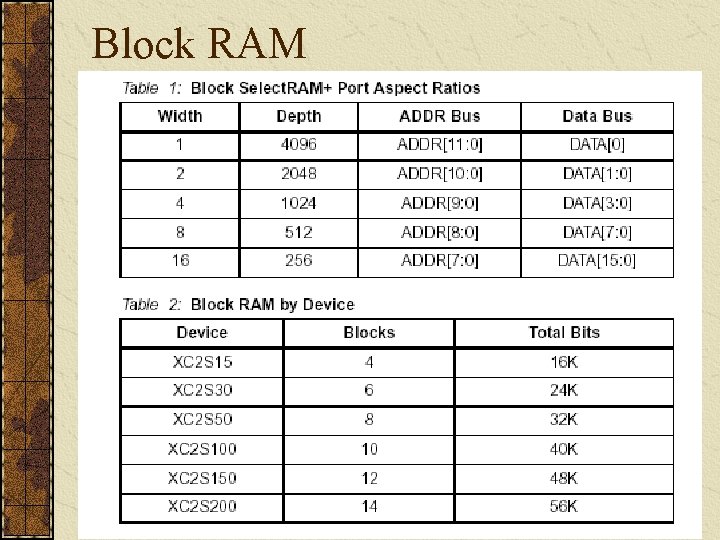

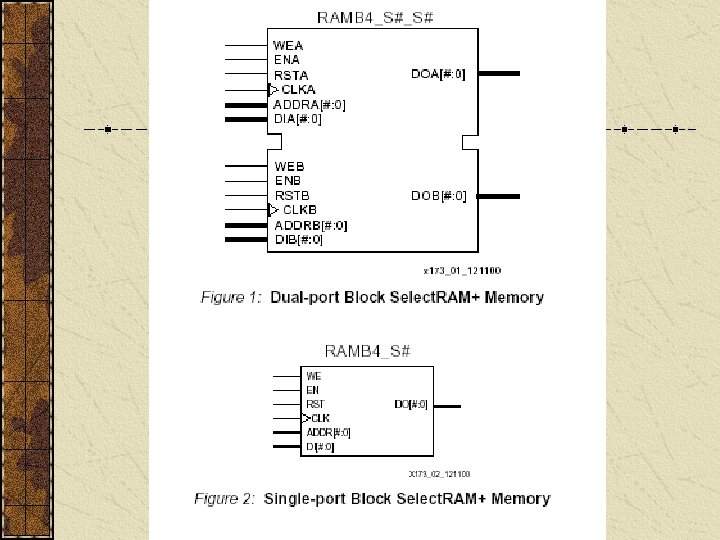

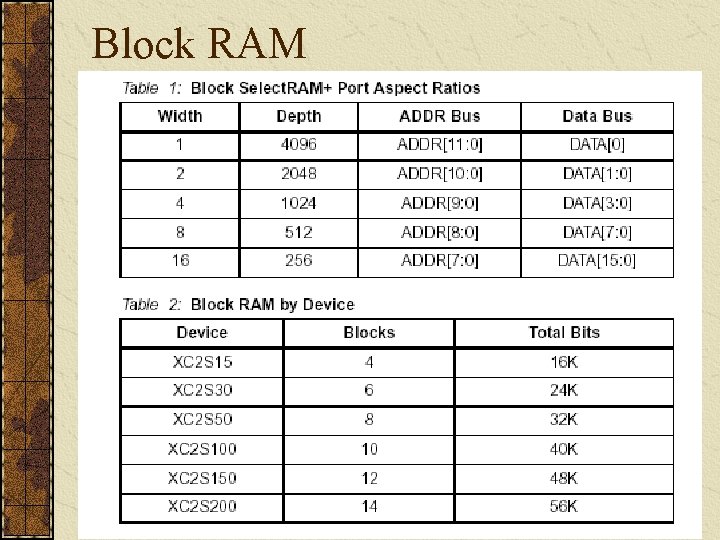

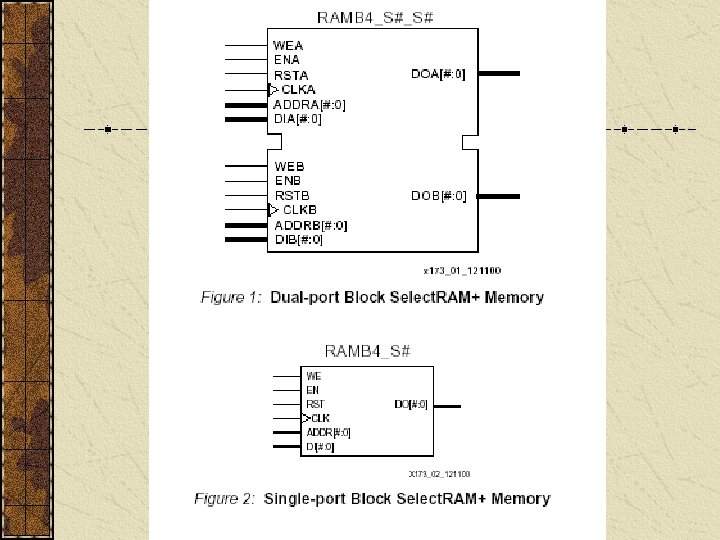

Block RAM

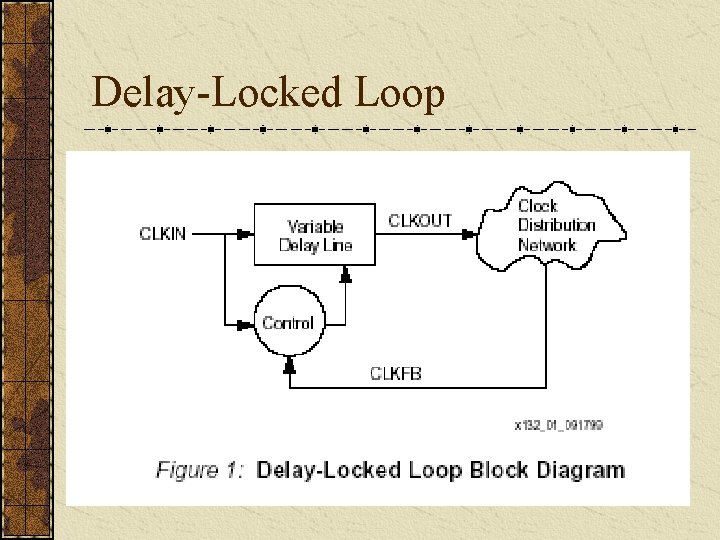

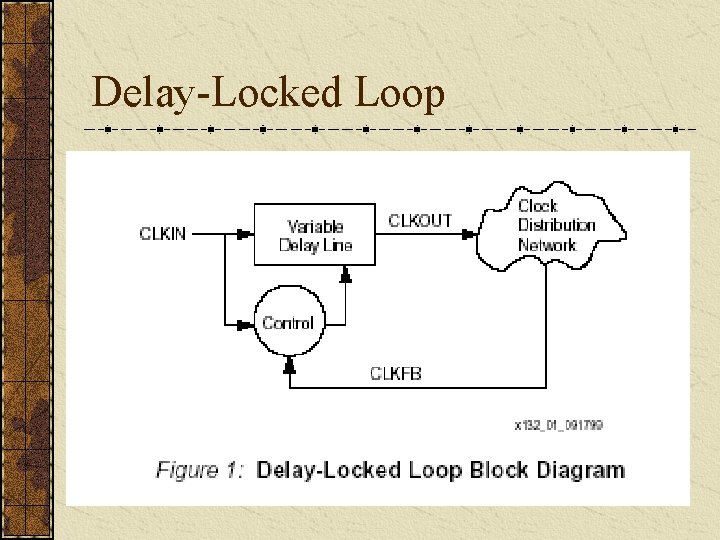

Delay-Locked Loop

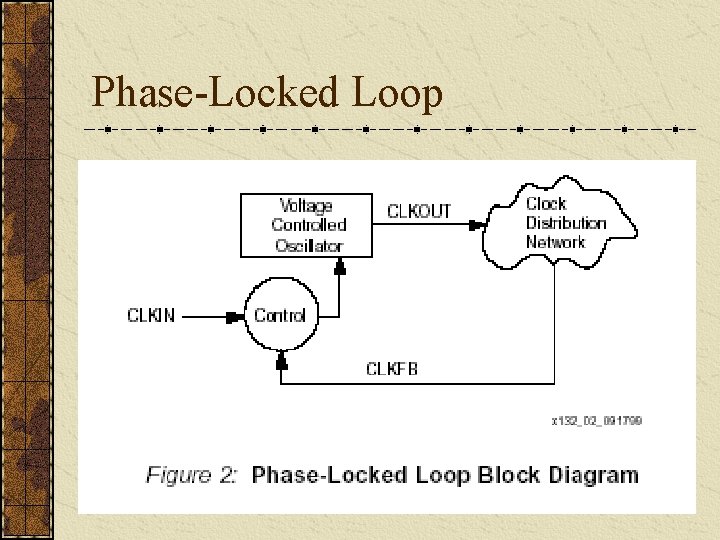

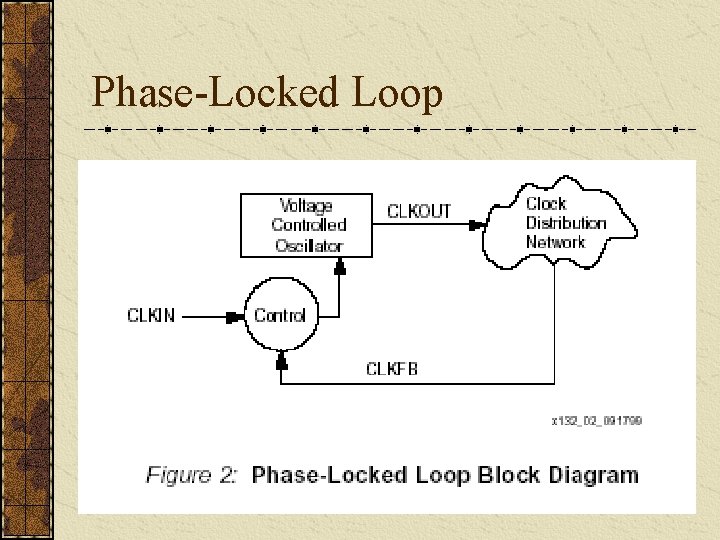

Phase-Locked Loop

CPLDs and FPGAs XC 9500 CPLD XC 4000 FPGA Spartan II FPGA Virtex FPGA

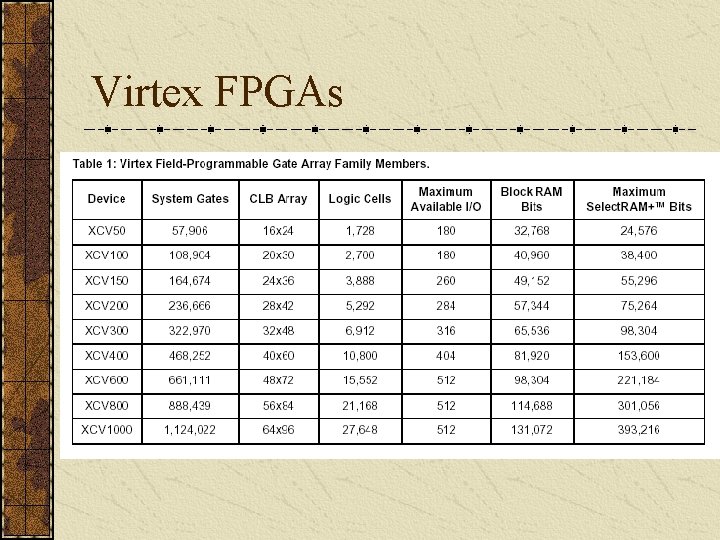

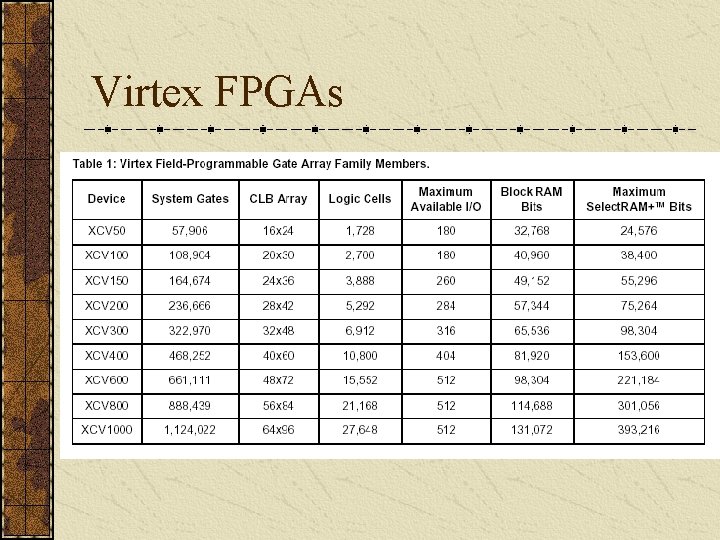

Virtex FPGAs

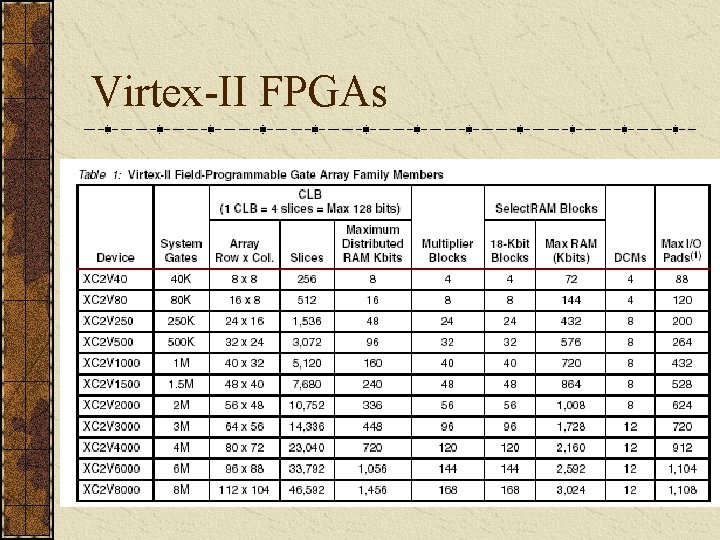

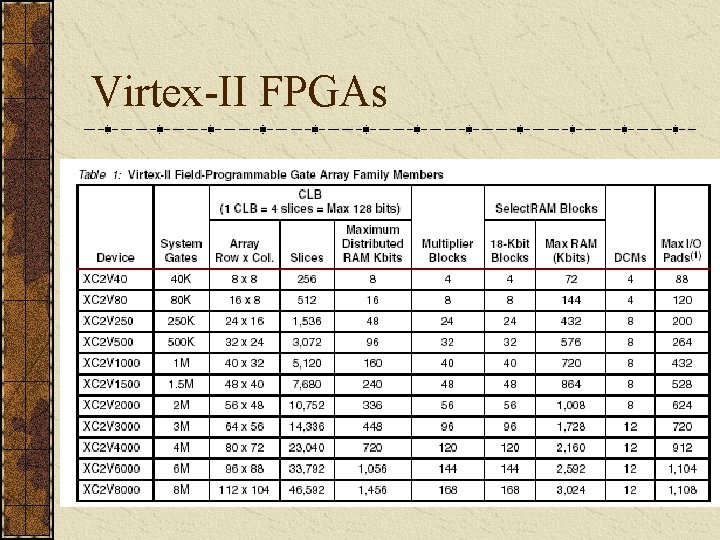

Virtex-II FPGAs

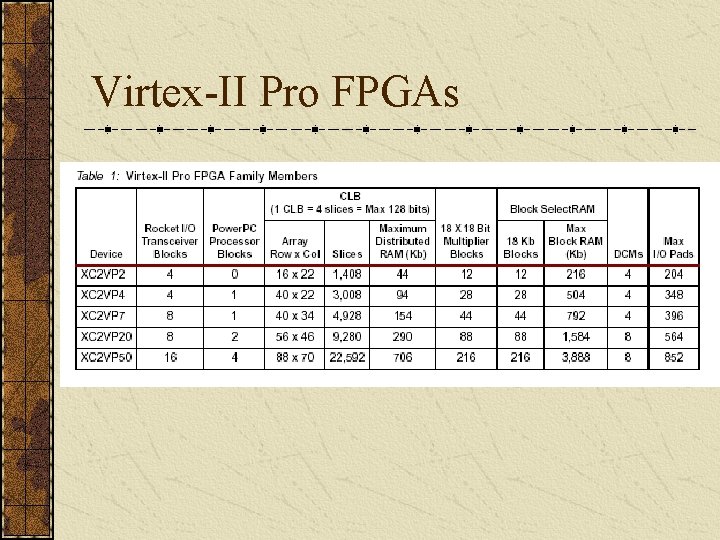

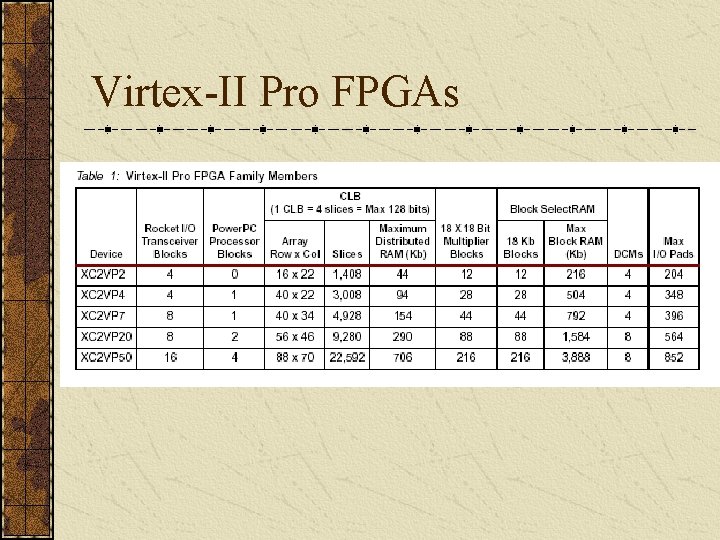

Virtex-II Pro FPGAs