Xilinx 95009500 XL CPLD Testing CNGS 2009 TEMPEMI

- Slides: 36

Xilinx 9500/9500 XL CPLD Testing CNGS 2009 TE/MPE/MI Radiation Working Group Update 3. 09 3 September 2009 rd B. Todd, M. Zerlauth, I. Romera, A. Castaneda 0 v 2

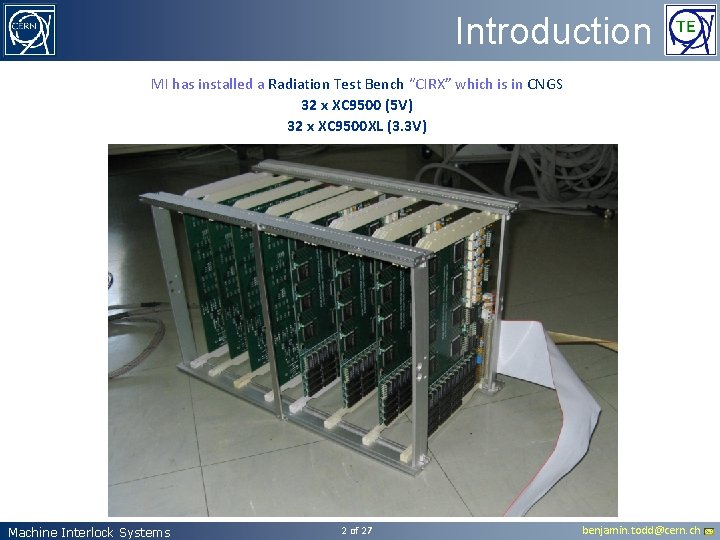

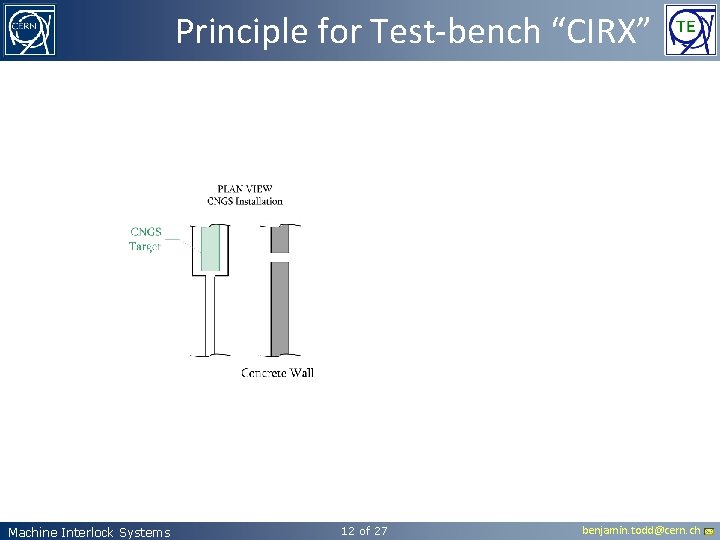

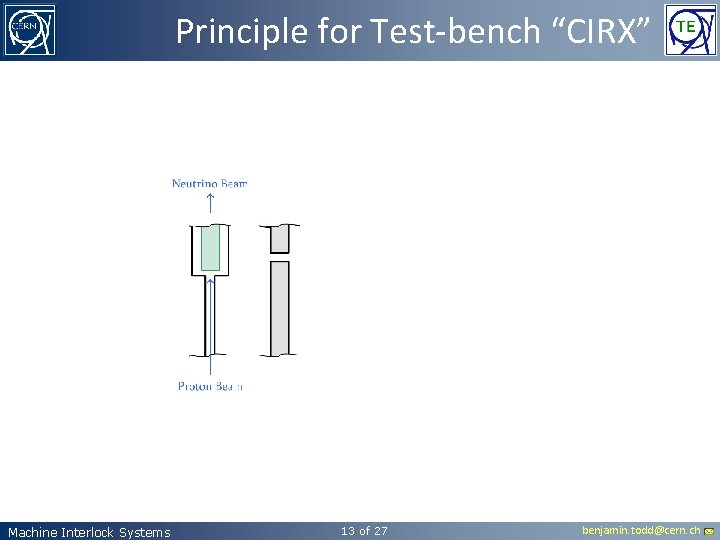

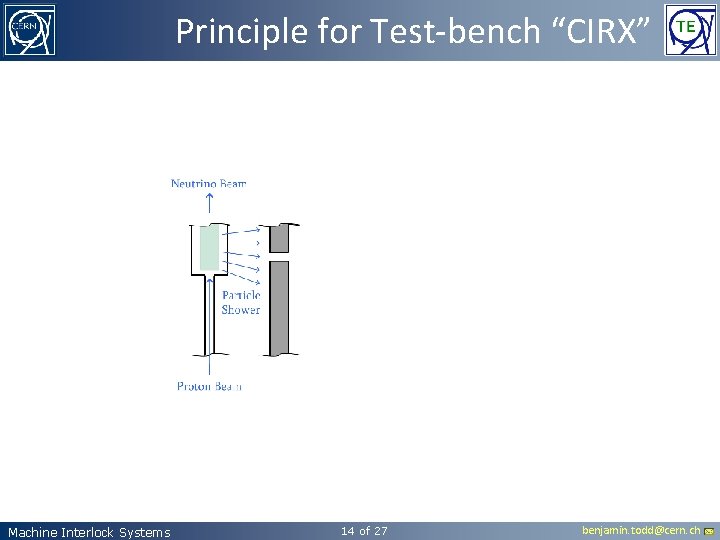

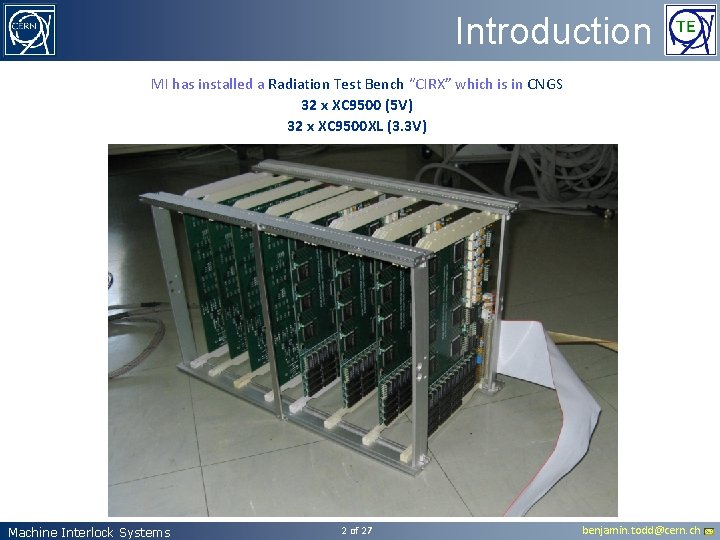

Introduction MI has installed a Radiation Test Bench “CIRX” which is in CNGS 32 x XC 9500 (5 V) 32 x XC 9500 XL (3. 3 V) Machine Interlock Systems 2 of 27 benjamin. todd@cern. ch

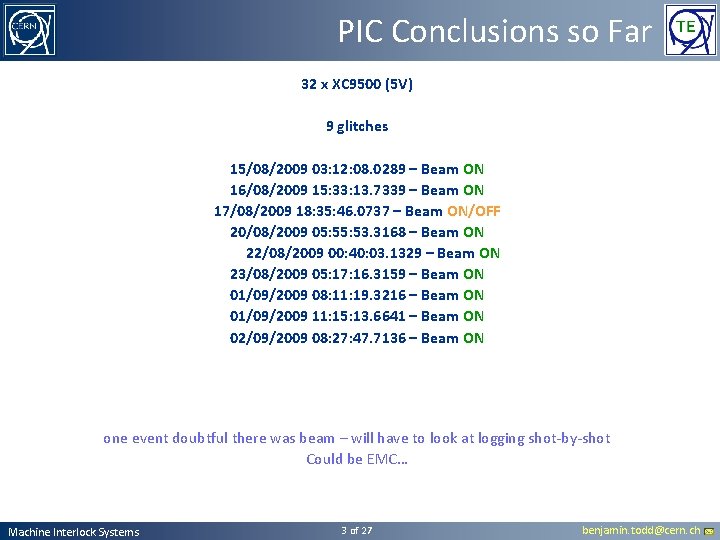

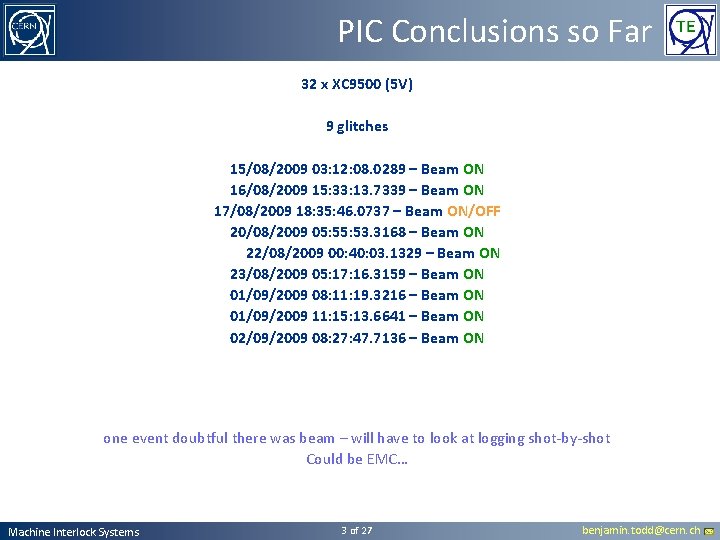

PIC Conclusions so Far 32 x XC 9500 (5 V) 9 glitches 15/08/2009 03: 12: 08. 0289 – Beam ON 16/08/2009 15: 33: 13. 7339 – Beam ON 17/08/2009 18: 35: 46. 0737 – Beam ON/OFF 20/08/2009 05: 53. 3168 – Beam ON 22/08/2009 00: 40: 03. 1329 – Beam ON 23/08/2009 05: 17: 16. 3159 – Beam ON 01/09/2009 08: 11: 19. 3216 – Beam ON 01/09/2009 11: 15: 13. 6641 – Beam ON 02/09/2009 08: 27: 47. 7136 – Beam ON one event doubtful there was beam – will have to look at logging shot-by-shot Could be EMC… Machine Interlock Systems 3 of 27 benjamin. todd@cern. ch

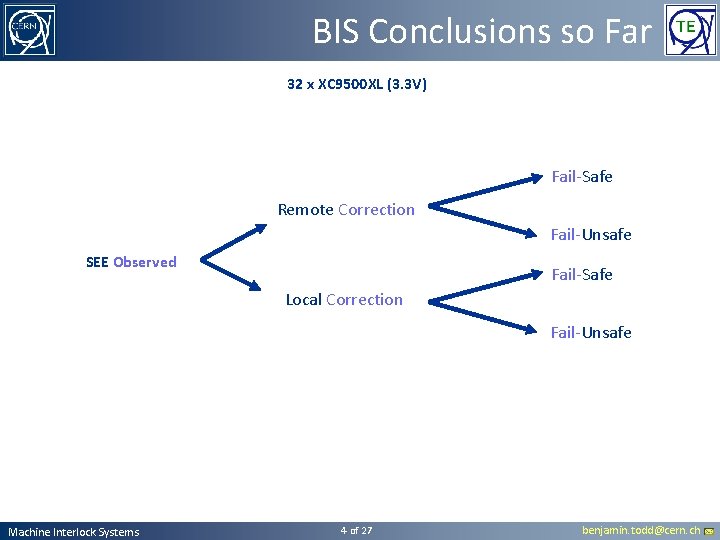

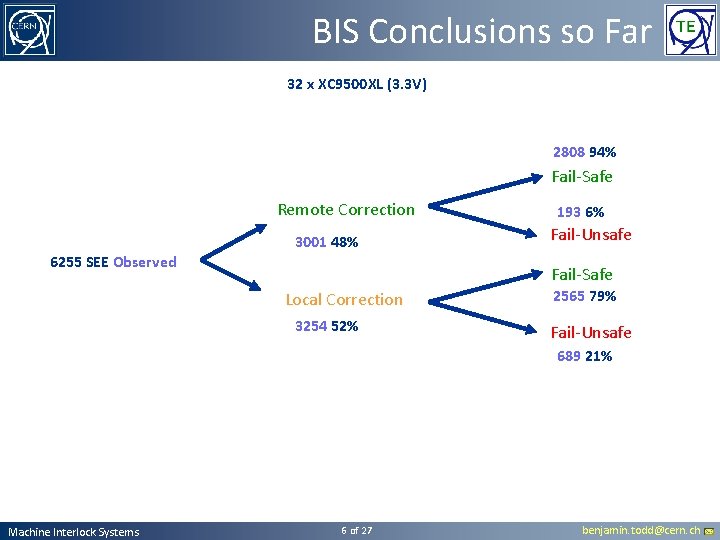

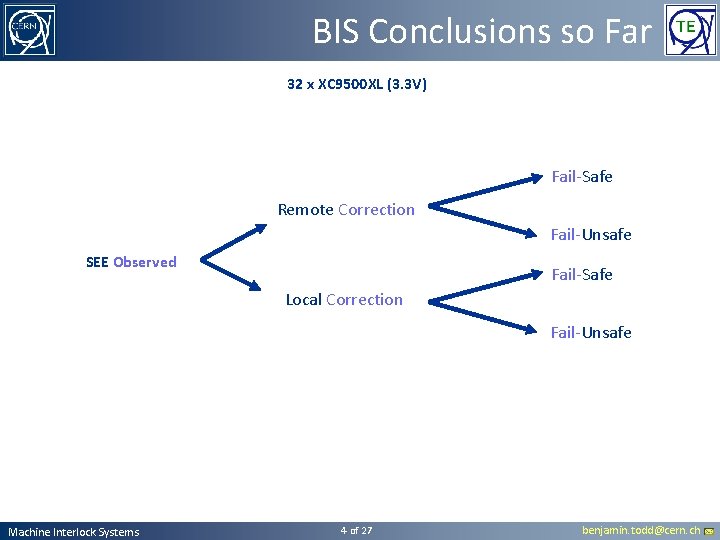

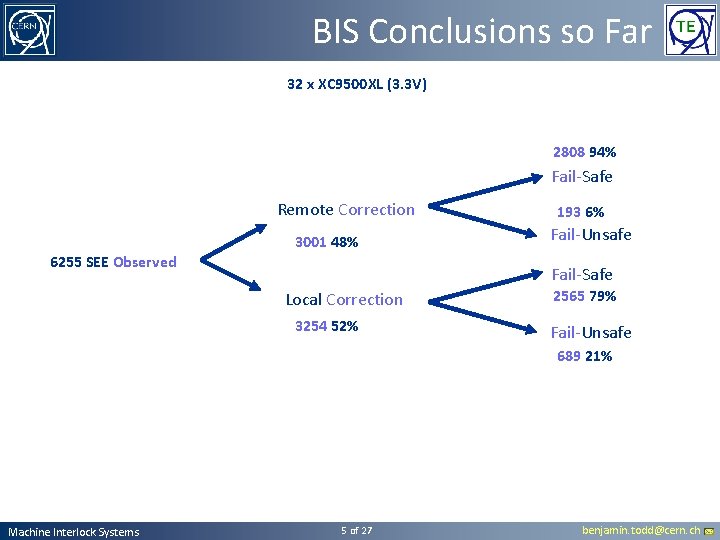

BIS Conclusions so Far 32 x XC 9500 XL (3. 3 V) Fail-Safe Remote Correction Fail-Unsafe 6255 SEE Observed Fail-Safe Local Correction Fail-Unsafe Machine Interlock Systems 4 of 27 benjamin. todd@cern. ch

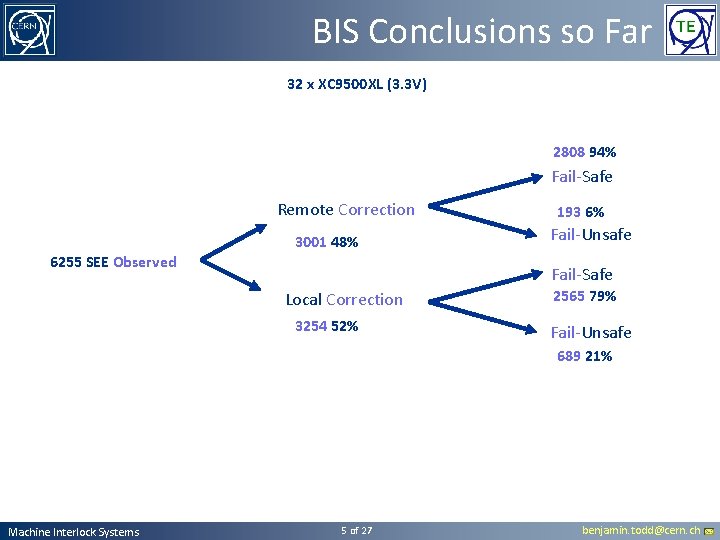

BIS Conclusions so Far 32 x XC 9500 XL (3. 3 V) 2808 94% Fail-Safe Remote Correction 3001 48% 6255 SEE Observed 193 6% Fail-Unsafe Fail-Safe Local Correction 3254 52% 2565 79% Fail-Unsafe 689 21% Machine Interlock Systems 5 of 27 benjamin. todd@cern. ch

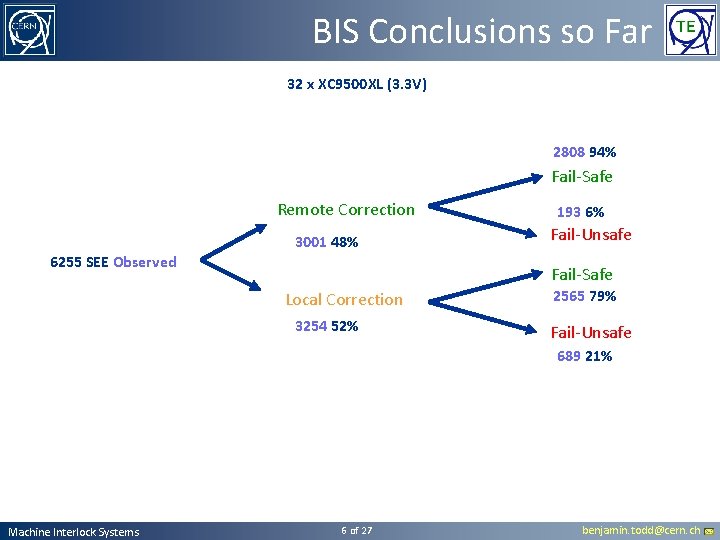

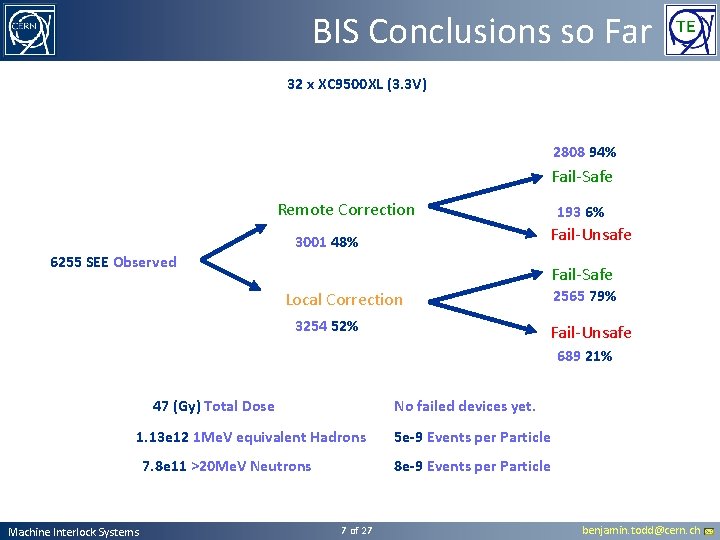

BIS Conclusions so Far 32 x XC 9500 XL (3. 3 V) 2808 94% Fail-Safe Remote Correction 3001 48% 6255 SEE Observed 193 6% Fail-Unsafe Fail-Safe Local Correction 3254 52% 2565 79% Fail-Unsafe 689 21% Machine Interlock Systems 6 of 27 benjamin. todd@cern. ch

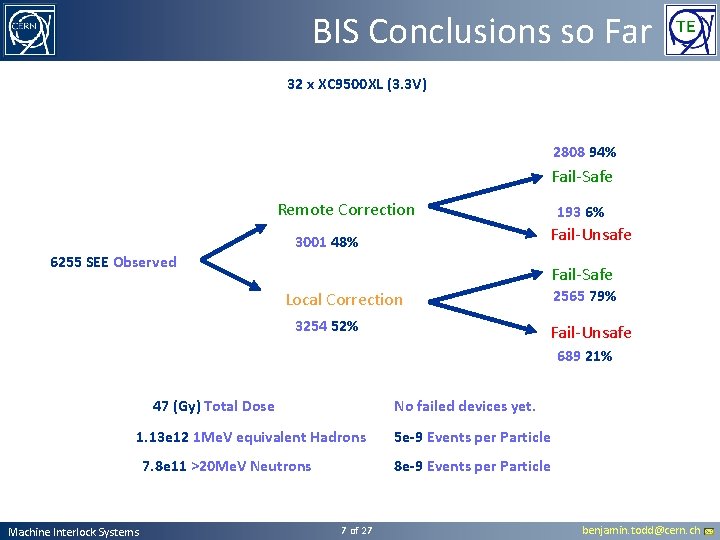

BIS Conclusions so Far 32 x XC 9500 XL (3. 3 V) 2808 94% Fail-Safe Remote Correction 193 6% Fail-Unsafe 3001 48% 6255 SEE Observed Fail-Safe 2565 79% Local Correction 3254 52% Fail-Unsafe 689 21% 47 (Gy) Total Dose No failed devices yet. 1. 13 e 12 1 Me. V equivalent Hadrons 7. 8 e 11 >20 Me. V Neutrons Machine Interlock Systems 5 e-9 Events per Particle 8 e-9 Events per Particle 7 of 27 benjamin. todd@cern. ch

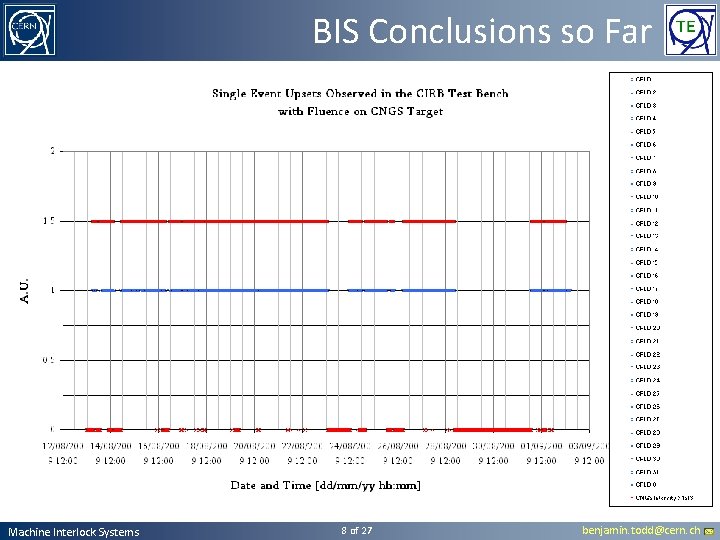

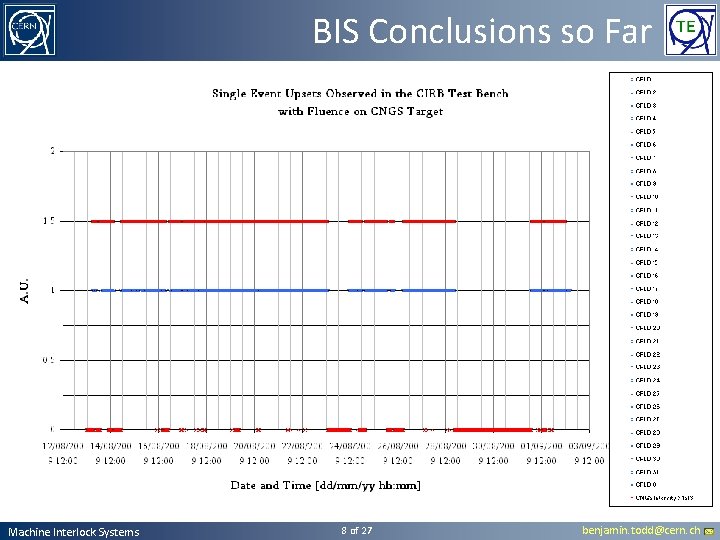

BIS Conclusions so Far Machine Interlock Systems 8 of 27 benjamin. todd@cern. ch

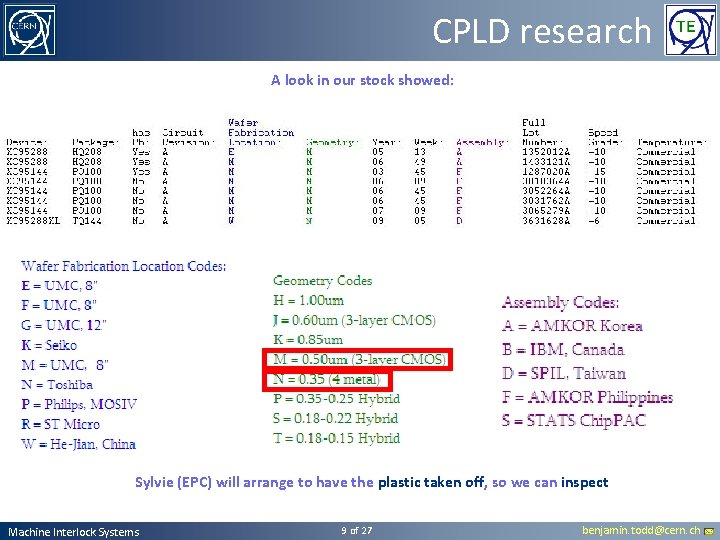

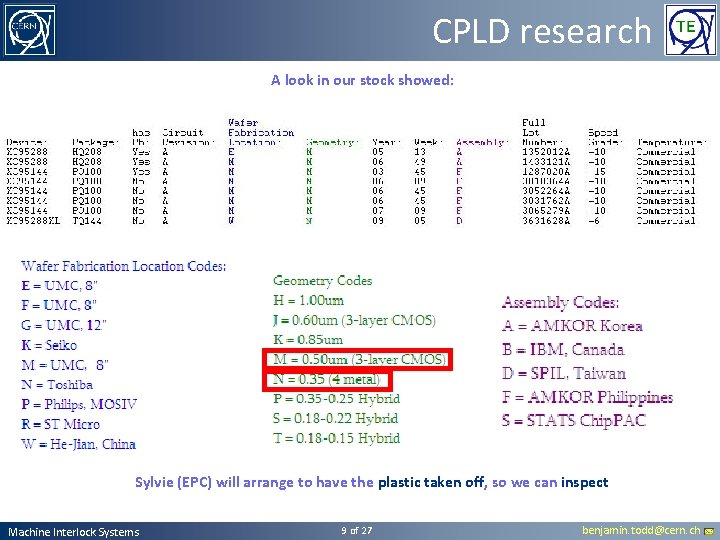

CPLD research A look in our stock showed: Sylvie (EPC) will arrange to have the plastic taken off, so we can inspect Machine Interlock Systems 9 of 27 benjamin. todd@cern. ch

Conclusions Next steps: 1. Keep going Want to get figures for Total Dose too 2. Contingency preparation for moving the BIC away from radiation UA 63/67 Machine Interlock Systems 10 of 27 benjamin. todd@cern. ch

FIN Machine Interlock Systems 11 of 27 benjamin. todd@cern. ch

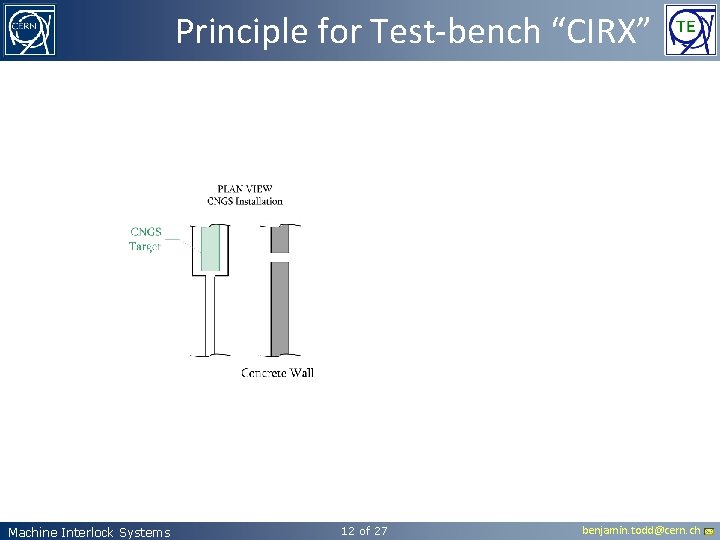

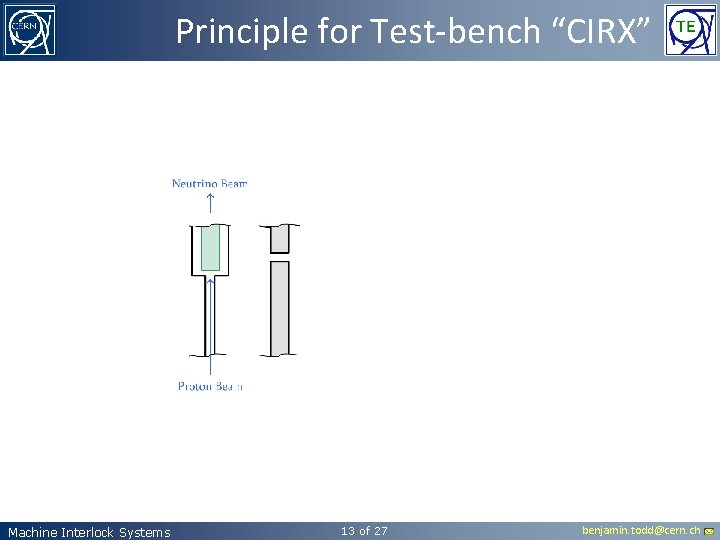

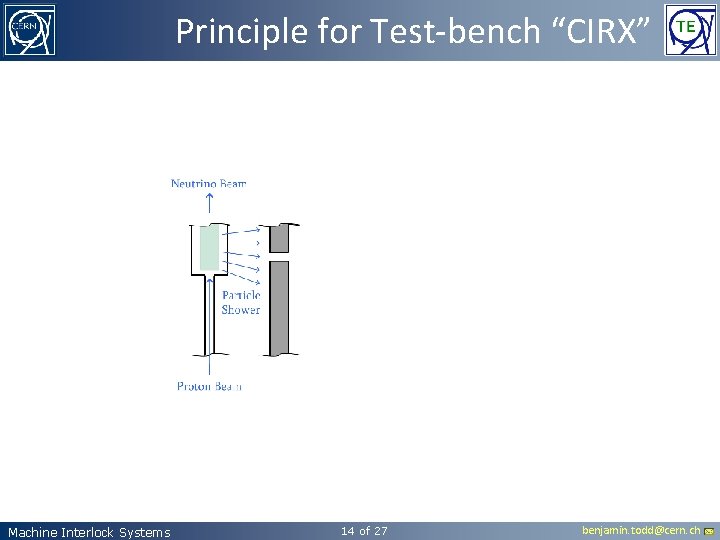

Principle for Test-bench “CIRX” Machine Interlock Systems 12 of 27 benjamin. todd@cern. ch

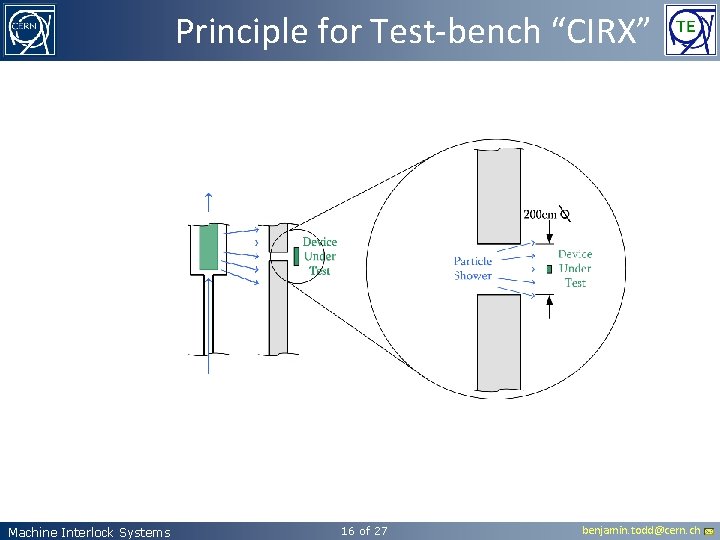

Principle for Test-bench “CIRX” Machine Interlock Systems 13 of 27 benjamin. todd@cern. ch

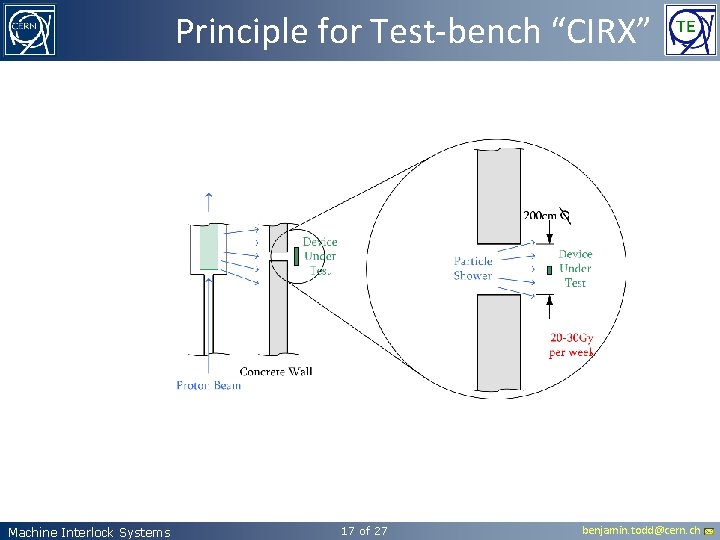

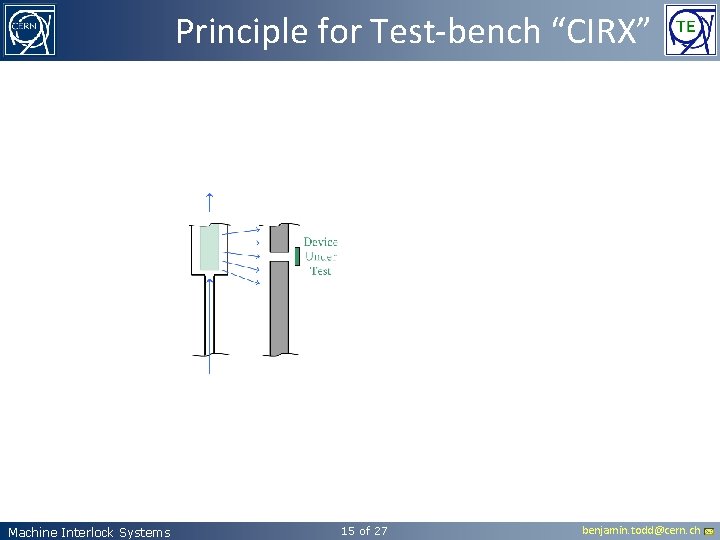

Principle for Test-bench “CIRX” Machine Interlock Systems 14 of 27 benjamin. todd@cern. ch

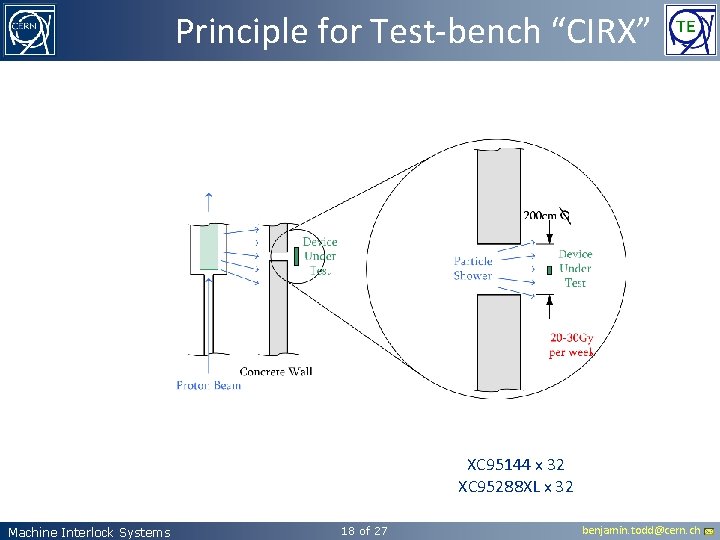

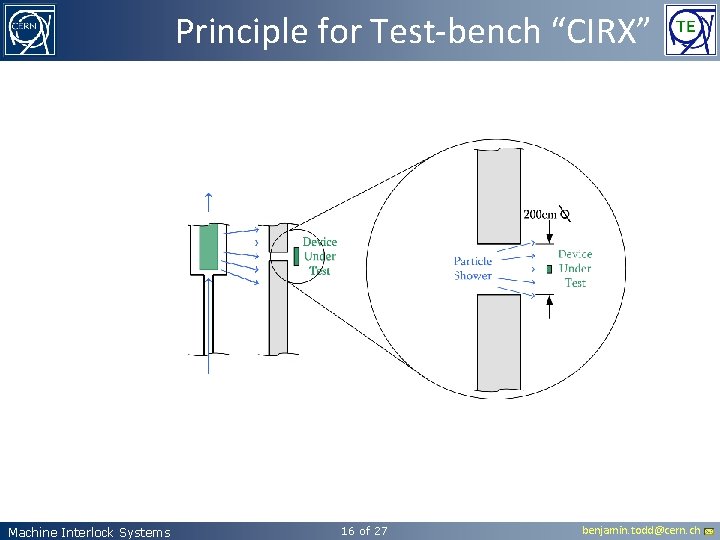

Principle for Test-bench “CIRX” Machine Interlock Systems 15 of 27 benjamin. todd@cern. ch

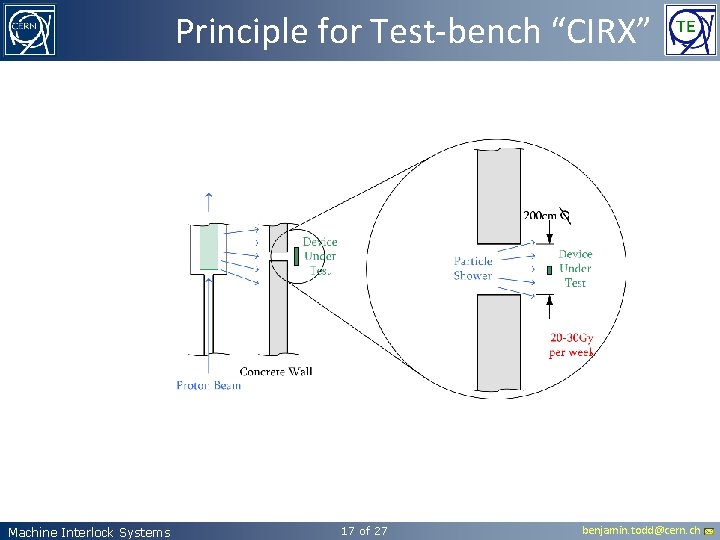

Principle for Test-bench “CIRX” Machine Interlock Systems 16 of 27 benjamin. todd@cern. ch

Principle for Test-bench “CIRX” Machine Interlock Systems 17 of 27 benjamin. todd@cern. ch

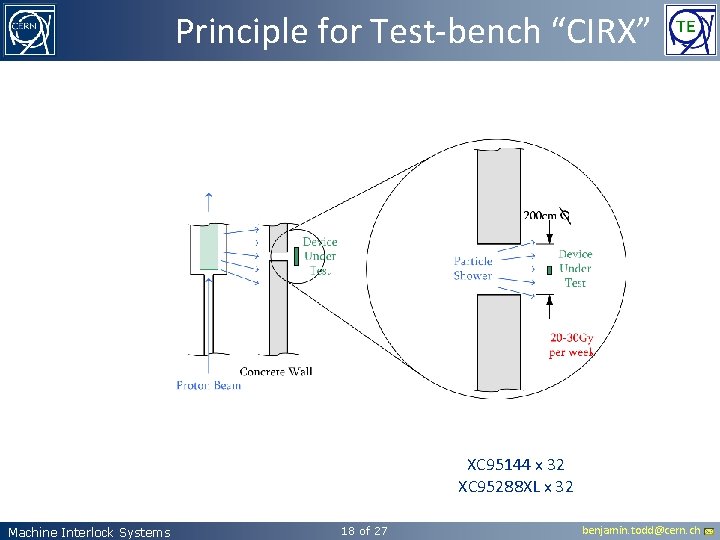

Principle for Test-bench “CIRX” XC 95144 x 32 XC 95288 XL x 32 Machine Interlock Systems 18 of 27 benjamin. todd@cern. ch

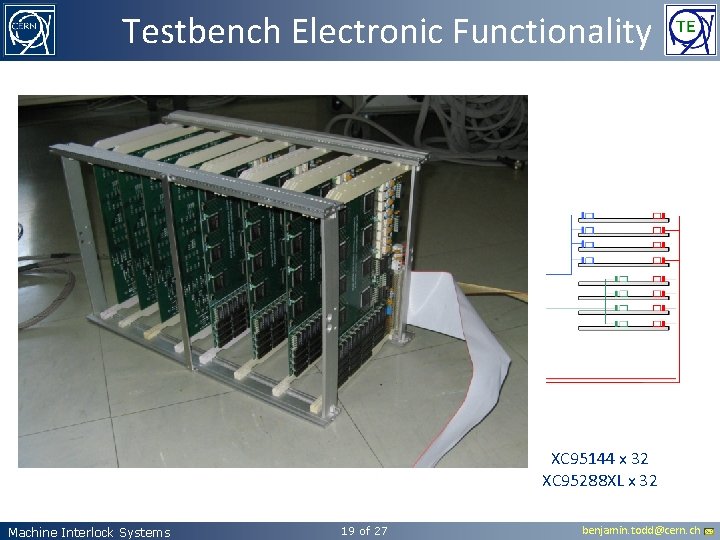

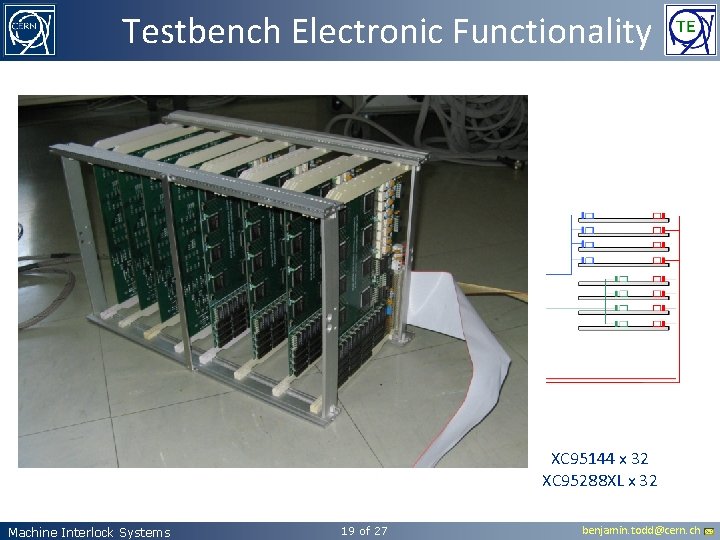

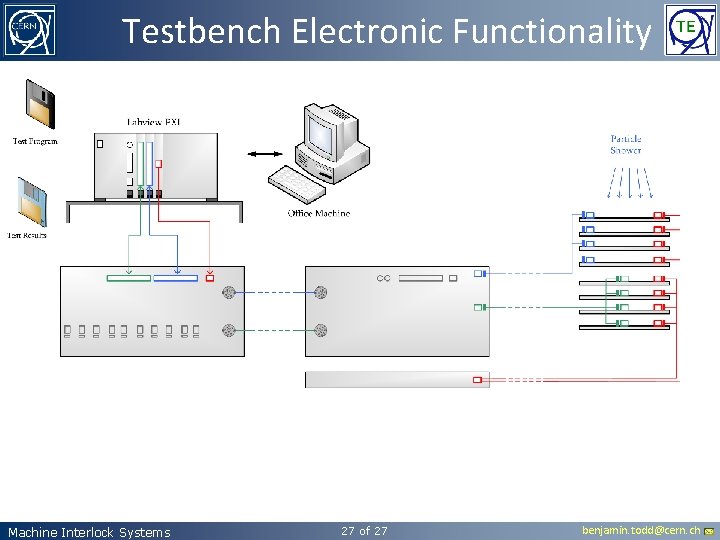

Testbench Electronic Functionality XC 95144 x 32 XC 95288 XL x 32 Machine Interlock Systems 19 of 27 benjamin. todd@cern. ch

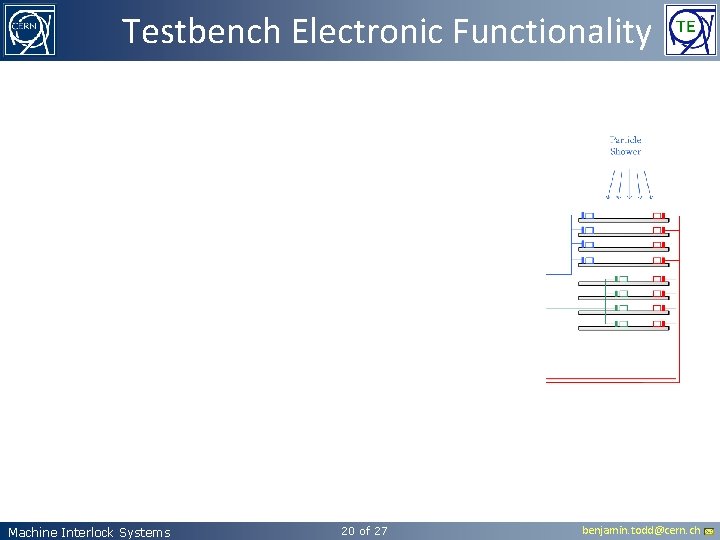

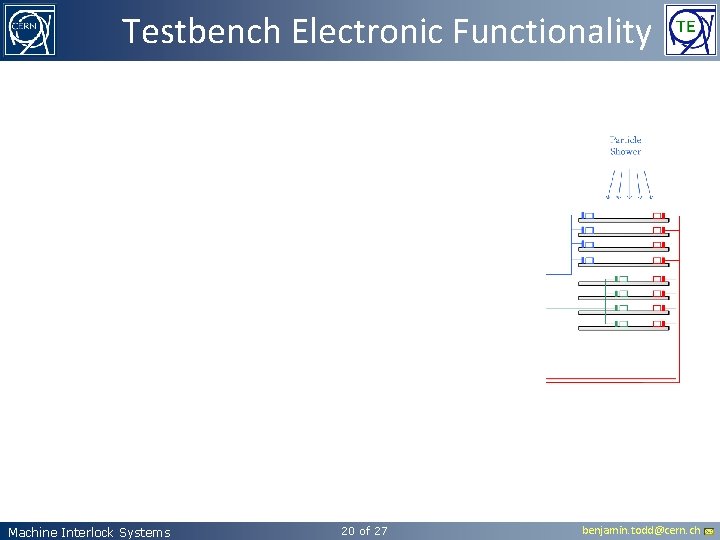

Testbench Electronic Functionality Machine Interlock Systems 20 of 27 benjamin. todd@cern. ch

Testbench Electronic Functionality Machine Interlock Systems 21 of 27 benjamin. todd@cern. ch

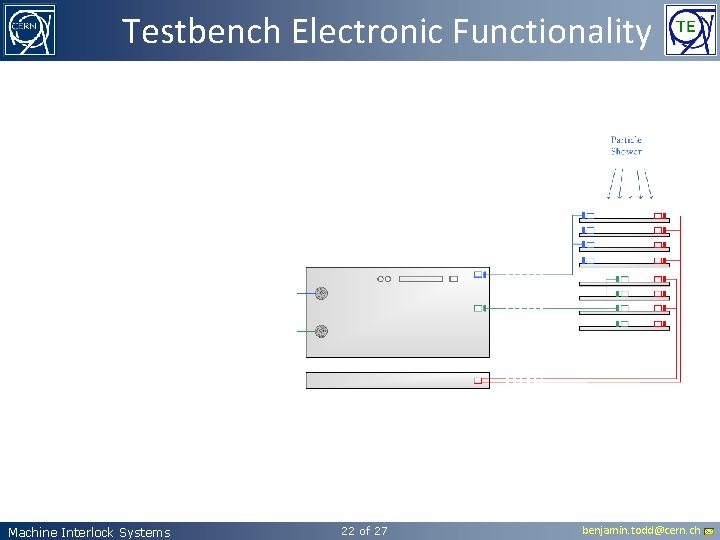

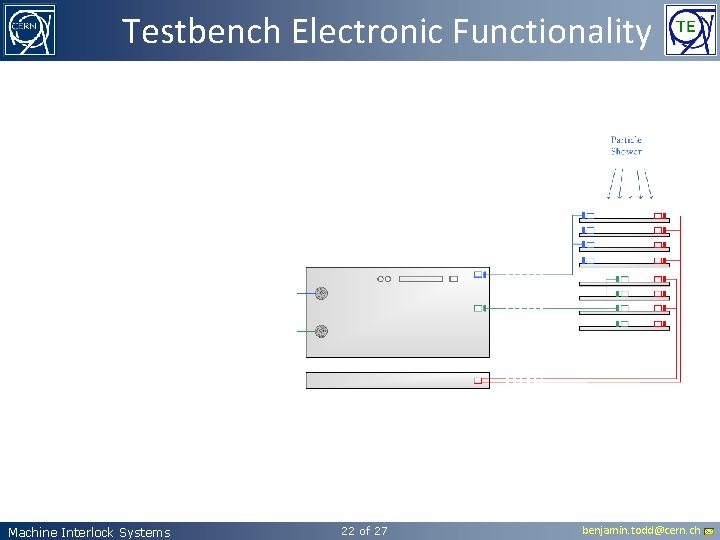

Testbench Electronic Functionality Machine Interlock Systems 22 of 27 benjamin. todd@cern. ch

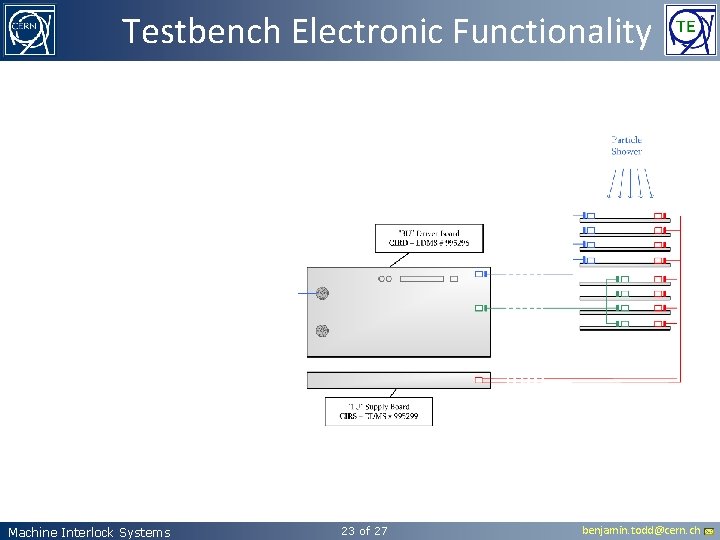

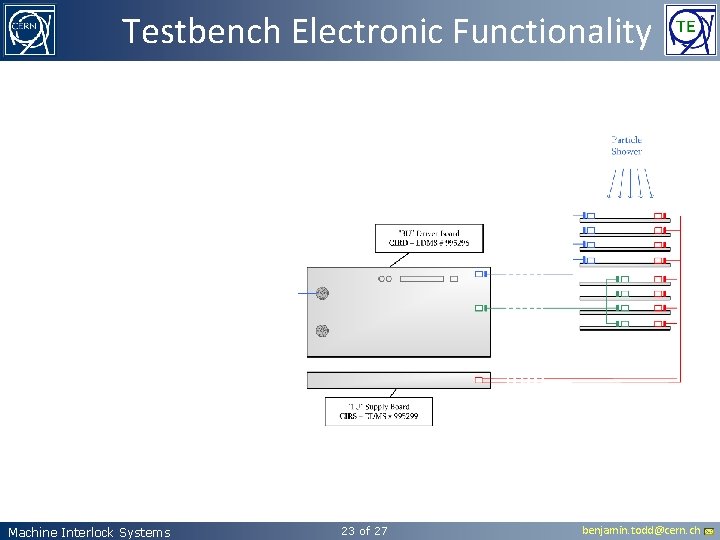

Testbench Electronic Functionality Machine Interlock Systems 23 of 27 benjamin. todd@cern. ch

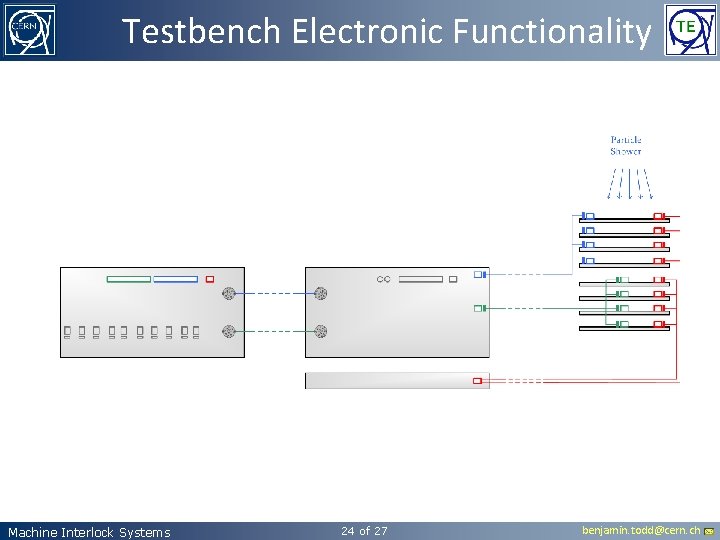

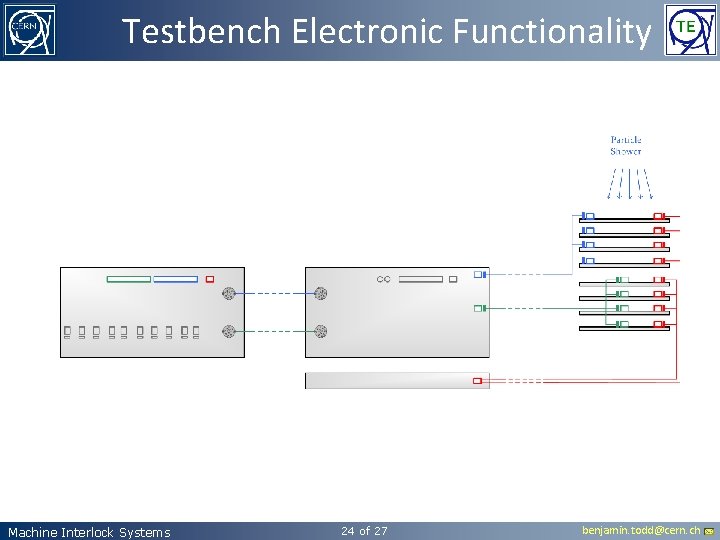

Testbench Electronic Functionality Machine Interlock Systems 24 of 27 benjamin. todd@cern. ch

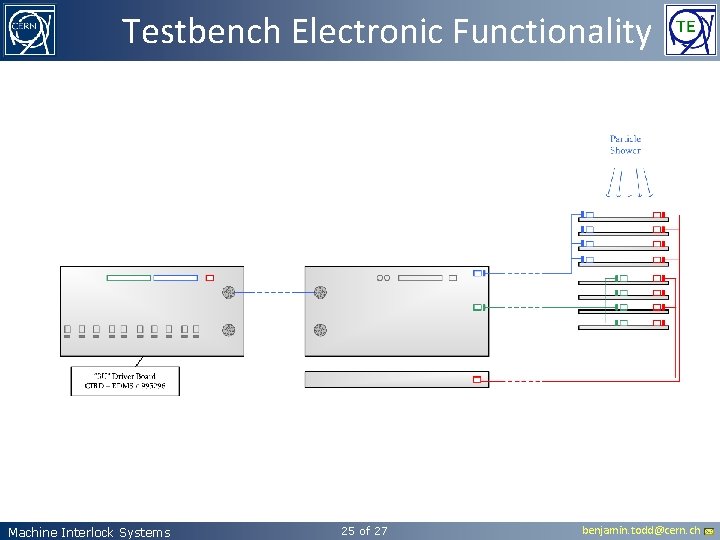

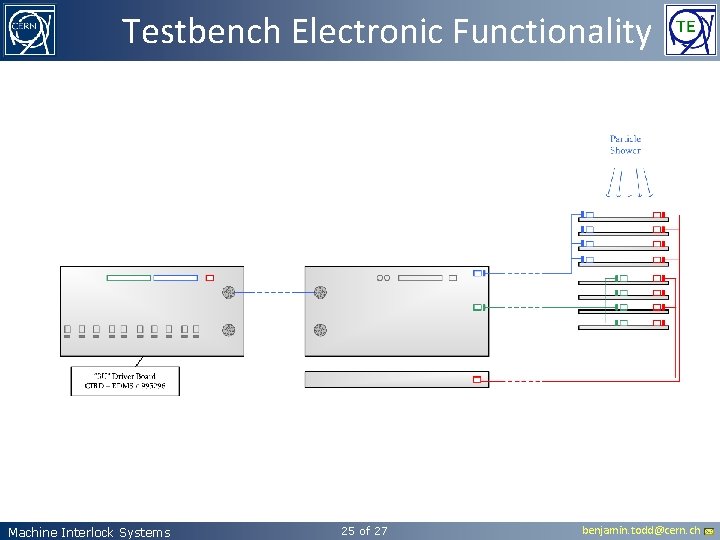

Testbench Electronic Functionality Machine Interlock Systems 25 of 27 benjamin. todd@cern. ch

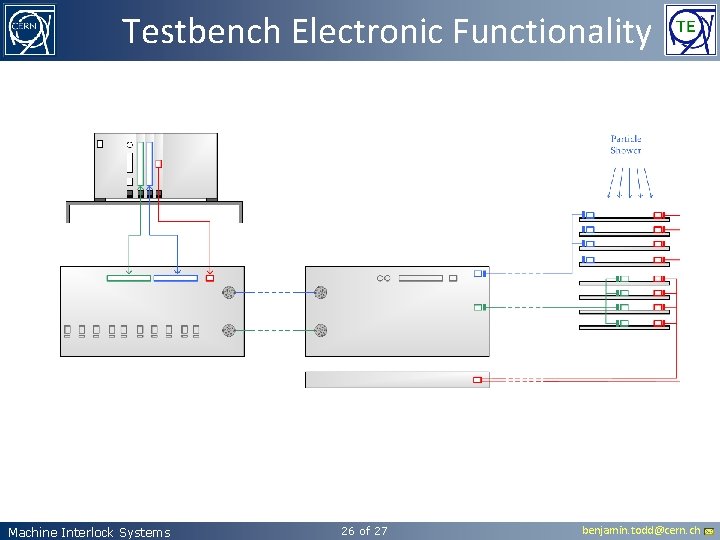

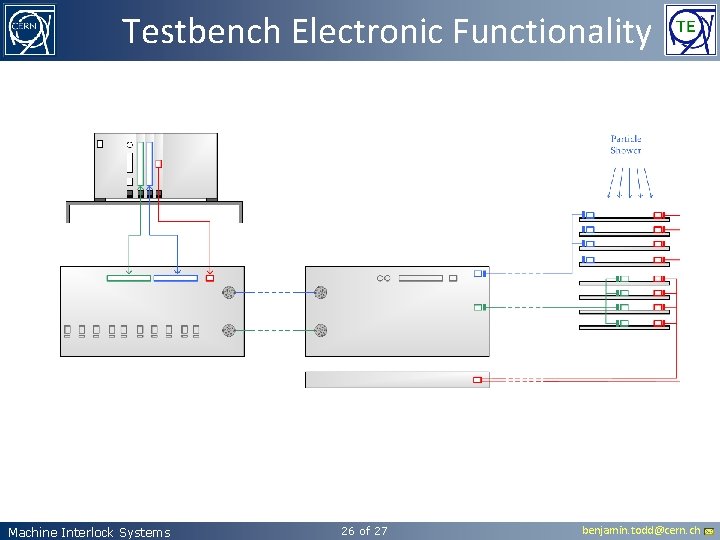

Testbench Electronic Functionality Machine Interlock Systems 26 of 27 benjamin. todd@cern. ch

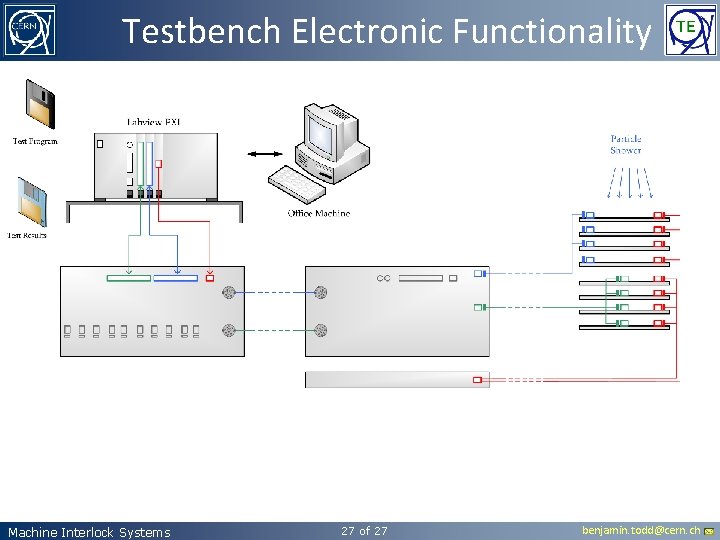

Testbench Electronic Functionality Machine Interlock Systems 27 of 27 benjamin. todd@cern. ch

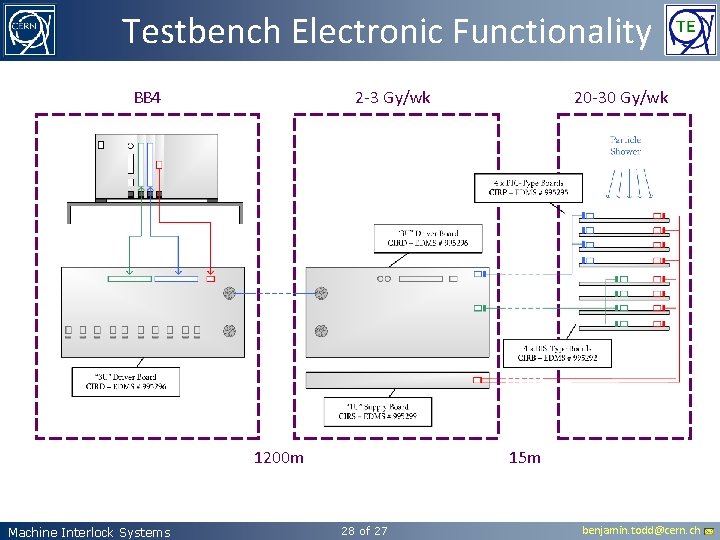

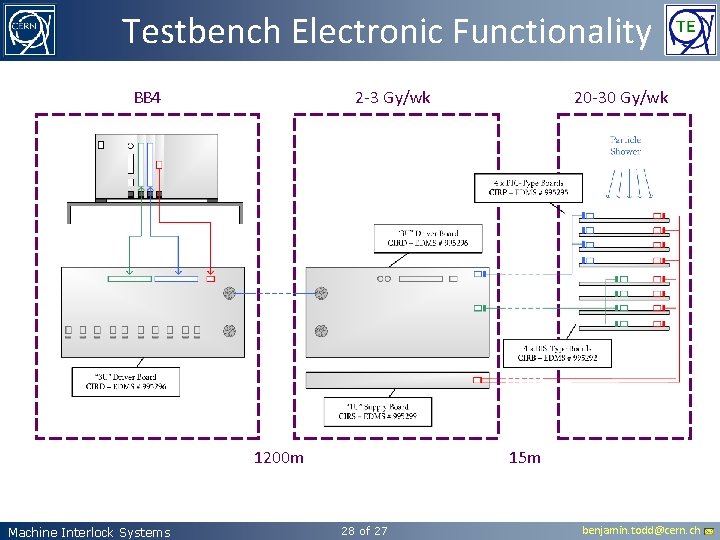

Testbench Electronic Functionality BB 4 2 -3 Gy/wk 1200 m Machine Interlock Systems 20 -30 Gy/wk 15 m 28 of 27 benjamin. todd@cern. ch

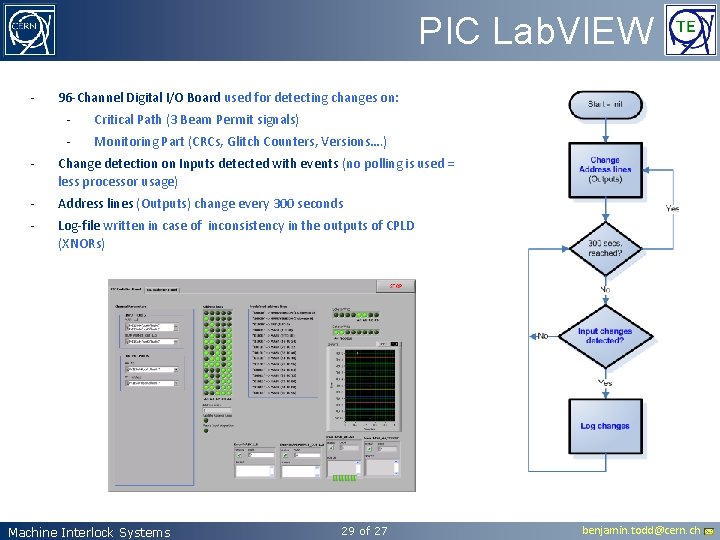

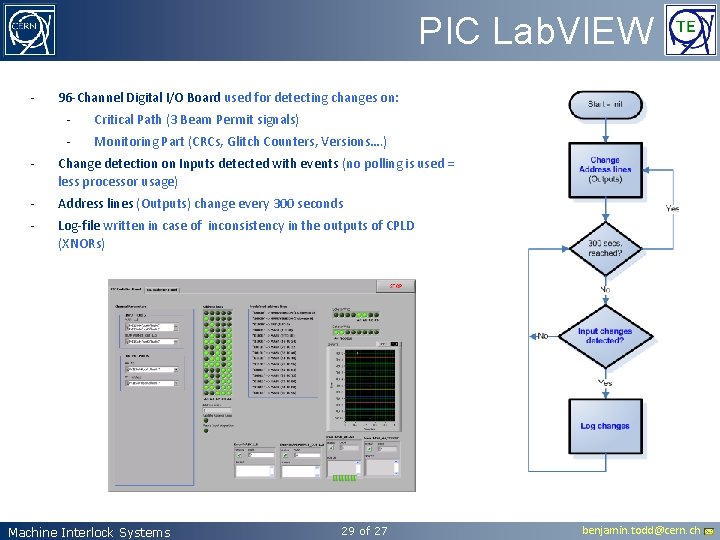

PIC Lab. VIEW - 96 -Channel Digital I/O Board used for detecting changes on: - Critical Path (3 Beam Permit signals) - Monitoring Part (CRCs, Glitch Counters, Versions…. ) - Change detection on Inputs detected with events (no polling is used = less processor usage) - Address lines (Outputs) change every 300 seconds - Log-file written in case of inconsistency in the outputs of CPLD (XNORs) Machine Interlock Systems 29 of 27 benjamin. todd@cern. ch

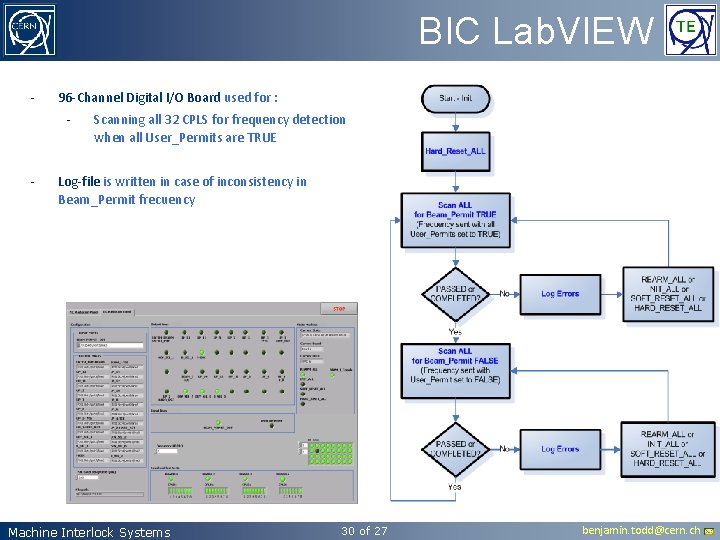

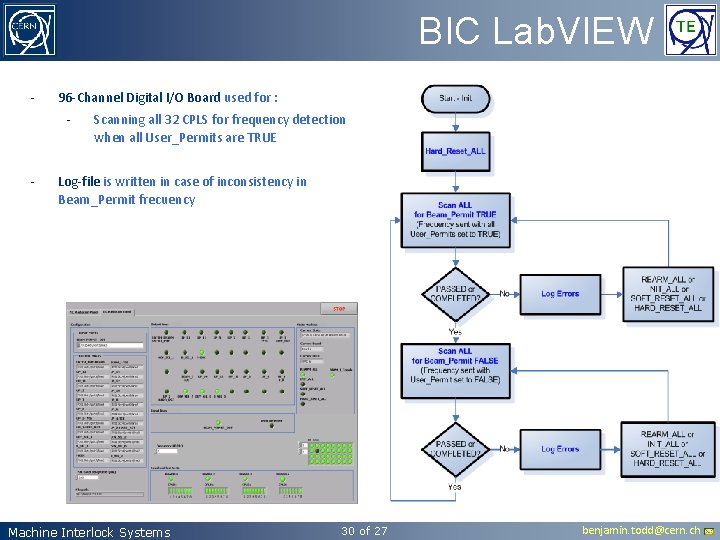

BIC Lab. VIEW - 96 -Channel Digital I/O Board used for : - - Scanning all 32 CPLS for frequency detection when all User_Permits are TRUE Log-file is written in case of inconsistency in Beam_Permit frecuency Machine Interlock Systems 30 of 27 benjamin. todd@cern. ch

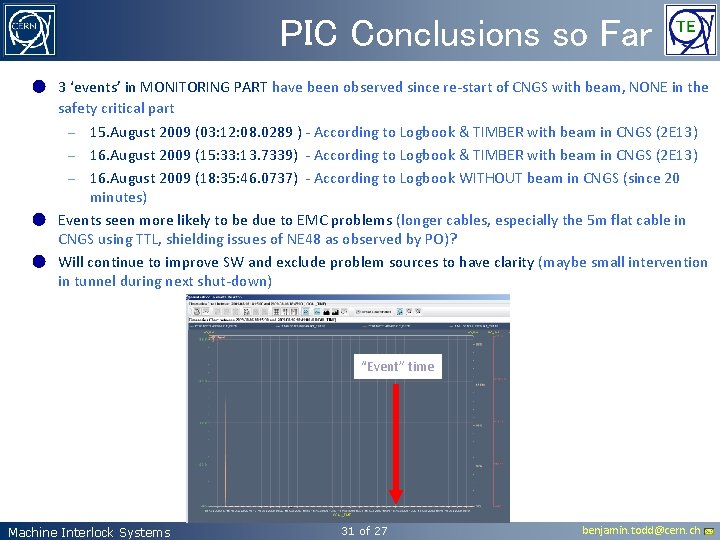

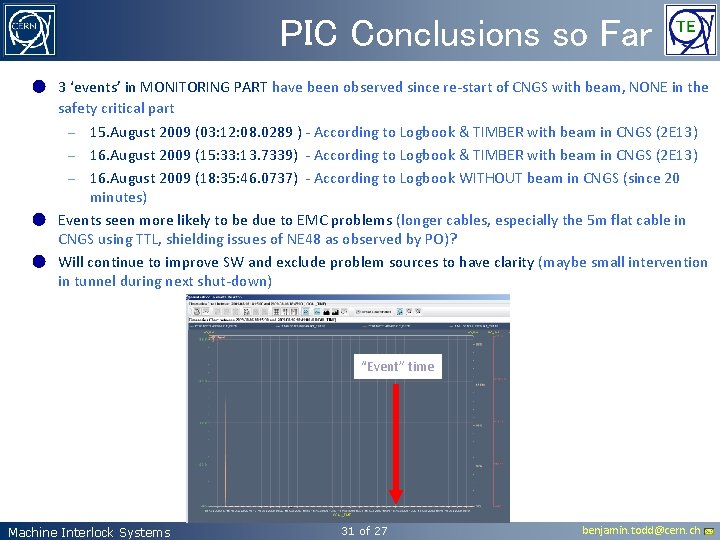

PIC Conclusions so Far ● 3 ‘events’ in MONITORING PART have been observed since re-start of CNGS with beam, NONE in the safety critical part – 15. August 2009 (03: 12: 08. 0289 ) - According to Logbook & TIMBER with beam in CNGS (2 E 13) – 16. August 2009 (15: 33: 13. 7339) - According to Logbook & TIMBER with beam in CNGS (2 E 13) – 16. August 2009 (18: 35: 46. 0737) - According to Logbook WITHOUT beam in CNGS (since 20 minutes) ● Events seen more likely to be due to EMC problems (longer cables, especially the 5 m flat cable in CNGS using TTL, shielding issues of NE 48 as observed by PO)? ● Will continue to improve SW and exclude problem sources to have clarity (maybe small intervention in tunnel during next shut-down) “Event” time Machine Interlock Systems 31 of 27 benjamin. todd@cern. ch

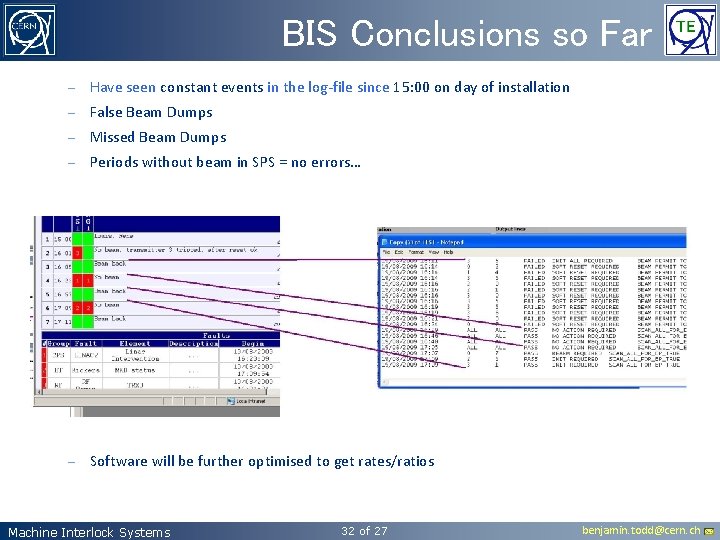

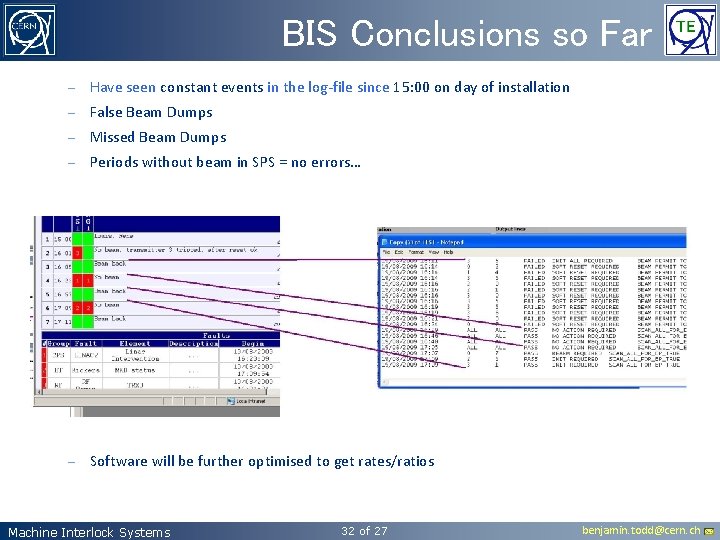

BIS Conclusions so Far – Have seen constant events in the log-file since 15: 00 on day of installation – False Beam Dumps – Missed Beam Dumps – Periods without beam in SPS = no errors… – Software will be further optimised to get rates/ratios Machine Interlock Systems 32 of 27 benjamin. todd@cern. ch

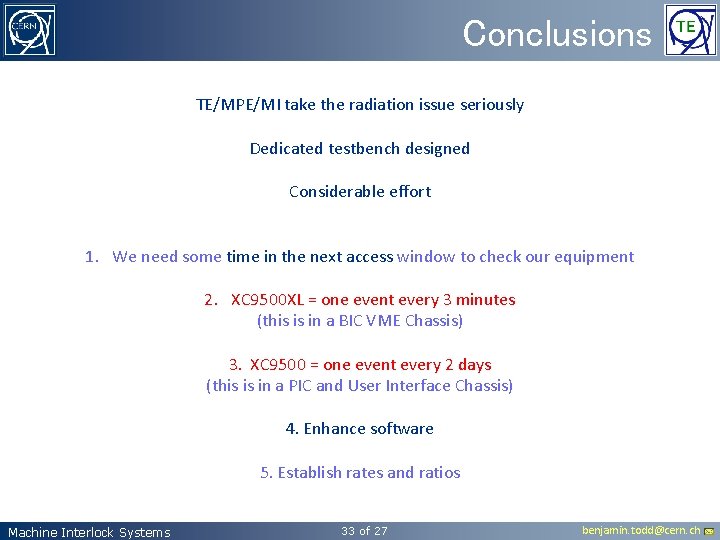

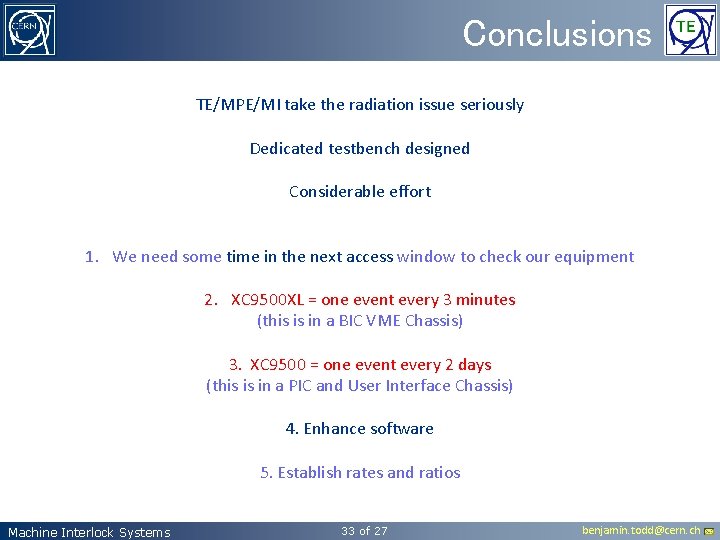

Conclusions TE/MPE/MI take the radiation issue seriously Dedicated testbench designed Considerable effort 1. We need some time in the next access window to check our equipment 2. XC 9500 XL = one event every 3 minutes (this is in a BIC VME Chassis) 3. XC 9500 = one event every 2 days (this is in a PIC and User Interface Chassis) 4. Enhance software 5. Establish rates and ratios Machine Interlock Systems 33 of 27 benjamin. todd@cern. ch

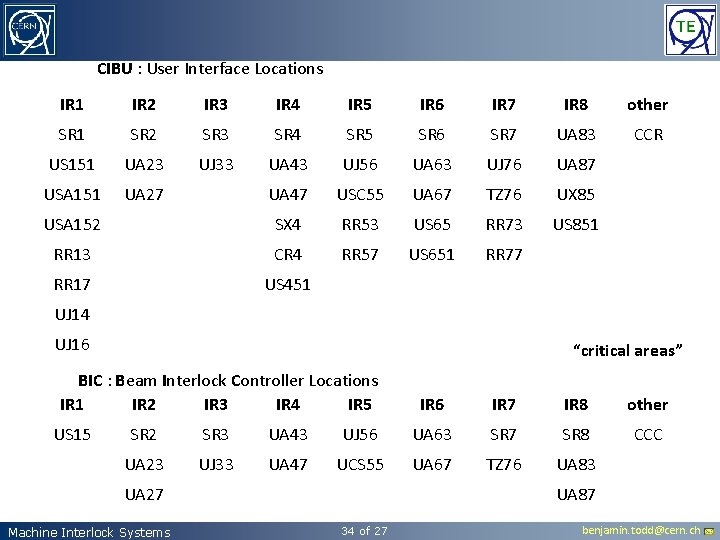

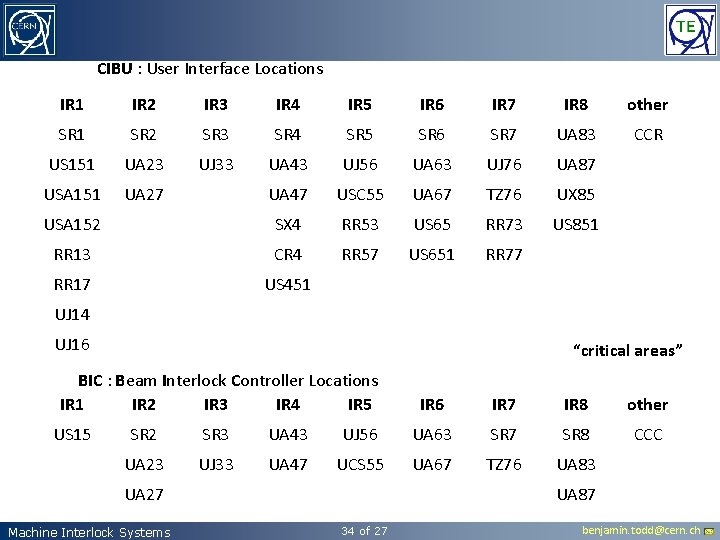

CIBU : User Interface Locations IR 1 IR 2 IR 3 IR 4 IR 5 IR 6 IR 7 IR 8 other SR 1 SR 2 SR 3 SR 4 SR 5 SR 6 SR 7 UA 83 CCR US 151 UA 23 UJ 33 UA 43 UJ 56 UA 63 UJ 76 UA 87 USA 151 UA 27 UA 47 USC 55 UA 67 TZ 76 UX 85 USA 152 SX 4 RR 53 US 65 RR 73 US 851 RR 13 CR 4 RR 57 US 651 RR 77 RR 17 US 451 UJ 14 UJ 16 “critical areas” BIC : Beam Interlock Controller Locations IR 1 IR 2 IR 3 IR 4 IR 5 US 15 IR 6 IR 7 IR 8 other CCC SR 2 SR 3 UA 43 UJ 56 UA 63 SR 7 SR 8 UA 23 UJ 33 UA 47 UCS 55 UA 67 TZ 76 UA 83 UA 27 Machine Interlock Systems UA 87 34 of 27 benjamin. todd@cern. ch

FIN Machine Interlock Systems 35 of 27 benjamin. todd@cern. ch

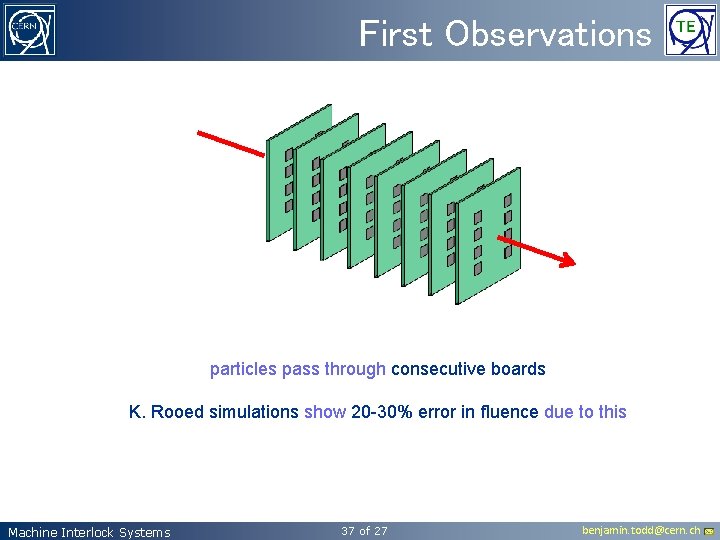

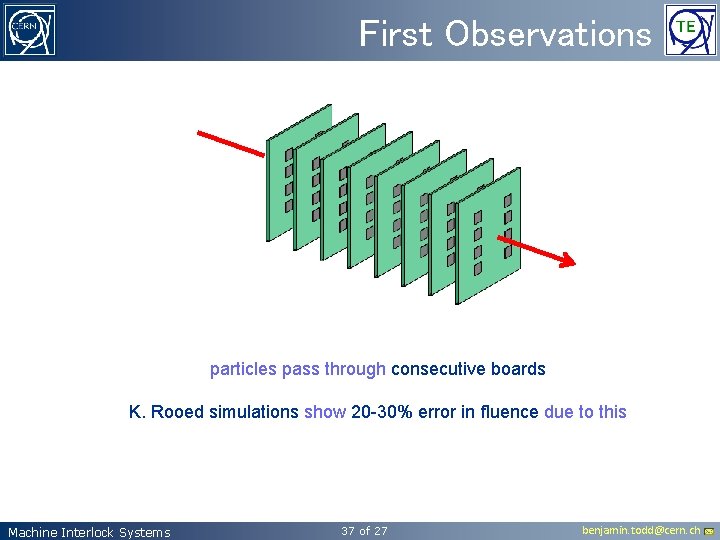

First Observations particles pass through consecutive boards K. Rooed simulations show 20 -30% error in fluence due to this Machine Interlock Systems 37 of 27 benjamin. todd@cern. ch