XC 9500 XL New 3 3 v ISP

- Slides: 20

XC 9500 XL New 3. 3 v ISP CPLDs

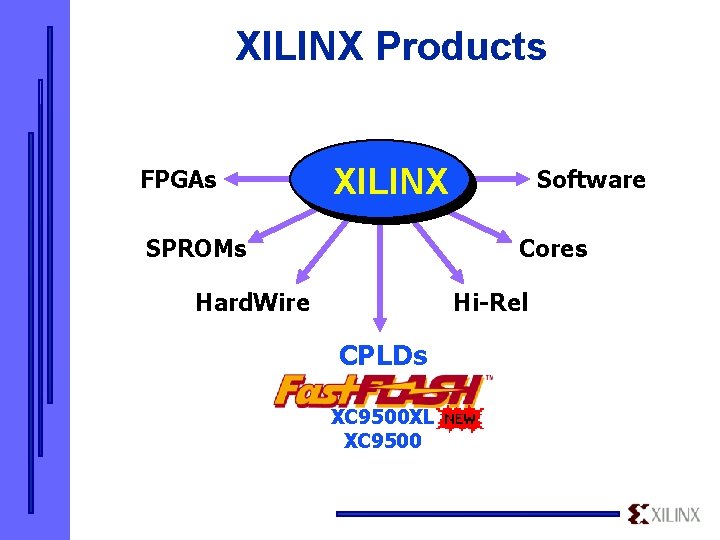

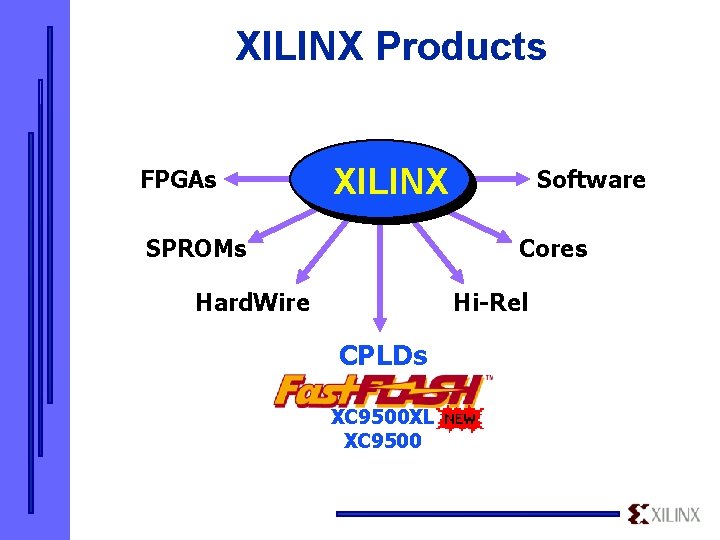

XILINX Products FPGAs XILINX SPROMs Software Cores Hard. Wire Hi-Rel CPLDs XC 9500 XL XC 9500

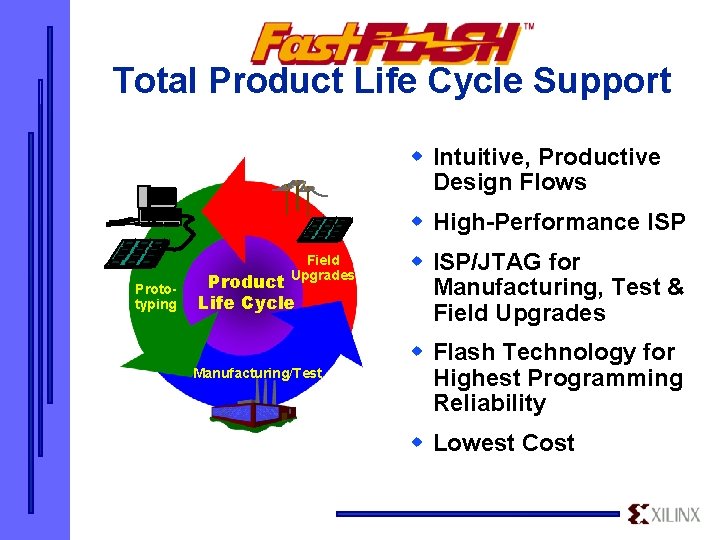

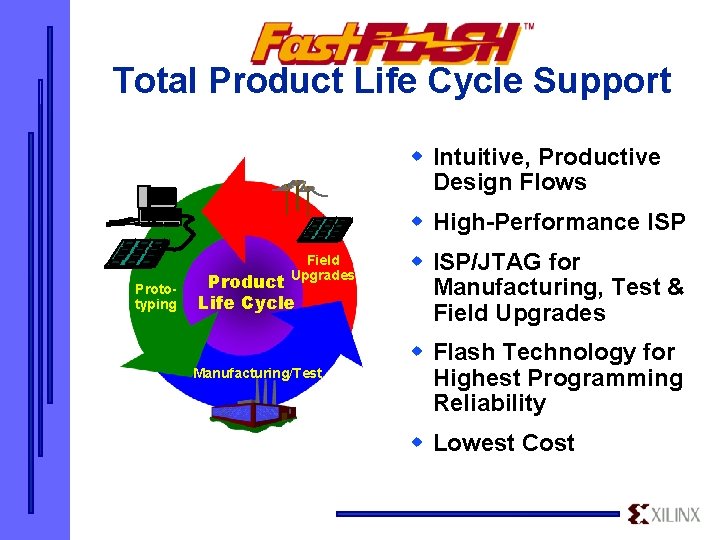

Total Product Life Cycle Support w Intuitive, Productive Design Flows w High-Performance ISP Prototyping Field Upgrades Product Life Cycle Manufacturing/Test w ISP/JTAG for Manufacturing, Test & Field Upgrades w Flash Technology for Highest Programming Reliability w Lowest Cost

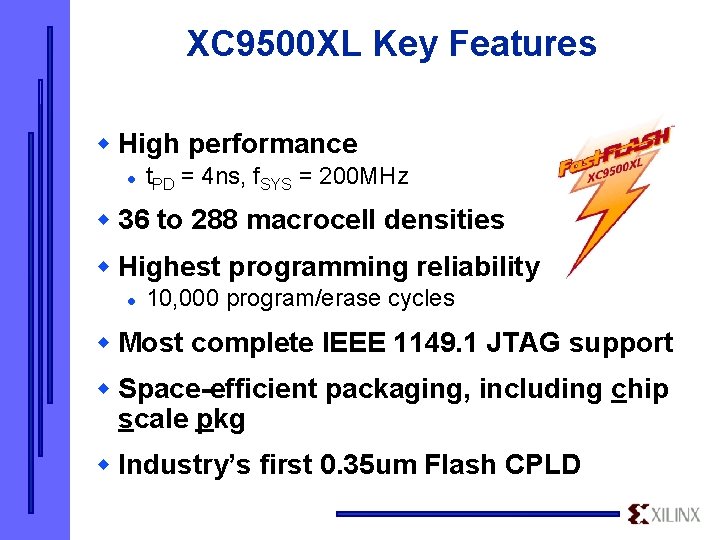

XC 9500 XL Key Features w High performance l t. PD = 4 ns, f. SYS = 200 MHz w 36 to 288 macrocell densities w Highest programming reliability l 10, 000 program/erase cycles w Most complete IEEE 1149. 1 JTAG support w Space-efficient packaging, including chip scale pkg w Industry’s first 0. 35 um Flash CPLD

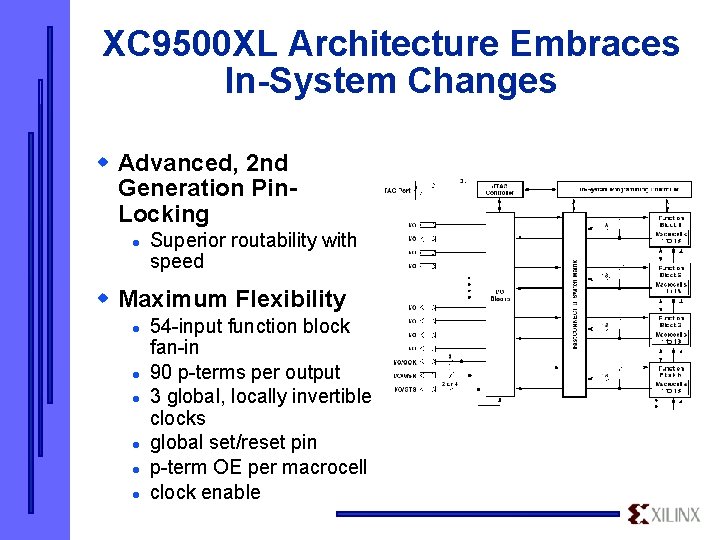

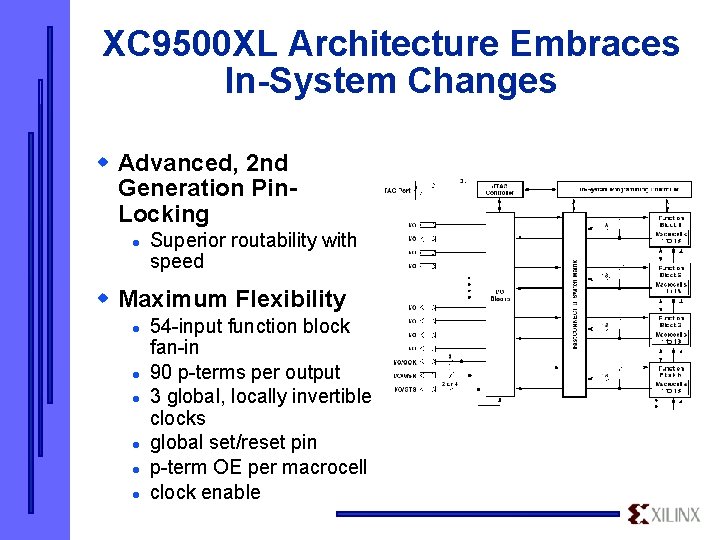

XC 9500 XL Architecture Embraces In-System Changes w Advanced, 2 nd Generation Pin. Locking l Superior routability with speed w Maximum Flexibility l l l 54 -input function block fan-in 90 p-terms per output 3 global, locally invertible clocks global set/reset pin p-term OE per macrocell clock enable

XC 9500 XL System Features w I/O Flexibility l 5 v tolerant; direct interface to 3. 3 v & 2. 5 v w Input hysteresis on all pins w User programmable grounds w Bus hold circuitry for simple bus interface w Easy ATE integration for ISP & JTAG l fast, concurrent programming times

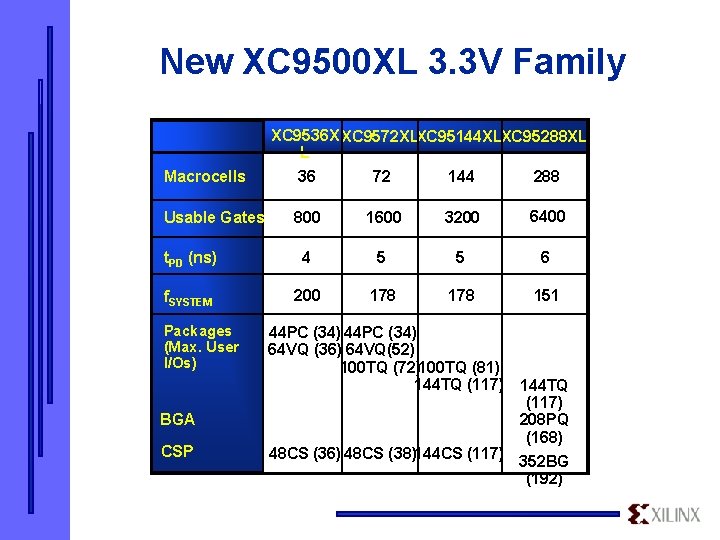

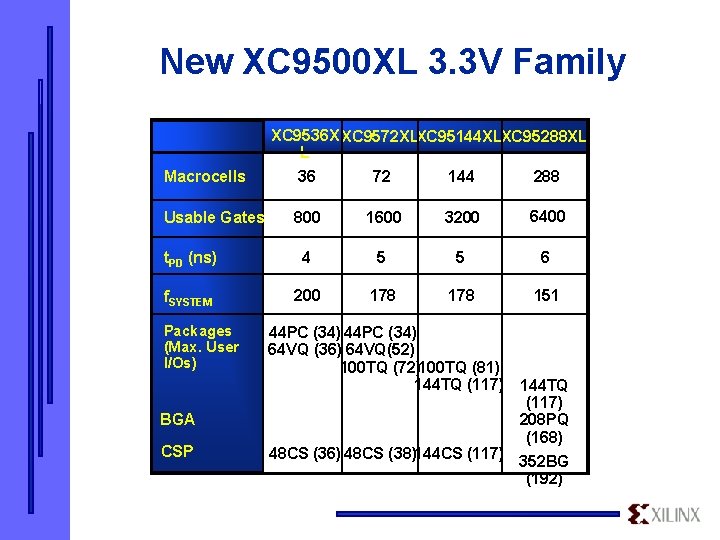

New XC 9500 XL 3. 3 V Family Macrocells XC 9536 X XC 9572 XLXC 95144 XLXC 95288 XL L 288 36 72 144 800 1600 3200 6400 t. PD (ns) 4 5 5 6 f. SYSTEM 200 178 151 Usable Gates Packages (Max. User I/Os) BGA CSP 44 PC (34) 64 VQ (36) 64 VQ(52) 100 TQ (72)100 TQ (81) 144 TQ (117) 208 PQ (168) 48 CS (36) 48 CS (38)144 CS (117) 352 BG (192)

XC 9500 XL Supports High-Speed Applications w Fast decode logic l DSP, SDRAM, CPU w High-frequency state machines l bus arbiter, data path controller w Leading-edge systems l l l networking graphics workstations

Most Complete JTAG Testability w IEEE Std 1149. 1 boundary-scan l l testability & advanced system debug/diagnosis 8 instructions supported (incl. CLAMP) w Full support on all family members w Industry-standard ISP interface w Complete 3 rd party support

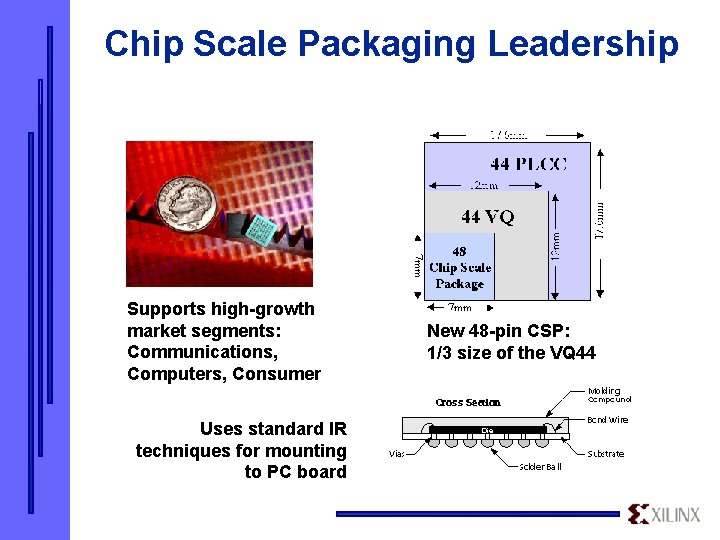

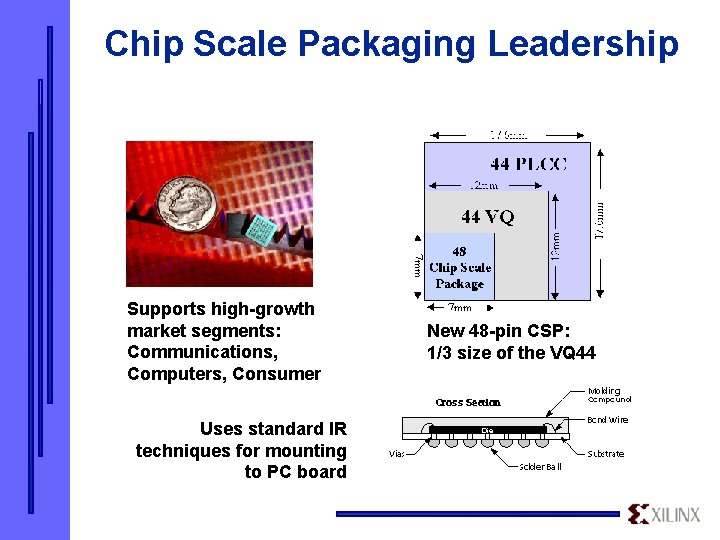

Chip Scale Packaging Leadership Supports high-growth market segments: Communications, Computers, Consumer Uses standard IR techniques for mounting to PC board New 48 -pin CSP: 1/3 size of the VQ 44

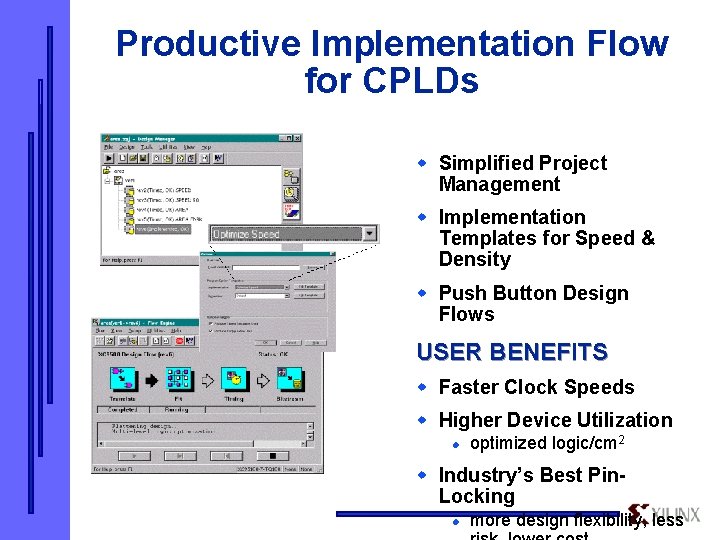

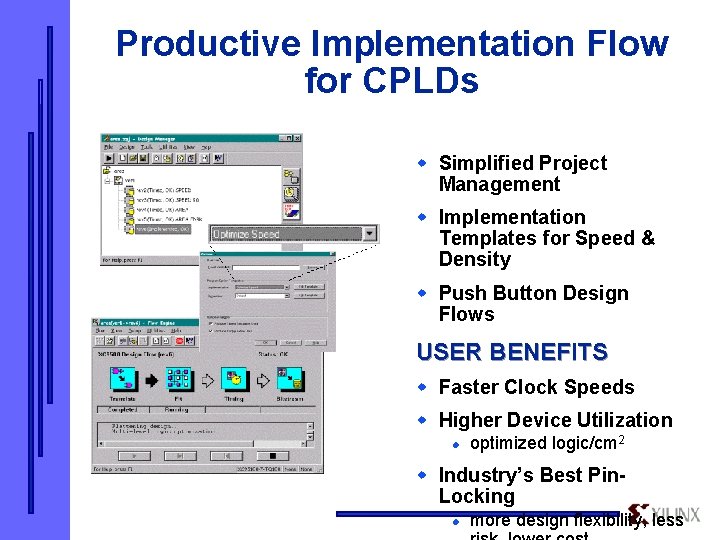

Productive Implementation Flow for CPLDs w Simplified Project Management w Implementation Templates for Speed & Density w Push Button Design Flows USER BENEFITS w Faster Clock Speeds w Higher Device Utilization l optimized logic/cm 2 w Industry’s Best Pin. Locking l more design flexibility, less

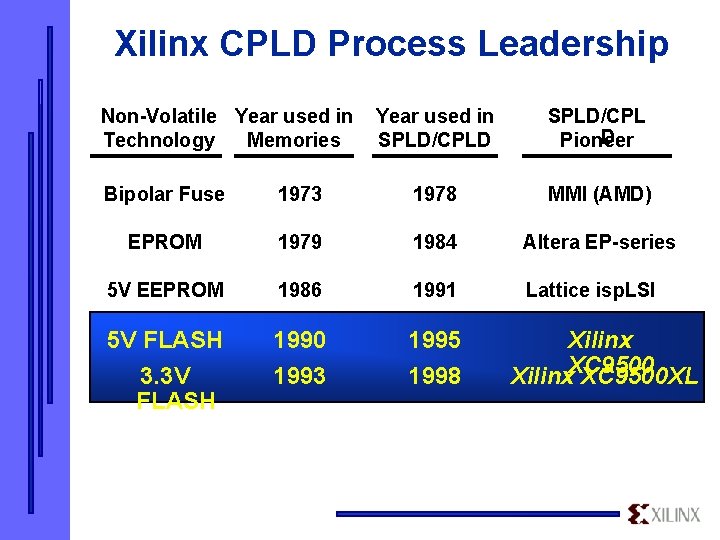

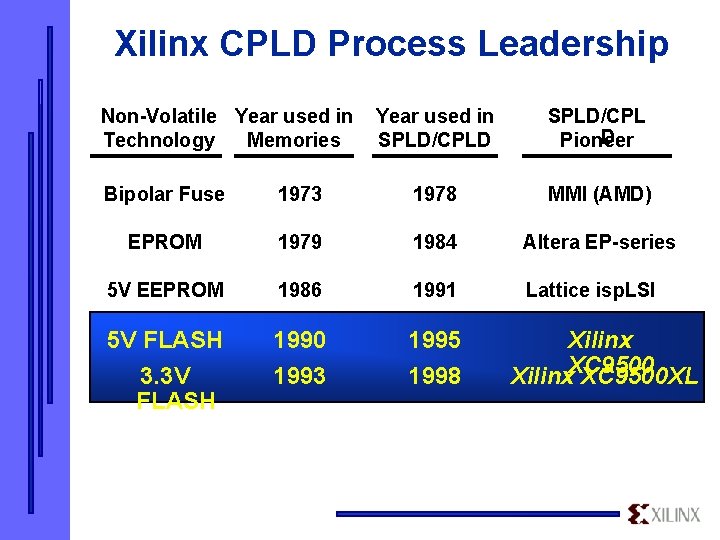

Xilinx CPLD Process Leadership Non-Volatile Year used in Technology Memories Year used in SPLD/CPLD SPLD/CPL D Pioneer Bipolar Fuse 1973 1978 MMI (AMD) EPROM 1979 1984 Altera EP-series 5 V EEPROM 1986 1991 Lattice isp. LSI 5 V FLASH 3. 3 V FLASH 1990 1993 1995 1998 Xilinx. XC 9500 XL

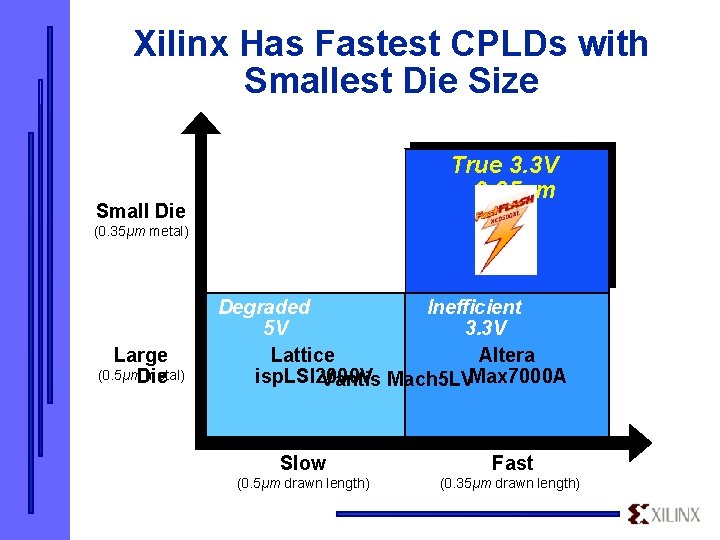

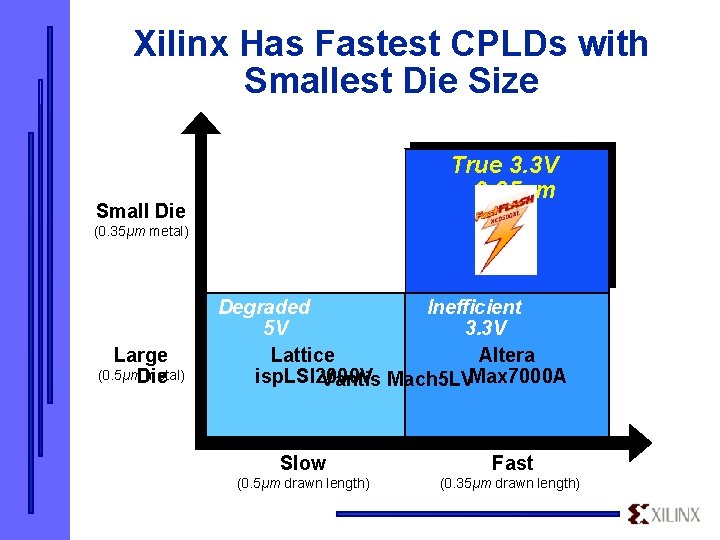

Xilinx Has Fastest CPLDs with Smallest Die Size True 3. 3 V 0. 35µm Small Die (0. 35µm metal) Large (0. 5µm. Die metal) Degraded Inefficient 5 V 3. 3 V Lattice Altera isp. LSI 2000 V Vantis Mach 5 LVMax 7000 A Slow Fast (0. 5µm drawn length) (0. 35µm drawn length)

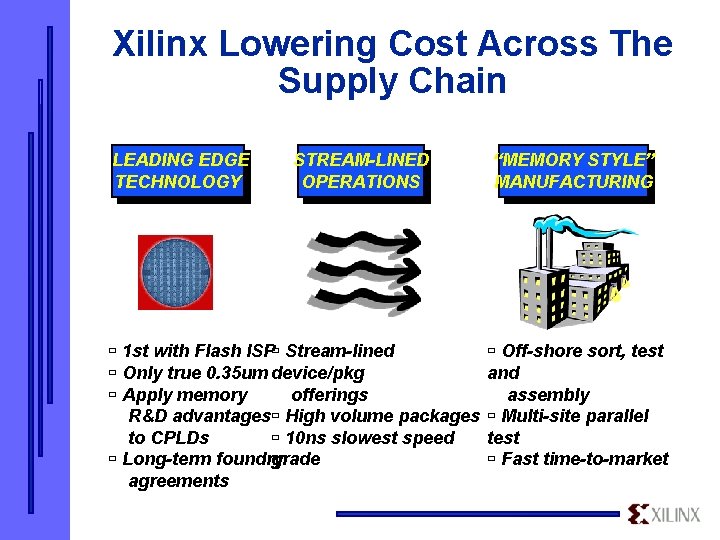

Xilinx Lowering Cost Across The Supply Chain LEADING EDGE TECHNOLOGY STREAM-LINED OPERATIONS ù 1 st with Flash ISPù Stream-lined ù Only true 0. 35 um device/pkg ù Apply memory offerings R&D advantagesù High volume packages to CPLDs ù 10 ns slowest speed ù Long-term foundry grade agreements “MEMORY STYLE” MANUFACTURING ù Off-shore sort, test and assembly ù Multi-site parallel test ù Fast time-to-market

New Price Points Open Up New CPLD Applications w Motherboards for PCs and servers w PC peripherals and add-on cards l l DVD players/controller cards Graphics cards w Automotive l l Engine control Automotive navigation systems (GPS) w Consumer l l Coffeemakers Video Games/Toys

XC 9500 XL The Complete CPLD Solution w Product Life Cycle Support w Flexible 3. 3 v ISP Architecture w New Leadership Features w Productive Software w Lowest Cost Solution

XC 9500 XL Appendix

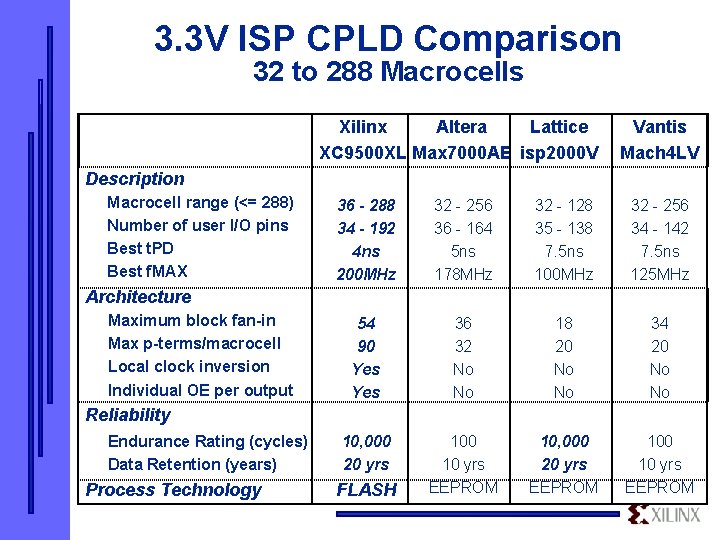

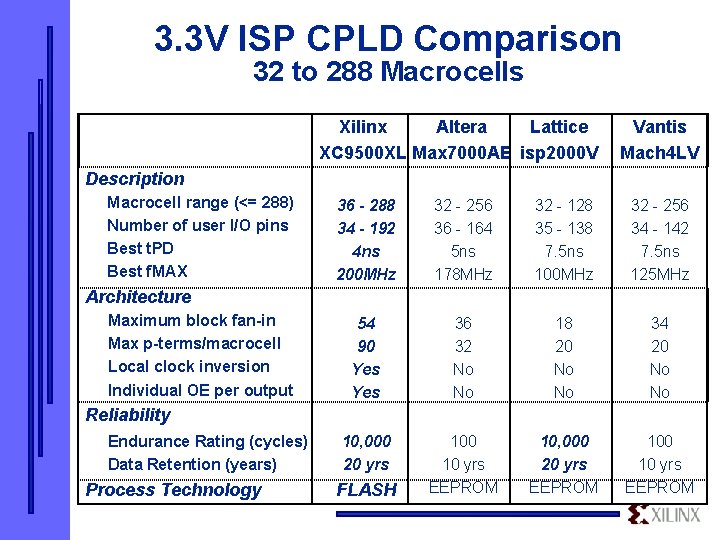

3. 3 V ISP CPLD Comparison 32 to 288 Macrocells Xilinx Altera Lattice XC 9500 XL Max 7000 AE isp 2000 V Vantis Mach 4 LV Description Macrocell range (<= 288) Number of user I/O pins Best t. PD Best f. MAX 36 - 288 34 - 192 4 ns 200 MHz 32 - 256 36 - 164 5 ns 178 MHz 32 - 128 35 - 138 7. 5 ns 100 MHz 32 - 256 34 - 142 7. 5 ns 125 MHz 54 90 Yes 36 32 No No 18 20 No No 34 20 No No 10, 000 20 yrs 100 10 yrs EEPROM 10, 000 20 yrs EEPROM 100 10 yrs EEPROM Architecture Maximum block fan-in Max p-terms/macrocell Local clock inversion Individual OE per output Reliability Endurance Rating (cycles) Data Retention (years) Process Technology FLASH

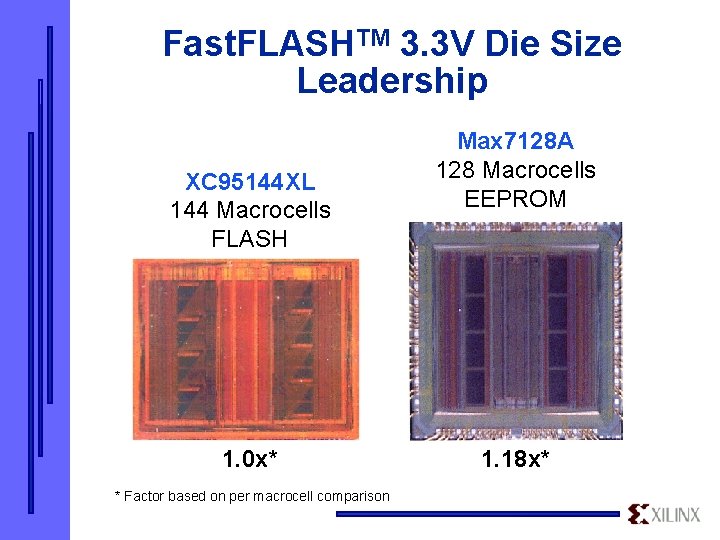

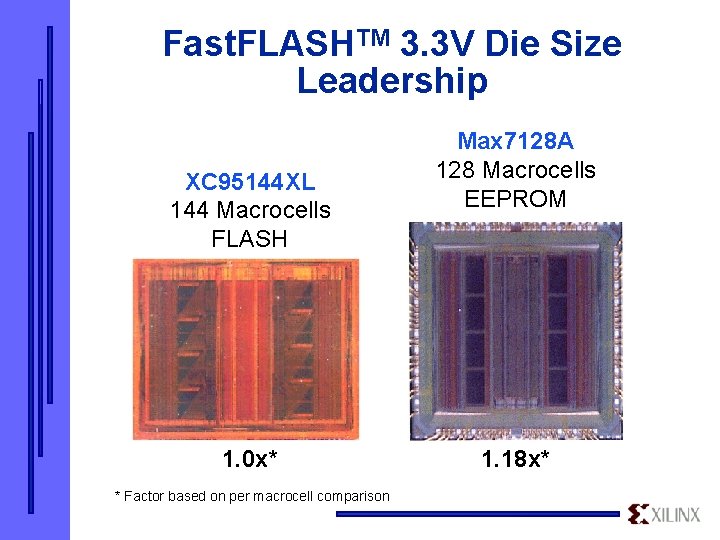

Fast. FLASHTM 3. 3 V Die Size Leadership XC 95144 XL 144 Macrocells FLASH 1. 0 x* * Factor based on per macrocell comparison Max 7128 A 128 Macrocells EEPROM 1. 18 x*

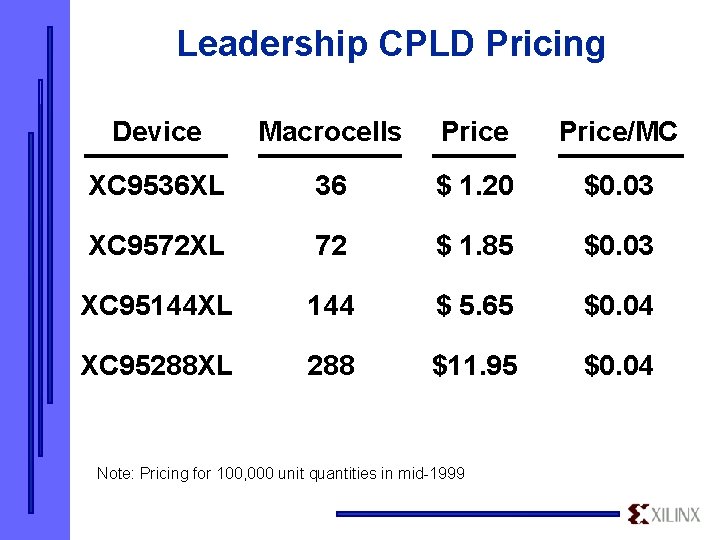

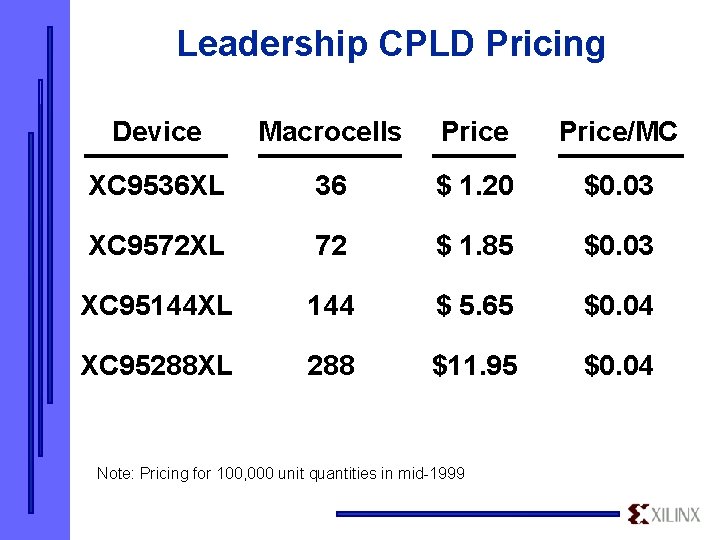

Leadership CPLD Pricing Device Macrocells Price/MC XC 9536 XL 36 $ 1. 20 $0. 03 XC 9572 XL 72 $ 1. 85 $0. 03 XC 95144 XL 144 $ 5. 65 $0. 04 XC 95288 XL 288 $11. 95 $0. 04 Note: Pricing for 100, 000 unit quantities in mid-1999