XC 9500 XL Architecture CPLD Product Applications TIBarch

XC 9500 XL Architecture CPLD Product Applications TIB_arch. B 1

XC 9500 XL Overview w Superset of XC 9500 CPLD w Optimized for 3. 3 V systems — compatible levels with 5. 0/2. 5 V w High f. MAX = 200 MHz w Fast t. PD = 4 nsec w Best ISP/JTAG support w Best pinlocking w Advanced Packaging TIB_arch. B 1

Agenda w Overview w Technology w Architecture w ISP w Electrical Compatibility w Support w Family TIB_arch. B 1

Features Each macrocell independently selects clock source and phase inversion Clock enable at each macrocell Hysteresis on all inputs Pullup/Bus Hold Option on Pins at power on Expanded Function Block Inputs TIB_arch. B 1

Technology w 0. 35 micron Fast. FLASH technology w 4 Layers of Metal w Optimized for high speed 3. 3 V systems w Ideal for ISP CPLDs w Reprogramming Endurance = 10, 000 w Charge Retention = 20 years TIB_arch. B 1

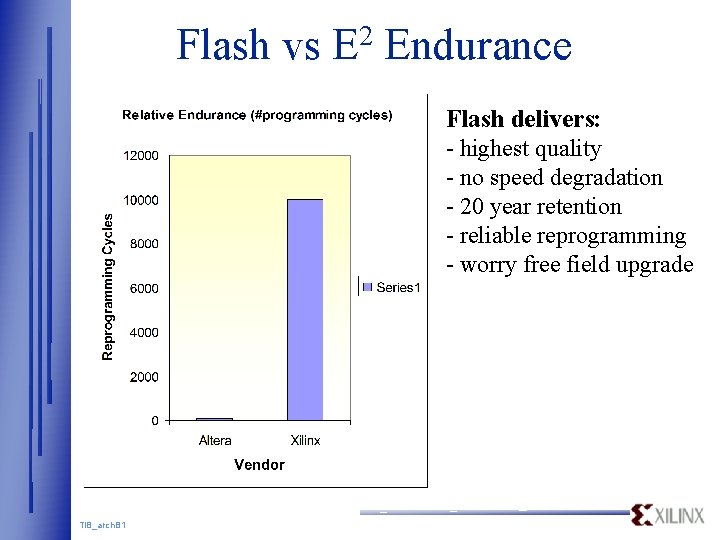

Flash vs E 2 Endurance Flash delivers: - highest quality - no speed degradation - 20 year retention - reliable reprogramming - worry free field upgrade TIB_arch. B 1

Architecture w Uniform w Identical Function Blocks w Identical Macrocells w Identical I/O pins w Abundant Global/Product Term Resources w Great synthesis results w Best pinlocking results TIB_arch. B 1

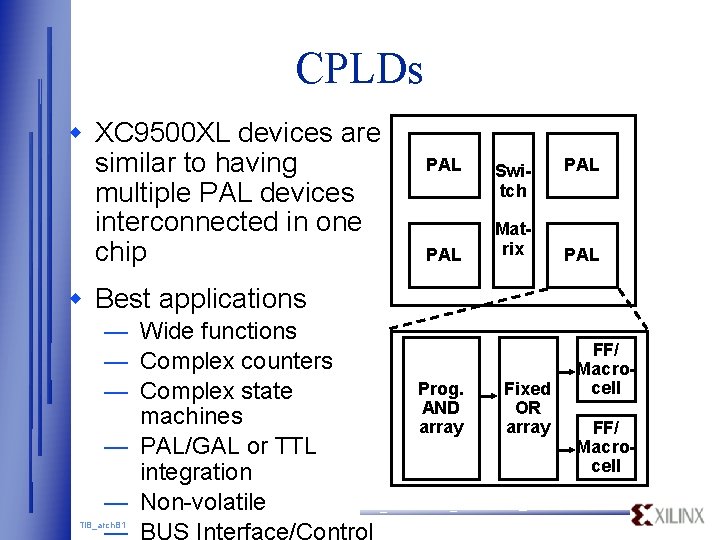

CPLDs w XC 9500 XL devices are similar to having multiple PAL devices interconnected in one chip PAL Switch Matrix PAL w Best applications — Wide functions — Complex counters — Complex state machines — PAL/GAL or TTL integration — Non-volatile — BUS Interface/Control TIB_arch. B 1 Prog. AND array Fixed OR array FF/ Macrocell

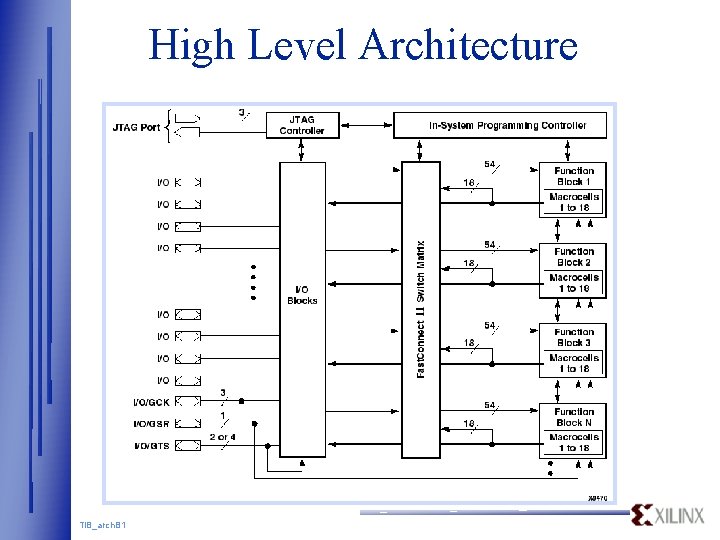

High Level Architecture TIB_arch. B 1

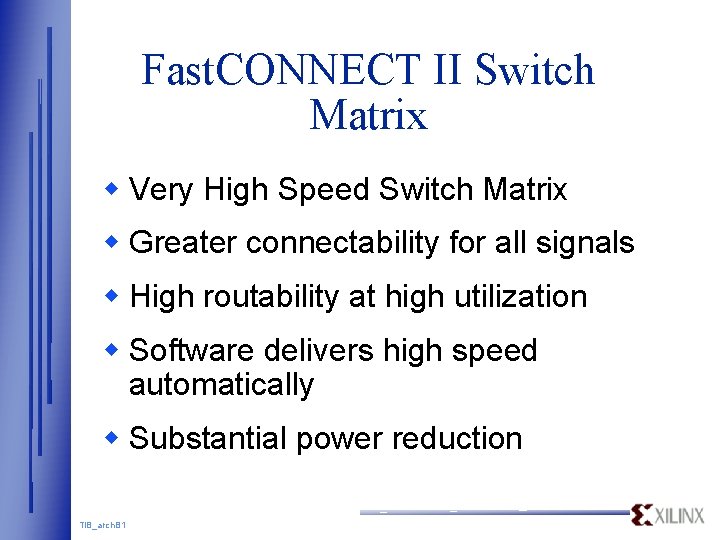

Fast. CONNECT II Switch Matrix w Very High Speed Switch Matrix w Greater connectability for all signals w High routability at high utilization w Software delivers high speed automatically w Substantial power reduction TIB_arch. B 1

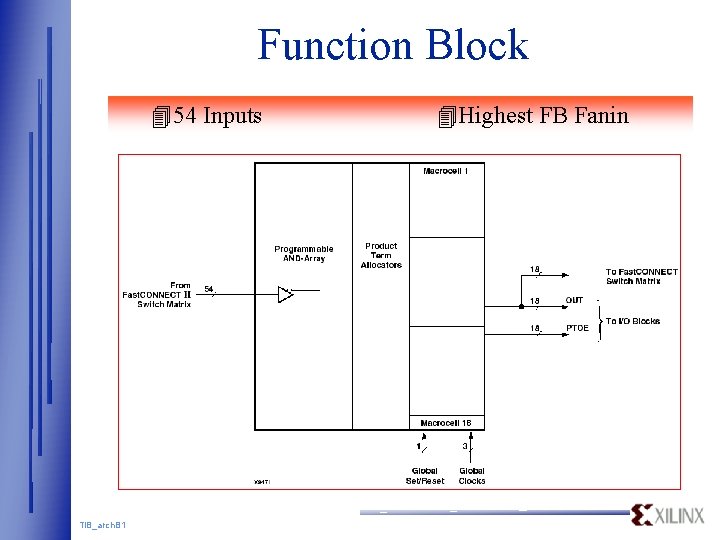

Function Block 54 Inputs TIB_arch. B 1 Highest FB Fanin

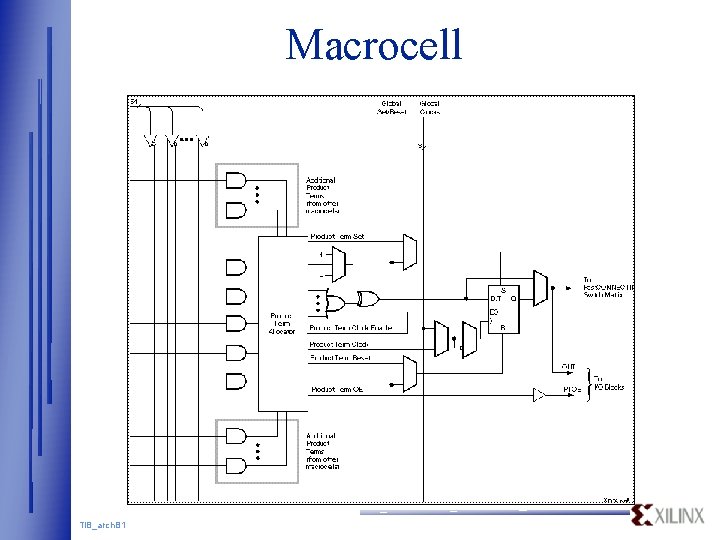

Macrocell TIB_arch. B 1

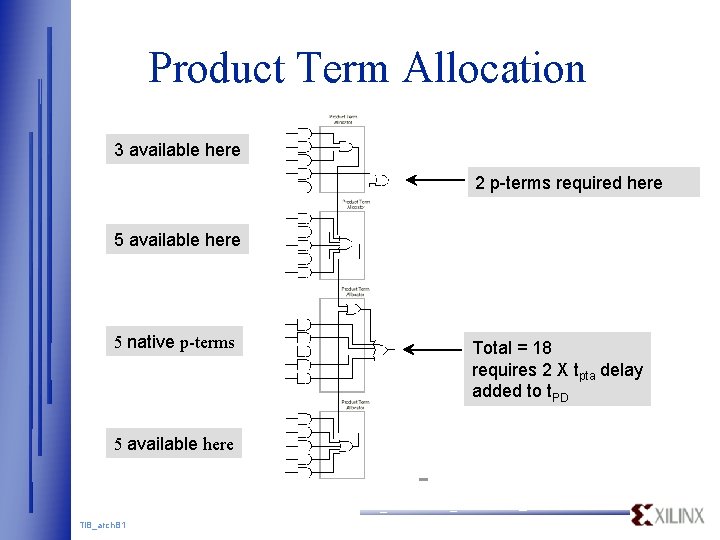

Product Term Allocation 3 available here 2 p-terms required here 5 available here 5 native p-terms 5 available here TIB_arch. B 1 Total = 18 requires 2 X tpta delay added to t. PD

Industry’s Best Pin-Locking w Product Term Allocator allows any product term to be borrowed by any macrocell in the same function block w Product Term Allocator allows for timing to be held for small to medium logic changes w Footprint compatibility allows for easy migration to larger or smaller devices using the same device package TIB_arch. B 1

Why Pin-Locking is Necessary w The major advantages of In System Programming can only be realized with field-upgrades w It does not make sense to do field upgrades if the board needs to be reworked for minor logic changes w It does not make sense to do field upgrades if timing cannot be met TIB_arch. B 1

Pin Locking vs Pin Preassignment w The software should be allowed to make first pass pin assignments w Pre-assigning pins can lead to timing and density underutilization TIB_arch. B 1

ISP w Original XC 9500 JTAG and ISP instructions: — Program Erase Blankcheck — ID Code Usercode — Intest Extest Verify Hi-Z Bypass w New instruction: — CLAMP — permits pin by pin definition of logic level during bypass w Added S/W support with XACT M 1. 5 TIB_arch. B 1

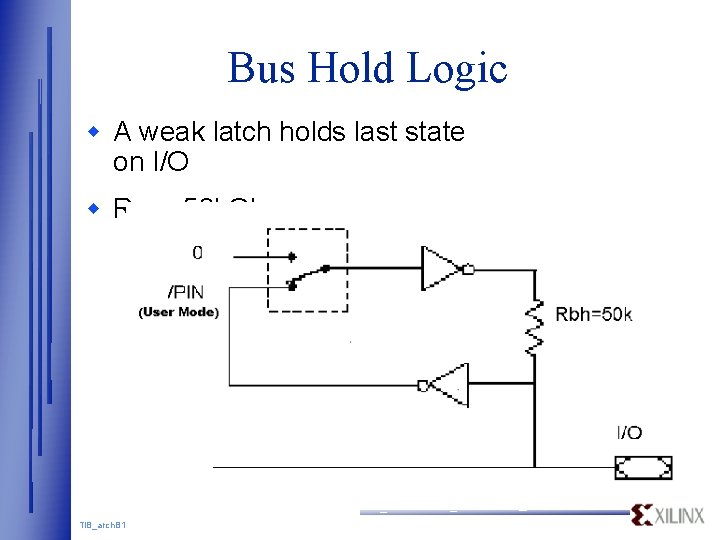

Bus Hold Logic w A weak latch holds last state on I/O w RBH= 50 k. Ohms TIB_arch. B 1

Bus Hold Logic w Two modes of operation — User mode: Holds last state — ISP or blank device: pull-up resistor w Better than just a pull-up resistor — eliminates slow changing of bus signals during hi-z — reduced system power during TIB_arch. B 1

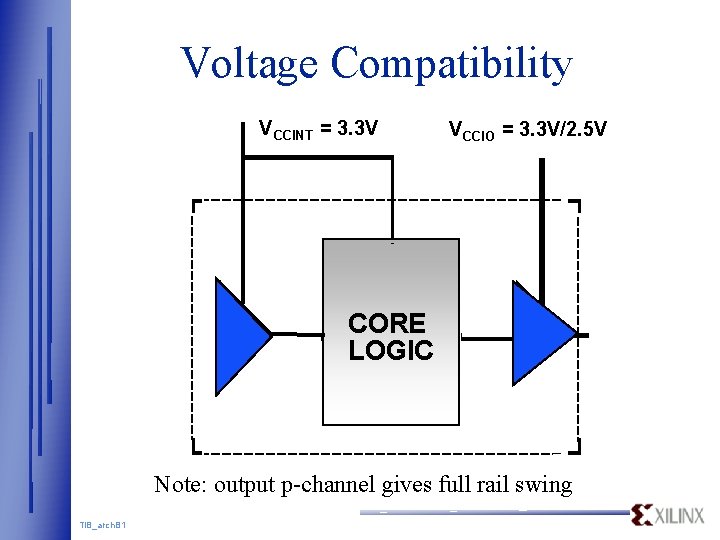

Voltage Compatibility VCCINT = 3. 3 V VCCIO = 3. 3 V/2. 5 V CORE LOGIC Note: output p-channel gives full rail swing TIB_arch. B 1

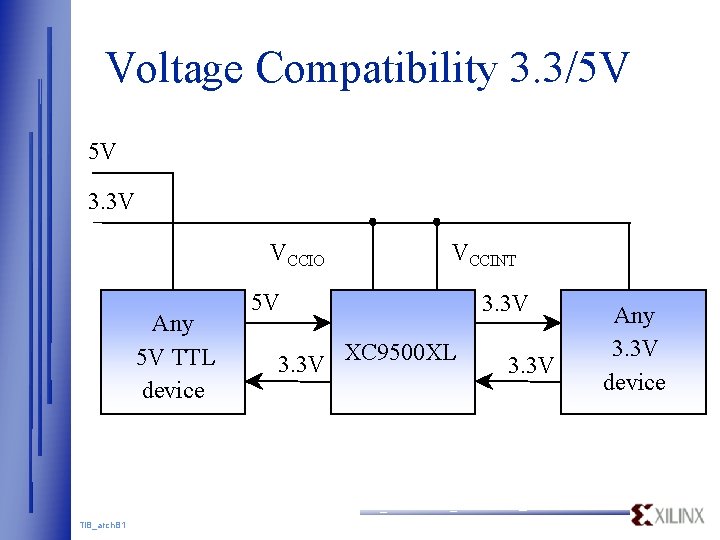

Voltage Compatibility 3. 3/5 V 5 V 3. 3 V VCCIO Any 5 V TTL device TIB_arch. B 1 VCCINT 5 V 3. 3 V XC 9500 XL 3. 3 V Any 3. 3 V device

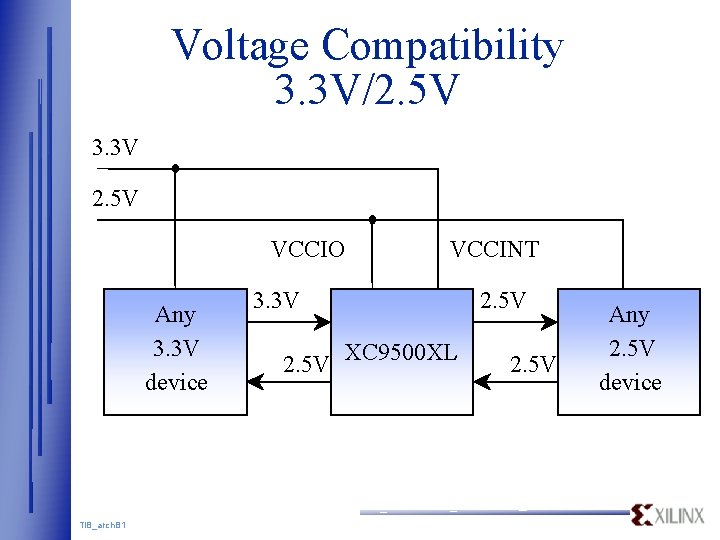

Voltage Compatibility 3. 3 V/2. 5 V 3. 3 V 2. 5 V VCCIO Any 3. 3 V device TIB_arch. B 1 VCCINT 3. 3 V 2. 5 V XC 9500 XL 2. 5 V Any 2. 5 V device

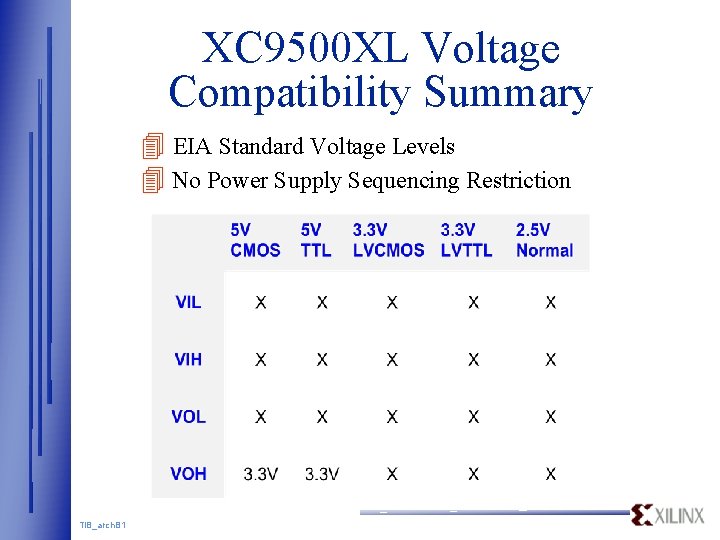

XC 9500 XL Voltage Compatibility Summary EIA Standard Voltage Levels No Power Supply Sequencing Restriction TIB_arch. B 1

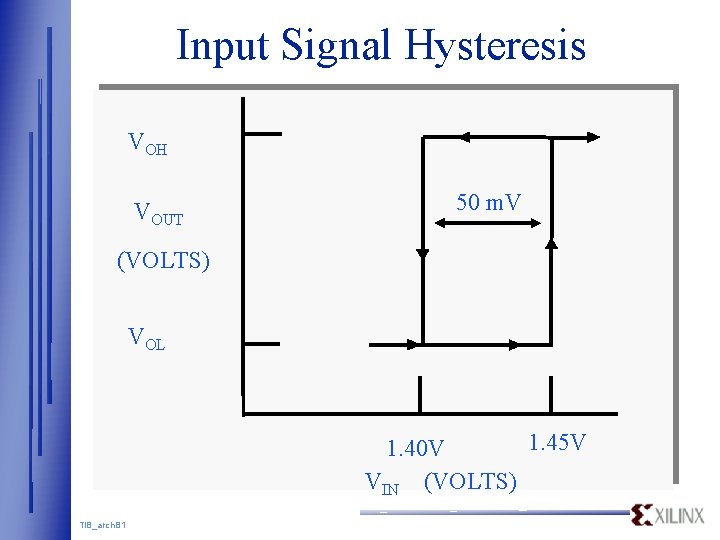

Input Signal Hysteresis VOH VOUT 50 m. V (VOLTS) VOL 1. 45 V 1. 40 V VIN (VOLTS) TIB_arch. B 1

Power Optimization w Minimum of 67% decrease in power over 5 V CPLDs w Low power option per macrocell w Even lower power if I/Os swing 02. 5 V w Fast. CONNECT II lower power than XC 9500 w I/Os swing full VCCIO range with pchannel pullups (shuts off attached TIB_arch. B 1

XC 9500 XL Design Software w XC 9500 XL Fitters in all Xilinx Standard S/W Packages — Foundation M 1. 5 — Alliance M 1. 5 w Support for Schematics, Verilog, VHDL, Abel — Exemplar — Synopsys — Synplicity — more TIB_arch. B 1

Programming Flexibility w Mount XC 9500/XL device to PCB, fixing pinouts w Program via download cable (no programmer required) w Recompile design, erase & reprogram multiple times w Debug logic with extended JTAG test w XC 9500/XL advantages – Pin-locking architecture maintains pinouts. ISP Download Cable – Endurance of 10, 000 cycles XC 9500 – Extended JTAG test XC 9500 TIB_arch. B 1

Expanded Manufacturing Capability w Mount XC 9500/XL and program using standard manufacturing automatic test equipment and JTAG w Board test using IEEE 1149. 1 compliant JTAG w Implement last-minute design changes w XC 9500/XL advantages – Fast program time (~1 second XC 95144 XL) using Automated Test Equipment (ATE) – Excellent pin-locking for last-minute design changes – Complete IEEE 1149. 1 JTAG TIB_arch. B 1

Third Party ATE Support w Hewlett-Packard w Teradyne w Gen-RAD w Common Support for both Xilinx FPGAs and CPLDs. TIB_arch. B 1

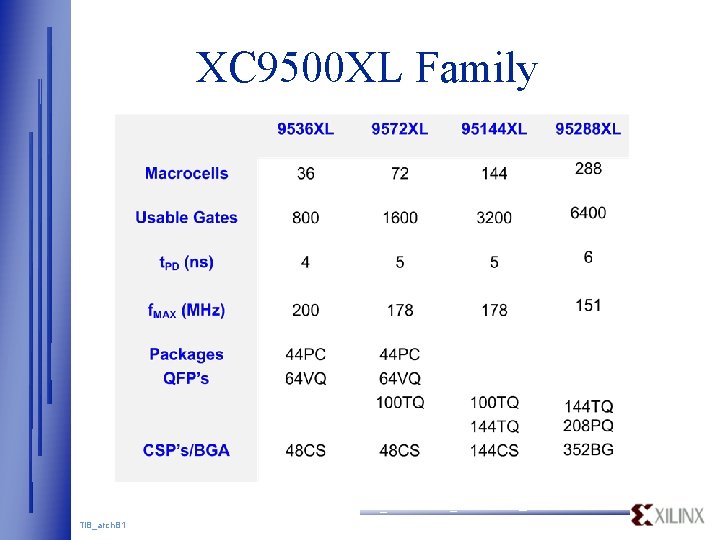

XC 9500 XL Family TIB_arch. B 1

Conclusion XC 9500 XL is the CPLD family that meets your leading-edge system needs TIB_arch. B 1

- Slides: 32