Work Package 5 IC Technologies Michael Campbell and

Work Package 5 IC Technologies Michael Campbell and Federico Faccio Microelectronics Section ESE Group, EP Department, CERN

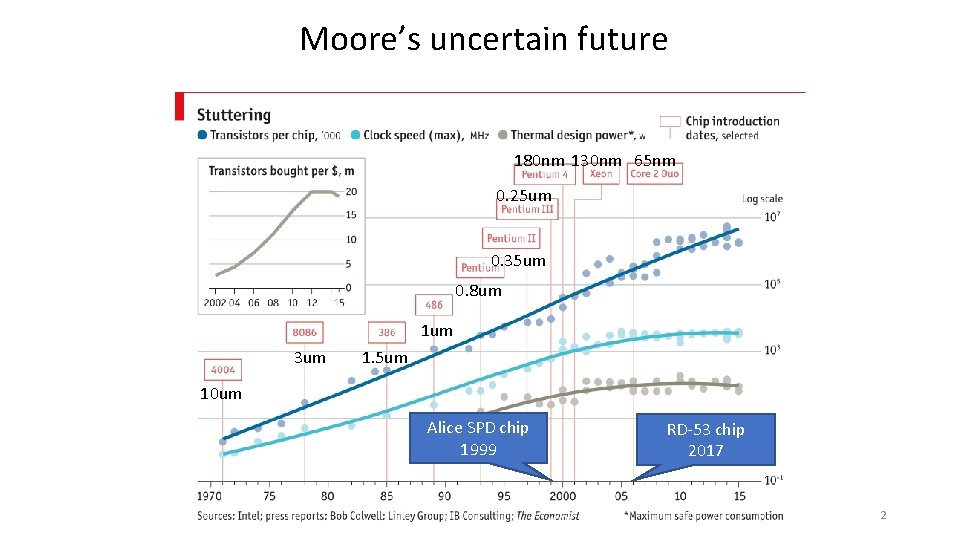

Moore’s uncertain future 180 nm 130 nm 65 nm 0. 25 um 0. 35 um 0. 8 um 1 um 3 um 1. 5 um 10 um Alice SPD chip 1999 RD-53 chip 2017 2

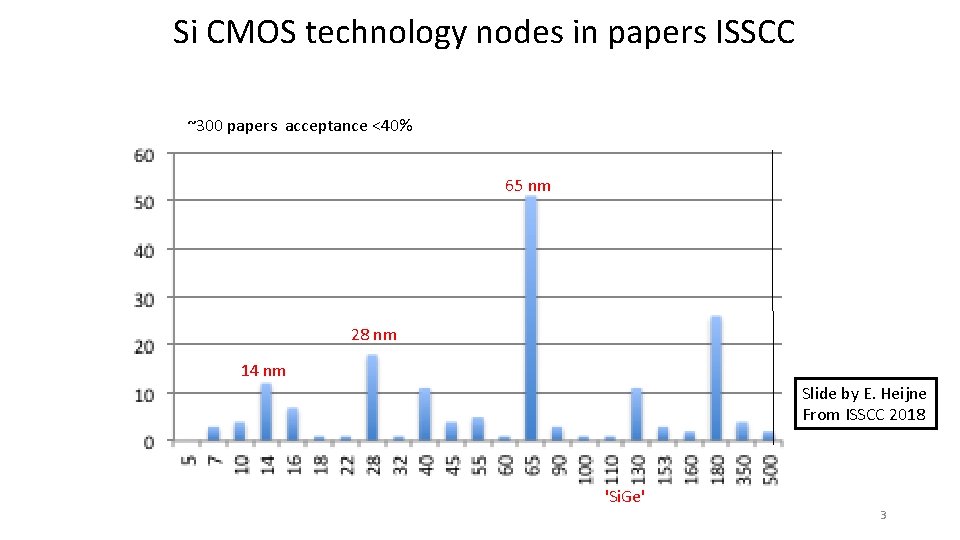

Si CMOS technology nodes in papers ISSCC 2018 ~300 papers acceptance <40% 65 nm 28 nm 14 nm Slide by E. Heijne From ISSCC 2018 'Si. Ge' 3

Looking ahead – scaling • As a community we have accumulated (at least) 10 years delay since 1999 • With the 65 nm process we cannot increase IO speed beyond 10 Gbps • FPGA chips (which we rely on off-detector) are pulling away from us • We cannot stand still but going forward requires significant resources • Below 28 nm Fin. FETs become the workhorse 4

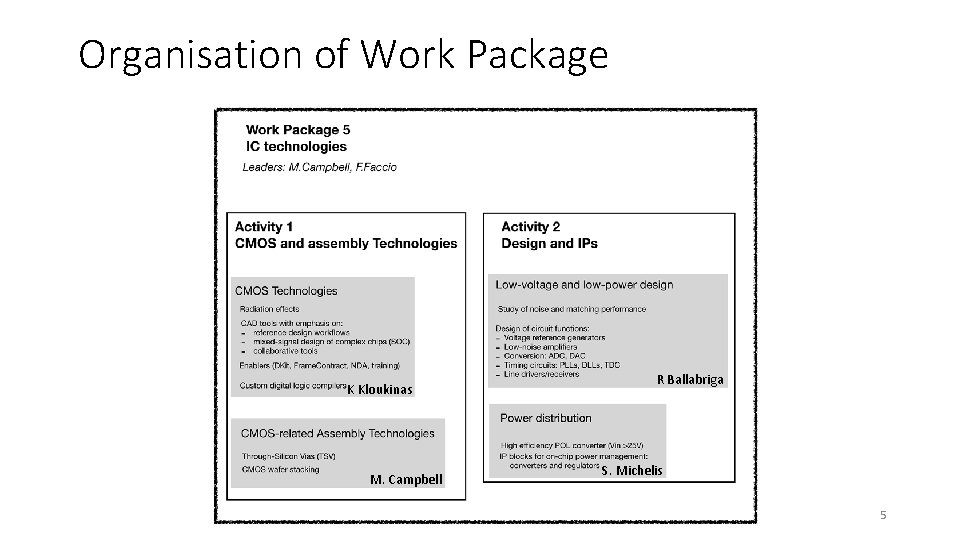

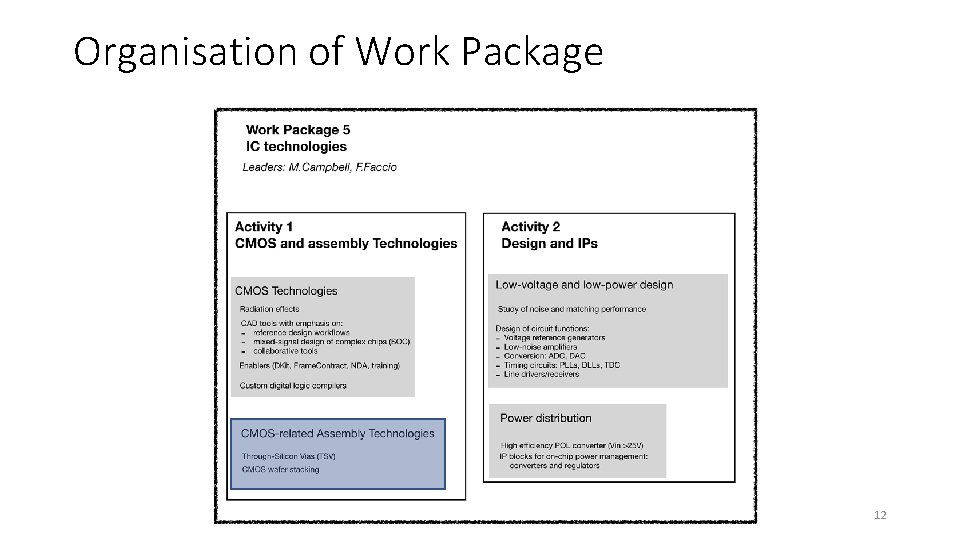

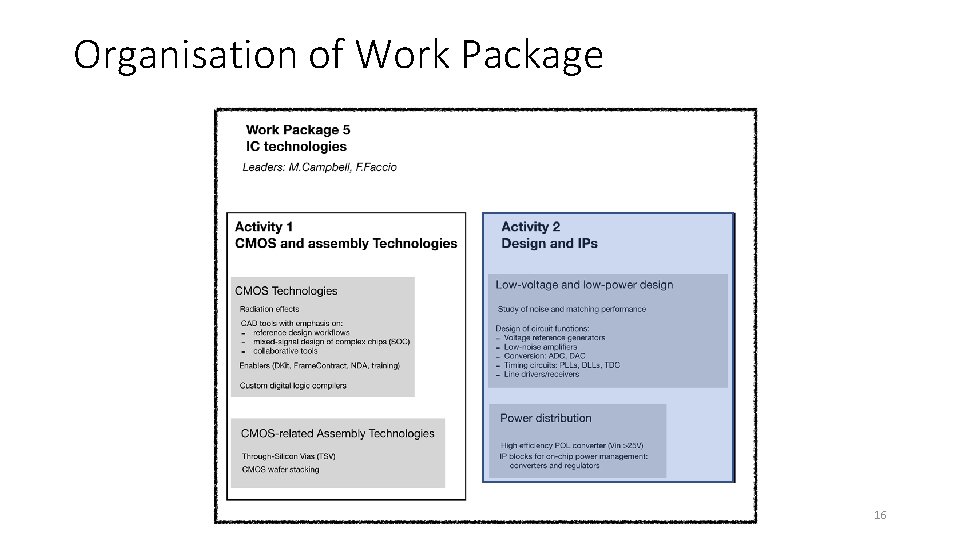

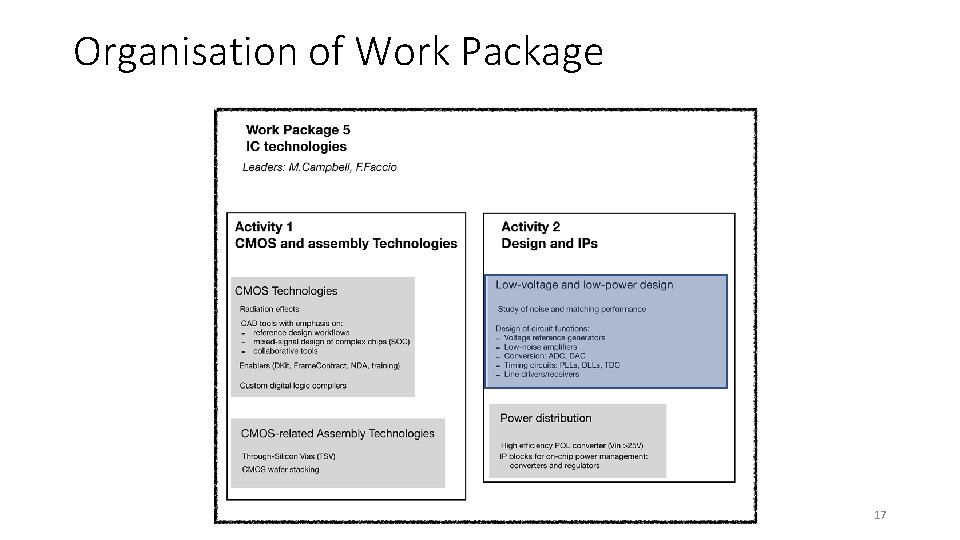

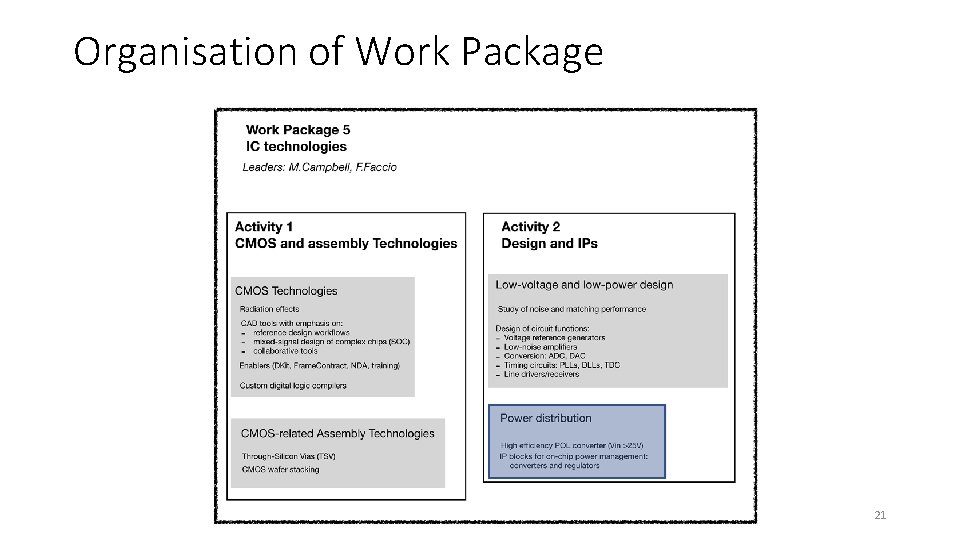

Organisation of Work Package K Kloukinas M. Campbell R Ballabriga S. Michelis 5

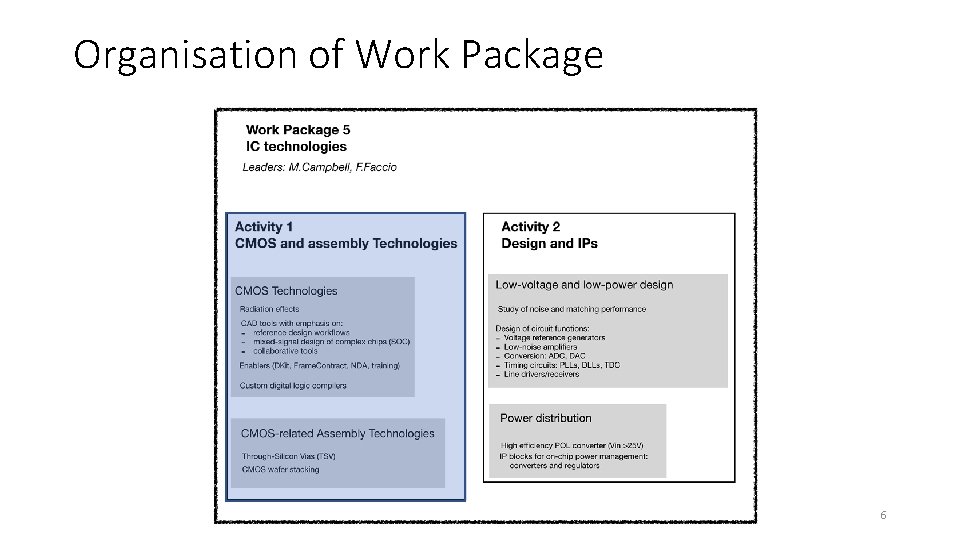

Organisation of Work Package 6

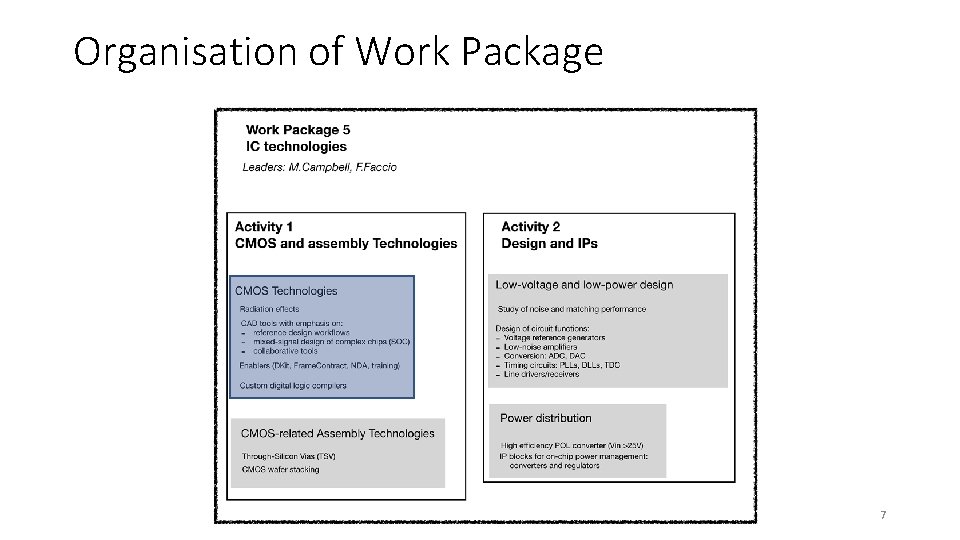

Organisation of Work Package 7

1 a CMOS Technologies - summary • Survey CMOS technologies available • 28 nm planar • 16 nm Fin. FET • Understand fundamental radiation hardness • At this point is would be helpful to know the kind of machine being planned (CLIC, HE-LHC, FCC-pp, FCC-ee) as the requirements can vary by 5 -6 orders of magnitude! • Prepare infrastructure for access • NDA permitting collaborative design and access to MPW and engineering runs • Design kits and EDA tools • Training for designers 8

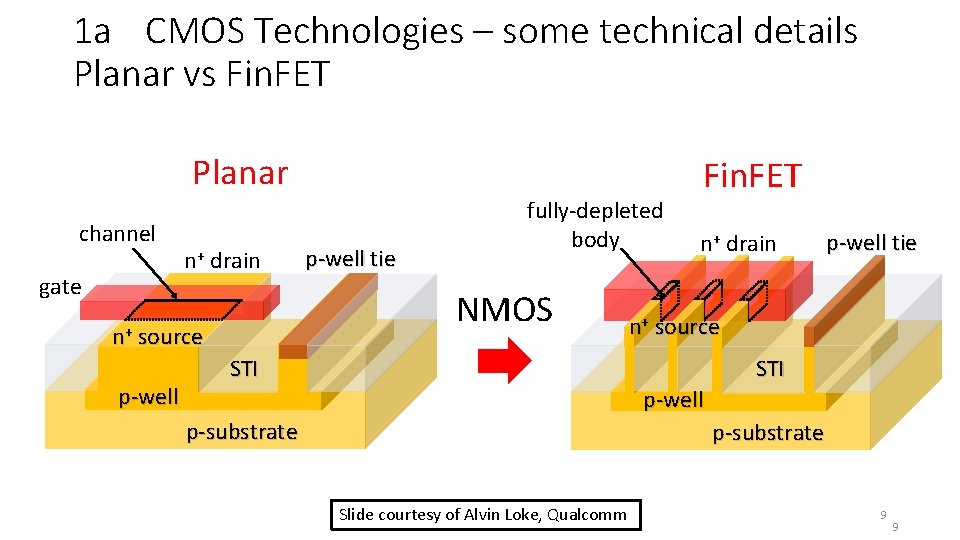

1 a CMOS Technologies – some technical details Planar vs Fin. FET Planar channel gate n+ drain NMOS n+ source p-well tie fully-depleted body Fin. FET n+ drain p-well tie n+ source STI p-well p-substrate Slide courtesy of Alvin Loke, Qualcomm 9 9

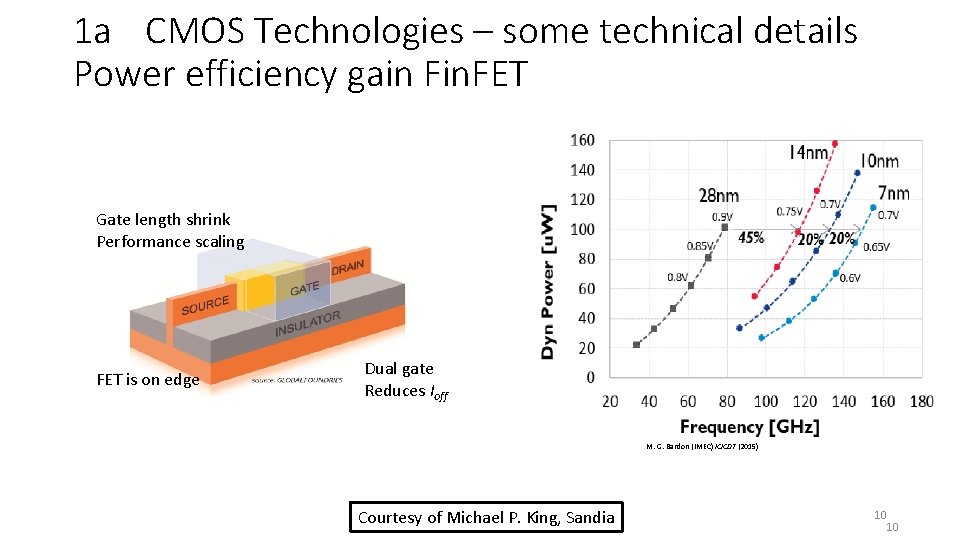

1 a CMOS Technologies – some technical details Power efficiency gain Fin. FET Gate length shrink Performance scaling FET is on edge Dual gate Reduces Ioff M. G. Bardon (IMEC) ICICDT (2015) Courtesy of Michael P. King, Sandia 10 10

1 a CMOS Technologies – some practical details • NDA’s take an age to negotiate but are an absolute necessity to enable collaborative work. They must also be scrupulously respected. • Confidential foundry information • Use restrictions • Export controls • Access to high end design tools is going to be essential for successful submissions in the new processes • Europractice needs our strongest support! • Training of existing and new designers in the use of the new tools and with an awareness of radiation tolerant design practices will be essential 11

Organisation of Work Package 12

1 b Assembly technologies – summary • Hybrid pixel detectors will continue to be needed in the regions of the experiments with high hit rates • TSV processing allows increased data throughput as data can be extracted from anywhere in the pixel matrix • In the long term access to commercial processes where wafer stacking permits the connection of a sensor and an electronics layer will blur the lines between hybrid and monolithic detectors 13

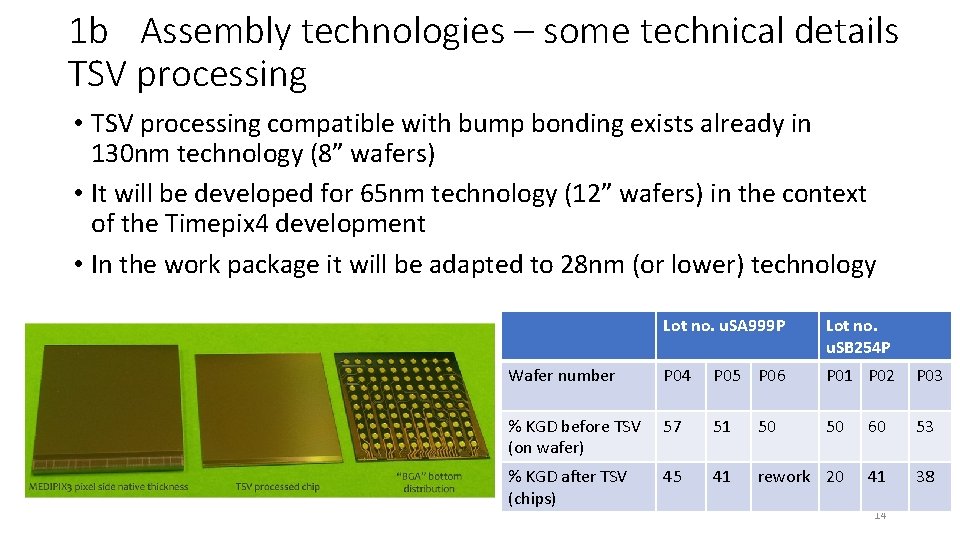

1 b Assembly technologies – some technical details TSV processing • TSV processing compatible with bump bonding exists already in 130 nm technology (8” wafers) • It will be developed for 65 nm technology (12” wafers) in the context of the Timepix 4 development • In the work package it will be adapted to 28 nm (or lower) technology Lot no. u. SA 999 P Lot no. u. SB 254 P Wafer number P 04 P 05 P 06 P 01 P 02 P 03 % KGD before TSV (on wafer) 57 51 50 50 60 53 % KGD after TSV (chips) 45 41 rework 20 41 38 14

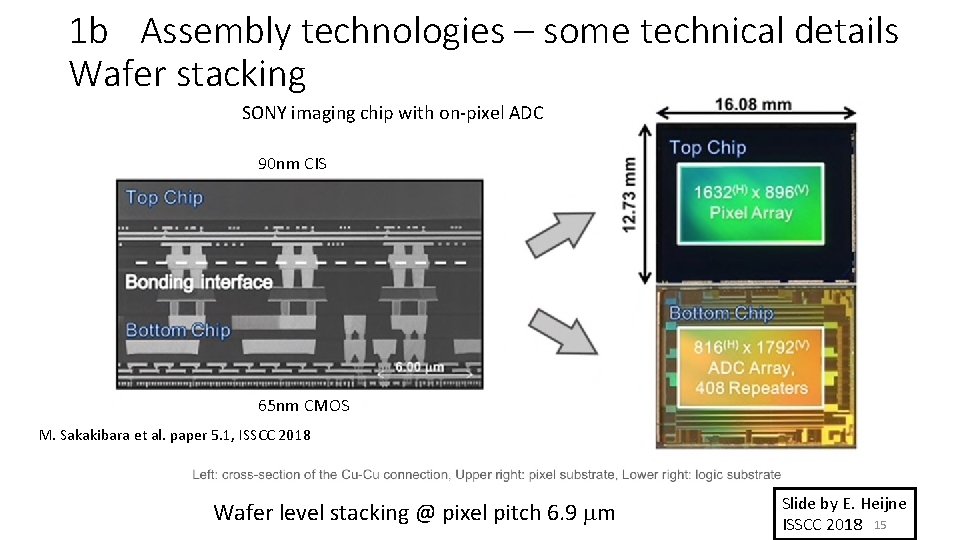

1 b Assembly technologies – some technical details Wafer stacking SONY imaging chip with on-pixel ADC 90 nm CIS 65 nm CMOS M. Sakakibara et al. paper 5. 1, ISSCC 2018 Wafer level stacking @ pixel pitch 6. 9 mm Slide by E. Heijne ISSCC 2018 15

Organisation of Work Package 16

Organisation of Work Package 17

2 a Low voltage and low power design - summary • Evaluate ASIC technologies for analog design, build up experience in using them • Design circuit building block and characterise them on silicon • Encourage the participation of other Institutes from the HEP ASIC community • Disseminate the produced know-how and contribute to the diffusion of a first-time working silicon culture 18

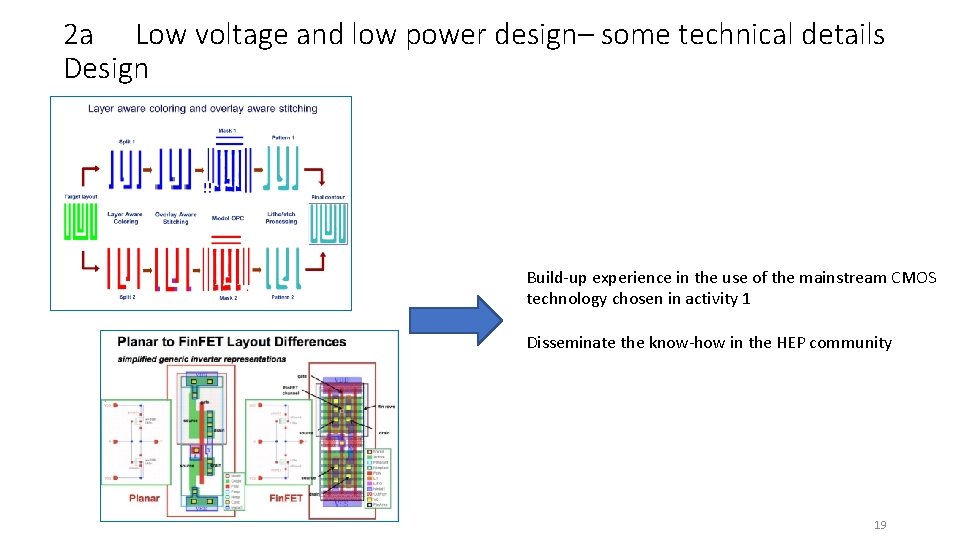

2 a Low voltage and low power design– some technical details Design Build-up experience in the use of the mainstream CMOS technology chosen in activity 1 Disseminate the know-how in the HEP community 19

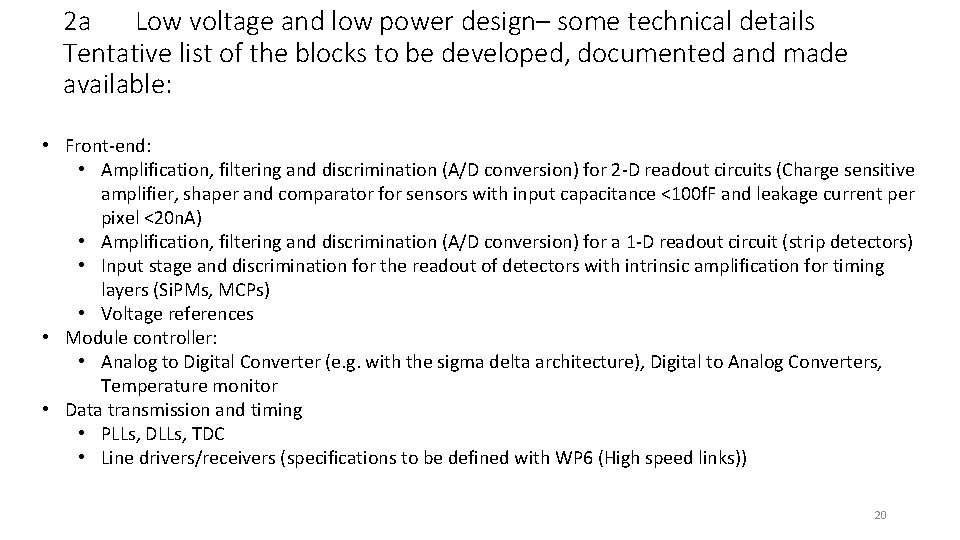

2 a Low voltage and low power design– some technical details Tentative list of the blocks to be developed, documented and made available: • Front-end: • Amplification, filtering and discrimination (A/D conversion) for 2 -D readout circuits (Charge sensitive amplifier, shaper and comparator for sensors with input capacitance <100 f. F and leakage current per pixel <20 n. A) • Amplification, filtering and discrimination (A/D conversion) for a 1 -D readout circuit (strip detectors) • Input stage and discrimination for the readout of detectors with intrinsic amplification for timing layers (Si. PMs, MCPs) • Voltage references • Module controller: • Analog to Digital Converter (e. g. with the sigma delta architecture), Digital to Analog Converters, Temperature monitor • Data transmission and timing • PLLs, DLLs, TDC • Line drivers/receivers (specifications to be defined with WP 6 (High speed links)) 20

Organisation of Work Package 21

2 b Power distribution - summary Develop components/macroblocks for a modular power distribution scheme: a. First-stage step-down POL converter from 25 V to 2. 5 -1. 8 V b. Macroblock step-down to be embedded in Systems-on-Chip c. Macroblock linear regulator to be embedded in Systems-on-Chip 22

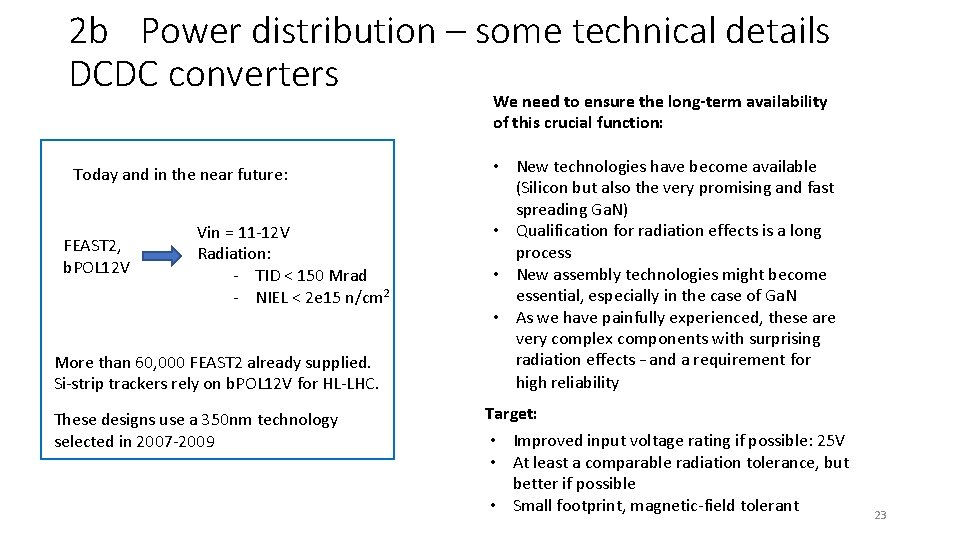

2 b Power distribution – some technical details DCDC converters We need to ensure the long-term availability of this crucial function: Today and in the near future: FEAST 2, b. POL 12 V Vin = 11 -12 V Radiation: - TID < 150 Mrad - NIEL < 2 e 15 n/cm 2 More than 60, 000 FEAST 2 already supplied. Si-strip trackers rely on b. POL 12 V for HL-LHC. These designs use a 350 nm technology selected in 2007 -2009 • New technologies have become available (Silicon but also the very promising and fast spreading Ga. N) • Qualification for radiation effects is a long process • New assembly technologies might become essential, especially in the case of Ga. N • As we have painfully experienced, these are very complex components with surprising radiation effects – and a requirement for high reliability Target: • Improved input voltage rating if possible: 25 V • At least a comparable radiation tolerance, but better if possible • Small footprint, magnetic-field tolerant 23

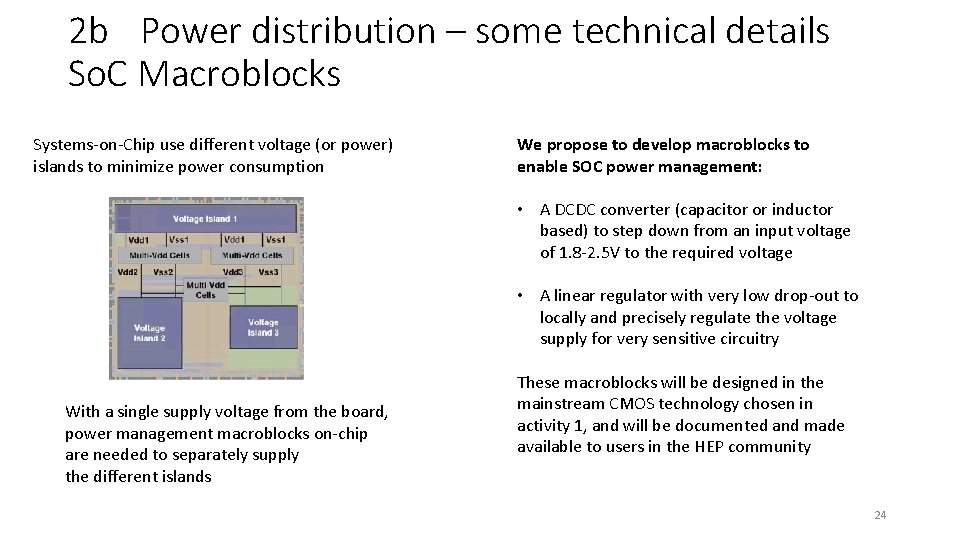

2 b Power distribution – some technical details So. C Macroblocks Systems-on-Chip use different voltage (or power) islands to minimize power consumption We propose to develop macroblocks to enable SOC power management: • A DCDC converter (capacitor or inductor based) to step down from an input voltage of 1. 8 -2. 5 V to the required voltage • A linear regulator with very low drop-out to locally and precisely regulate the voltage supply for very sensitive circuitry With a single supply voltage from the board, power management macroblocks on-chip are needed to separately supply the different islands These macroblocks will be designed in the mainstream CMOS technology chosen in activity 1, and will be documented and made available to users in the HEP community 24

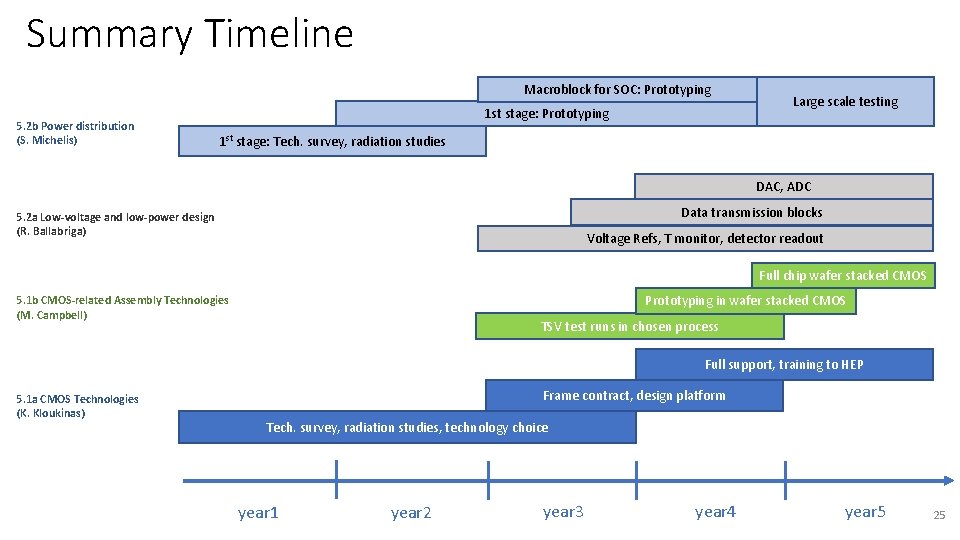

Summary Timeline Macroblock for SOC: Prototyping 5. 2 b Power distribution (S. Michelis) 1 st stage: Prototyping Large scale testing 1 st stage: Tech. survey, radiation studies DAC, ADC Data transmission blocks 5. 2 a Low-voltage and low-power design (R. Ballabriga) Voltage Refs, T monitor, detector readout Full chip wafer stacked CMOS Prototyping in wafer stacked CMOS 5. 1 b CMOS-related Assembly Technologies (M. Campbell) TSV test runs in chosen process Full support, training to HEP 5. 1 a CMOS Technologies (K. Kloukinas) Frame contract, design platform Tech. survey, radiation studies, technology choice year 1 year 2 year 3 year 4 year 5 25

- Slides: 25