WK 15 Chapter 15 PC Standard Bus Interfaces

WK 15 Chapter 15 PC Standard Bus Interfaces Brey: The Intel Microprocessors, 7 e © 2006 Pearson Education, Upper Saddle River, NJ 07458. All Rights Reserved.

Chapter Objectives • Describe pin and signal details of typical standard PC buses: PCI Parallel bus USB Serial bus • Illustrate simple interfaces Brey: The Intel Microprocessors, 7 e © 2006 Pearson Education, Upper Saddle River, NJ 07458. All Rights Reserved.

The need for buses • Early PCs had a few parallel ports and serial ports • A port was needed for each device interfaced: e. g. one printer required a parallel port, e. g. COM 1 • A standard bus is needed to connect several of devices (boards, equipment) made by different manufacturers Brey: The Intel Microprocessors, 7 e © 2006 Pearson Education, Upper Saddle River, NJ 07458. All Rights Reserved.

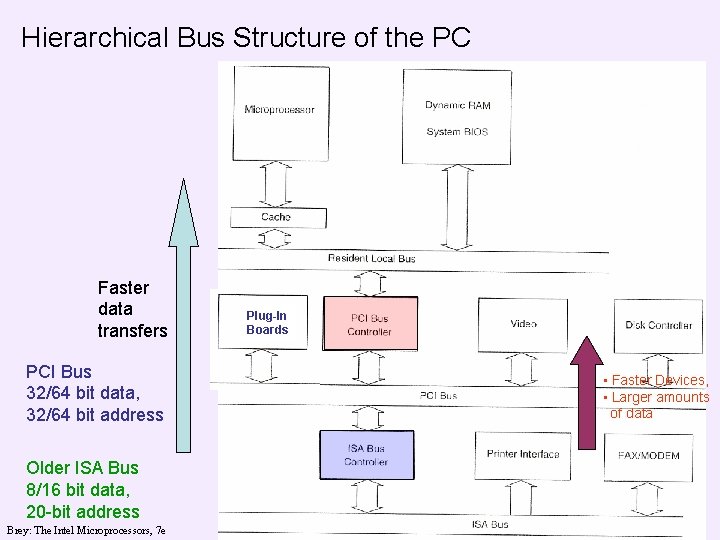

Hierarchical Bus Structure of the PC Faster data transfers PCI Bus 32/64 bit data, 32/64 bit address Plug-In Boards • Faster Devices, • Larger amounts of data Older ISA Bus 8/16 bit data, 20 -bit address Brey: The Intel Microprocessors, 7 e © 2006 Pearson Education, Upper Saddle River, NJ 07458. All Rights Reserved.

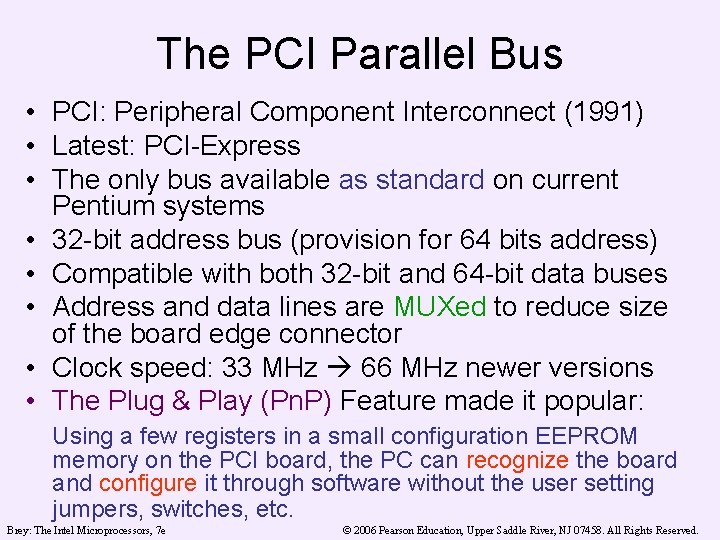

The PCI Parallel Bus • PCI: Peripheral Component Interconnect (1991) • Latest: PCI-Express • The only bus available as standard on current Pentium systems • 32 -bit address bus (provision for 64 bits address) • Compatible with both 32 -bit and 64 -bit data buses • Address and data lines are MUXed to reduce size of the board edge connector • Clock speed: 33 MHz 66 MHz newer versions • The Plug & Play (Pn. P) Feature made it popular: Using a few registers in a small configuration EEPROM memory on the PCI board, the PC can recognize the board and configure it through software without the user setting jumpers, switches, etc. Brey: The Intel Microprocessors, 7 e © 2006 Pearson Education, Upper Saddle River, NJ 07458. All Rights Reserved.

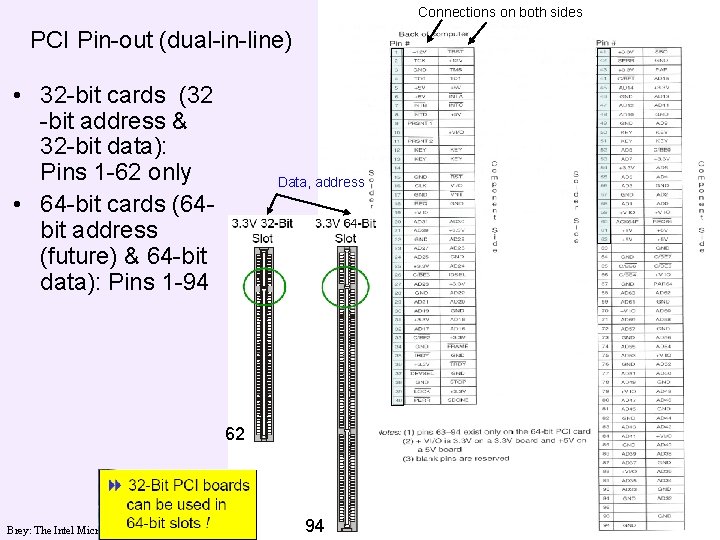

Connections on both sides PCI Pin-out (dual-in-line) • 32 -bit cards (32 -bit address & 32 -bit data): Pins 1 -62 only • 64 -bit cards (64 bit address (future) & 64 -bit data): Pins 1 -94 Data, address 62 Brey: The Intel Microprocessors, 7 e 94 © 2006 Pearson Education, Upper Saddle River, NJ 07458. All Rights Reserved.

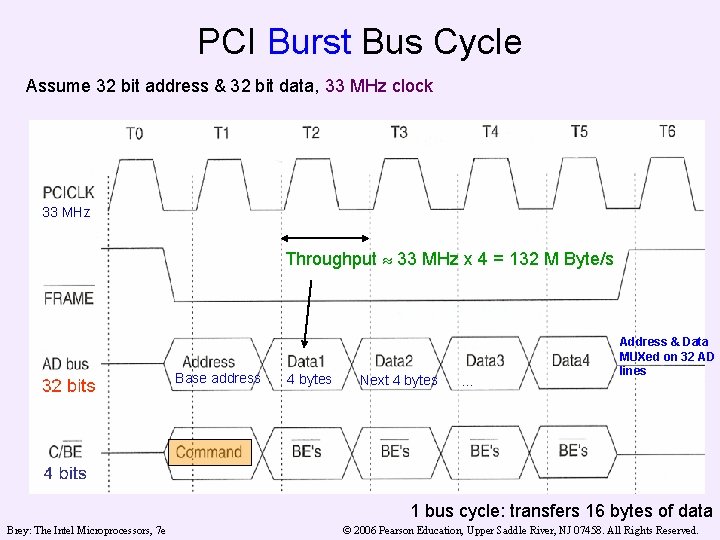

PCI Burst Bus Cycle Assume 32 bit address & 32 bit data, 33 MHz clock 33 MHz Throughput 33 MHz x 4 = 132 M Byte/s Base address 4 bytes Next 4 bytes … Address & Data MUXed on 32 AD lines 1 bus cycle: transfers 16 bytes of data Brey: The Intel Microprocessors, 7 e © 2006 Pearson Education, Upper Saddle River, NJ 07458. All Rights Reserved.

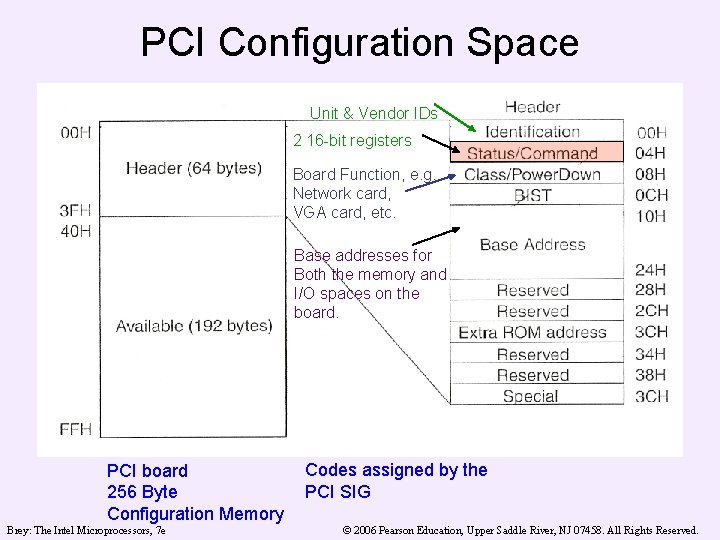

PCI Configuration Space Unit & Vendor IDs 2 16 -bit registers Board Function, e. g. Network card, VGA card, etc. Base addresses for Both the memory and I/O spaces on the board. PCI board 256 Byte Configuration Memory Brey: The Intel Microprocessors, 7 e Codes assigned by the PCI SIG © 2006 Pearson Education, Upper Saddle River, NJ 07458. All Rights Reserved.

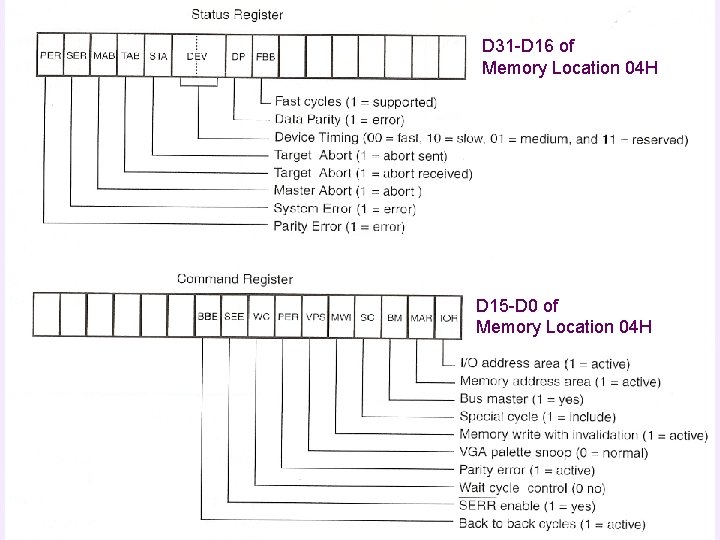

D 31 -D 16 of Memory Location 04 H D 15 -D 0 of Memory Location 04 H Brey: The Intel Microprocessors, 7 e © 2006 Pearson Education, Upper Saddle River, NJ 07458. All Rights Reserved.

The USB Bus • The universal serial bus (USB) • A very convenient way to interface many I/O device to the personal computer: keyboards, mice, flash drives, hard drives, speakers, TV tuners, webcams, etc. • The 4 -wire serial bus supports multiple connected devices • Supplies power to devices Brey: The Intel Microprocessors, 7 e © 2006 Pearson Education, Upper Saddle River, NJ 07458. All Rights Reserved.

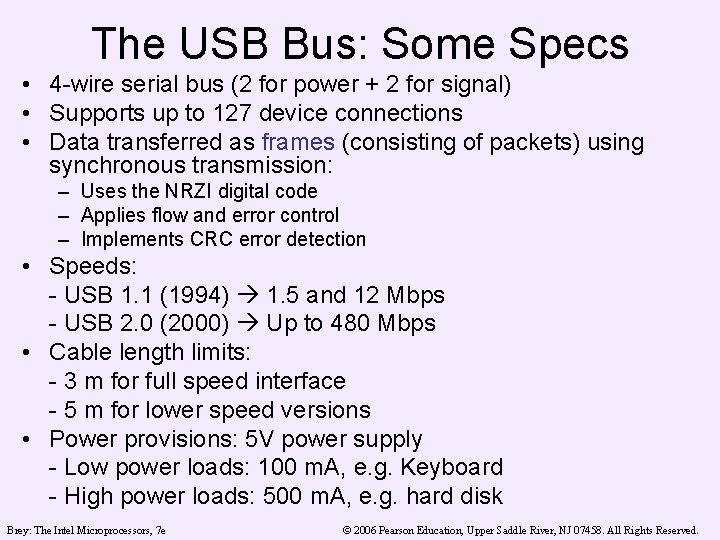

The USB Bus: Some Specs • 4 -wire serial bus (2 for power + 2 for signal) • Supports up to 127 device connections • Data transferred as frames (consisting of packets) using synchronous transmission: – Uses the NRZI digital code – Applies flow and error control – Implements CRC error detection • Speeds: - USB 1. 1 (1994) 1. 5 and 12 Mbps - USB 2. 0 (2000) Up to 480 Mbps • Cable length limits: - 3 m for full speed interface - 5 m for lower speed versions • Power provisions: 5 V power supply - Low power loads: 100 m. A, e. g. Keyboard - High power loads: 500 m. A, e. g. hard disk Brey: The Intel Microprocessors, 7 e © 2006 Pearson Education, Upper Saddle River, NJ 07458. All Rights Reserved.

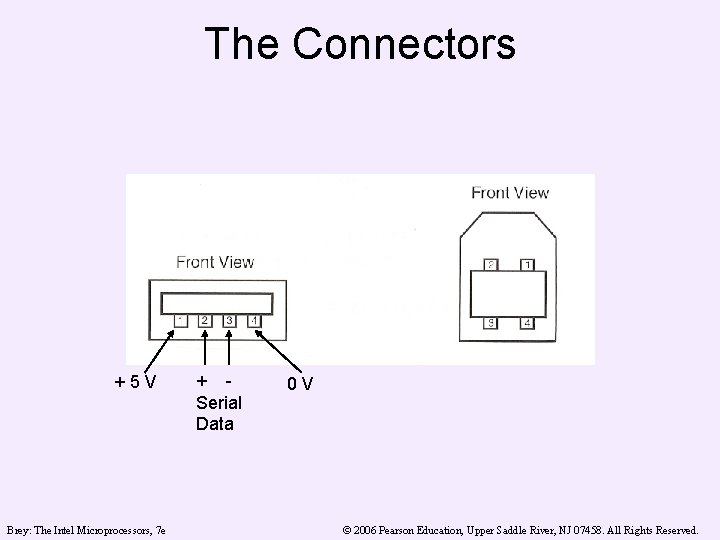

The Connectors +5 V Brey: The Intel Microprocessors, 7 e + Serial Data 0 V © 2006 Pearson Education, Upper Saddle River, NJ 07458. All Rights Reserved.

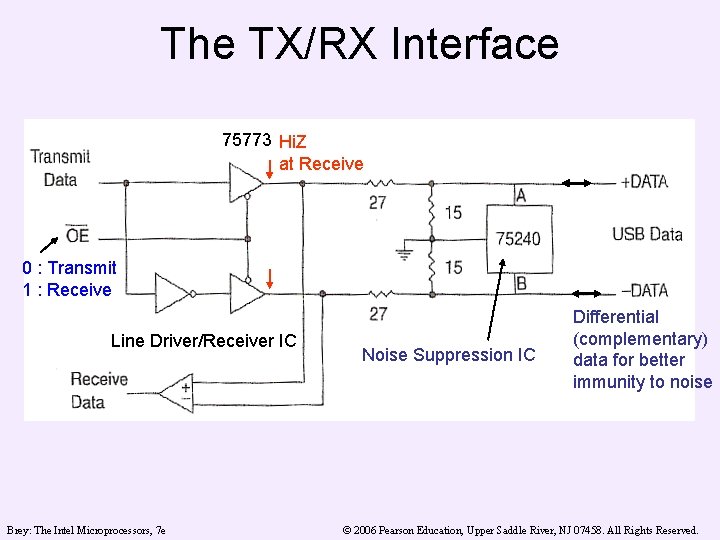

The TX/RX Interface 75773 Hi. Z at Receive 0 : Transmit 1 : Receive Line Driver/Receiver IC Brey: The Intel Microprocessors, 7 e Noise Suppression IC Differential (complementary) data for better immunity to noise © 2006 Pearson Education, Upper Saddle River, NJ 07458. All Rights Reserved.

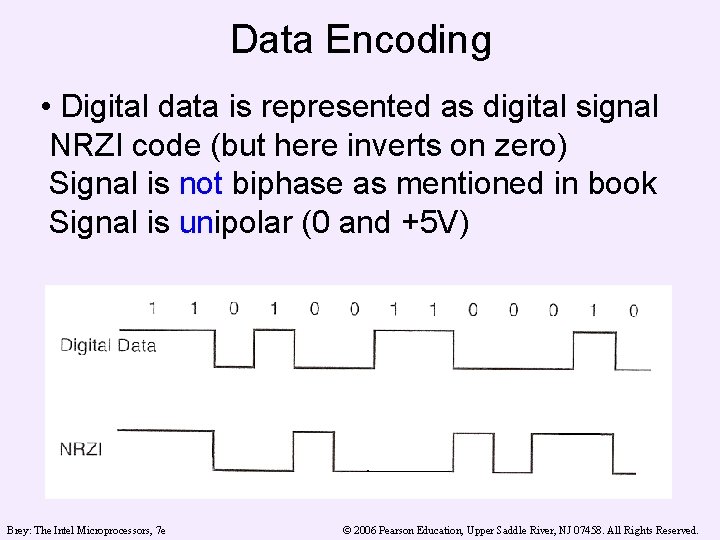

Data Encoding • Digital data is represented as digital signal NRZI code (but here inverts on zero) Signal is not biphase as mentioned in book Signal is unipolar (0 and +5 V) Brey: The Intel Microprocessors, 7 e © 2006 Pearson Education, Upper Saddle River, NJ 07458. All Rights Reserved.

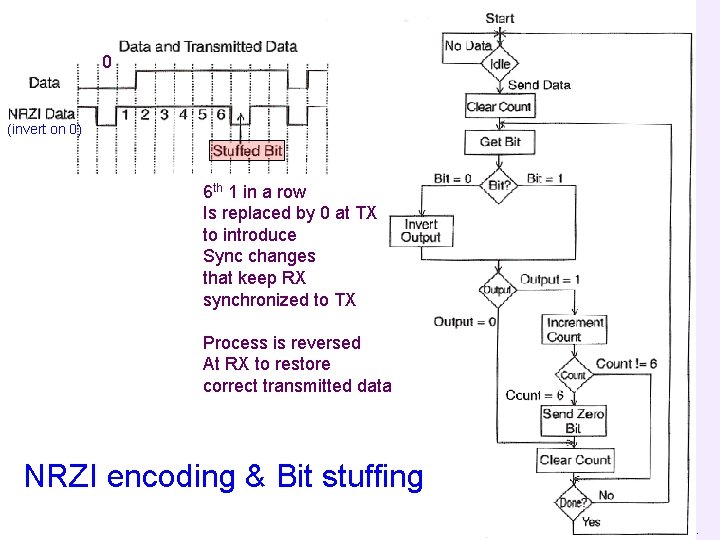

0 (invert on 0) 6 th 1 in a row Is replaced by 0 at TX to introduce Sync changes that keep RX synchronized to TX Process is reversed At RX to restore correct transmitted data NRZI encoding & Bit stuffing Brey: The Intel Microprocessors, 7 e © 2006 Pearson Education, Upper Saddle River, NJ 07458. All Rights Reserved.

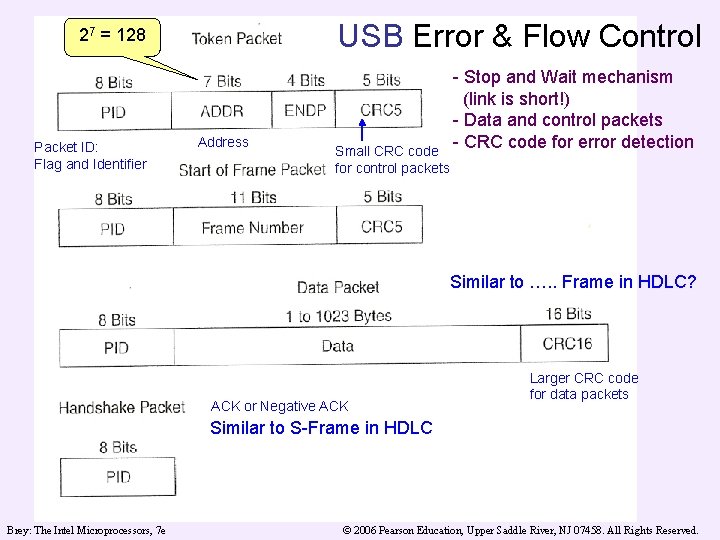

USB Error & Flow Control 27 = 128 Packet ID: Flag and Identifier Address Small CRC code for control packets - Stop and Wait mechanism (link is short!) - Data and control packets - CRC code for error detection Similar to …. . Frame in HDLC? ACK or Negative ACK Larger CRC code for data packets Similar to S-Frame in HDLC Brey: The Intel Microprocessors, 7 e © 2006 Pearson Education, Upper Saddle River, NJ 07458. All Rights Reserved.

To serve also as a good preamble flag, it must be a unique pattern: 2 nd 4 bits are complements of 1 st 4 bits! (e. g. E 1 = 11100001, A 5 = 10100101) PID Name Type Description E 1 OUT Token Host function transaction D 2 ACK Handshake Receiver accepts packet C 3 Data 0 Data packet (PID even) A 5 SOF Token Start of frame (frame = several packets? ) 69 IN Token Function host transaction 5 A Negative ACK Handshake Receiver does not accept packet 4 B Data 1 Data packet (PID odd) 3 C PRE Special Host preamble 2 D Setup Token Setup command 1 E Stall Token Stalled Brey: The Intel Microprocessors, 7 e © 2006 Pearson Education, Upper Saddle River, NJ 07458. All Rights Reserved.

- Slides: 17