Winter 2006 2007 Compiler Construction T 9 IR

![Translating expressions – example TR[x + 42] visit Add. Expr left right Add R Translating expressions – example TR[x + 42] visit Add. Expr left right Add R](https://slidetodoc.com/presentation_image_h2/8ff89a42a54b65c65186c6062eff11b2/image-8.jpg)

![Translating (short-circuit) OR TR[e 1 OR e 2] R 1 : = T[e 1] Translating (short-circuit) OR TR[e 1 OR e 2] R 1 : = T[e 1]](https://slidetodoc.com/presentation_image_h2/8ff89a42a54b65c65186c6062eff11b2/image-11.jpg)

![Translating (short-circuit) AND TR[e 1 AND e 2] R 1 : = T[e 1] Translating (short-circuit) AND TR[e 1 AND e 2] R 1 : = T[e 1]](https://slidetodoc.com/presentation_image_h2/8ff89a42a54b65c65186c6062eff11b2/image-12.jpg)

![Translating array and field access TR[e 1[e 2]] R 1 : = TR[e 1] Translating array and field access TR[e 1[e 2]] R 1 : = TR[e 1]](https://slidetodoc.com/presentation_image_h2/8ff89a42a54b65c65186c6062eff11b2/image-13.jpg)

![Translating statement block TR[s 1; s 2; … ; s. N] TR[s 1] TR[s Translating statement block TR[s 1; s 2; … ; s. N] TR[s 1] TR[s](https://slidetodoc.com/presentation_image_h2/8ff89a42a54b65c65186c6062eff11b2/image-14.jpg)

![Translating if-then-else TR[if (e) then s 1 else s 2] Fresh labels generated during Translating if-then-else TR[if (e) then s 1 else s 2] Fresh labels generated during](https://slidetodoc.com/presentation_image_h2/8ff89a42a54b65c65186c6062eff11b2/image-15.jpg)

![Translating if-then TR[if (e) then s] Can avoid generating labels unnecessarily R 1 : Translating if-then TR[if (e) then s] Can avoid generating labels unnecessarily R 1 :](https://slidetodoc.com/presentation_image_h2/8ff89a42a54b65c65186c6062eff11b2/image-16.jpg)

![Translating while TR[while (e) s] _test_label: R 1 : = TR[e] Compare 0, R Translating while TR[while (e) s] _test_label: R 1 : = TR[e] Compare 0, R](https://slidetodoc.com/presentation_image_h2/8ff89a42a54b65c65186c6062eff11b2/image-17.jpg)

![Translating call/return TR[C. foo(e 1, …, en)] R 1 : = TR[e 1] formal Translating call/return TR[C. foo(e 1, …, en)] R 1 : = TR[e 1] formal](https://slidetodoc.com/presentation_image_h2/8ff89a42a54b65c65186c6062eff11b2/image-18.jpg)

![Example revisited TR[ x = 42; while (x > 0) { x=x-1; } ] Example revisited TR[ x = 42; while (x > 0) { x=x-1; } ]](https://slidetodoc.com/presentation_image_h2/8ff89a42a54b65c65186c6062eff11b2/image-20.jpg)

- Slides: 37

Winter 2006 -2007 Compiler Construction T 9 – IR part 2 + Runtime organization Mooly Sagiv and Roman Manevich School of Computer Science Tel-Aviv University

Announcements n What is expected in PA 3 documentation (5 pts) n n n Testing strategy: lists of tests and what they check (scope rules, type rules etc. ) How did you conduct the semantic analysis – in which order do you do things Don’t document the most obvious things (“The input to CUP is in IC. cup”), don’t repeat stuff already in PA 3. pdf Document non-obvious choices (“We build the type table after parsing”, “we do not handle situation X”, “we handle special situation Y like so”) Output format (e. g. , “first we print type table then we print…”) Know thy group’s code 2

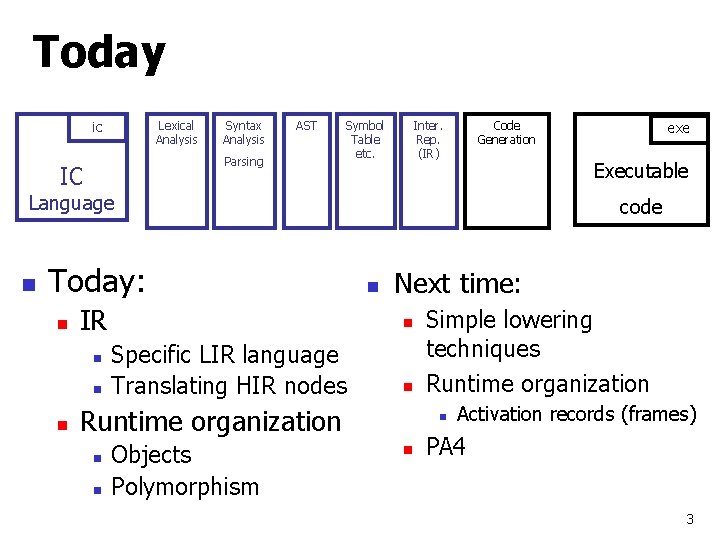

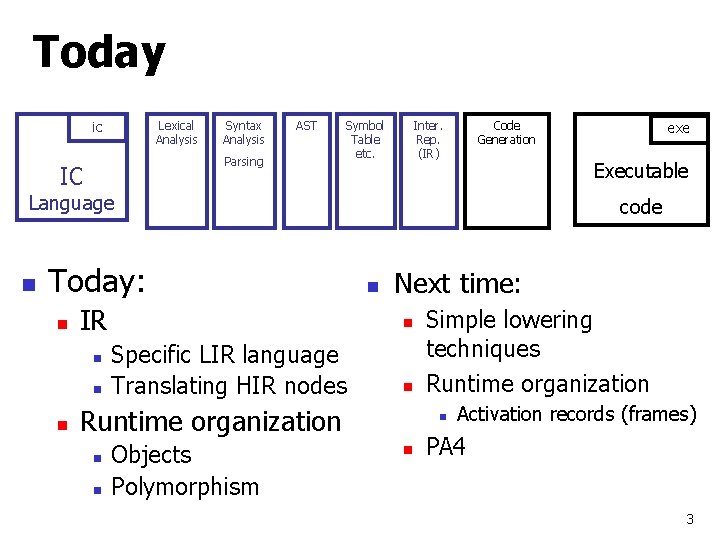

Today ic Lexical Analysis Syntax Analysis AST Parsing IC Symbol Table etc. Inter. Rep. (IR) Code Generation Executable Language n Today: n IR n n n code n Next time: n Specific LIR language Translating HIR nodes n Runtime organization n n Objects Polymorphism exe Simple lowering techniques Runtime organization n n Activation records (frames) PA 4 3

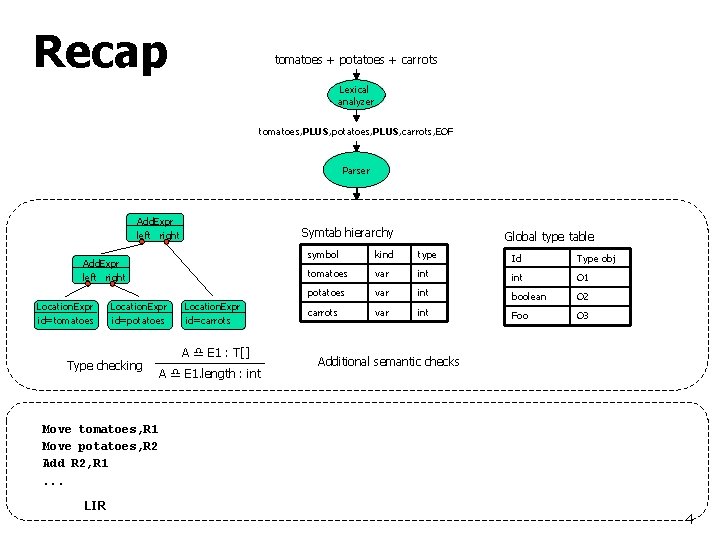

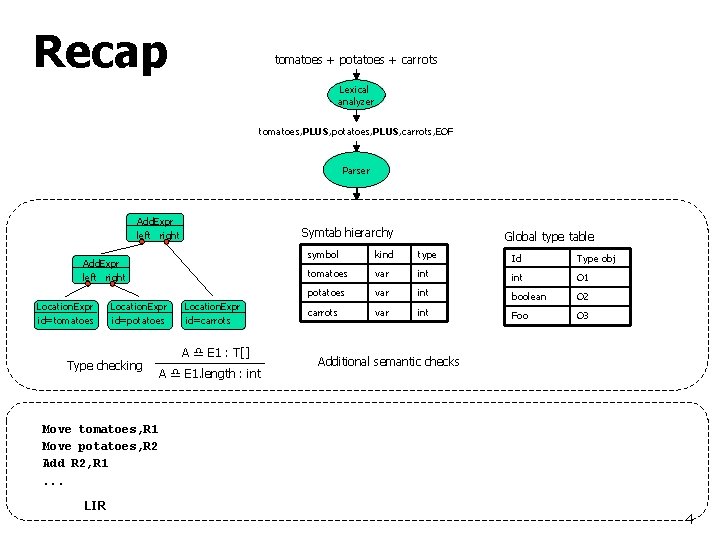

Recap tomatoes + potatoes + carrots Lexical analyzer tomatoes, PLUS, potatoes, PLUS, carrots, EOF Parser Add. Expr left right Symtab hierarchy Add. Expr left right Location. Expr id=tomatoes Location. Expr id=potatoes Type checking Location. Expr id=carrots A E 1 : T[] A E 1. length : int Global type table symbol kind type Id Type obj tomatoes var int O 1 potatoes var int boolean O 2 carrots var int Foo O 3 Additional semantic checks Move tomatoes, R 1 Move potatoes, R 2 Add R 2, R 1. . . LIR 4

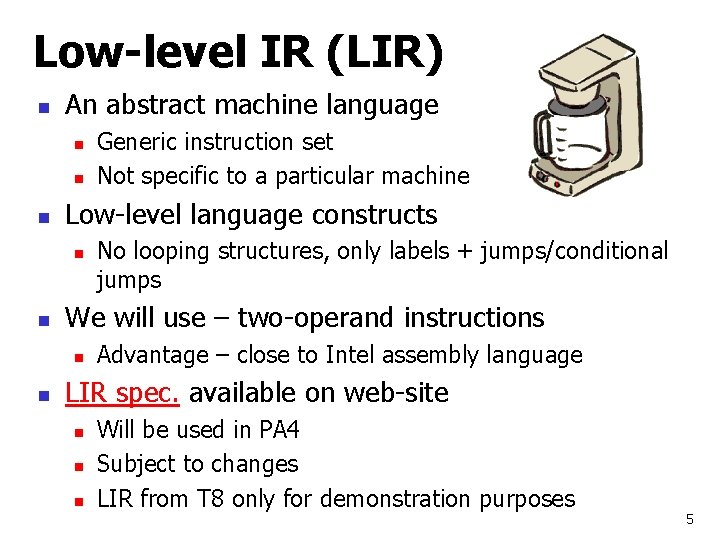

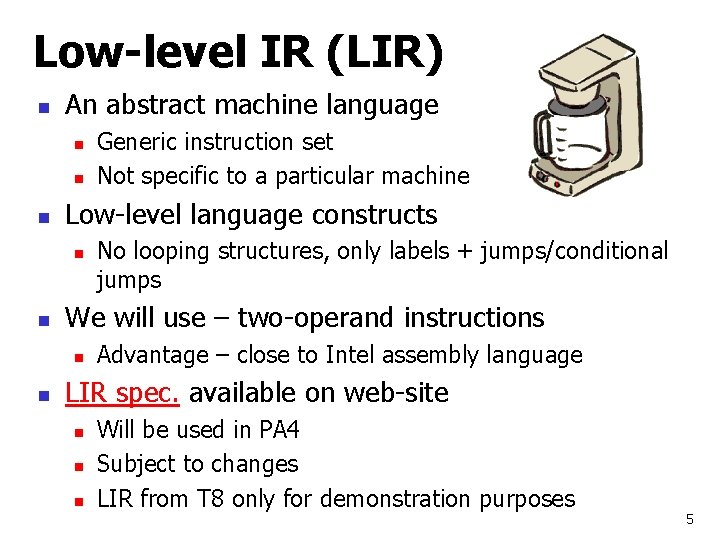

Low-level IR (LIR) n An abstract machine language n n n Low-level language constructs n n No looping structures, only labels + jumps/conditional jumps We will use – two-operand instructions n n Generic instruction set Not specific to a particular machine Advantage – close to Intel assembly language LIR spec. available on web-site n n n Will be used in PA 4 Subject to changes LIR from T 8 only for demonstration purposes 5

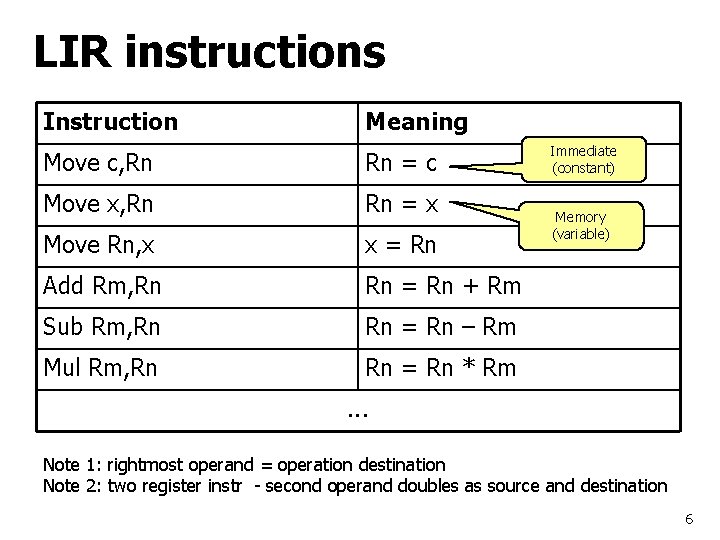

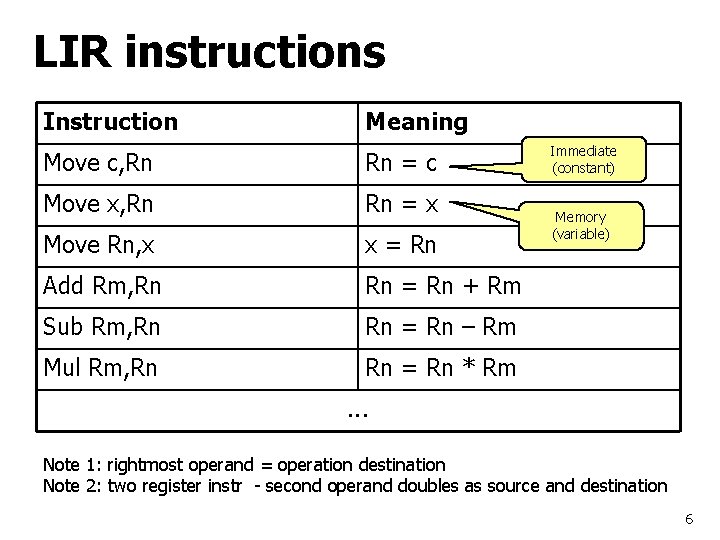

LIR instructions Instruction Meaning Move c, Rn Rn = c Move x, Rn Rn = x Move Rn, x x = Rn Add Rm, Rn Rn = Rn + Rm Sub Rm, Rn Rn = Rn – Rm Mul Rm, Rn Rn = Rn * Rm Immediate (constant) Memory (variable) . . . Note 1: rightmost operand = operation destination Note 2: two register instr - second operand doubles as source and destination 6

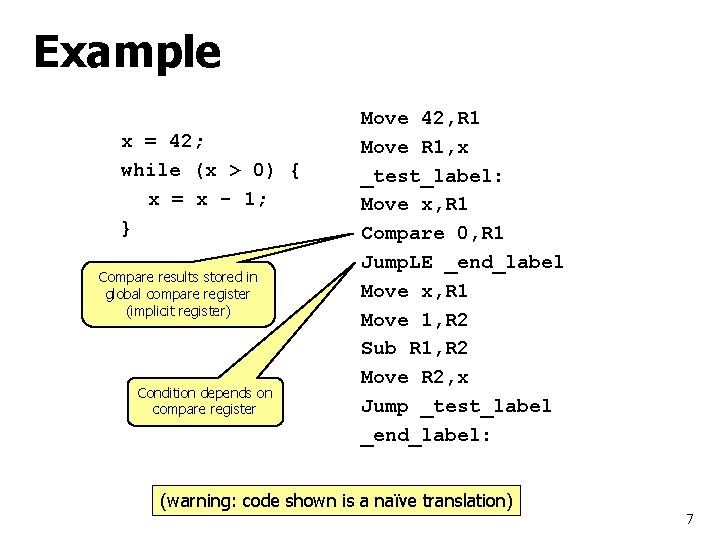

Example x = 42; while (x > 0) { x = x - 1; } Compare results stored in global compare register (implicit register) Condition depends on compare register Move 42, R 1 Move R 1, x _test_label: Move x, R 1 Compare 0, R 1 Jump. LE _end_label Move x, R 1 Move 1, R 2 Sub R 1, R 2 Move R 2, x Jump _test_label _end_label: (warning: code shown is a naïve translation) 7

![Translating expressions example TRx 42 visit Add Expr left right Add R Translating expressions – example TR[x + 42] visit Add. Expr left right Add R](https://slidetodoc.com/presentation_image_h2/8ff89a42a54b65c65186c6062eff11b2/image-8.jpg)

Translating expressions – example TR[x + 42] visit Add. Expr left right Add R 2, R 1 visit (right) visit (left) Move x, R 1 Move 42, R 2 Add R 2, R 1 Location. Ex Value. Expr id = x val = 42 Move x, R 1 Move 42, R 2 Very inefficient translation – can we do better? 8

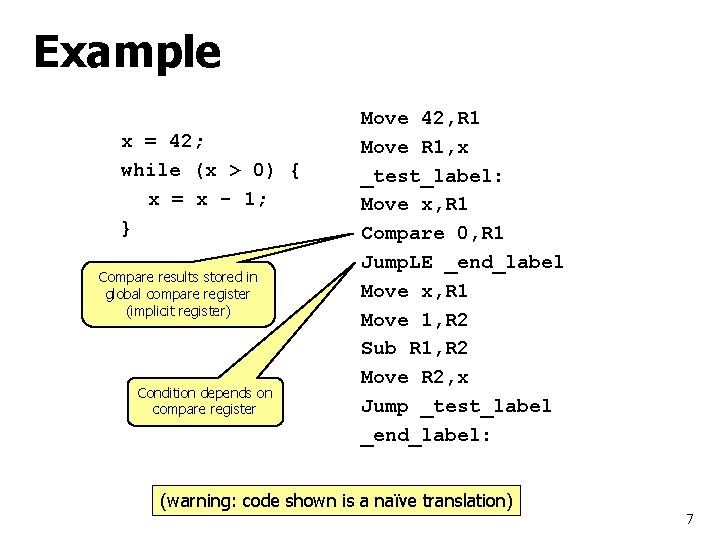

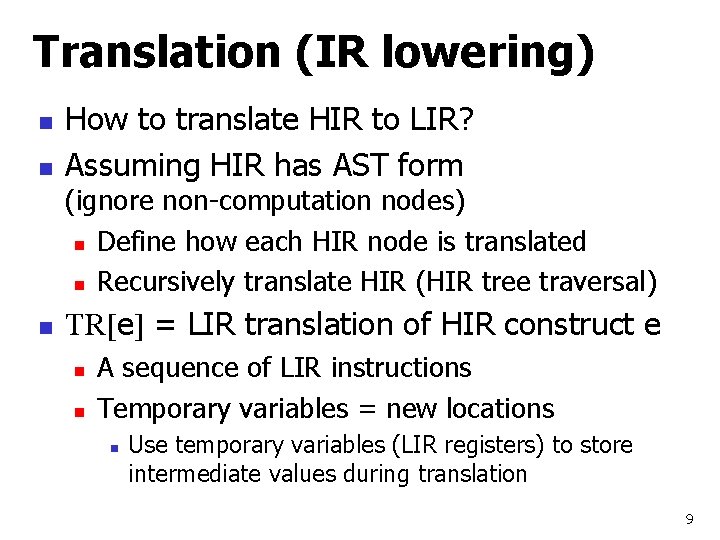

Translation (IR lowering) n n How to translate HIR to LIR? Assuming HIR has AST form (ignore non-computation nodes) n Define how each HIR node is translated n Recursively translate HIR (HIR tree traversal) n TR[e] = LIR translation of HIR construct e n n A sequence of LIR instructions Temporary variables = new locations n Use temporary variables (LIR registers) to store intermediate values during translation 9

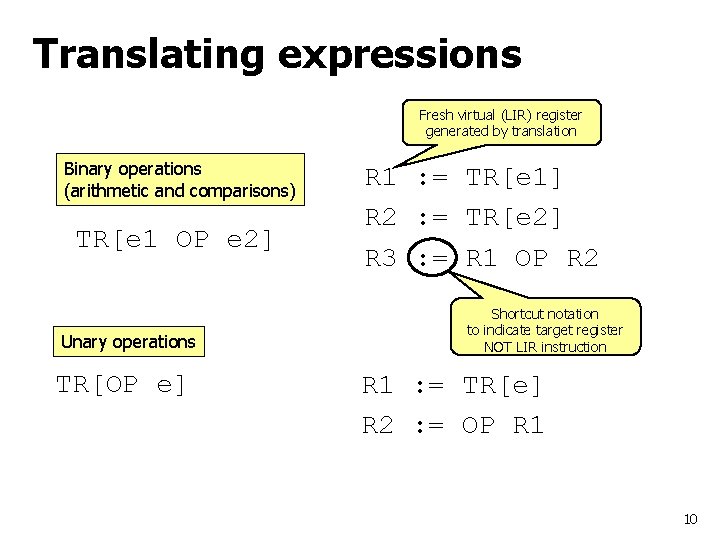

Translating expressions Fresh virtual (LIR) register generated by translation Binary operations (arithmetic and comparisons) TR[e 1 OP e 2] Unary operations TR[OP e] R 1 : = TR[e 1] R 2 : = TR[e 2] R 3 : = R 1 OP R 2 Shortcut notation to indicate target register NOT LIR instruction R 1 : = TR[e] R 2 : = OP R 1 10

![Translating shortcircuit OR TRe 1 OR e 2 R 1 Te 1 Translating (short-circuit) OR TR[e 1 OR e 2] R 1 : = T[e 1]](https://slidetodoc.com/presentation_image_h2/8ff89a42a54b65c65186c6062eff11b2/image-11.jpg)

Translating (short-circuit) OR TR[e 1 OR e 2] R 1 : = T[e 1] Compare 1, R 1 Jump. True _end_label R 2 : = T[e 2] Or R 2, R 1 _end_label: (OR can be replaced by Move operation since R 1 is 0) 11

![Translating shortcircuit AND TRe 1 AND e 2 R 1 Te 1 Translating (short-circuit) AND TR[e 1 AND e 2] R 1 : = T[e 1]](https://slidetodoc.com/presentation_image_h2/8ff89a42a54b65c65186c6062eff11b2/image-12.jpg)

Translating (short-circuit) AND TR[e 1 AND e 2] R 1 : = T[e 1] Compare 0, R 1 Jump. True _end_label R 2 : = T[e 2] And R 2, R 1 _end_label: (AND can be replaced by Move operation since R 1 is 1) 12

![Translating array and field access TRe 1e 2 R 1 TRe 1 Translating array and field access TR[e 1[e 2]] R 1 : = TR[e 1]](https://slidetodoc.com/presentation_image_h2/8ff89a42a54b65c65186c6062eff11b2/image-13.jpg)

Translating array and field access TR[e 1[e 2]] R 1 : = TR[e 1] R 2 : = TR[e 2] Move. Array R 1[R 2], R 3 Give class type of e 1 need to compute offset of field f TR[e 1. f] Need to identify class type of e 1 from semantic analysis phase R 1 : = TR[e 1] Move. Field R 1. cf, R 3 Constant representing offset of field f in objects of class type of e 1 (we shall discuss object representation soon) 13

![Translating statement block TRs 1 s 2 s N TRs 1 TRs Translating statement block TR[s 1; s 2; … ; s. N] TR[s 1] TR[s](https://slidetodoc.com/presentation_image_h2/8ff89a42a54b65c65186c6062eff11b2/image-14.jpg)

Translating statement block TR[s 1; s 2; … ; s. N] TR[s 1] TR[s 2] TR[s 3] … TR[s. N] 14

![Translating ifthenelse TRif e then s 1 else s 2 Fresh labels generated during Translating if-then-else TR[if (e) then s 1 else s 2] Fresh labels generated during](https://slidetodoc.com/presentation_image_h2/8ff89a42a54b65c65186c6062eff11b2/image-15.jpg)

Translating if-then-else TR[if (e) then s 1 else s 2] Fresh labels generated during translation R 1 : = TR[e] Compare 0, R 1 Jump. True _false_label T[s 1] Jump _end_label _false_label: T[s 2] _end_label: 15

![Translating ifthen TRif e then s Can avoid generating labels unnecessarily R 1 Translating if-then TR[if (e) then s] Can avoid generating labels unnecessarily R 1 :](https://slidetodoc.com/presentation_image_h2/8ff89a42a54b65c65186c6062eff11b2/image-16.jpg)

Translating if-then TR[if (e) then s] Can avoid generating labels unnecessarily R 1 : = TR[e] Compare 0, R 1 Jump. True _end_label TR[s 1] _end_label: 16

![Translating while TRwhile e s testlabel R 1 TRe Compare 0 R Translating while TR[while (e) s] _test_label: R 1 : = TR[e] Compare 0, R](https://slidetodoc.com/presentation_image_h2/8ff89a42a54b65c65186c6062eff11b2/image-17.jpg)

Translating while TR[while (e) s] _test_label: R 1 : = TR[e] Compare 0, R 1 Jump. True _end_label TR[s] Jump _test_label _end_label 17

![Translating callreturn TRC fooe 1 en R 1 TRe 1 formal Translating call/return TR[C. foo(e 1, …, en)] R 1 : = TR[e 1] formal](https://slidetodoc.com/presentation_image_h2/8ff89a42a54b65c65186c6062eff11b2/image-18.jpg)

Translating call/return TR[C. foo(e 1, …, en)] R 1 : = TR[e 1] formal parameter name … Rn : = TR[en] Static. Call C_foo(x 1=R 1, …, xn=Rn), R TR[e 1. foo(e 2)] R 1 : = TR[e 1] R 2 : = TR[e 2] actual argument register Virtual. Call R 1. cfoo(x=R 2), R TR[return e] R 1 : = TR[e] Return R 1 Constant representing offset of method f in dispatch table of class type of e 1 18

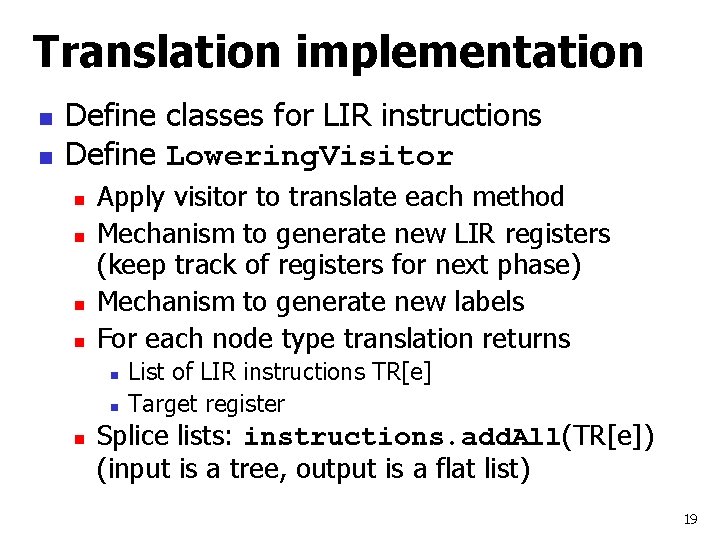

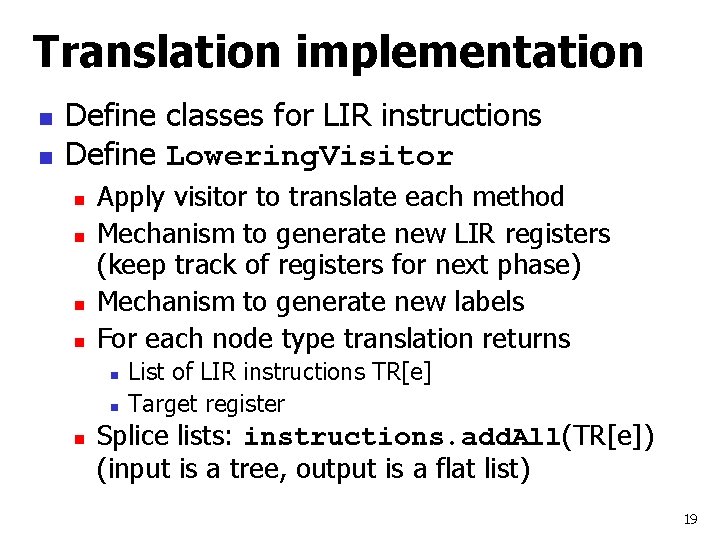

Translation implementation n n Define classes for LIR instructions Define Lowering. Visitor n n Apply visitor to translate each method Mechanism to generate new LIR registers (keep track of registers for next phase) Mechanism to generate new labels For each node type translation returns n n n List of LIR instructions TR[e] Target register Splice lists: instructions. add. All(TR[e]) (input is a tree, output is a flat list) 19

![Example revisited TR x 42 while x 0 xx1 Example revisited TR[ x = 42; while (x > 0) { x=x-1; } ]](https://slidetodoc.com/presentation_image_h2/8ff89a42a54b65c65186c6062eff11b2/image-20.jpg)

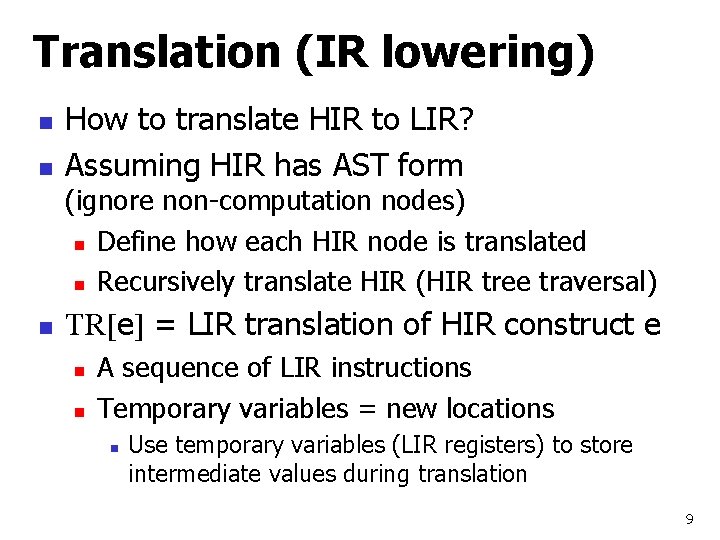

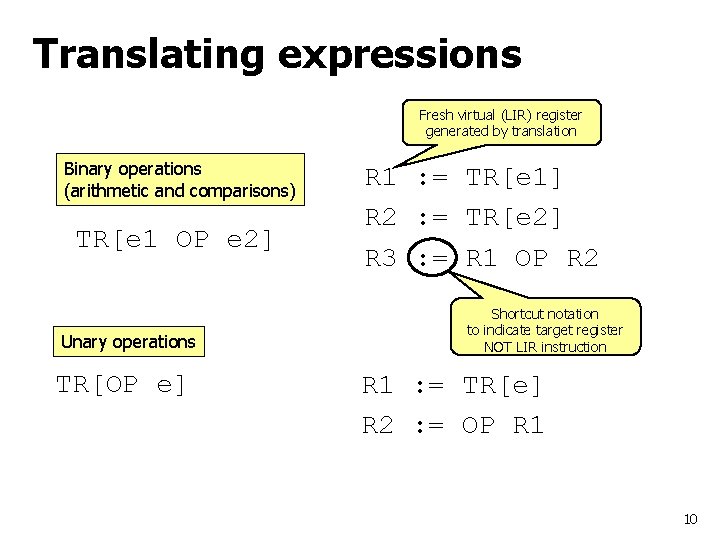

Example revisited TR[ x = 42; while (x > 0) { x=x-1; } ] Move 42, R 1 Move R 1, x _test_label: Move x, R 1 Compare 0, R 1 Jump. LE _end_label TR[x=x-1] Jump _test_label _end_label: TR[x = 42] TR[ while (x > 0) { x=x-1; } ] Move 42, R 1 Move R 1, x _test_label: Move x, R 1 Compare 0, R 1 Jump. LE _end_label Move x, R 1 Move 1, R 2 Sub R 2, R 1 Move R 1, x Jump _test_label _end_label: Move 42, R 1 Move R 1, x TR[ while (x > 0) { x=x-1; } ] spliced list for TR[x=x-1] (actually a DFS walk) 20

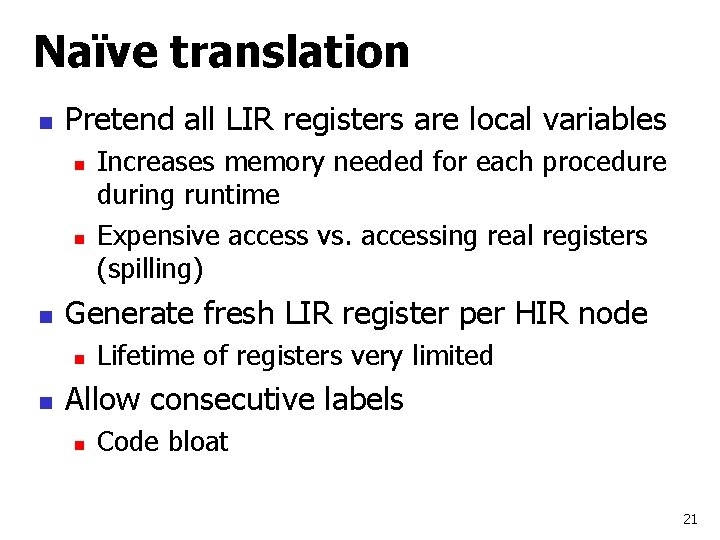

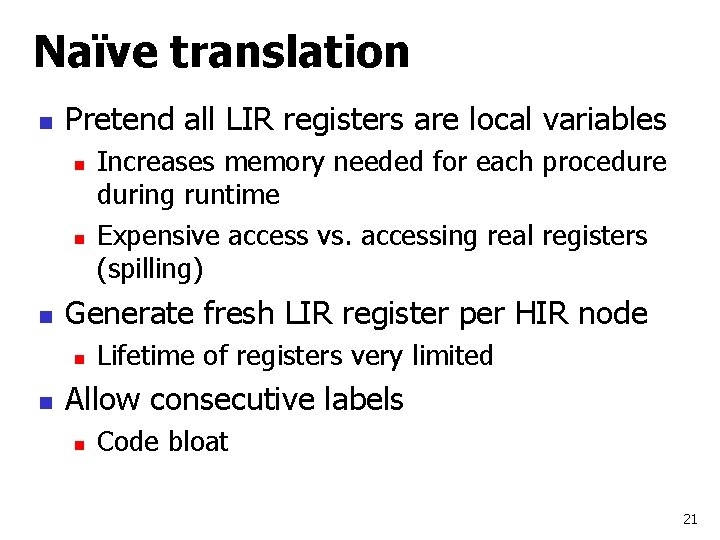

Naïve translation n Pretend all LIR registers are local variables n n n Generate fresh LIR register per HIR node n n Increases memory needed for each procedure during runtime Expensive access vs. accessing real registers (spilling) Lifetime of registers very limited Allow consecutive labels n Code bloat 21

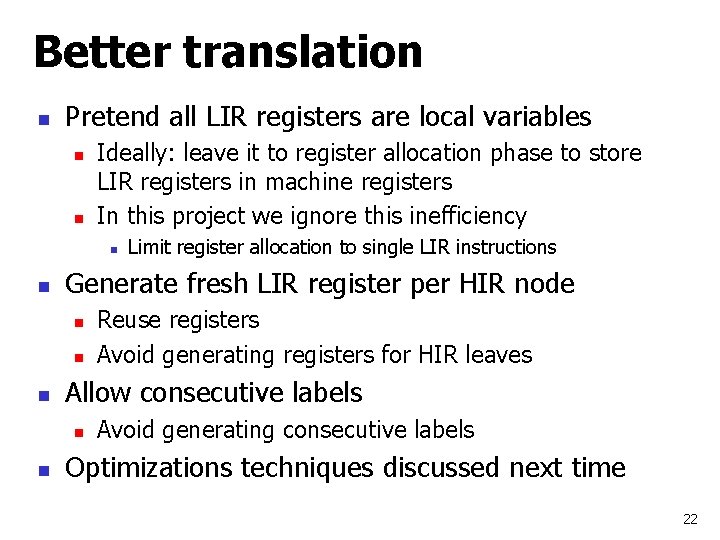

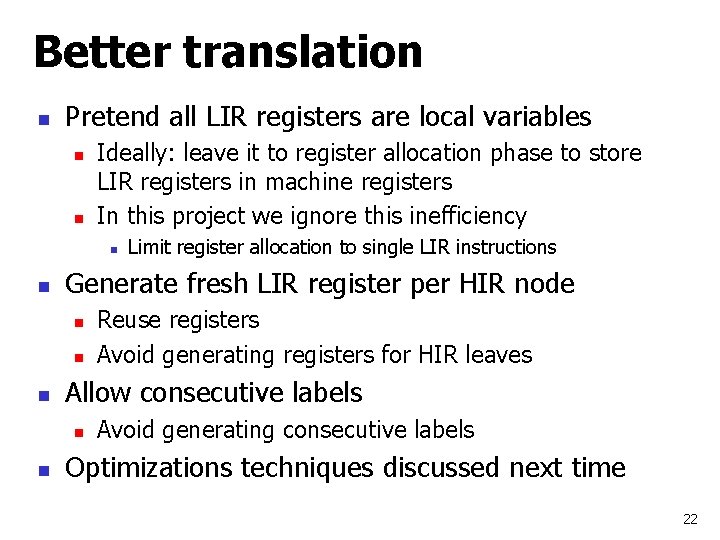

Better translation n Pretend all LIR registers are local variables n n Ideally: leave it to register allocation phase to store LIR registers in machine registers In this project we ignore this inefficiency n n Generate fresh LIR register per HIR node n n n Reuse registers Avoid generating registers for HIR leaves Allow consecutive labels n n Limit register allocation to single LIR instructions Avoid generating consecutive labels Optimizations techniques discussed next time 22

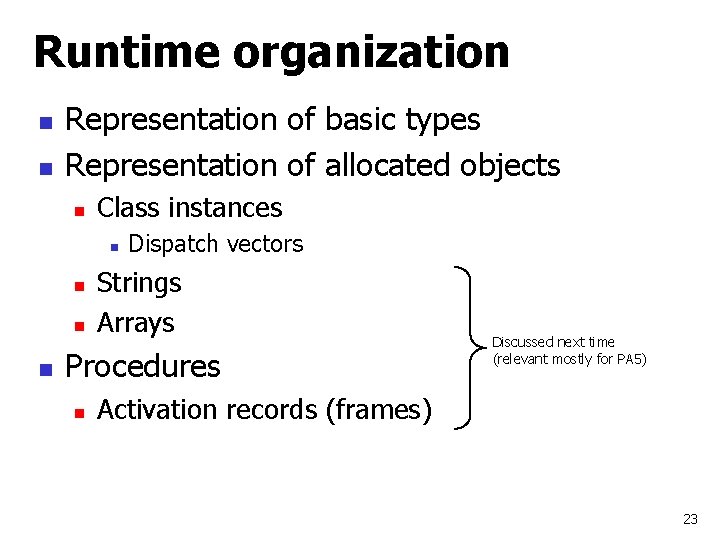

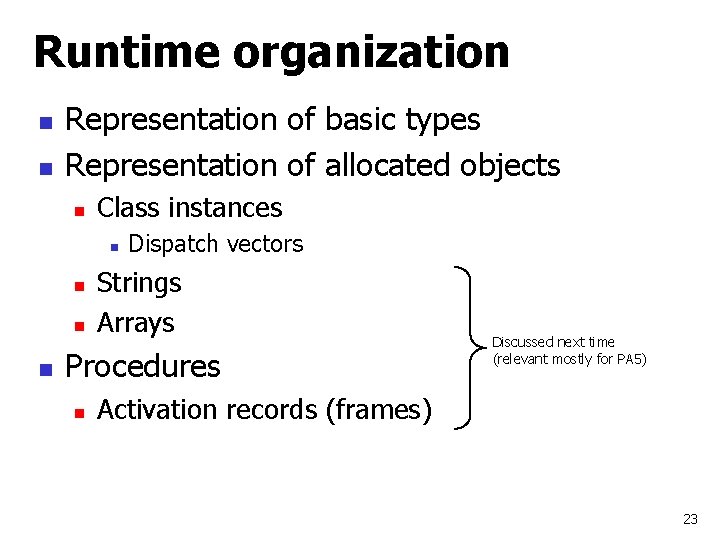

Runtime organization n n Representation of basic types Representation of allocated objects n Class instances n n Dispatch vectors Strings Arrays Procedures n Discussed next time (relevant mostly for PA 5) Activation records (frames) 23

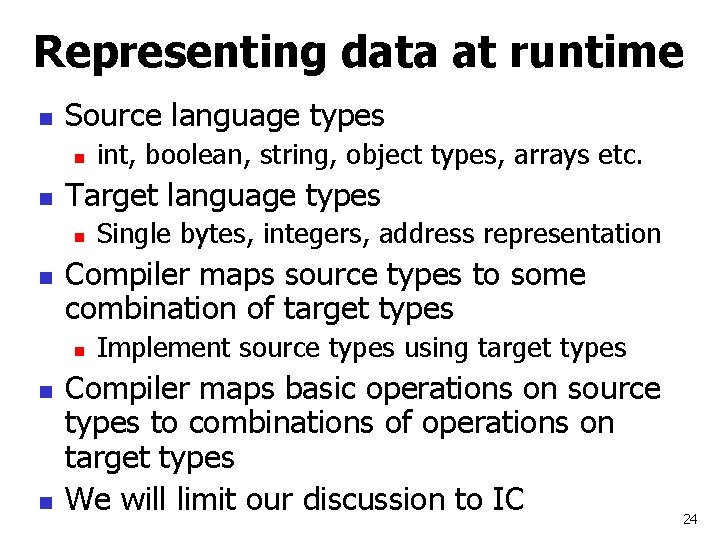

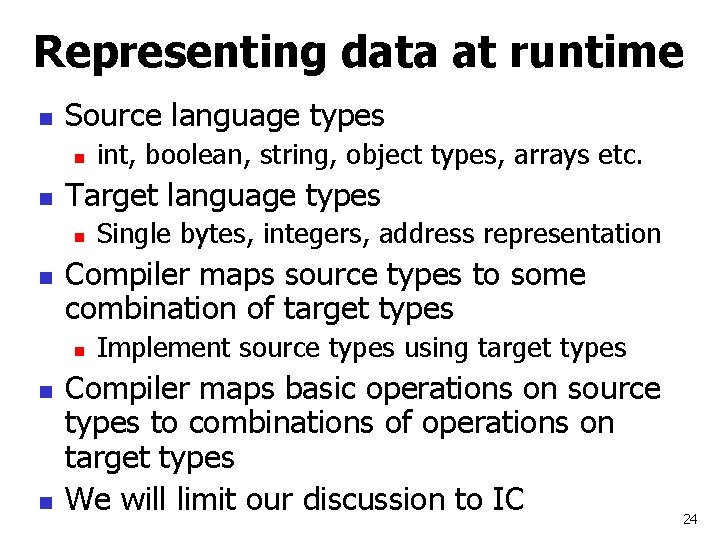

Representing data at runtime n Source language types n n Target language types n n n Single bytes, integers, address representation Compiler maps source types to some combination of target types n n int, boolean, string, object types, arrays etc. Implement source types using target types Compiler maps basic operations on source types to combinations of operations on target types We will limit our discussion to IC 24

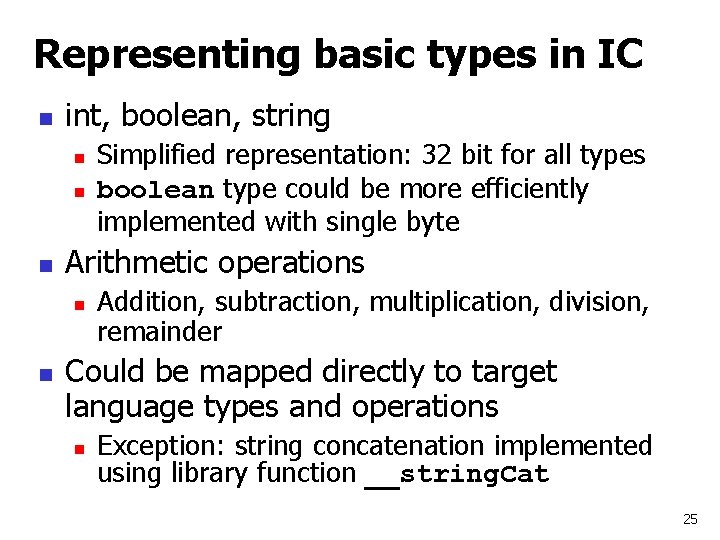

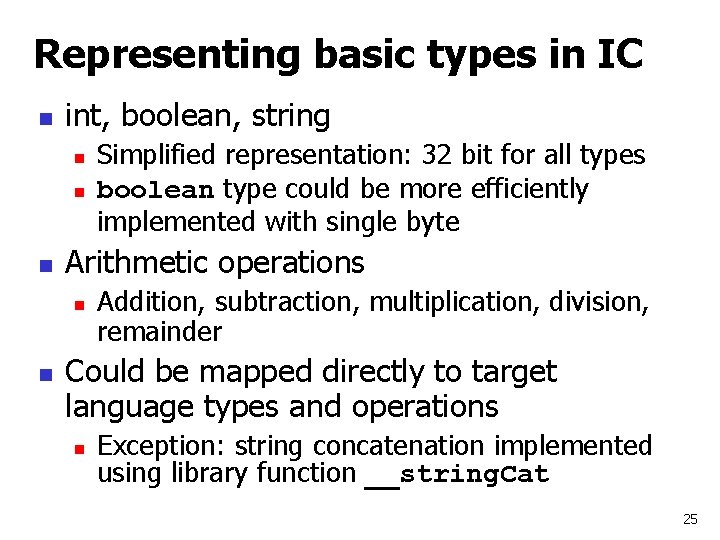

Representing basic types in IC n int, boolean, string n n n Arithmetic operations n n Simplified representation: 32 bit for all types boolean type could be more efficiently implemented with single byte Addition, subtraction, multiplication, division, remainder Could be mapped directly to target language types and operations n Exception: string concatenation implemented using library function __string. Cat 25

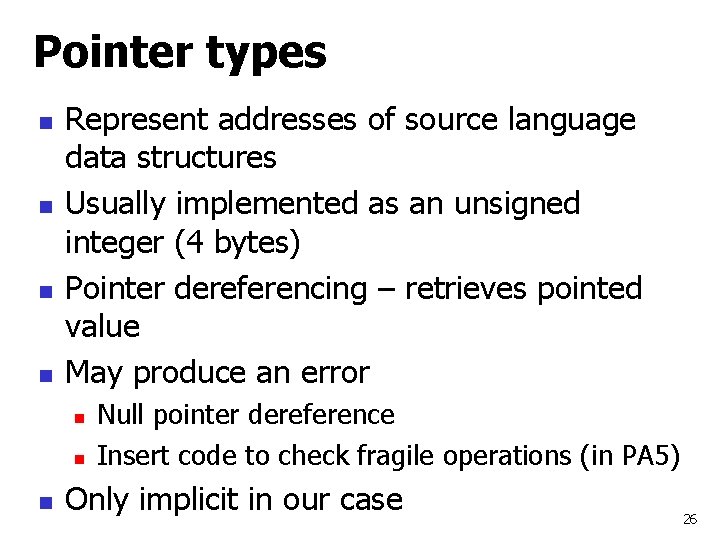

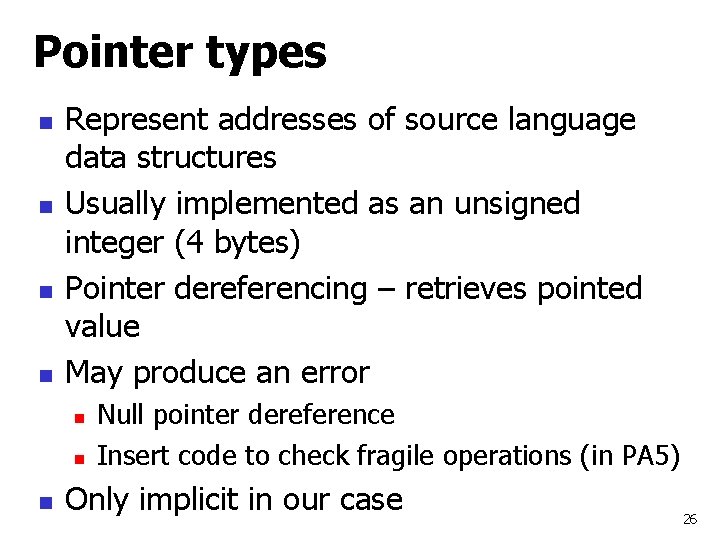

Pointer types n n Represent addresses of source language data structures Usually implemented as an unsigned integer (4 bytes) Pointer dereferencing – retrieves pointed value May produce an error n n n Null pointer dereference Insert code to check fragile operations (in PA 5) Only implicit in our case 26

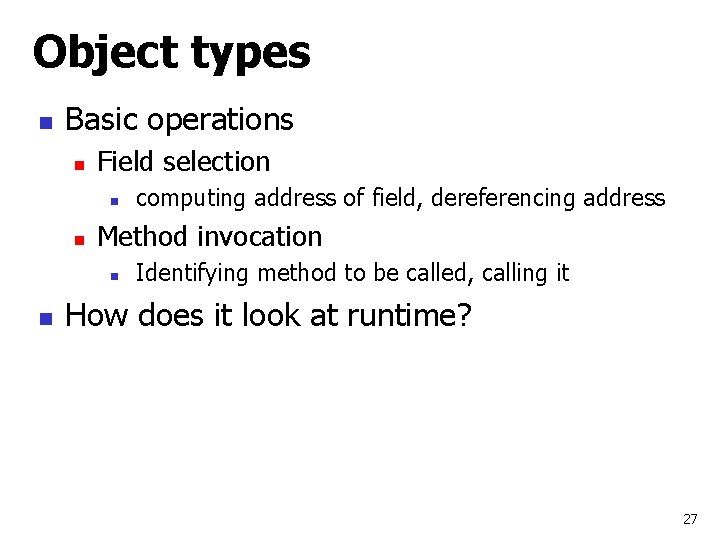

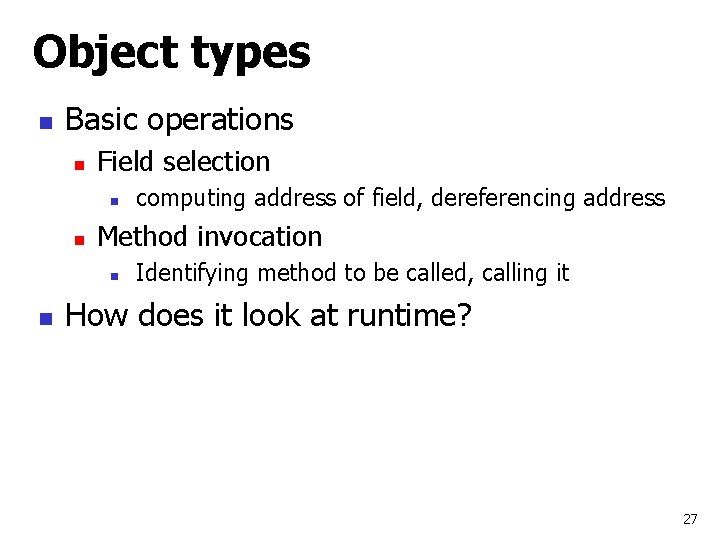

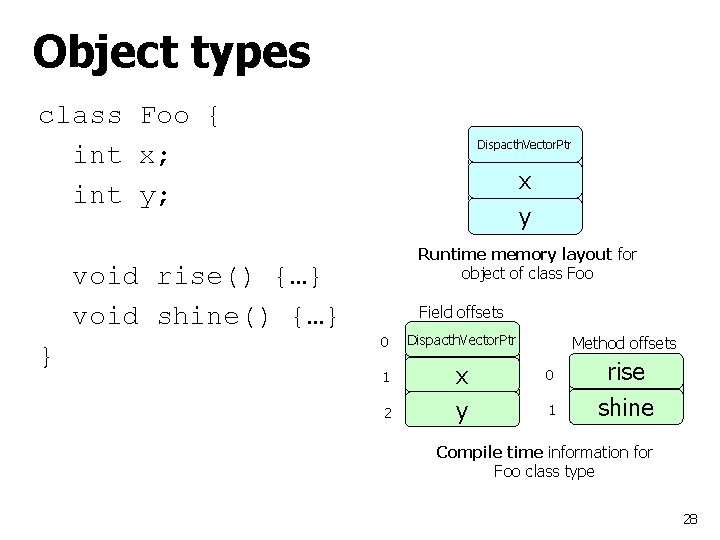

Object types n Basic operations n Field selection n n Method invocation n n computing address of field, dereferencing address Identifying method to be called, calling it How does it look at runtime? 27

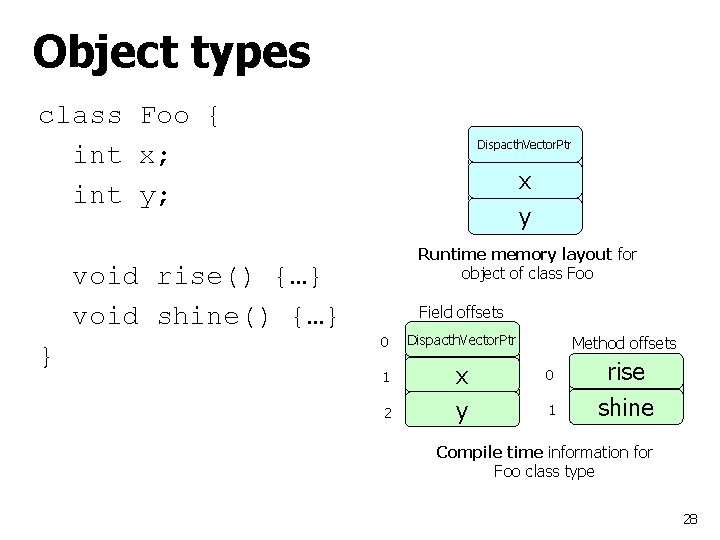

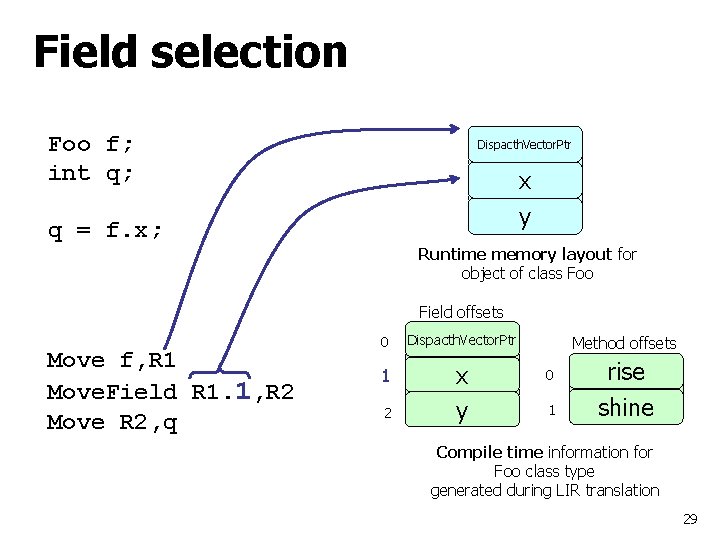

Object types class Foo { int x; int y; Dispacth. Vector. Ptr x y Runtime memory layout for object of class Foo void rise() {…} void shine() {…} } Field offsets 0 1 2 Dispacth. Vector. Ptr x y Method offsets 0 1 rise shine Compile time information for Foo class type 28

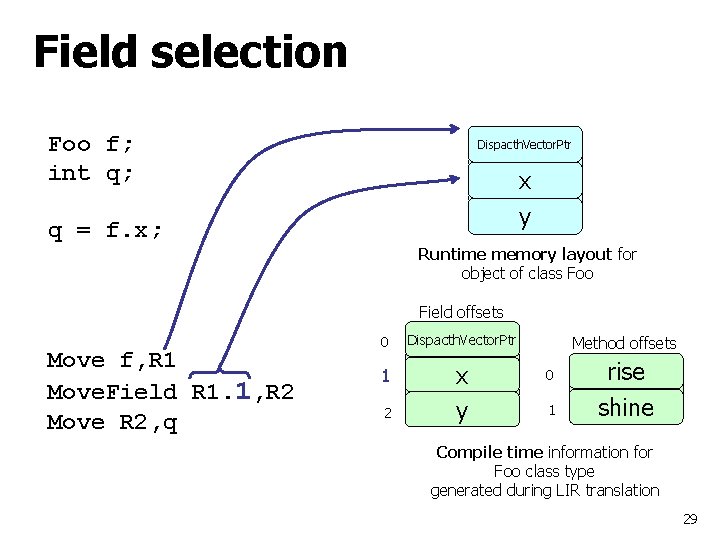

Field selection Foo f; int q; Dispacth. Vector. Ptr x y q = f. x; Runtime memory layout for object of class Foo Field offsets Move f, R 1 Move. Field R 1. 1, R 2 Move R 2, q 0 Dispacth. Vector. Ptr 1 x y 2 Method offsets 0 1 rise shine Compile time information for Foo class type generated during LIR translation 29

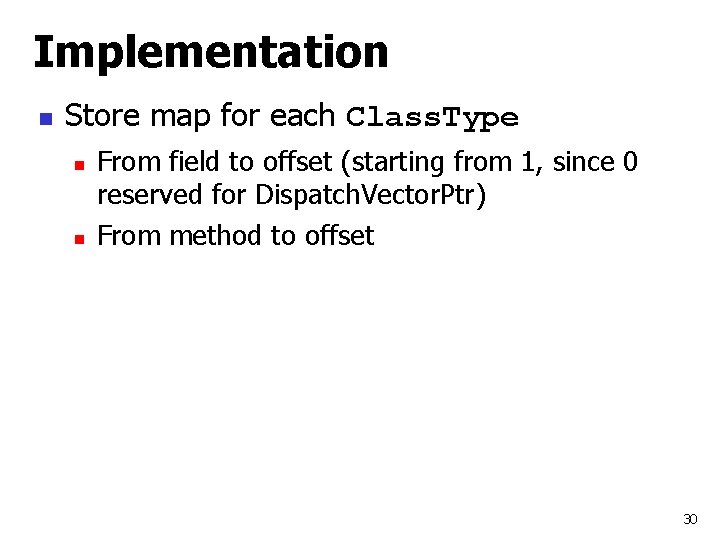

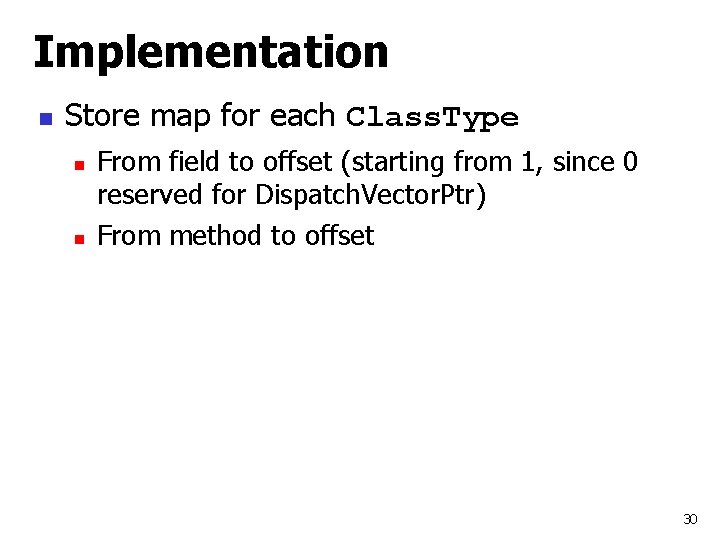

Implementation n Store map for each Class. Type n n From field to offset (starting from 1, since 0 reserved for Dispatch. Vector. Ptr) From method to offset 30

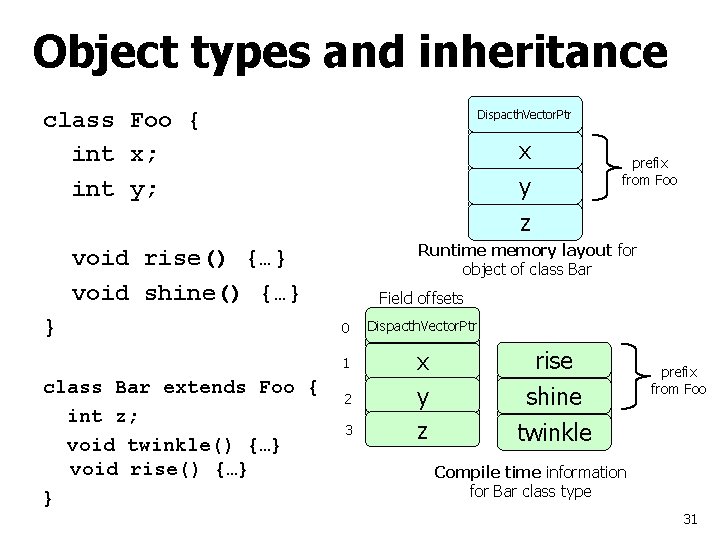

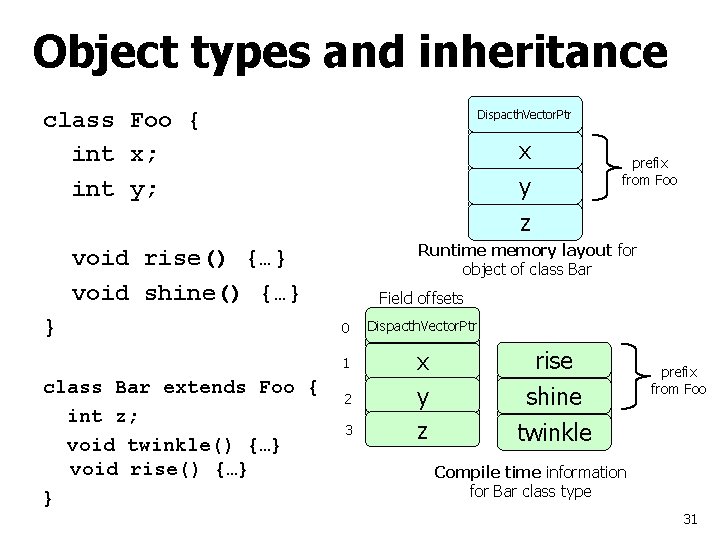

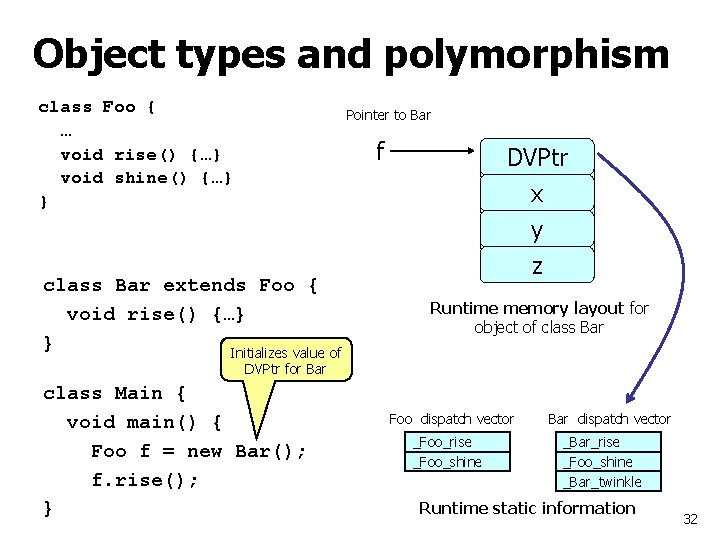

Object types and inheritance Dispacth. Vector. Ptr class Foo { int x; int y; x y z Runtime memory layout for object of class Bar void rise() {…} void shine() {…} } Field offsets 0 1 class Bar extends Foo { int z; void twinkle() {…} void rise() {…} } prefix from Foo 2 3 Dispacth. Vector. Ptr x y z rise shine prefix from Foo twinkle Compile time information for Bar class type 31

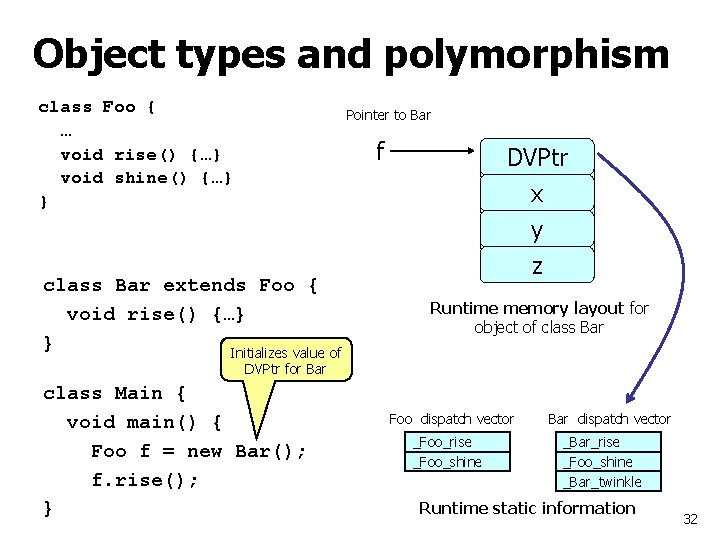

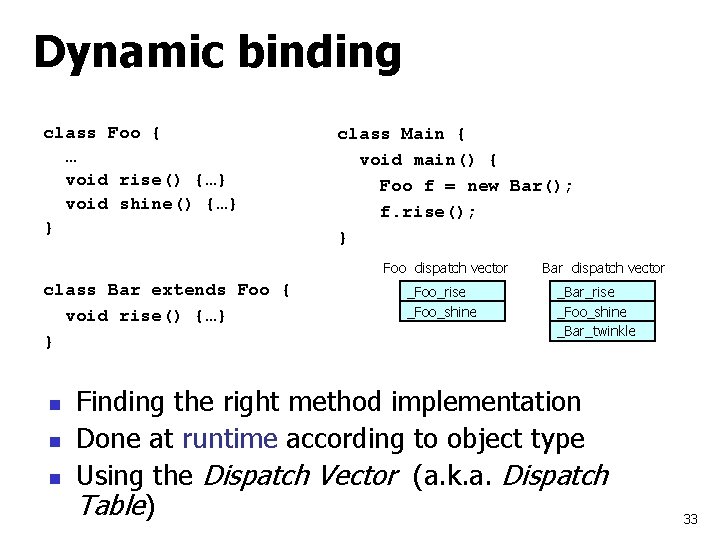

Object types and polymorphism class Foo { … void rise() {…} void shine() {…} } Pointer to Bar f class Bar extends Foo { void rise() {…} } Initializes value of DVPtr x y z Runtime memory layout for object of class Bar DVPtr for Bar class Main { void main() { Foo f = new Bar(); f. rise(); } Foo dispatch vector _Foo_rise _Foo_shine Bar dispatch vector _Bar_rise _Foo_shine _Bar_twinkle Runtime static information 32

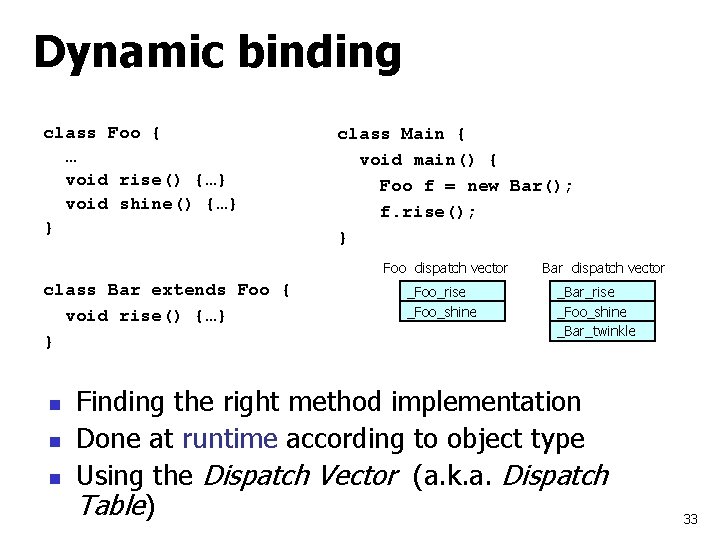

Dynamic binding class Foo { … void rise() {…} void shine() {…} } class Main { void main() { Foo f = new Bar(); f. rise(); } Foo dispatch vector class Bar extends Foo { void rise() {…} } n n n _Foo_rise _Foo_shine Bar dispatch vector _Bar_rise _Foo_shine _Bar_twinkle Finding the right method implementation Done at runtime according to object type Using the Dispatch Vector (a. k. a. Dispatch Table) 33

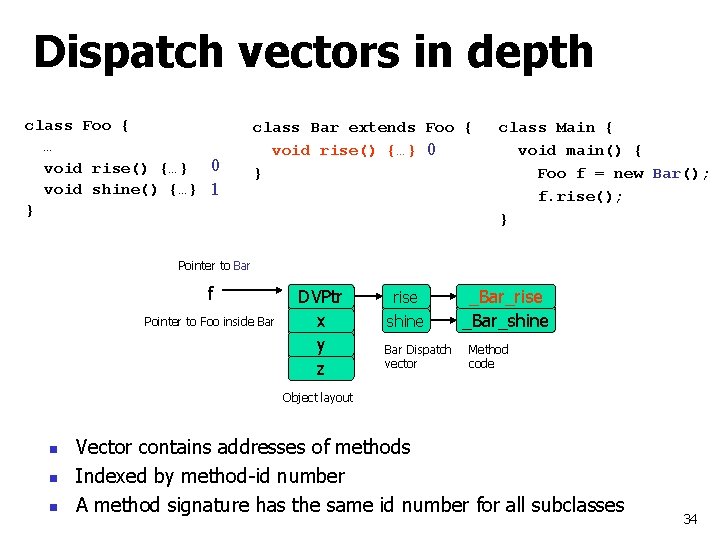

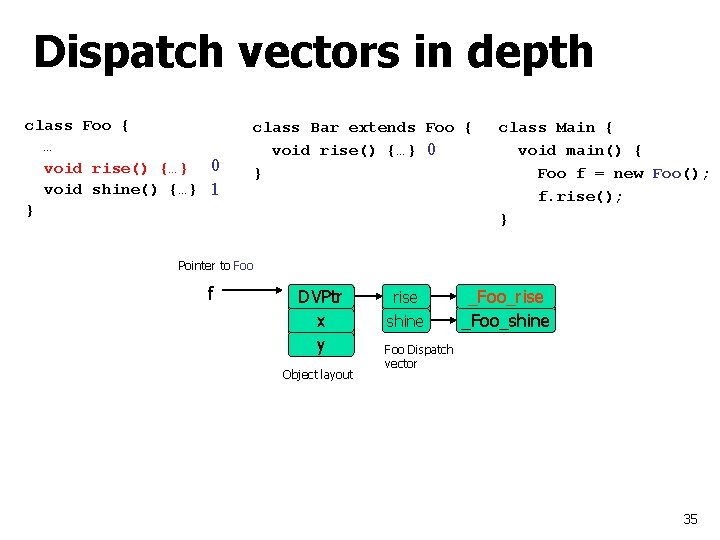

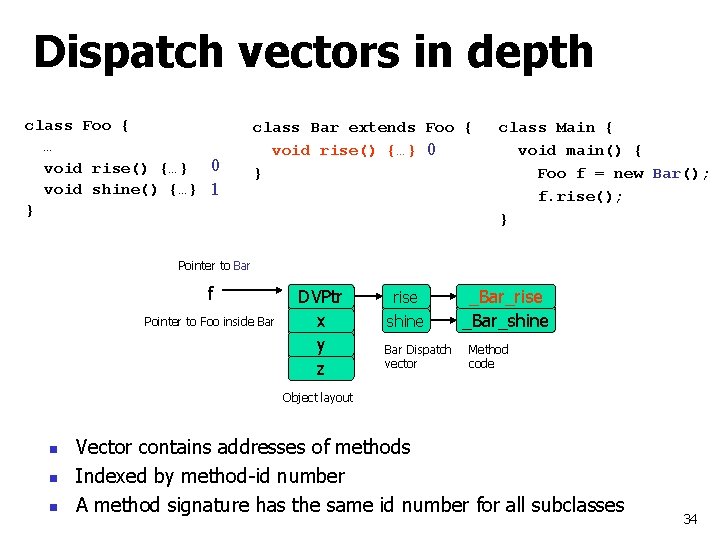

Dispatch vectors in depth class Foo { … void rise() {…} 0 void shine() {…} 1 } class Bar extends Foo { void rise() {…} 0 } class Main { void main() { Foo f = new Bar(); f. rise(); } Pointer to Bar f Pointer to Foo inside Bar DVPtr x y z rise shine Bar Dispatch vector _Bar_rise _Bar_shine Method code Object layout n n n Vector contains addresses of methods Indexed by method-id number A method signature has the same id number for all subclasses 34

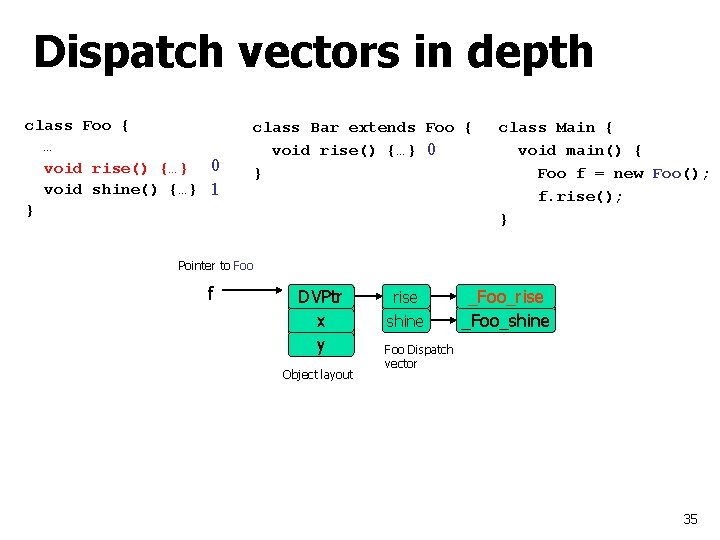

Dispatch vectors in depth class Foo { … void rise() {…} 0 void shine() {…} 1 } class Bar extends Foo { void rise() {…} 0 } class Main { void main() { Foo f = new Foo(); f. rise(); } Pointer to Foo f DVPtr x y Object layout rise shine _Foo_rise _Foo_shine Foo Dispatch vector 35

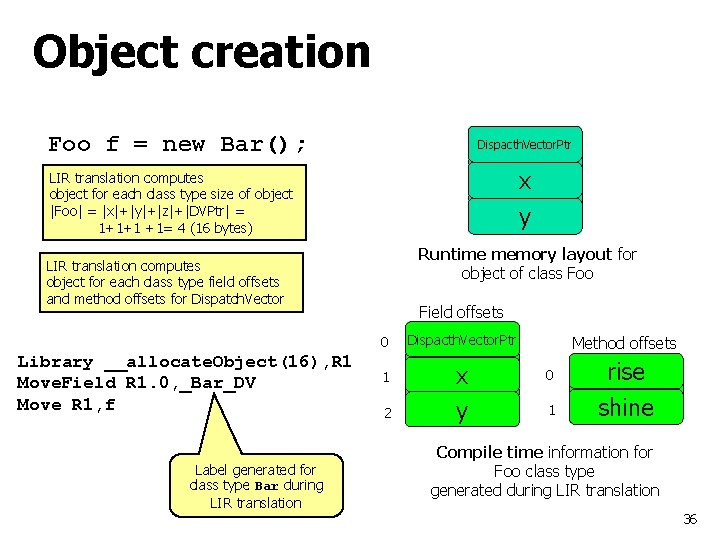

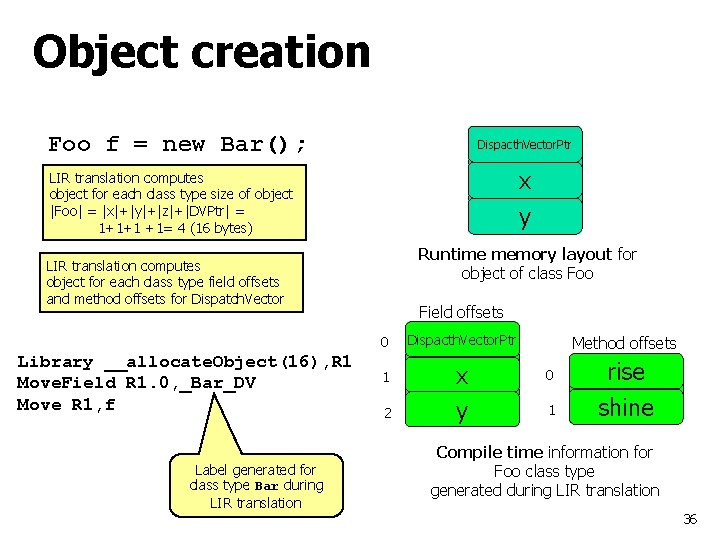

Object creation Foo f = new Bar(); Dispacth. Vector. Ptr x y LIR translation computes object for each class type size of object |Foo| = |x|+|y|+|z|+|DVPtr| = 1+1+1 +1= 4 (16 bytes) Runtime memory layout for object of class Foo LIR translation computes object for each class type field offsets and method offsets for Dispatch. Vector Field offsets 0 Library __allocate. Object(16), R 1 Move. Field R 1. 0, _Bar_DV Move R 1, f Label generated for class type Bar during LIR translation 1 2 Dispacth. Vector. Ptr x y Method offsets 0 1 rise shine Compile time information for Foo class type generated during LIR translation 36

See you next week 37