Wild Circuits Investigating the Limits of MINMAXAVG Circuits

![Definitions: MIN/MAX/AVG Circuits l Settings of the gate outputs from the interval [0, 1] Definitions: MIN/MAX/AVG Circuits l Settings of the gate outputs from the interval [0, 1]](https://slidetodoc.com/presentation_image/50a0d5ec1fc59464ff8667c2861d72c1/image-3.jpg)

![Caveats l Assumptions: 1. 2. 3. l All values above [below] threshold are equal Caveats l Assumptions: 1. 2. 3. l All values above [below] threshold are equal](https://slidetodoc.com/presentation_image/50a0d5ec1fc59464ff8667c2861d72c1/image-11.jpg)

- Slides: 23

Wild Circuits Investigating the Limits of MIN/MAX/AVG Circuits Brendan Juba Faculty Advisor: Manuel Blum Graduate Mentor: Ryan Williams

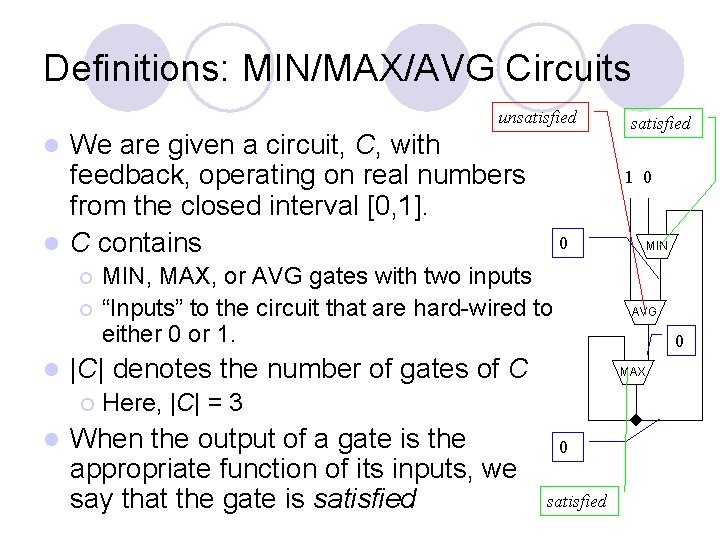

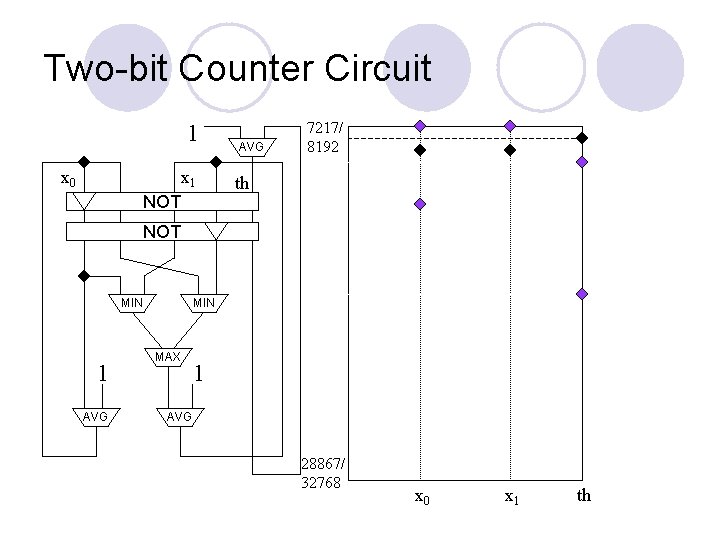

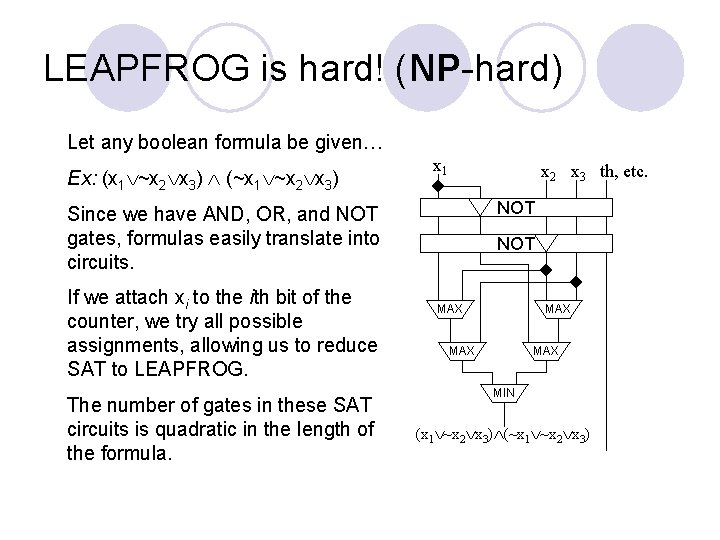

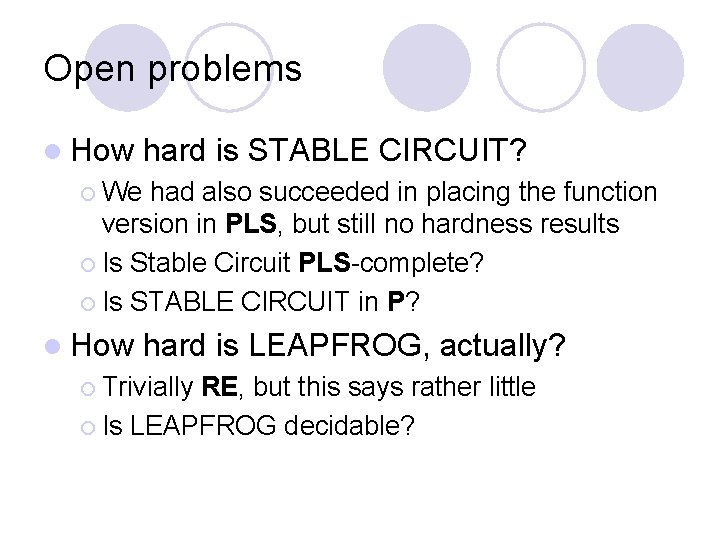

Definitions: MIN/MAX/AVG Circuits unsatisfied We are given a circuit, C, with feedback, operating on real numbers from the closed interval [0, 1]. l C contains satisfied l 1 0 0 MIN, MAX, or AVG gates with two inputs ¡ “Inputs” to the circuit that are hard-wired to either 0 or 1. MIN ¡ l 0 |C| denotes the number of gates of C ¡ l AVG MAX Here, |C| = 3 When the output of a gate is the appropriate function of its inputs, we say that the gate is satisfied 0 satisfied

![Definitions MINMAXAVG Circuits l Settings of the gate outputs from the interval 0 1 Definitions: MIN/MAX/AVG Circuits l Settings of the gate outputs from the interval [0, 1]](https://slidetodoc.com/presentation_image/50a0d5ec1fc59464ff8667c2861d72c1/image-3.jpg)

Definitions: MIN/MAX/AVG Circuits l Settings of the gate outputs from the interval [0, 1] are value vectors ¡ ¡ A value vector for C, v [0, 1]|C| The ith entry, vi, is the output of the ith gate. l l ¡ MIN This is an implicit ordering of the gates of C We may also consider an update function, F: [0, 1]|C| ¡ 1 0 A single-gate update function replaces the output of a single designated gate with the correct output value. We will call iterating over the single gate update functions “gate-by-gate update” AVG MAX

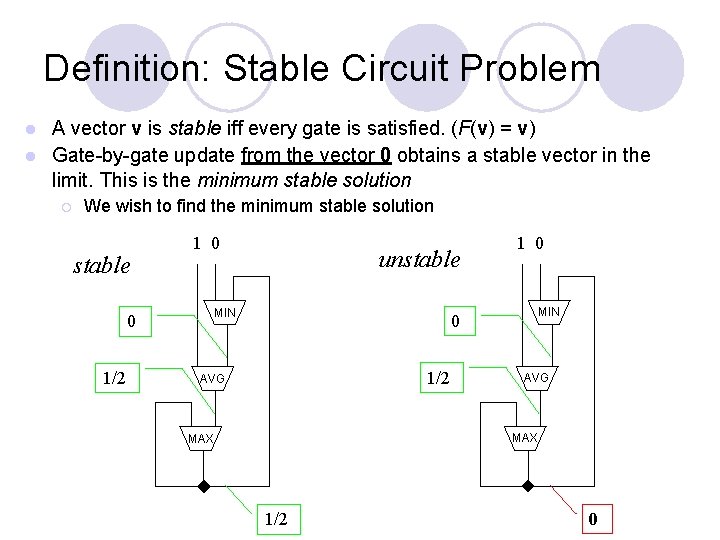

Definition: Stable Circuit Problem A vector v is stable iff every gate is satisfied. (F(v) = v) l Gate-by-gate update from the vector 0 obtains a stable vector in the limit. This is the minimum stable solution l ¡ We wish to find the minimum stable solution stable 1 0 MIN 0 1/2 unstable 1 0 MIN 0 1/2 AVG MAX 1/2 0

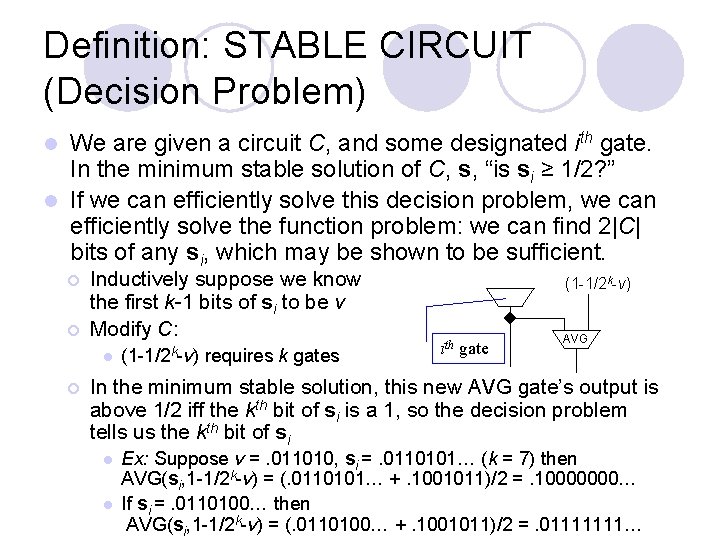

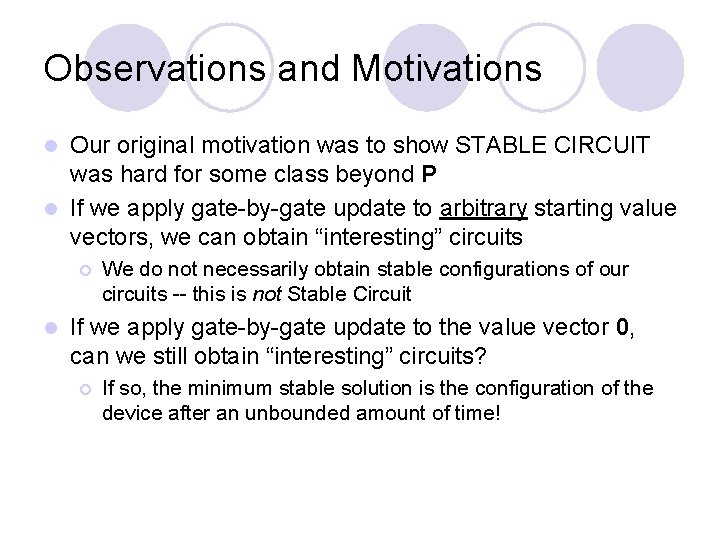

Definition: STABLE CIRCUIT (Decision Problem) We are given a circuit C, and some designated ith gate. In the minimum stable solution of C, s, “is si ≥ 1/2? ” l If we can efficiently solve this decision problem, we can efficiently solve the function problem: we can find 2|C| bits of any si, which may be shown to be sufficient. l ¡ ¡ Inductively suppose we know the first k-1 bits of si to be v Modify C: l ¡ (1 -1/2 k-v) requires k gates (1 -1/2 k-v) ith gate AVG In the minimum stable solution, this new AVG gate’s output is above 1/2 iff the kth bit of si is a 1, so the decision problem tells us the kth bit of si l l Ex: Suppose v =. 011010, si =. 0110101… (k = 7) then AVG(si, 1 -1/2 k-v) = (. 0110101… +. 1001011)/2 =. 10000000… If si =. 0110100… then AVG(si, 1 -1/2 k-v) = (. 0110100… +. 1001011)/2 =. 01111111…

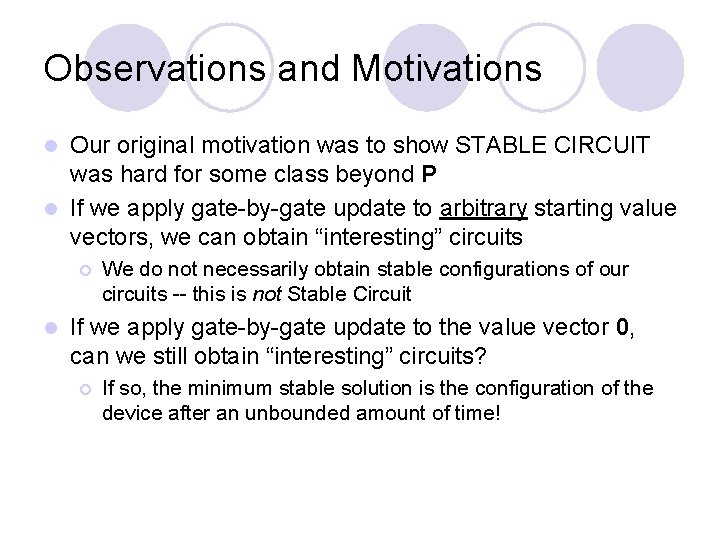

Previously, on STABLE CIRCUIT l STABLE CIRCUIT is in NP co-NP (Condon, 1992) ¡ We can modify our circuits to have a unique solution that is identical to the minimum stable solution up to the 2|C|th bit ¡ This unique solution can be guessed and checked l STABLE CIRCUIT is P-hard ¡ MONOTONE CIRCUIT is a special case

Observations and Motivations Our original motivation was to show STABLE CIRCUIT was hard for some class beyond P l If we apply gate-by-gate update to arbitrary starting value vectors, we can obtain “interesting” circuits l ¡ l We do not necessarily obtain stable configurations of our circuits -- this is not Stable Circuit If we apply gate-by-gate update to the value vector 0, can we still obtain “interesting” circuits? ¡ If so, the minimum stable solution is the configuration of the device after an unbounded amount of time!

Can we obtain “interesting” circuits starting from 0? YES

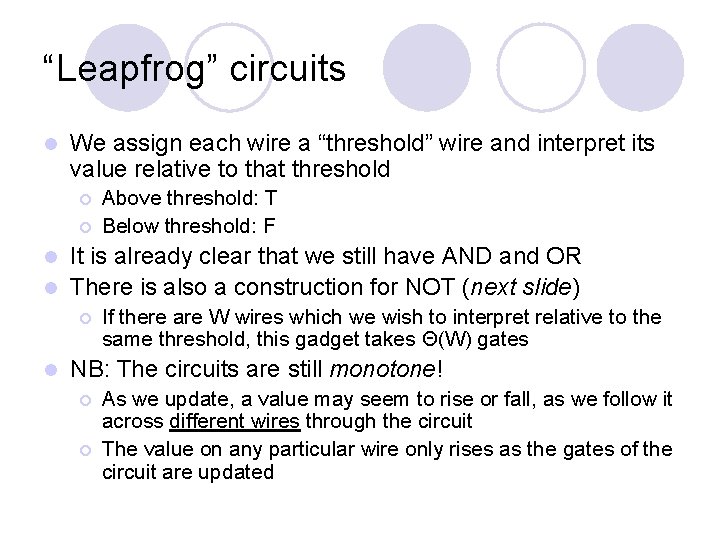

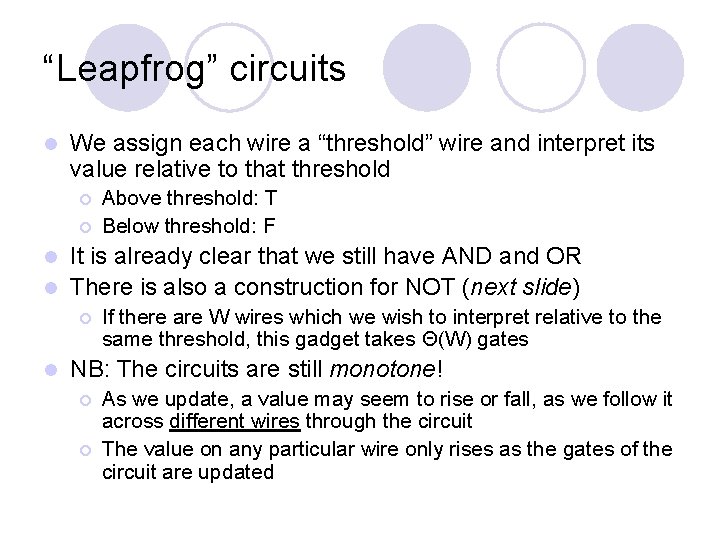

“Leapfrog” circuits l We assign each wire a “threshold” wire and interpret its value relative to that threshold ¡ ¡ Above threshold: T Below threshold: F It is already clear that we still have AND and OR l There is also a construction for NOT (next slide) l ¡ l If there are W wires which we wish to interpret relative to the same threshold, this gadget takes Θ(W) gates NB: The circuits are still monotone! ¡ ¡ As we update, a value may seem to rise or fall, as we follow it across different wires through the circuit The value on any particular wire only rises as the gates of the circuit are updated

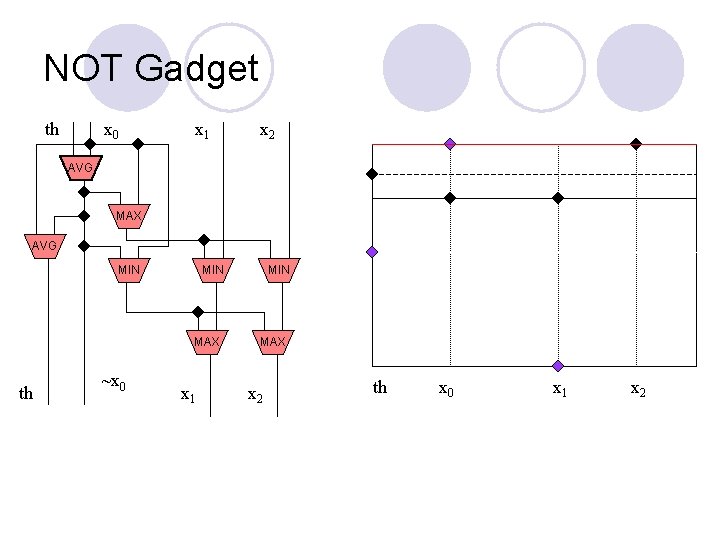

NOT Gadget th x 0 x 1 x 2 AVG MAX AVG MIN MAX th ~x 0 x 1 MIN MAX x 2 th x 0 x 1 x 2

![Caveats l Assumptions 1 2 3 l All values above below threshold are equal Caveats l Assumptions: 1. 2. 3. l All values above [below] threshold are equal](https://slidetodoc.com/presentation_image/50a0d5ec1fc59464ff8667c2861d72c1/image-11.jpg)

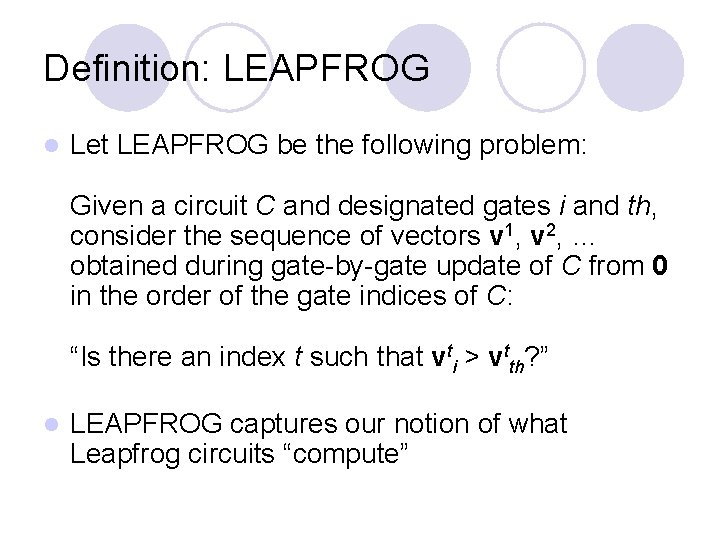

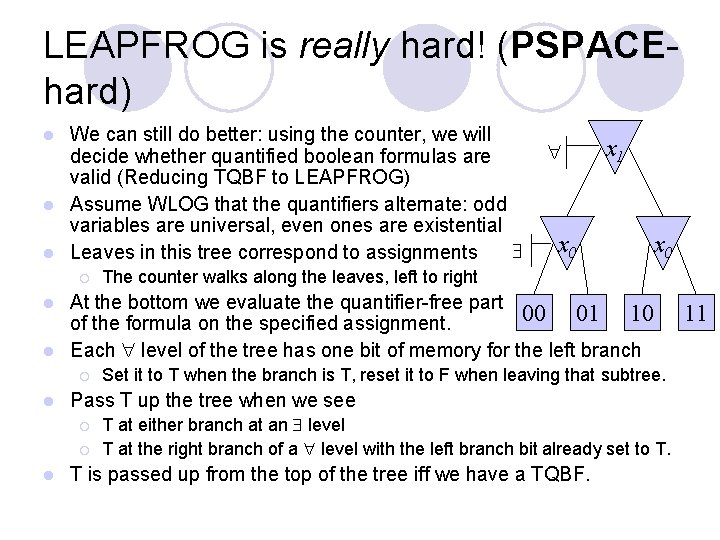

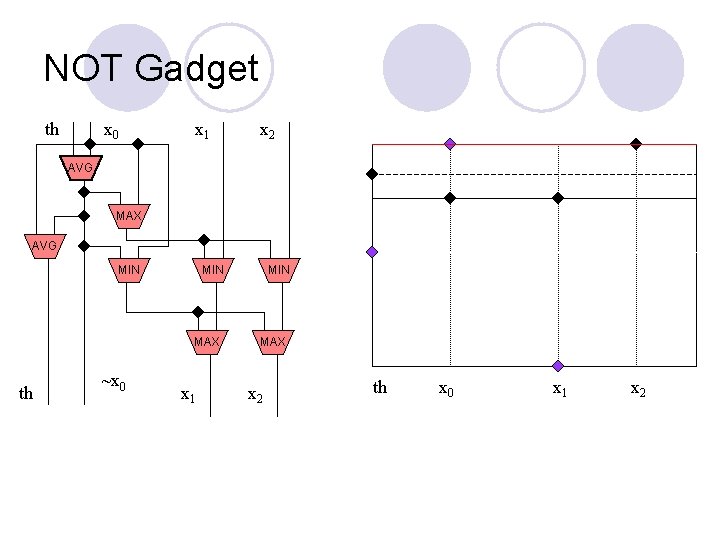

Caveats l Assumptions: 1. 2. 3. l All values above [below] threshold are equal th has a value distinct from all other inputs We may specify the update order for the gates of the circuit Take each in turn: 1. 2. Everything starts from zero and the property is preserved by our AND, OR, and NOT gates We can push th above zero by means of an AVG gate l 3. With feedback, we must also pass the other wires through AVG gates to preserve relative values Update order doesn’t change the solution we approach

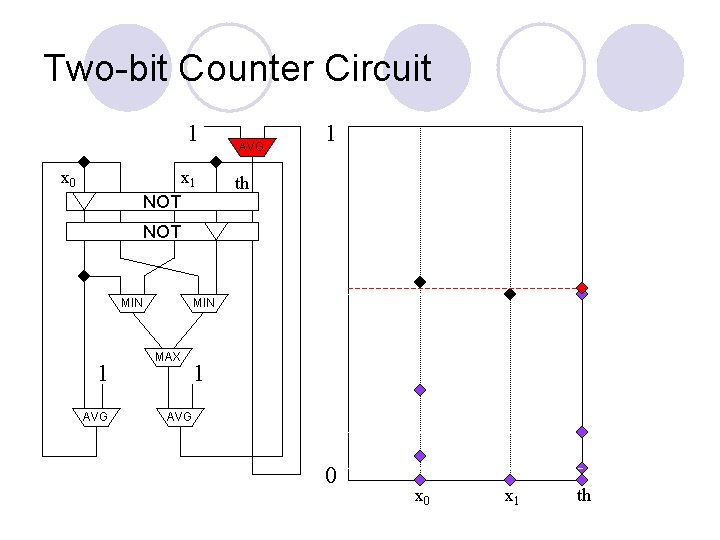

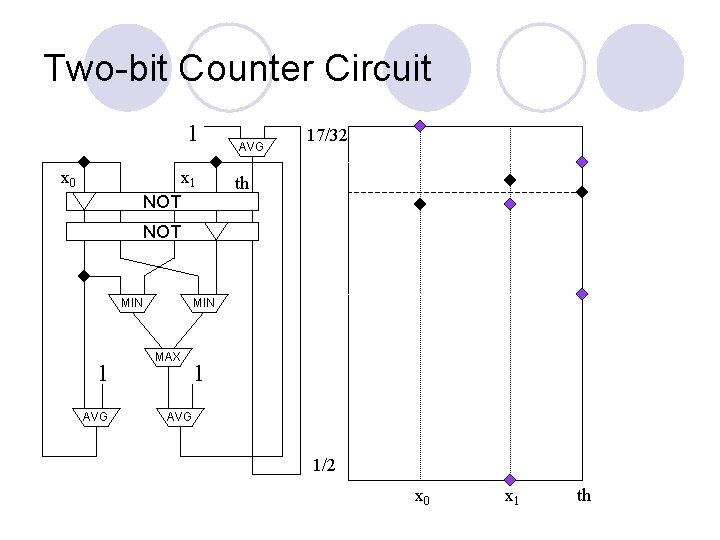

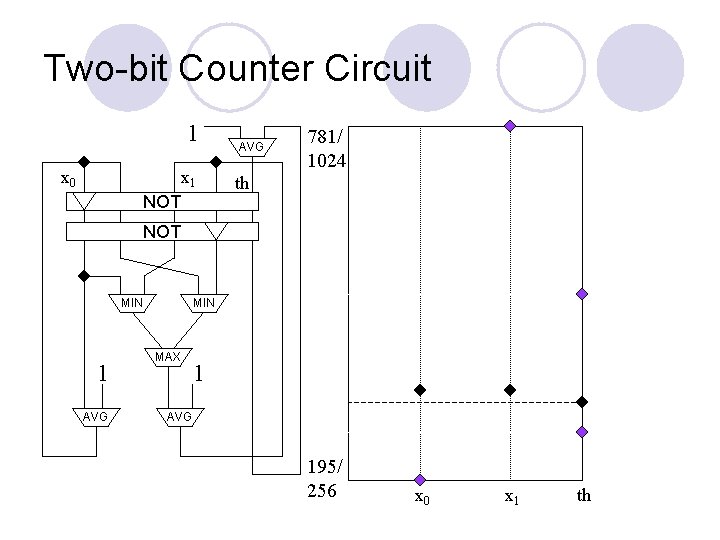

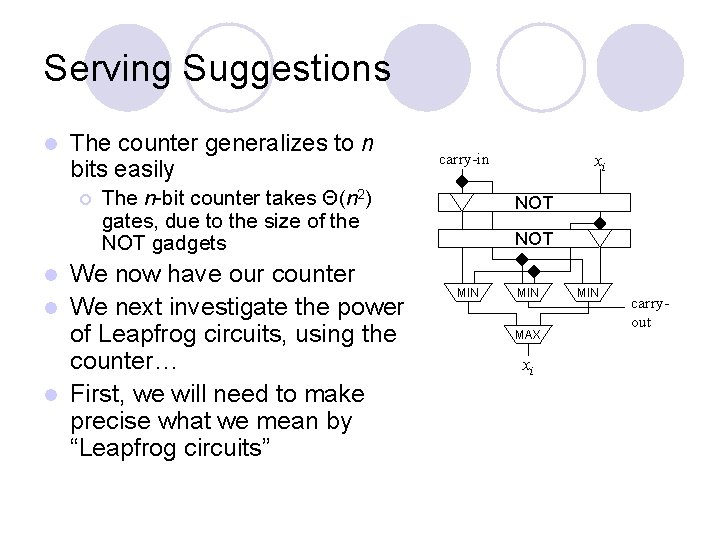

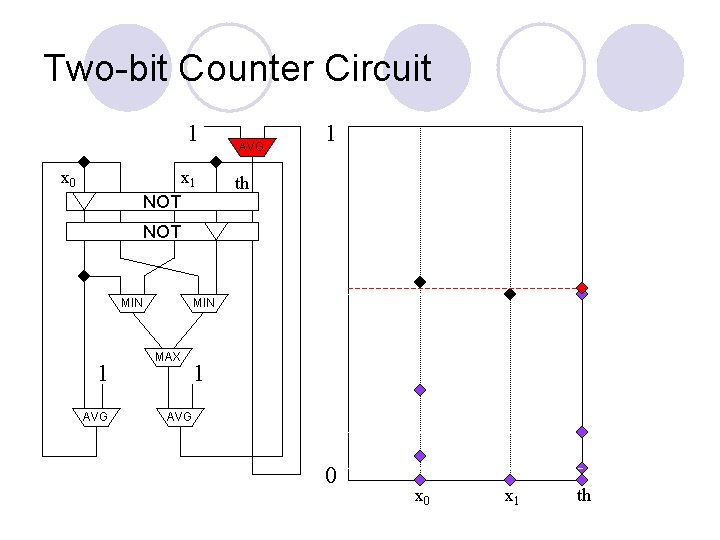

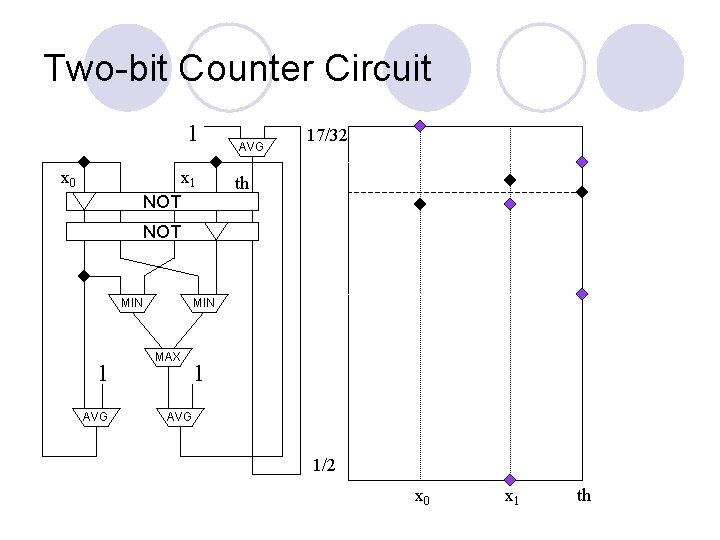

Two-bit Counter Circuit 1 x 0 x 1 NOT AVG 1 th NOT MIN 1 AVG MIN MAX 1 AVG 0 x 1 th

Two-bit Counter Circuit 1 x 0 x 1 NOT AVG 17/32 th NOT MIN 1 AVG MIN MAX 1 AVG 1/2 x 0 x 1 th

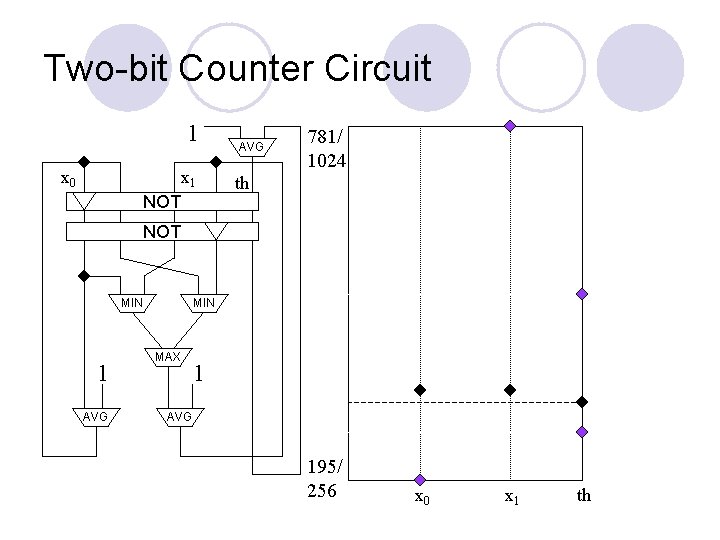

Two-bit Counter Circuit 1 x 0 x 1 NOT AVG 781/ 1024 th NOT MIN 1 AVG MIN MAX 1 AVG 195/ 256 x 0 x 1 th

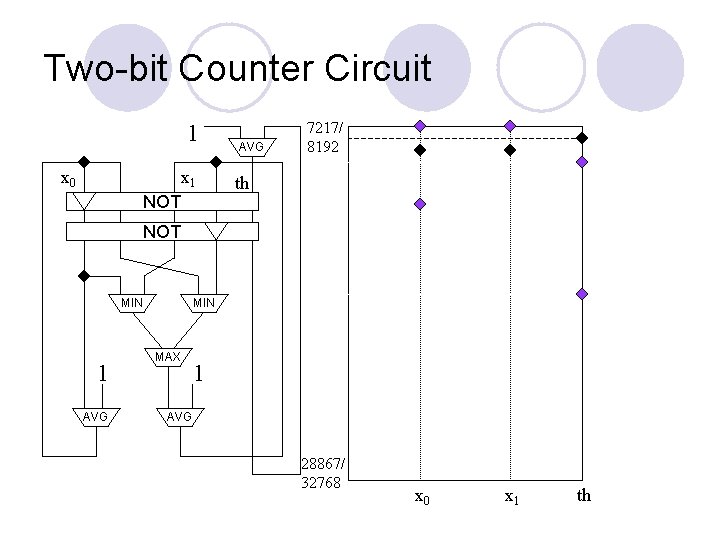

Two-bit Counter Circuit 1 x 0 x 1 NOT AVG 7217/ 8192 th NOT MIN 1 AVG MIN MAX 1 AVG 28867/ 32768 x 0 x 1 th

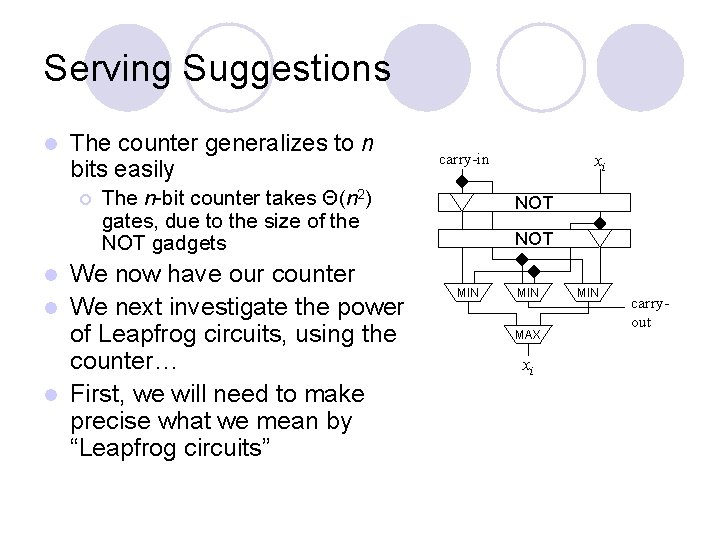

Serving Suggestions l The counter generalizes to n bits easily ¡ The n-bit counter takes Θ(n 2) gates, due to the size of the NOT gadgets We now have our counter l We next investigate the power of Leapfrog circuits, using the counter… l First, we will need to make precise what we mean by “Leapfrog circuits” l carry-in xi NOT MIN MAX xi MIN carryout

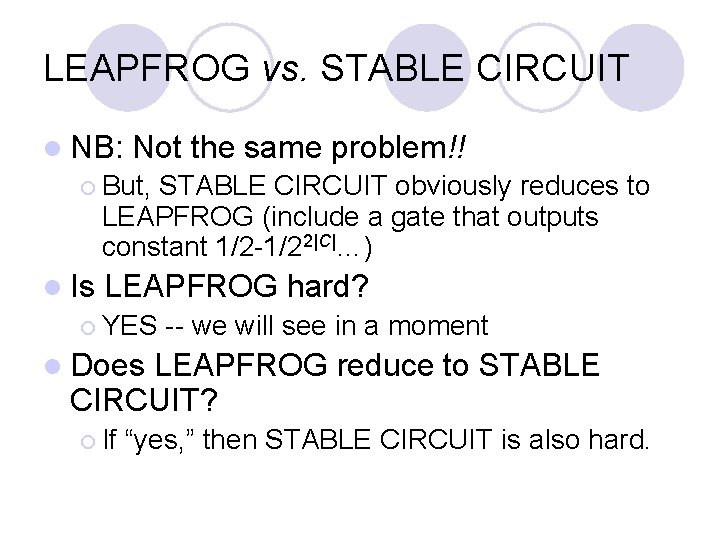

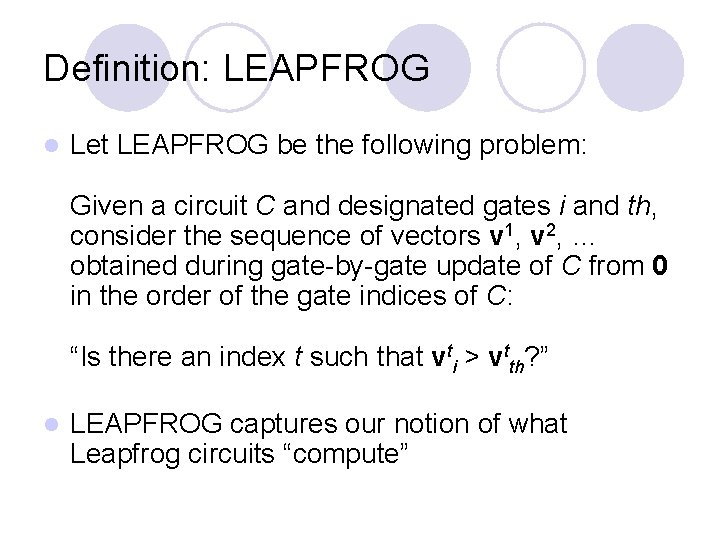

Definition: LEAPFROG l Let LEAPFROG be the following problem: Given a circuit C and designated gates i and th, consider the sequence of vectors v 1, v 2, … obtained during gate-by-gate update of C from 0 in the order of the gate indices of C: “Is there an index t such that vti > vtth? ” l LEAPFROG captures our notion of what Leapfrog circuits “compute”

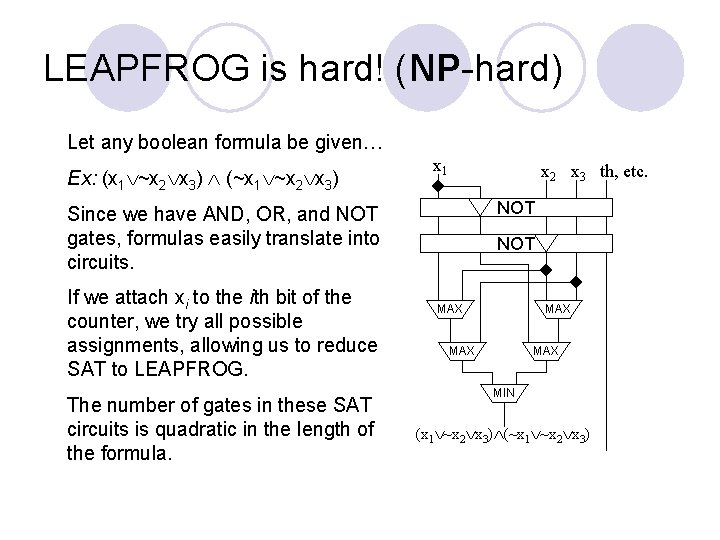

LEAPFROG vs. STABLE CIRCUIT l NB: Not the same problem!! ¡ But, STABLE CIRCUIT obviously reduces to LEAPFROG (include a gate that outputs constant 1/2 -1/22|C|…) l Is LEAPFROG hard? ¡ YES -- we will see in a moment l Does LEAPFROG reduce to STABLE CIRCUIT? ¡ If “yes, ” then STABLE CIRCUIT is also hard.

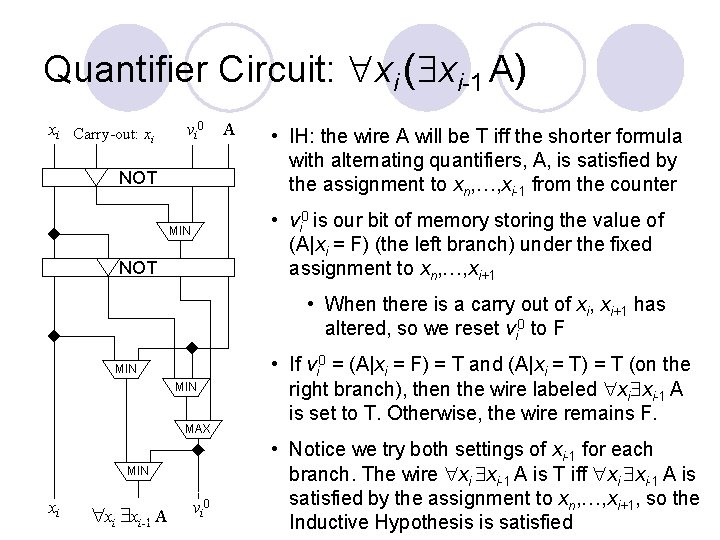

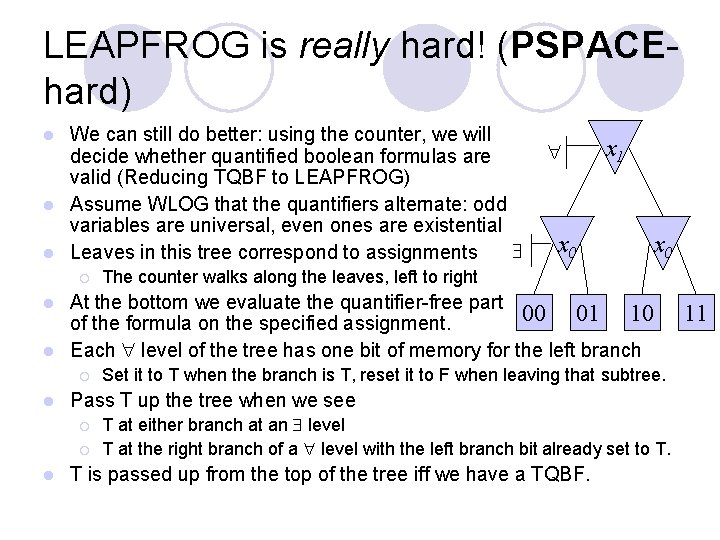

LEAPFROG is hard! (NP-hard) Let any boolean formula be given… Ex: (x 1 ~x 2 x 3) (~x 1 ~x 2 x 3) x 1 x 2 x 3 th, etc. NOT Since we have AND, OR, and NOT gates, formulas easily translate into circuits. If we attach xi to the ith bit of the counter, we try all possible assignments, allowing us to reduce SAT to LEAPFROG. The number of gates in these SAT circuits is quadratic in the length of the formula. NOT MAX MAX MIN (x 1 ~x 2 x 3) (~x 1 ~x 2 x 3)

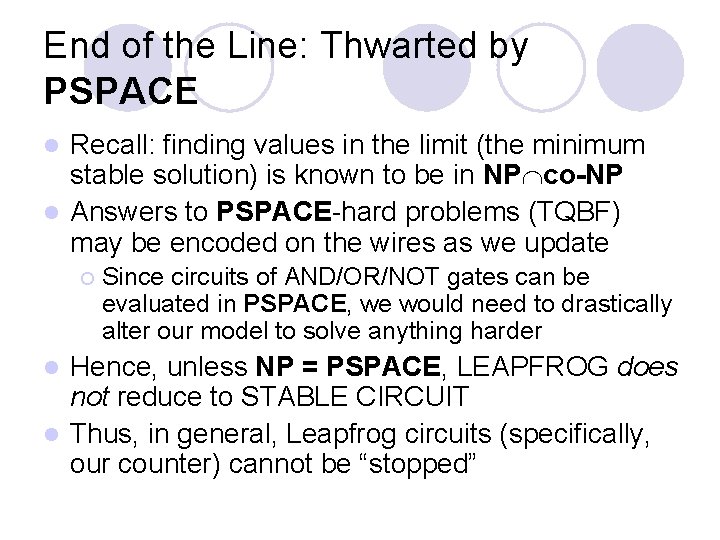

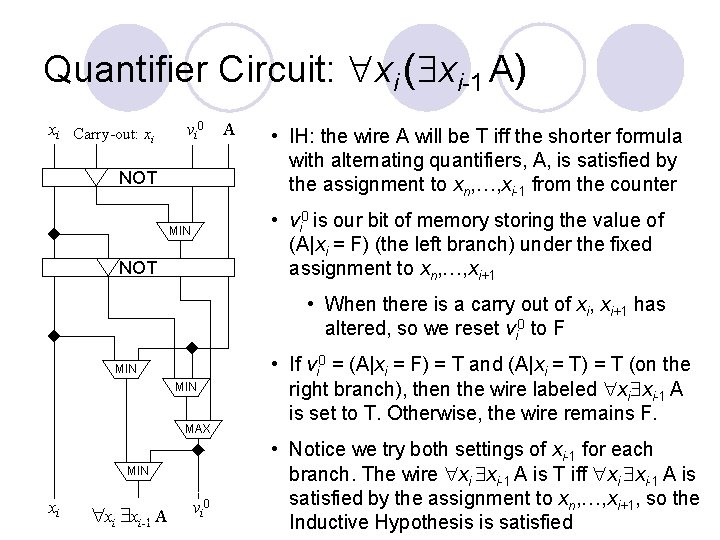

LEAPFROG is really hard! (PSPACEhard) We can still do better: using the counter, we will decide whether quantified boolean formulas are valid (Reducing TQBF to LEAPFROG) l Assume WLOG that the quantifiers alternate: odd variables are universal, even ones are existential l Leaves in this tree correspond to assignments l ¡ x 0 x 1 x 0 The counter walks along the leaves, left to right At the bottom we evaluate the quantifier-free part 00 01 10 of the formula on the specified assignment. l Each level of the tree has one bit of memory for the left branch l ¡ l Pass T up the tree when we see ¡ ¡ l Set it to T when the branch is T, reset it to F when leaving that subtree. T at either branch at an level T at the right branch of a level with the left branch bit already set to T. T is passed up from the top of the tree iff we have a TQBF. 11

Quantifier Circuit: xi ( xi-1 A) xi Carry-out: xi vi 0 NOT A • IH: the wire A will be T iff the shorter formula with alternating quantifiers, A, is satisfied by the assignment to xn, …, xi-1 from the counter • vi 0 is our bit of memory storing the value of (A|xi = F) (the left branch) under the fixed assignment to xn, …, xi+1 MIN NOT • When there is a carry out of xi, xi+1 has altered, so we reset vi 0 to F MIN MAX MIN xi xi-1 A vi 0 • If vi 0 = (A|xi = F) = T and (A|xi = T) = T (on the right branch), then the wire labeled xi xi-1 A is set to T. Otherwise, the wire remains F. • Notice we try both settings of xi-1 for each branch. The wire xi xi-1 A is T iff xi xi-1 A is satisfied by the assignment to xn, …, xi+1, so the Inductive Hypothesis is satisfied

End of the Line: Thwarted by PSPACE Recall: finding values in the limit (the minimum stable solution) is known to be in NP co-NP l Answers to PSPACE-hard problems (TQBF) may be encoded on the wires as we update l ¡ Since circuits of AND/OR/NOT gates can be evaluated in PSPACE, we would need to drastically alter our model to solve anything harder Hence, unless NP = PSPACE, LEAPFROG does not reduce to STABLE CIRCUIT l Thus, in general, Leapfrog circuits (specifically, our counter) cannot be “stopped” l

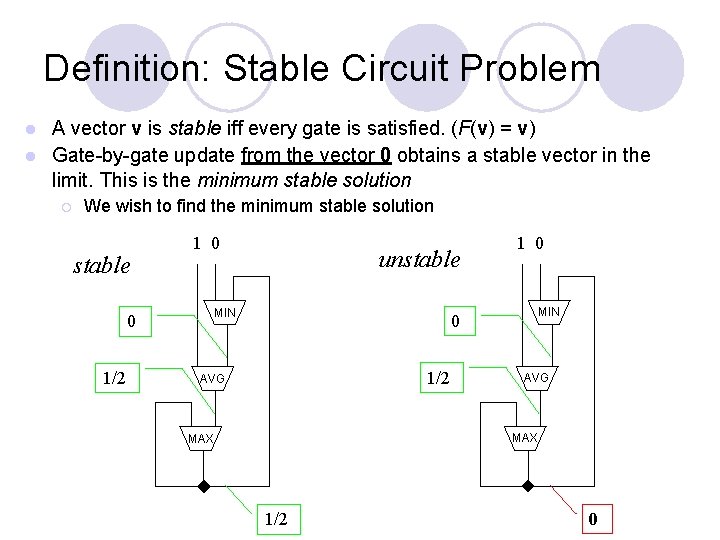

Open problems l How hard is STABLE CIRCUIT? ¡ We had also succeeded in placing the function version in PLS, but still no hardness results ¡ Is Stable Circuit PLS-complete? ¡ Is STABLE CIRCUIT in P? l How hard is LEAPFROG, actually? ¡ Trivially RE, but this says rather little ¡ Is LEAPFROG decidable?