Why does Booths algorithm work Consider ve multiplier

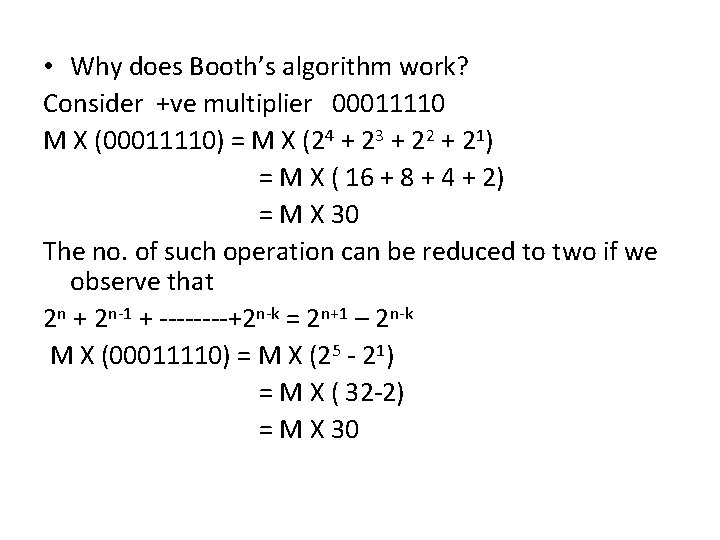

• Why does Booth’s algorithm work? Consider +ve multiplier 00011110 M X (00011110) = M X (24 + 23 + 22 + 21) = M X ( 16 + 8 + 4 + 2) = M X 30 The no. of such operation can be reduced to two if we observe that 2 n + 2 n-1 + ----+2 n-k = 2 n+1 – 2 n-k M X (00011110) = M X (25 - 21) = M X ( 32 -2) = M X 30

• The product can be generated by one addition and one subtraction of the multiplicand. • This scheme extends to any no of blocks of 1’s in a multiplier. Single 1 is treated as a block. • M X (01111010) = M x (27 – 23 + 22 – 21 )

Consider –ve multiplier Let X be a –ve no. X = [1 xn-2 xn-3 ------- x 1 x 0 ) value of X is -2 n-1 + (xn-2 X 2 n-2 ) + -------(x 0 X 20) • Assume leftmost 0 is in kth position X = [11111 -----10 xk-1 xk-2 ----x 1 x 0 ) • value of X is -2 n-1 + 2 n-2+------ 2 k+1 + (xk-1 X 2 k-1 ) + -------(x 0 X 20) 2 n-2+------ 2 k+1 = 2 n-1 - 2 k+1 - 2 n-1 + 2 n-2+------ 2 k+1 = - 2 k+1 X = - 2 k+1 + (xk-1 X 2 k-1 ) + -------(x 0 X 20) • •

Division • More complex than multiplication • Negative numbers are really bad! • Based on long division

Division of Unsigned Binary Integers Divisor 1011 00001101 Quotient 10010011 Dividend 1011 Partial Remainders 001110 1011 001111 100 Remainder

Flowchart for Unsigned Binary Division

This process can be extended to –ve no. s as follows: • M divisor, A, Q dividend. The dividend must be expressed as a 2 n bit 2’s complement no. • Shift A, Q left by 1 bit position. • If M and A have the same signs, perform A A-M; otherwise A A+M • The preceding operation is successful if the sign of A is same before and after the operation

– If the operation is successful or A= 0 then set Q 0 = 1 – If the operation is unsuccessful and A != 0 then set Q 0 = 0 and restore the previous value of A • Repeat steps 2 to 4 as many times as there are bit positions in Q • The reminder is in A. if the signs of both dividend and divisors were the same , then the quotient is in Q; otherwise the correct quotient is 2’s complement of Q

Example 1 A Q 0000 1101 0000 0111 1110 0001 1100 0011 0000 1000 0001 1110 0001 0010 1100 1001 0010 M = 1101 initial value shift add restore shift add set Q 0 = 1 shift add restore

Example 2 A Q 1111 0010 1111 1001 0010 1110 0001 1110 0100 1111 1000 1111 0010 0100 1001 0010 M = 0011 initial value shift add restore shift add set Q 0 = 1 shift add restore

Real Numbers • Numbers with fractions • Could be done in pure binary – 1001. 1010 = 24 + 20 +2 -1 + 2 -3 =9. 625 • Where is the binary point? • Fixed? – Very limited • Moving? – How do you show where it is?

Floating Point • • • +/- S x B+/-E The no. can be stored in a binary word as 3 fields Sign: + or – Significand S Exponent E

Floating Point Examples

Signs for Floating Point • Mantissa is stored in 2’s compliment • Exponent is in excess or biased notation – e. g. Excess (bias) 127 means (2 k -1 -1, where k is no of bits in the binary exponent) – 8 bit exponent field – Pure value range 0 -255 – Subtract 127 to get correct value – Range -127 to +128

Normalization • FP numbers are usually normalized • i. e. exponent is adjusted so that leading bit (MSB) of mantissa is 1 • Since it is always 1 there is no need to store it

Expressible Numbers • -ve no. s between –(2 -2 -23 ) X 2128 and -2 -127 • +ve no. s between 2 -127 and (2 -2 -23 ) X 2128 Five ranges can not be represented • - ve no. s less than –(2 -2 -23 ) X 2128 , called negative overflow • - ve no. s greater than -2 -127 , called negative underflow • Zero • +ve no. s less than 2 -127 , called positive underflow • +ve no. s greater than (2 -2 -23 ) X 2128 , called positive overflow

IEEE 754 • Standard for floating point storage • 32 and 64 bit standards • 8 and 11 bit exponent respectively

IEEE 754 Formats

Special cases: • An exponent of zero together with a fraction of zero represents +ve or –ve zero • An exponent of all ones together with a fraction of zero represents +ve or –ve infinity • An exponent zero together with a nonzero fraction represents a denormalized no. • An exponent of all ones together with a nonzero fraction represents Na. N

FP Arithmetic • A floating point operation may produce one of the following conditions: • Exponent overflow: a +ve exponent exceeds the maximum possible exponent value • Exponent underflow: a -ve exponent is less than the minimum possible exponent value • Significand underflow: In the process of aligning, digits may flow off the right end of the significand • Significand overflow: the addition of two significands of the same sign may result in a carry out of the most significant bit

Addition and Subtraction • • Check for zeros Align significands (adjusting exponents) Add or subtract significands Normalize result

FP Addition & Subtraction Flowchart

FP Arithmetic x/ • • • Check for zero Add/subtract exponents Multiply/divide significands (watch sign) Normalize Round All intermediate results should be in double length storage

Floating Point Multiplication

Floating Point Division

Precision consideration: • Guard bits: The ALU registers contain additional bits known as guard bits Let X = 1. 0 ------00 X 21 and Y = 1. 11 -------1 X 20 X = 1. 00 ----00 X 21 1. 00 ----00 0000 X 21 Y = 0. 11 ----11 X 21 0. 11 ----11 1000 X 21 Z = 0. 00 -----01 X 21 X –Y 0. 00 -----00 1000 X 21 = 1. 00 ----00 X 2 -22 1. 00 -----00 0000 X 2 -23

• Rounding: • Round to nearest: the result is rounded to the nearest representable no. • Round toward +infinity • Round toward -infinity • Round toward zero

- Slides: 27