Welcome to EE 130230 M Integrated Circuit Devices

- Slides: 11

Welcome to EE 130/230 M Integrated Circuit Devices Instructors: Prof. Tsu-Jae King Liu and Dr. Nuo Xu (tking and nuoxu @eecs. berkeley. edu) TA: Khalid Ashraf (kashraf@eecs. berkeley. edu) Web page: http: //www-inst. eecs. berkeley. edu/~ee 130/ b. Space site: EE 130/230 M Spring 2013 Objectives: • Fundamental understanding of the working principles of semiconductor devices used in modern ICs. • An ability to design a transistor to meet performance requirements within realistic constraints.

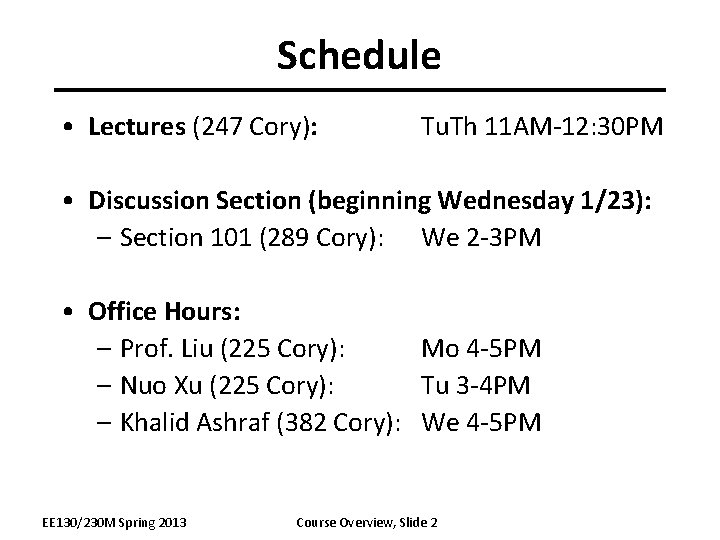

Schedule • Lectures (247 Cory): Tu. Th 11 AM-12: 30 PM • Discussion Section (beginning Wednesday 1/23): – Section 101 (289 Cory): We 2 -3 PM • Office Hours: – Prof. Liu (225 Cory): Mo 4 -5 PM – Nuo Xu (225 Cory): Tu 3 -4 PM – Khalid Ashraf (382 Cory): We 4 -5 PM EE 130/230 M Spring 2013 Course Overview, Slide 2

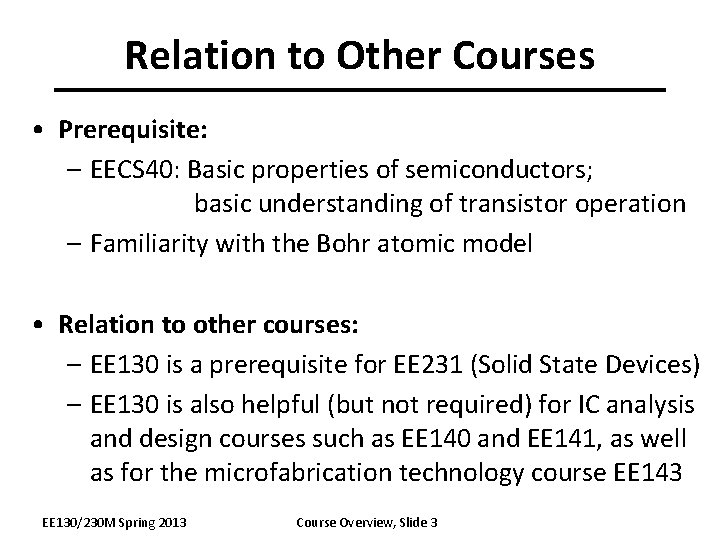

Relation to Other Courses • Prerequisite: – EECS 40: Basic properties of semiconductors; basic understanding of transistor operation – Familiarity with the Bohr atomic model • Relation to other courses: – EE 130 is a prerequisite for EE 231 (Solid State Devices) – EE 130 is also helpful (but not required) for IC analysis and design courses such as EE 140 and EE 141, as well as for the microfabrication technology course EE 143 EE 130/230 M Spring 2013 Course Overview, Slide 3

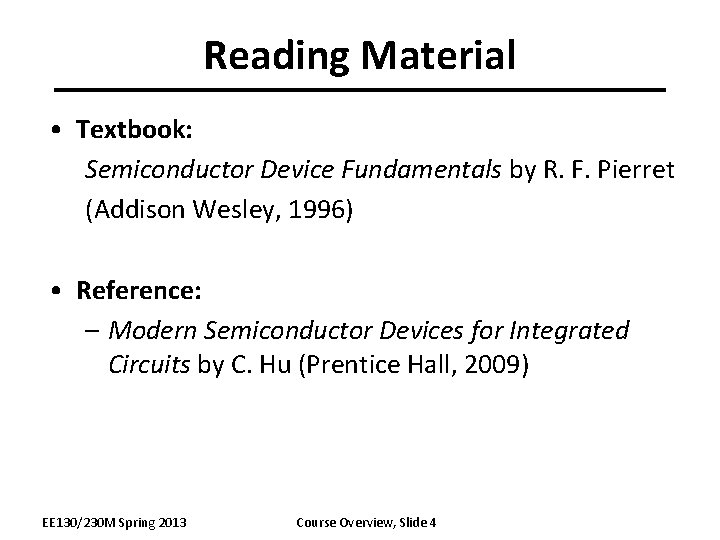

Reading Material • Textbook: Semiconductor Device Fundamentals by R. F. Pierret (Addison Wesley, 1996) • Reference: – Modern Semiconductor Devices for Integrated Circuits by C. Hu (Prentice Hall, 2009) EE 130/230 M Spring 2013 Course Overview, Slide 4

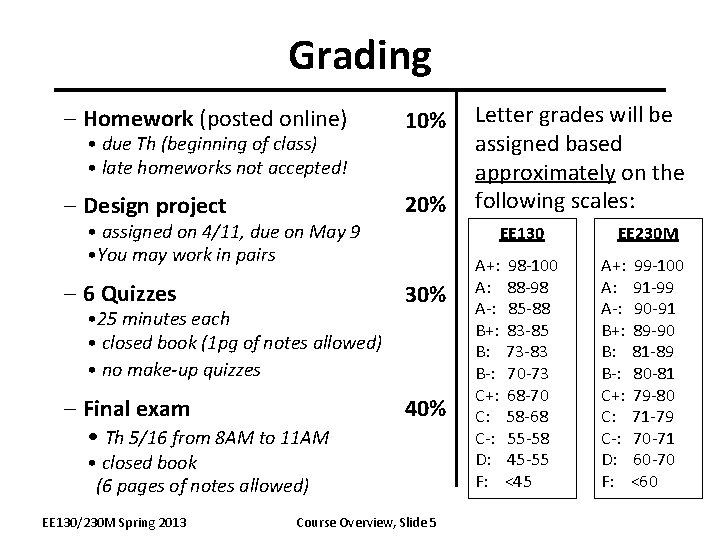

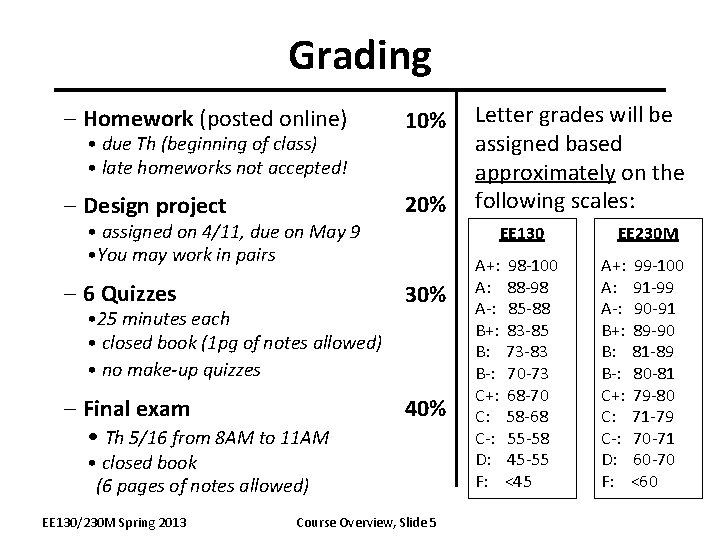

Grading – Homework (posted online) 10% – Design project 20% • due Th (beginning of class) • late homeworks not accepted! • assigned on 4/11, due on May 9 • You may work in pairs – 6 Quizzes 30% – Final exam • Th 5/16 from 8 AM to 11 AM 40% • 25 minutes each • closed book (1 pg of notes allowed) • no make-up quizzes • closed book (6 pages of notes allowed) EE 130/230 M Spring 2013 Course Overview, Slide 5 Letter grades will be assigned based approximately on the following scales: EE 130 EE 230 M A+: 98 -100 A: 88 -98 A-: 85 -88 B+: 83 -85 B: 73 -83 B-: 70 -73 C+: 68 -70 C: 58 -68 C-: 55 -58 D: 45 -55 F: <45 A+: 99 -100 A: 91 -99 A-: 90 -91 B+: 89 -90 B: 81 -89 B-: 80 -81 C+: 79 -80 C: 71 -79 C-: 70 -71 D: 60 -70 F: <60

Miscellany • Special accommodations: – Students may request accommodation of religious creed, disabilities, and other special circumstances. Please meet with Prof. Liu to discuss your request, in advance. • Academic (dis)honesty – Departmental policy will be strictly followed – Collaboration (not cheating!) is encouraged • Classroom etiquette: – – Arrive in class on time! Bring your own copy of the lecture notes. Turn off cell phones, etc. Avoid distracting conversations EE 130/230 M Spring 2013 Course Overview, Slide 6

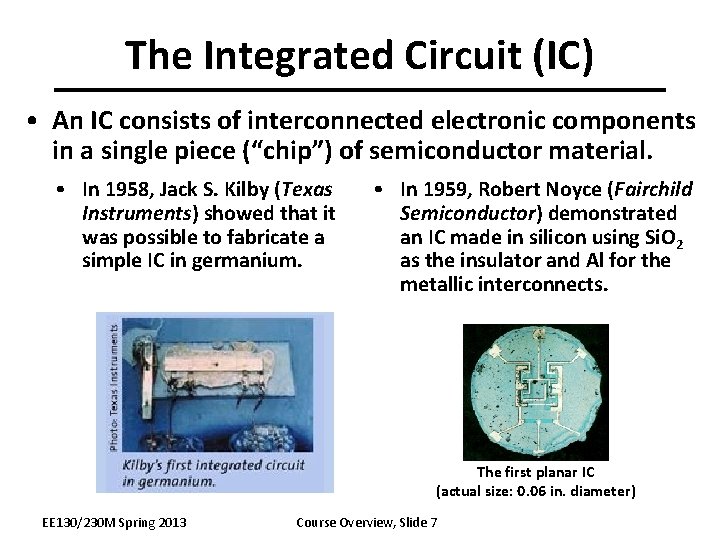

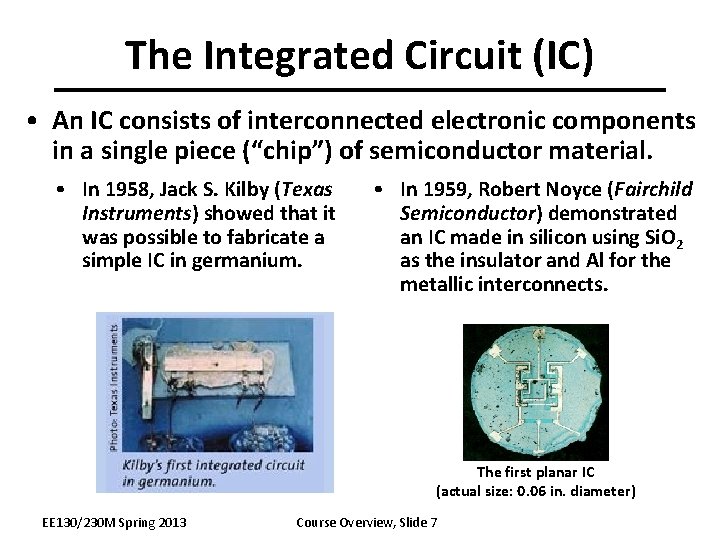

The Integrated Circuit (IC) • An IC consists of interconnected electronic components in a single piece (“chip”) of semiconductor material. • In 1958, Jack S. Kilby (Texas Instruments) showed that it was possible to fabricate a simple IC in germanium. • In 1959, Robert Noyce (Fairchild Semiconductor) demonstrated an IC made in silicon using Si. O 2 as the insulator and Al for the metallic interconnects. The first planar IC (actual size: 0. 06 in. diameter) EE 130/230 M Spring 2013 Course Overview, Slide 7

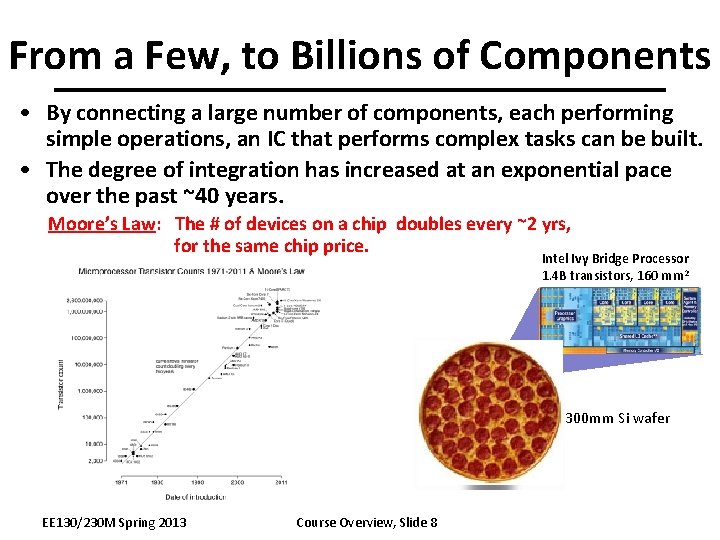

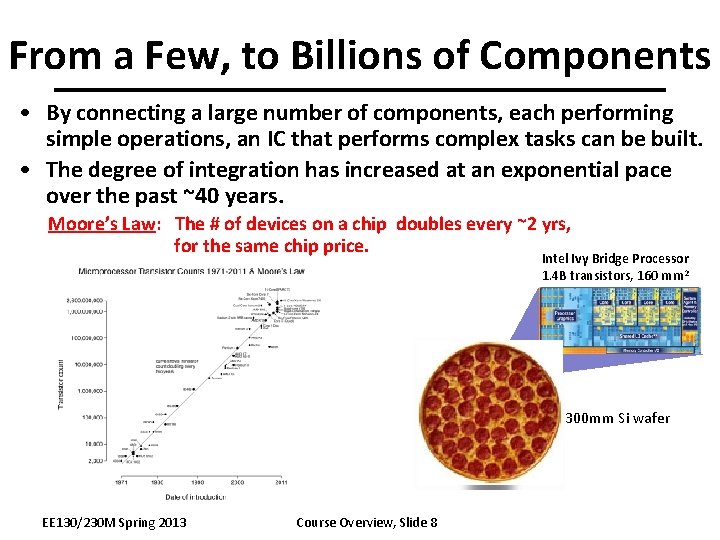

From a Few, to Billions of Components • By connecting a large number of components, each performing simple operations, an IC that performs complex tasks can be built. • The degree of integration has increased at an exponential pace over the past ~40 years. Moore’s Law: The # of devices on a chip doubles every ~2 yrs, for the same chip price. Intel Ivy Bridge Processor 1. 4 B transistors, 160 mm 2 300 mm Si wafer EE 130/230 M Spring 2013 Course Overview, Slide 8

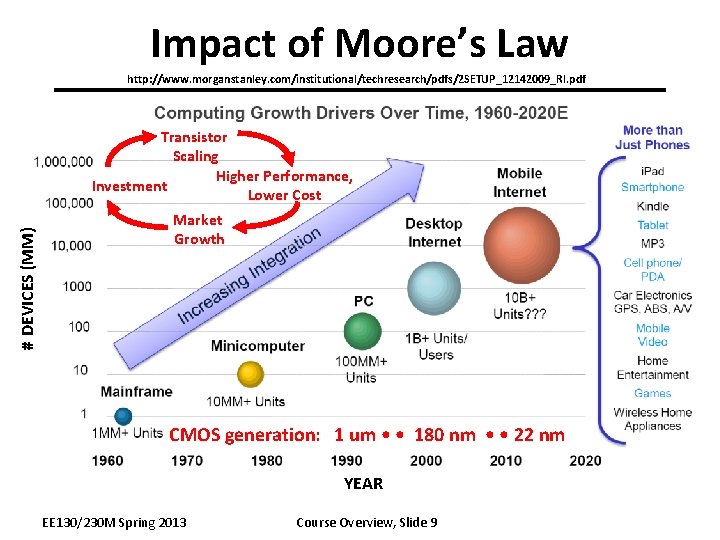

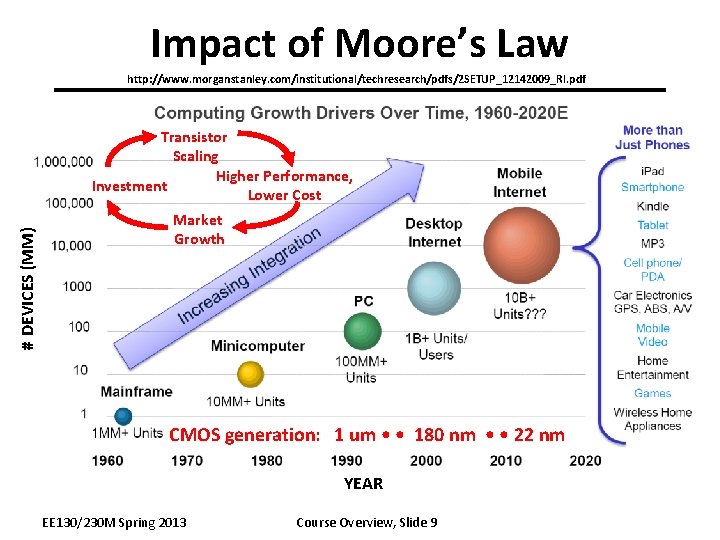

Impact of Moore’s Law http: //www. morganstanley. com/institutional/techresearch/pdfs/2 SETUP_12142009_RI. pdf # DEVICES (MM) Transistor Scaling Higher Performance, Investment Lower Cost Market Growth CMOS generation: 1 um • • 180 nm • • 22 nm YEAR EE 130/230 M Spring 2013 Course Overview, Slide 9

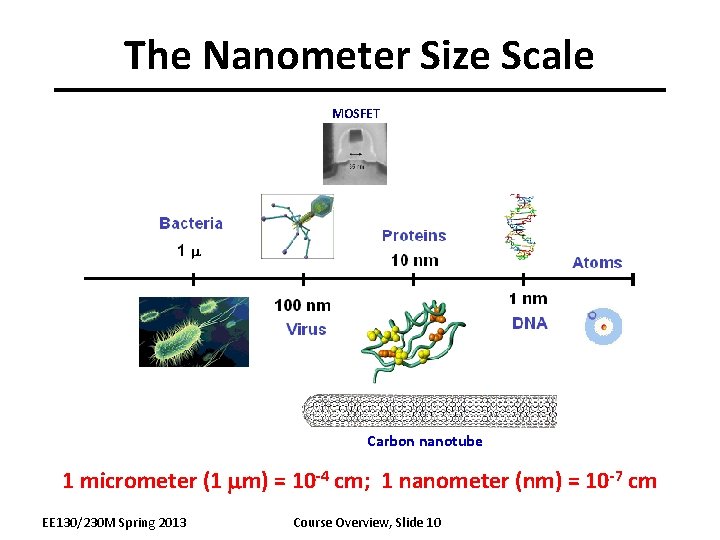

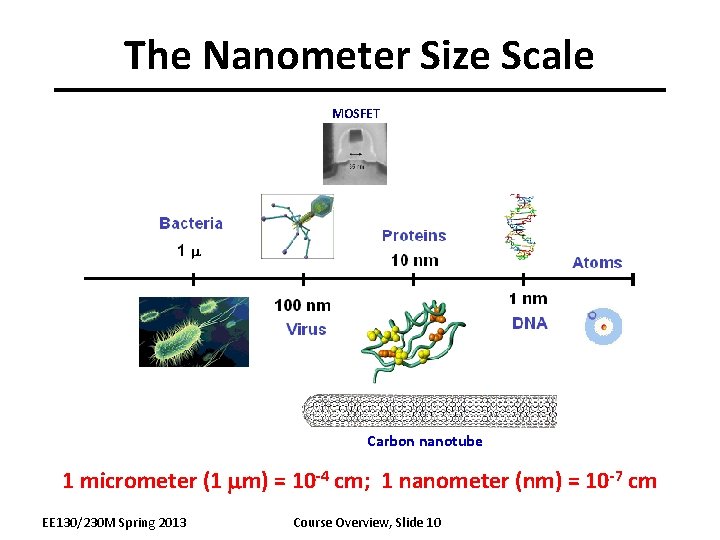

The Nanometer Size Scale MOSFET Carbon nanotube 1 micrometer (1 mm) = 10 -4 cm; 1 nanometer (nm) = 10 -7 cm EE 130/230 M Spring 2013 Course Overview, Slide 10

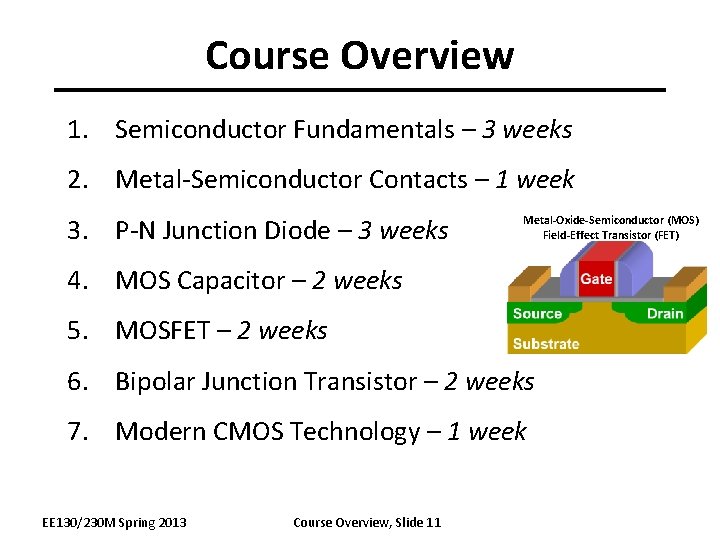

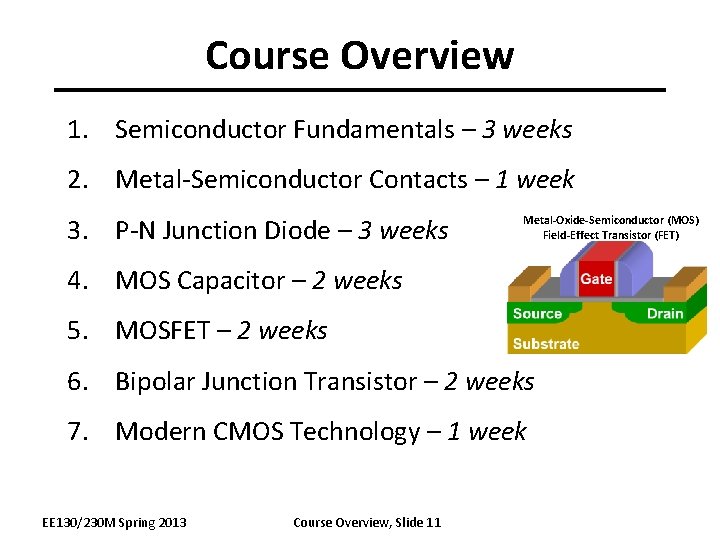

Course Overview 1. Semiconductor Fundamentals – 3 weeks 2. Metal-Semiconductor Contacts – 1 week 3. P-N Junction Diode – 3 weeks Metal-Oxide-Semiconductor (MOS) Field-Effect Transistor (FET) 4. MOS Capacitor – 2 weeks 5. MOSFET – 2 weeks 6. Bipolar Junction Transistor – 2 weeks 7. Modern CMOS Technology – 1 week EE 130/230 M Spring 2013 Course Overview, Slide 11