WEEK EMT 3533 DIGITAL IC DESIGN SYNTHESIS OF

- Slides: 21

WEEK EMT 353/3 DIGITAL IC DESIGN SYNTHESIS OF COMBINATIONAL LOGIC | SCHOOL OF MICROELECTRONIC ENGINEERING | Uni. MAP

Contents Introduction Rules of Combinational Logic Synthesis Synthesizable Coding Styles for Combinational Logic

Introduction It is a concern by designers to translate the Verilog codes into hardware In this case, synthesis tool is used for automated translation of Verilog code of design into hardware It is important that the same code designed for functional verification can be used directly to a synthesis tool to ensure the same simulation results are retrieved after synthesis

Introduction Not all constructs are synthesizable designers should make sure the constructs used are synthesizable. Timing parameters specified in pre-synthesis descriptions are either not allowed or ignored by synthesis tool (better not to use timing parameters in your design. . )

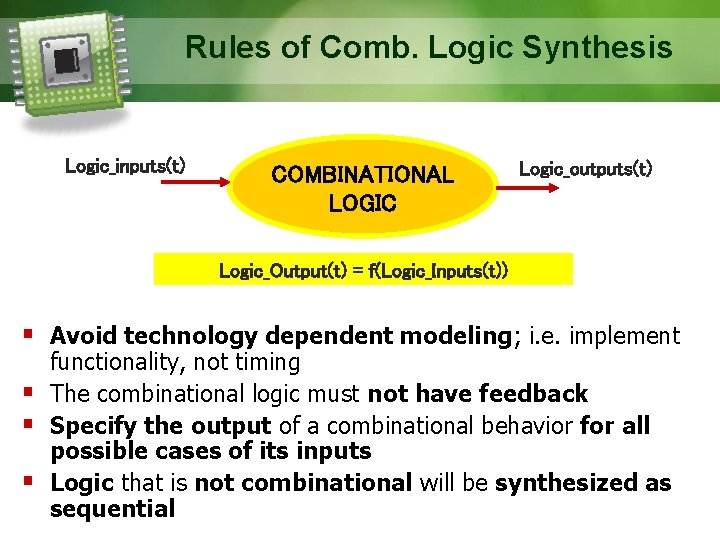

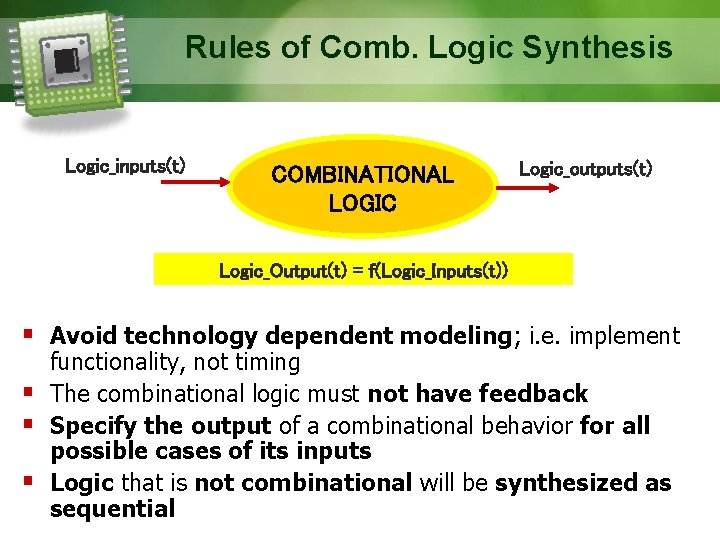

Rules of Comb. Logic Synthesis Logic_inputs(t) COMBINATIONAL LOGIC Logic_outputs(t) Logic_Output(t) = f(Logic_Inputs(t)) Avoid technology dependent modeling; i. e. implement functionality, not timing The combinational logic must not have feedback Specify the output of a combinational behavior for all possible cases of its inputs Logic that is not combinational will be synthesized as sequential

Synthesizable Coding Styles Gate level synthesis Continuous assignments synthesis Behavioral synthesis Mixed synthesis

Gate Level Synthesis Gate level designs are synthesizable However, UDP are not allowed by most of synthesis tools Tri-state gates are allowed if it is supported by the target technology (warning messages is issued by the synthesis tool if it is supported should be replaced by equivalent logic function)

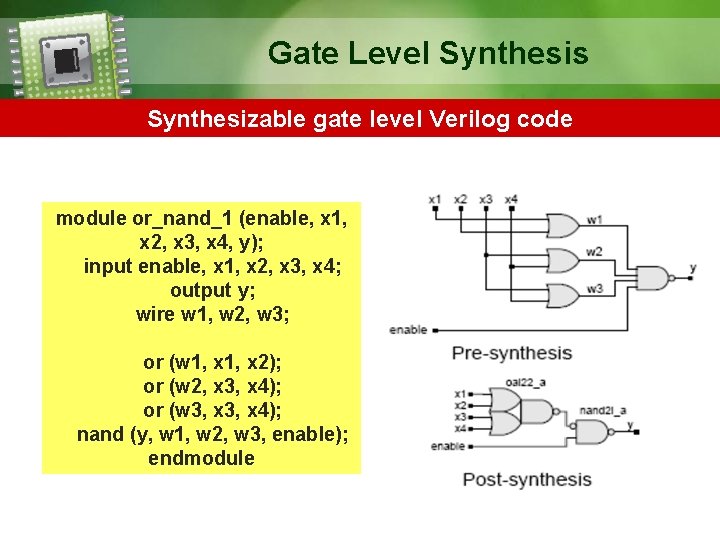

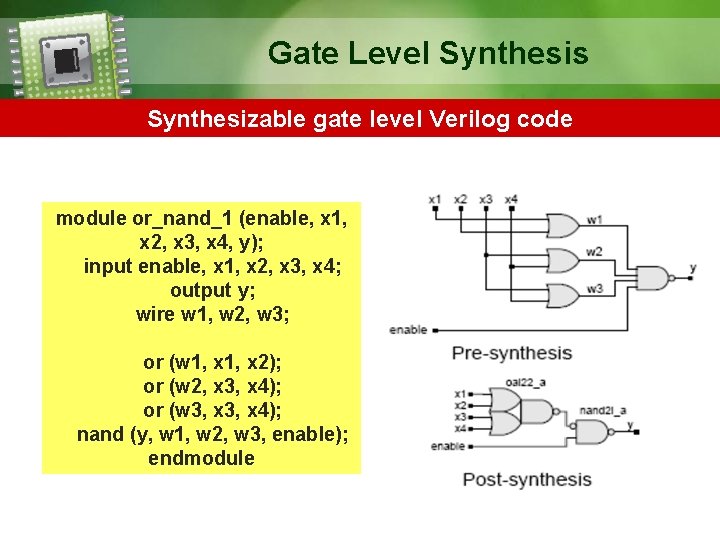

Gate Level Synthesis Synthesizable gate level Verilog code module or_nand_1 (enable, x 1, x 2, x 3, x 4, y); input enable, x 1, x 2, x 3, x 4; output y; wire w 1, w 2, w 3; or (w 1, x 2); or (w 2, x 3, x 4); or (w 3, x 4); nand (y, w 1, w 2, w 3, enable); endmodule

Gate Level Synthesis Tri-state Buffers Verilog language has built-in constructs for modeling and synthesizing the functionality of three-state devices Three-state devices are controlled by a signal whose value determines whether an input signal is connected to the output This functionality is important in physical circuits having multiple drivers

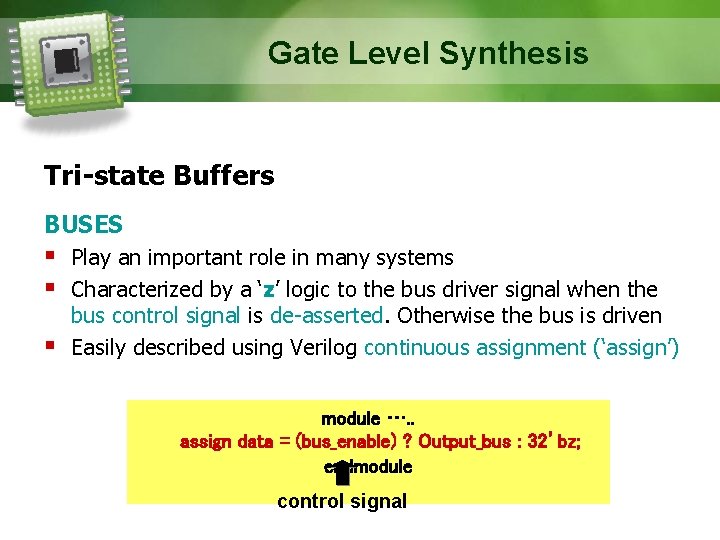

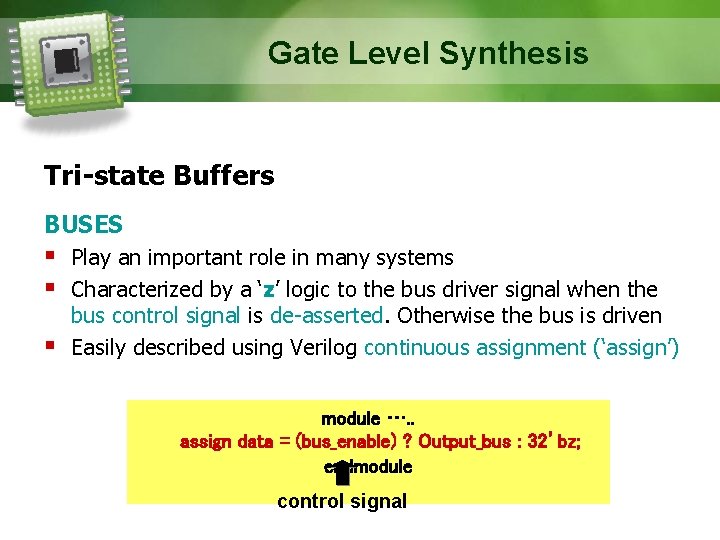

Gate Level Synthesis Tri-state Buffers BUSES Play an important role in many systems Characterized by a ‘z’ logic to the bus driver signal when the bus control signal is de-asserted. Otherwise the bus is driven Easily described using Verilog continuous assignment (‘assign’) module …. . assign data = (bus_enable) ? Output_bus : 32’bz; endmodule control signal

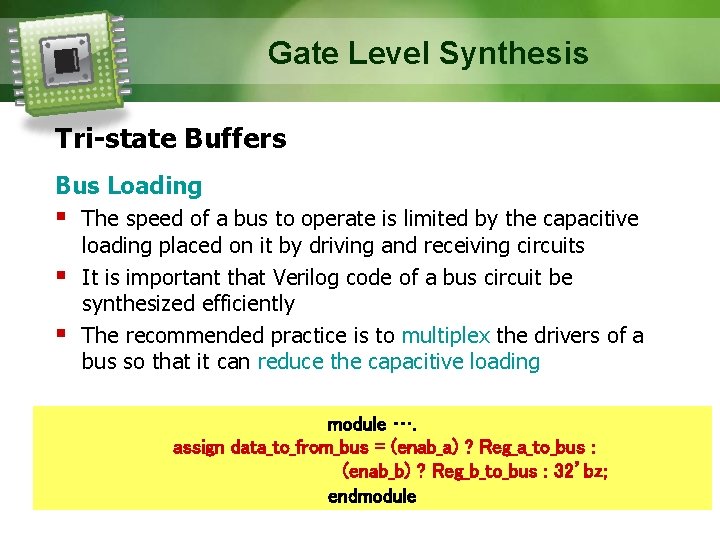

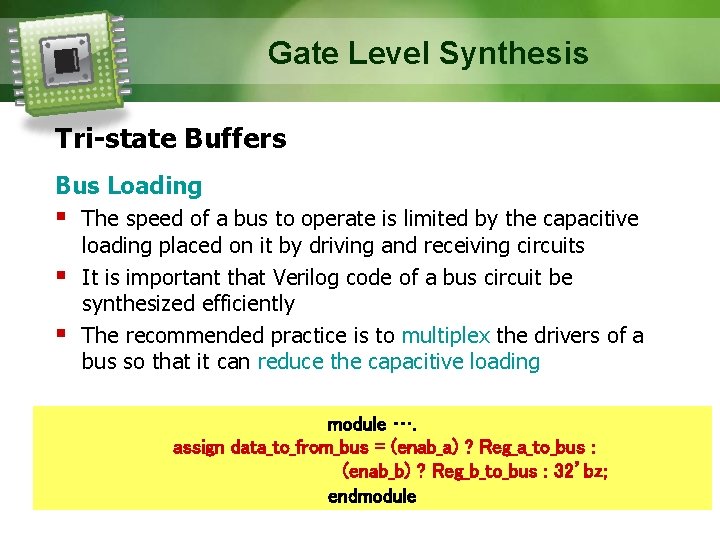

Gate Level Synthesis Tri-state Buffers Bus Loading The speed of a bus to operate is limited by the capacitive loading placed on it by driving and receiving circuits It is important that Verilog code of a bus circuit be synthesized efficiently The recommended practice is to multiplex the drivers of a bus so that it can reduce the capacitive loading module …. assign data_to_from_bus = (enab_a) ? Reg_a_to_bus : (enab_b) ? Reg_b_to_bus : 32’bz; endmodule

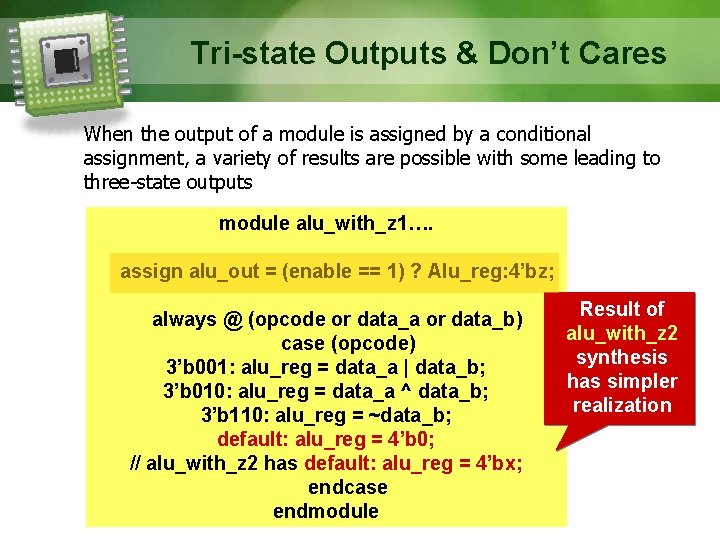

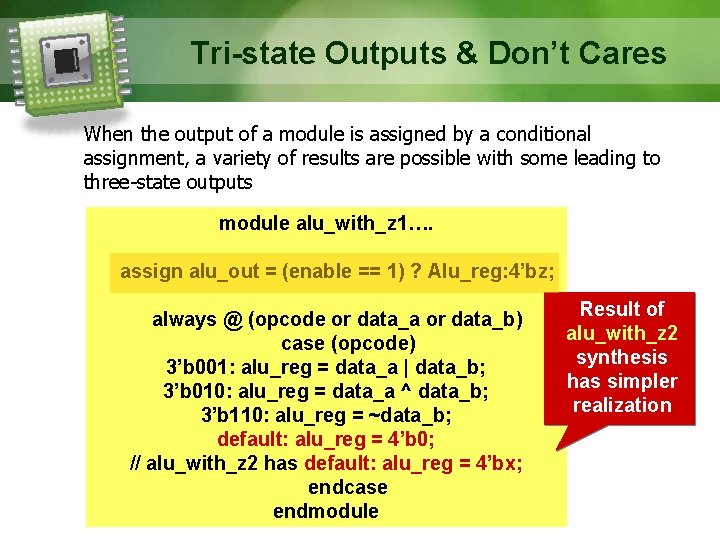

Tri-state Outputs & Don’t Cares When the output of a module is assigned by a conditional assignment, a variety of results are possible with some leading to three-state outputs module alu_with_z 1…. assign alu_out = (enable == 1) ? Alu_reg: 4’bz; always @ (opcode or data_a or data_b) case (opcode) 3’b 001: alu_reg = data_a | data_b; 3’b 010: alu_reg = data_a ^ data_b; 3’b 110: alu_reg = ~data_b; default: alu_reg = 4’b 0; // alu_with_z 2 has default: alu_reg = 4’bx; endcase endmodule Result of alu_with_z 2 synthesis has simpler realization

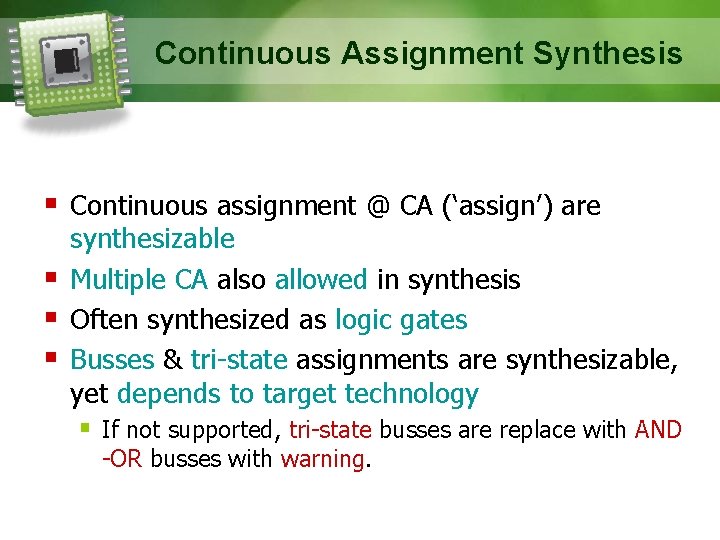

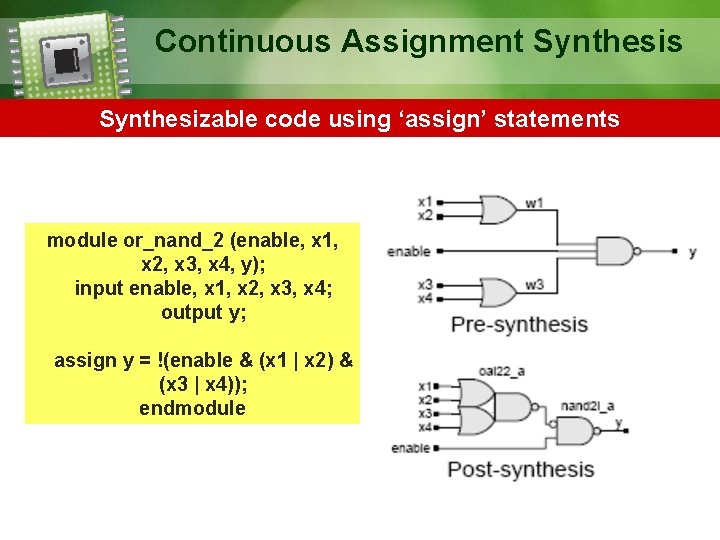

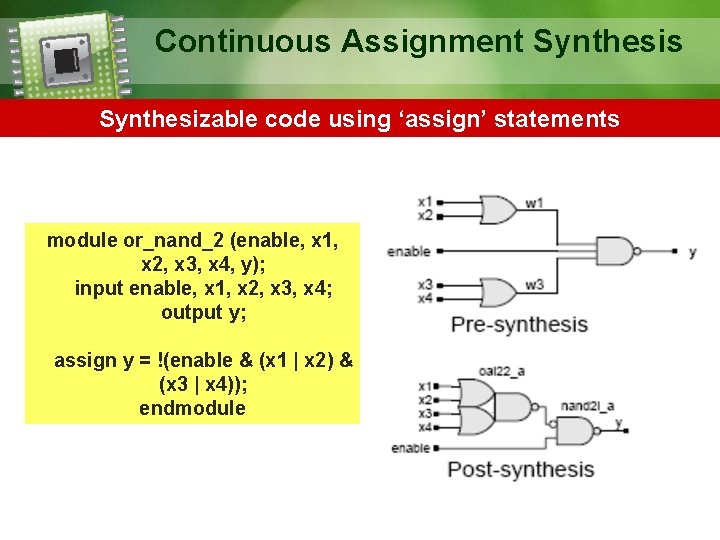

Continuous Assignment Synthesis Continuous assignment @ CA (‘assign’) are synthesizable Multiple CA also allowed in synthesis Often synthesized as logic gates Busses & tri-state assignments are synthesizable, yet depends to target technology If not supported, tri-state busses are replace with AND -OR busses with warning.

Continuous Assignment Synthesis Synthesizable code using ‘assign’ statements module or_nand_2 (enable, x 1, x 2, x 3, x 4, y); input enable, x 1, x 2, x 3, x 4; output y; assign y = !(enable & (x 1 | x 2) & (x 3 | x 4)); endmodule

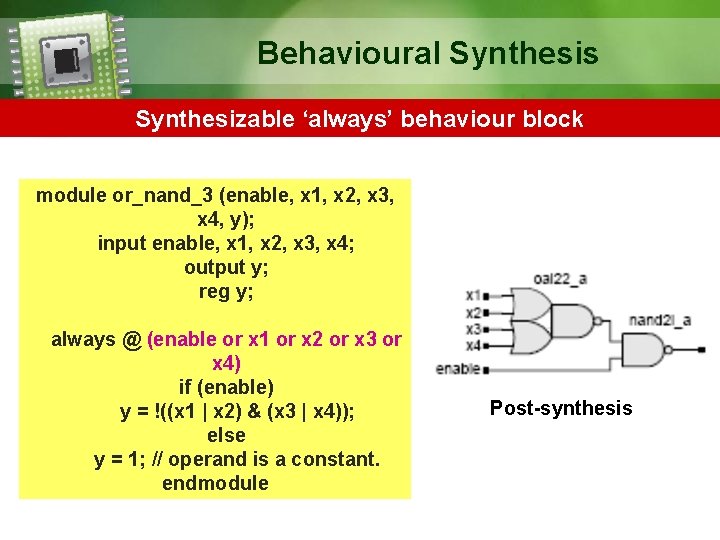

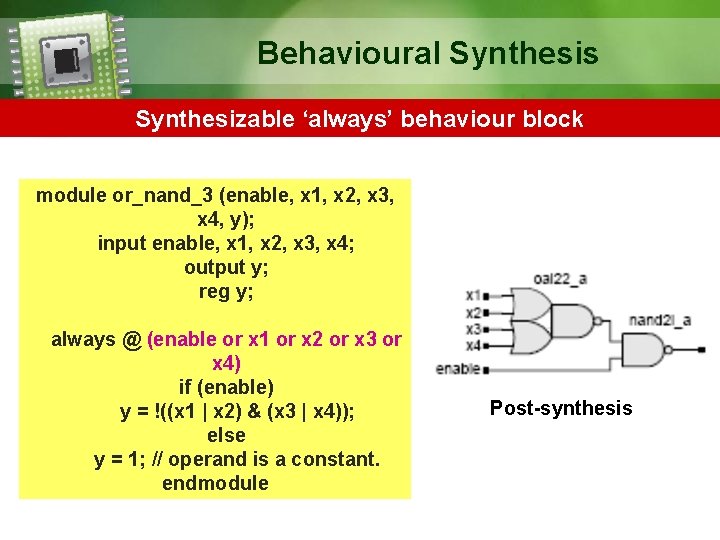

Behavioural Synthesis Cyclic (‘always’) block with procedural assignments is synthesizable Procedural blocks are more flexible in coding than gates & concurrent assignments So, it needs certain guidelines to make sure that ‘always’ statement is translated to such hardware. The guidelines cover: Input sensitivity Output assignments

Behavioural Synthesis Input Sensitivity Bear in mind that combinational circuit is sensitive to ALL its inputs So, an ‘always’ block should include ALL inputs in its sensitivity list Inputs of an ‘always’ block are variables or signals that are being read Shortcut : use asterisk (*) in sensitivity list implies all inputs always @ (*)

Behavioural Synthesis Output Assignments Another property of combinational logic is that its output always affected by a change in its inputs So, it is important to make sure that a combinational ‘always’ block prevents output latches Combinational circuit never retain their old value i. e. no latching occurs in output

Behavioural Synthesis Synthesizable ‘always’ behaviour block module or_nand_3 (enable, x 1, x 2, x 3, x 4, y); input enable, x 1, x 2, x 3, x 4; output y; reg y; always @ (enable or x 1 or x 2 or x 3 or x 4) if (enable) y = !((x 1 | x 2) & (x 3 | x 4)); else y = 1; // operand is a constant. endmodule Post-synthesis

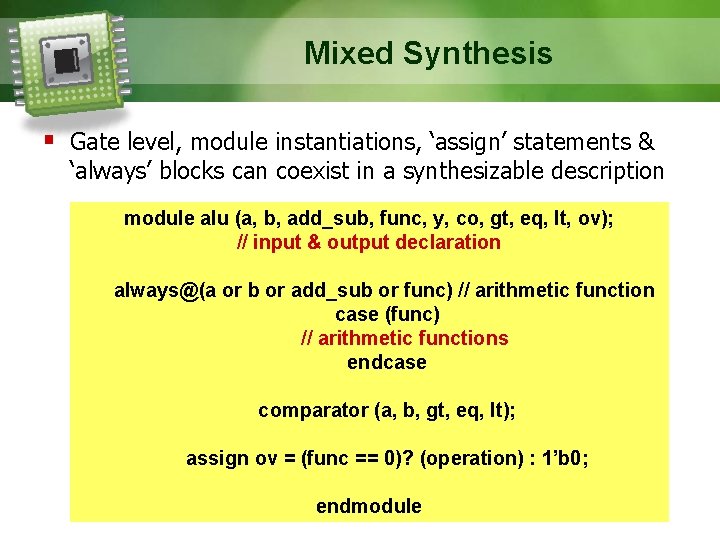

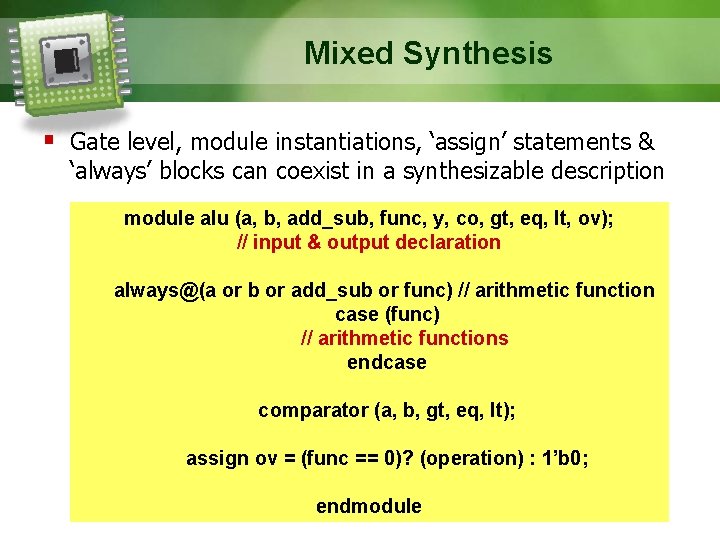

Mixed Synthesis Gate level, module instantiations, ‘assign’ statements & ‘always’ blocks can coexist in a synthesizable description module alu (a, b, add_sub, func, y, co, gt, eq, lt, ov); // input & output declaration always@(a or b or add_sub or func) // arithmetic function case (func) // arithmetic functions endcase comparator (a, b, gt, eq, lt); assign ov = (func == 0)? (operation) : 1’b 0; endmodule

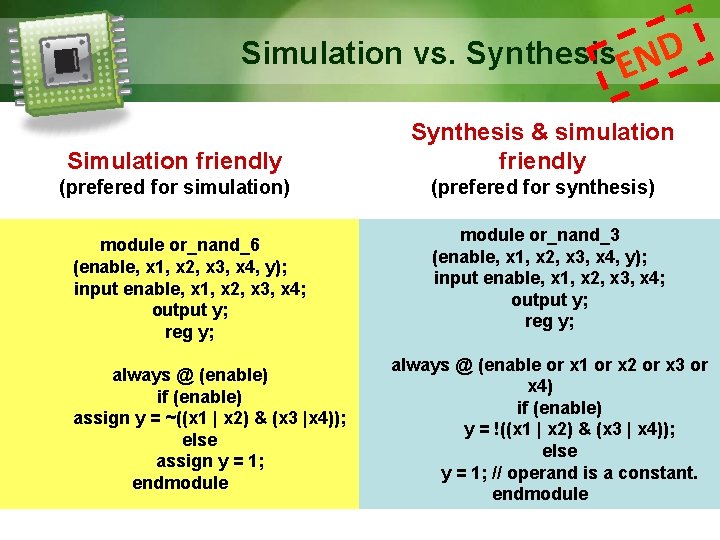

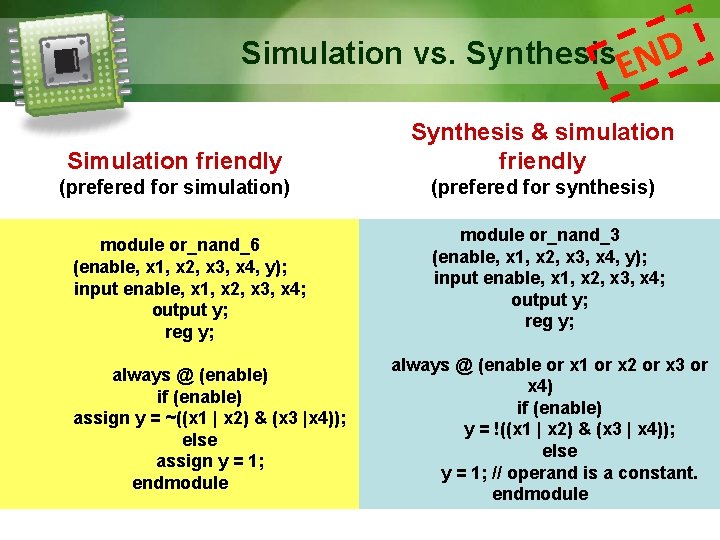

Simulation vs. Synthesis The use of procedural-continuous assignment (PCA) (assign. . deassign) reduces the size of the event sensitivity list and improves the simulation efficiency by dynamically changing the sensitivity list However, some tools do not support PCA for synthesis - two models might be used and switched between simulation and synthesis

Simulation vs. Synthesis D N E Simulation friendly Synthesis & simulation friendly (prefered for simulation) (prefered for synthesis) module or_nand_6 (enable, x 1, x 2, x 3, x 4, y); input enable, x 1, x 2, x 3, x 4; output y; reg y; always @ (enable) if (enable) assign y = ~((x 1 | x 2) & (x 3 |x 4)); else assign y = 1; endmodule or_nand_3 (enable, x 1, x 2, x 3, x 4, y); input enable, x 1, x 2, x 3, x 4; output y; reg y; always @ (enable or x 1 or x 2 or x 3 or x 4) if (enable) y = !((x 1 | x 2) & (x 3 | x 4)); else y = 1; // operand is a constant. endmodule