Week 1 Lecture 2 Week 2 Lecture 3

- Slides: 25

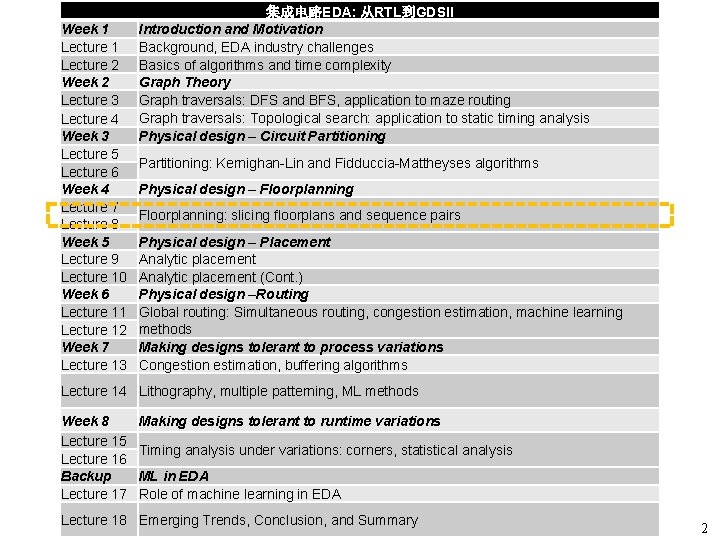

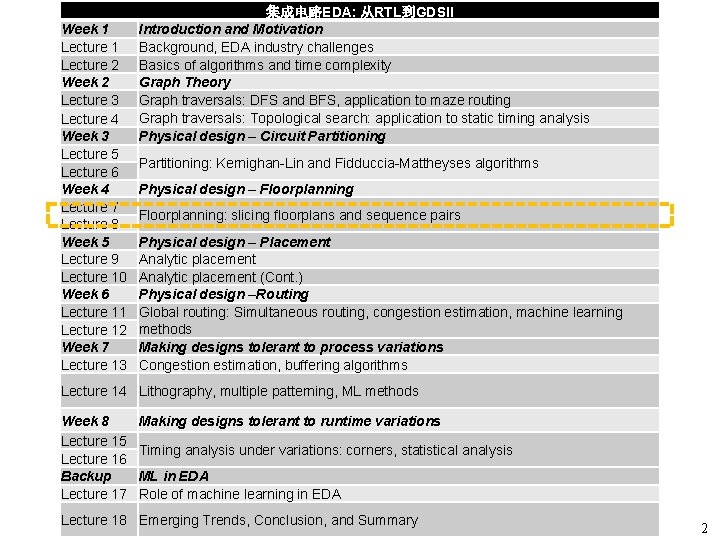

Week 1 Lecture 2 Week 2 Lecture 3 Lecture 4 Week 3 Lecture 5 Lecture 6 Week 4 Lecture 7 Lecture 8 Week 5 Lecture 9 Lecture 10 Week 6 Lecture 11 Lecture 12 Week 7 Lecture 13 集成电路EDA: 从RTL到GDSII Introduction and Motivation Background, EDA industry challenges Basics of algorithms and time complexity Graph Theory Graph traversals: DFS and BFS, application to maze routing Graph traversals: Topological search: application to static timing analysis Physical design – Circuit Partitioning: Kernighan-Lin and Fidduccia-Mattheyses algorithms Physical design – Floorplanning: slicing floorplans and sequence pairs Physical design – Placement Analytic placement (Cont. ) Physical design –Routing Global routing: Simultaneous routing, congestion estimation, machine learning methods Making designs tolerant to process variations Congestion estimation, buffering algorithms Lecture 14 Lithography, multiple patterning, ML methods Week 8 Lecture 15 Lecture 16 Backup Lecture 17 Making designs tolerant to runtime variations Timing analysis under variations: corners, statistical analysis ML in EDA Role of machine learning in EDA Lecture 18 Emerging Trends, Conclusion, and Summary 2

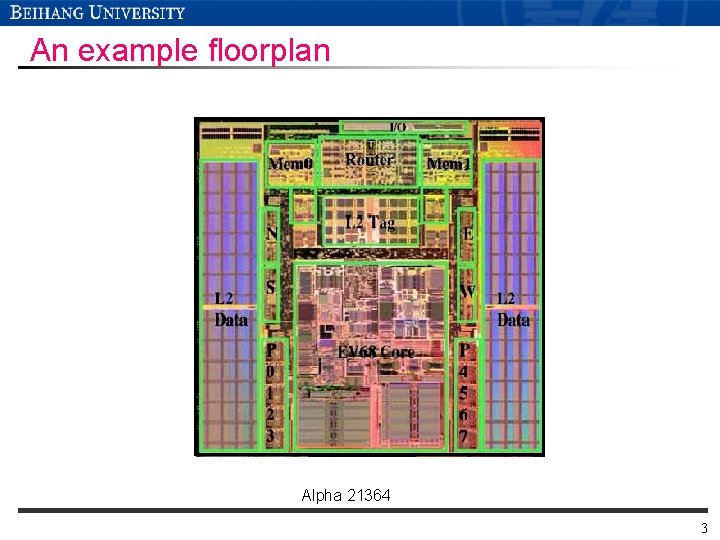

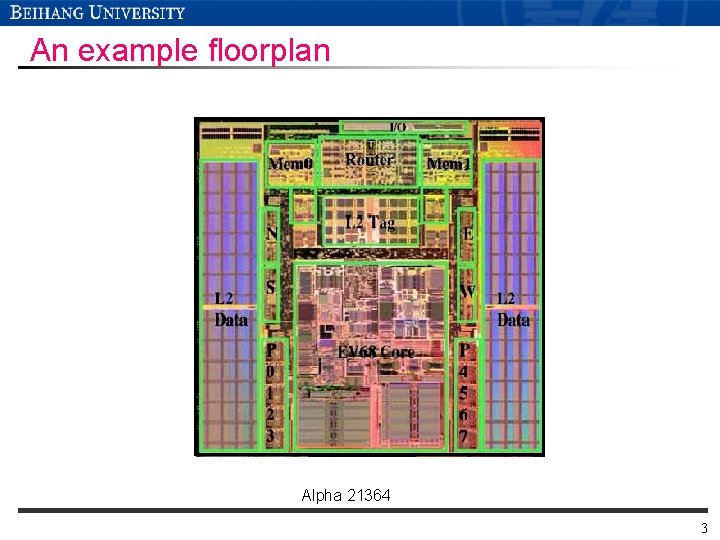

An example floorplan Alpha 21364 3

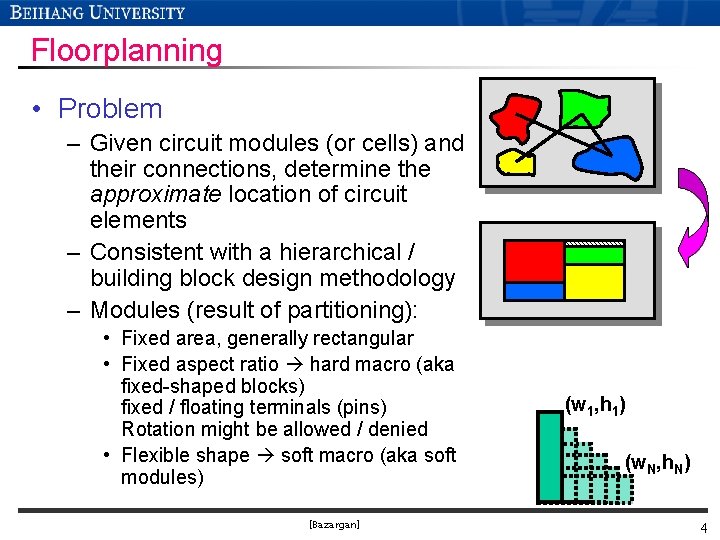

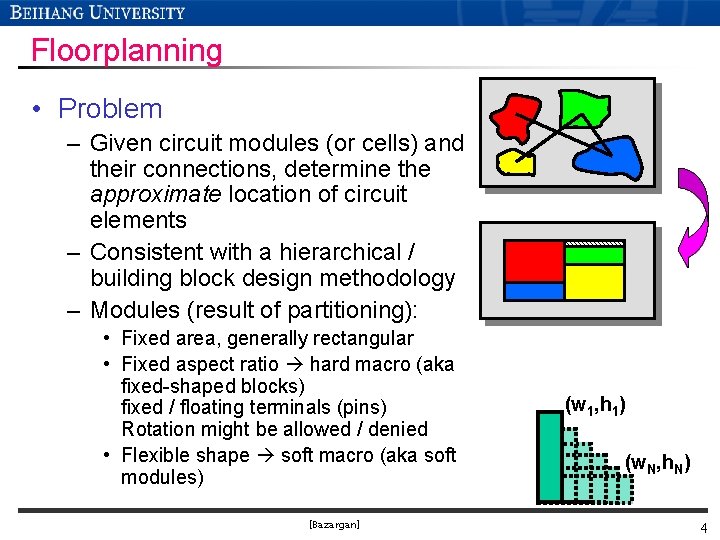

Floorplanning • Problem – Given circuit modules (or cells) and their connections, determine the approximate location of circuit elements – Consistent with a hierarchical / building block design methodology – Modules (result of partitioning): • Fixed area, generally rectangular • Fixed aspect ratio hard macro (aka fixed-shaped blocks) fixed / floating terminals (pins) Rotation might be allowed / denied • Flexible shape soft macro (aka soft modules) [Bazargan] (w 1, h 1) (w. N, h. N) 4

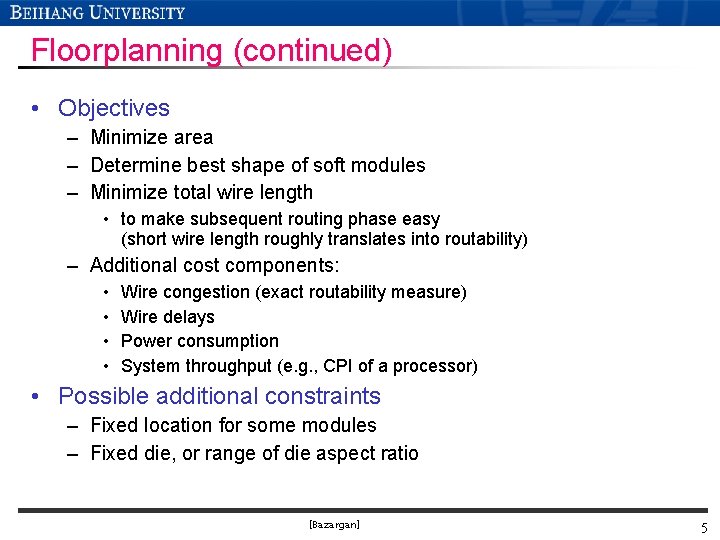

Floorplanning (continued) • Objectives – Minimize area – Determine best shape of soft modules – Minimize total wire length • to make subsequent routing phase easy (short wire length roughly translates into routability) – Additional cost components: • • Wire congestion (exact routability measure) Wire delays Power consumption System throughput (e. g. , CPI of a processor) • Possible additional constraints – Fixed location for some modules – Fixed die, or range of die aspect ratio [Bazargan] 5

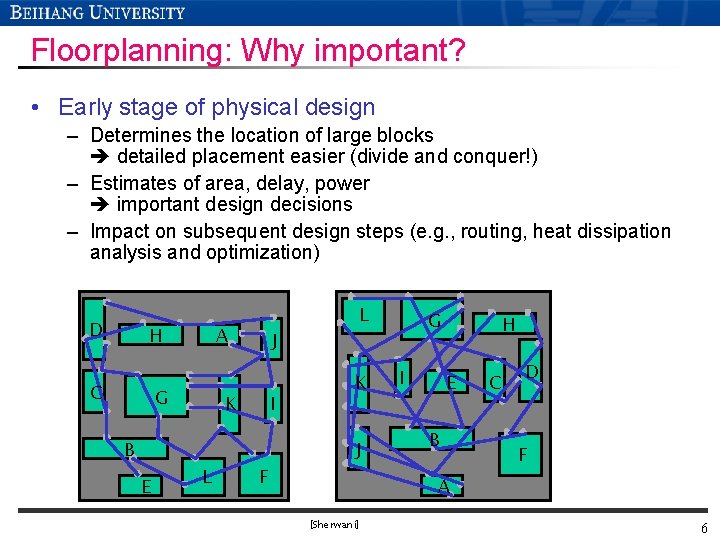

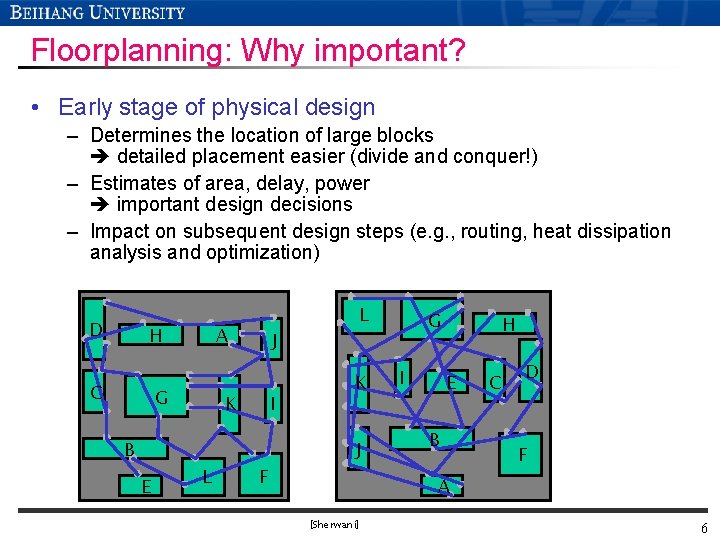

Floorplanning: Why important? • Early stage of physical design – Determines the location of large blocks detailed placement easier (divide and conquer!) – Estimates of area, delay, power important design decisions – Impact on subsequent design steps (e. g. , routing, heat dissipation analysis and optimization) D H C A G B E J K L I F L K J G I H E B C D F A [Sherwani] 6

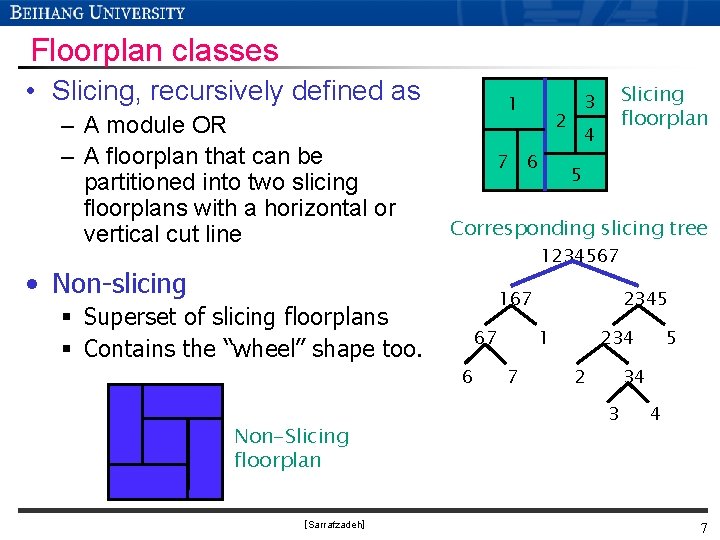

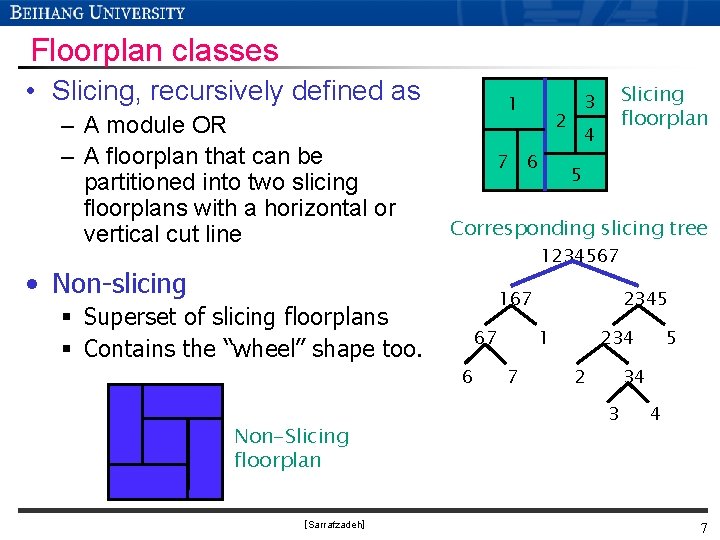

Floorplan classes • Slicing, recursively defined as – A module OR – A floorplan that can be partitioned into two slicing floorplans with a horizontal or vertical cut line 1 7 5 1234567 167 § Superset of slicing floorplans § Contains the “wheel” shape too. 67 6 [Sarrafzadeh] 4 Corresponding slicing tree • Non-slicing Non-Slicing floorplan 2 6 Slicing floorplan 3 2345 1 7 234 2 5 34 3 4 7

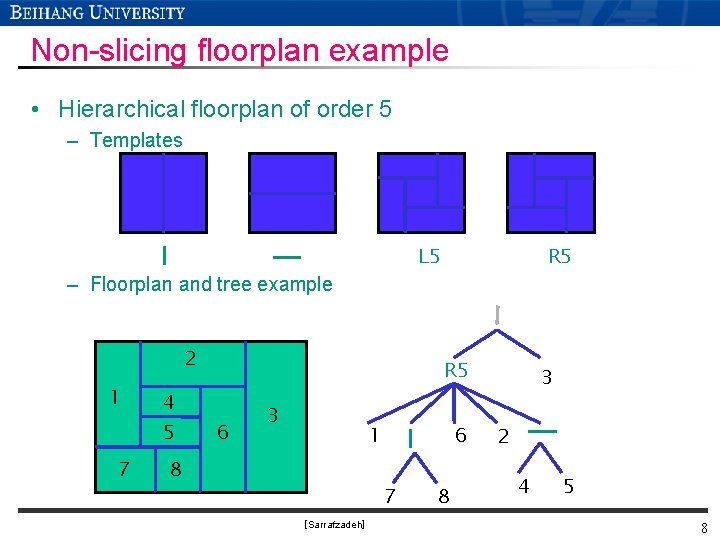

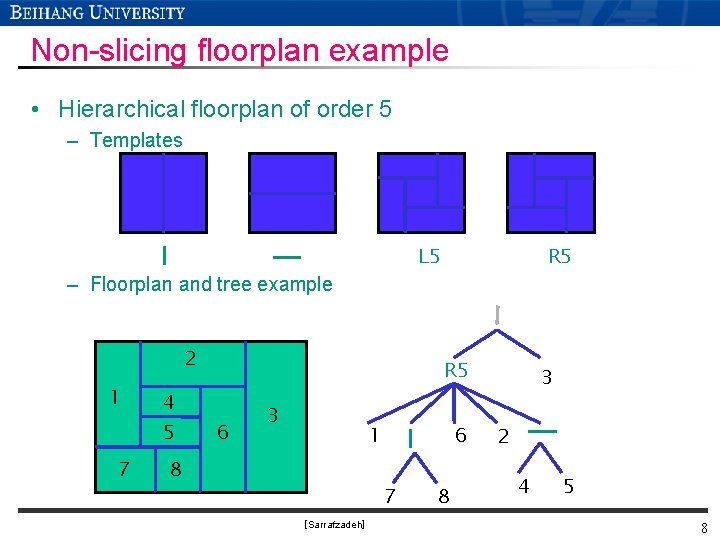

Non-slicing floorplan example • Hierarchical floorplan of order 5 – Templates L 5 R 5 – Floorplan and tree example 2 1 4 5 7 R 5 6 3 1 8 6 7 [Sarrafzadeh] 8 3 2 4 5 8

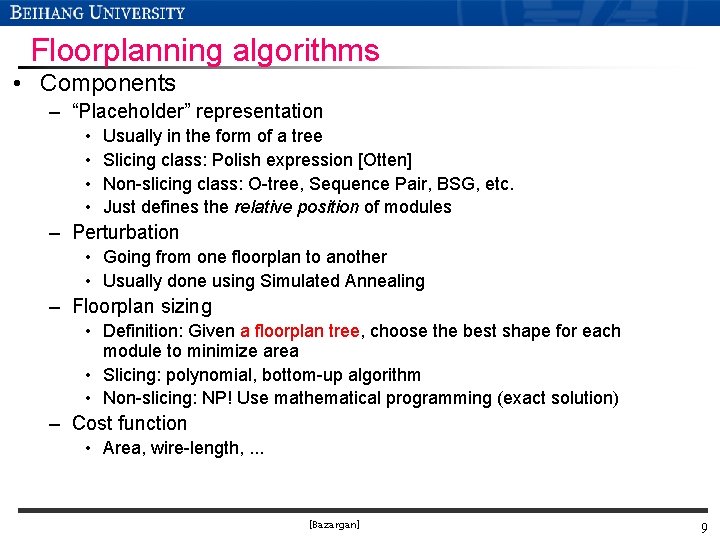

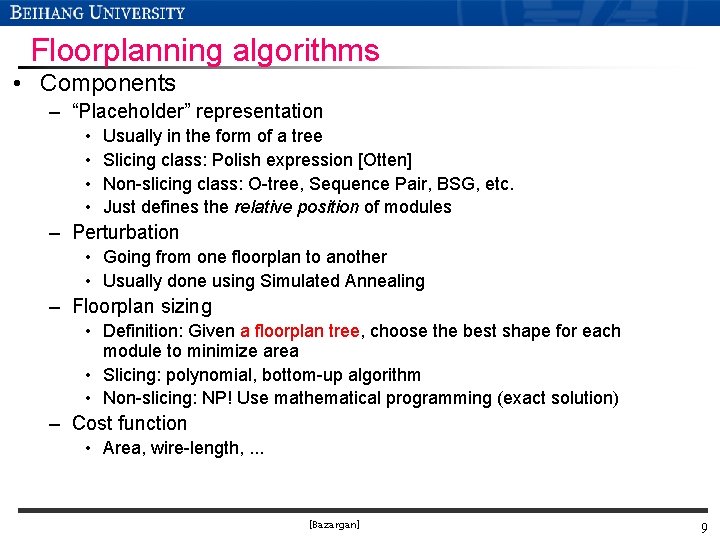

Floorplanning algorithms • Components – “Placeholder” representation • • Usually in the form of a tree Slicing class: Polish expression [Otten] Non-slicing class: O-tree, Sequence Pair, BSG, etc. Just defines the relative position of modules – Perturbation • Going from one floorplan to another • Usually done using Simulated Annealing – Floorplan sizing • Definition: Given a floorplan tree, choose the best shape for each module to minimize area • Slicing: polynomial, bottom-up algorithm • Non-slicing: NP! Use mathematical programming (exact solution) – Cost function • Area, wire-length, . . . [Bazargan] 9

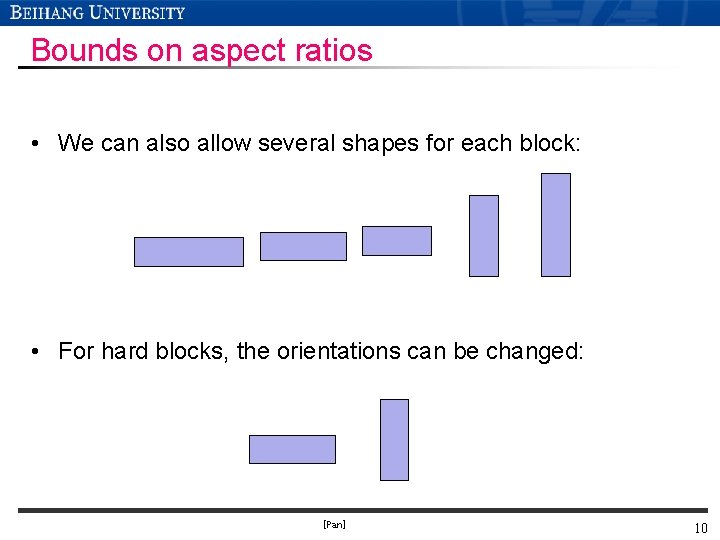

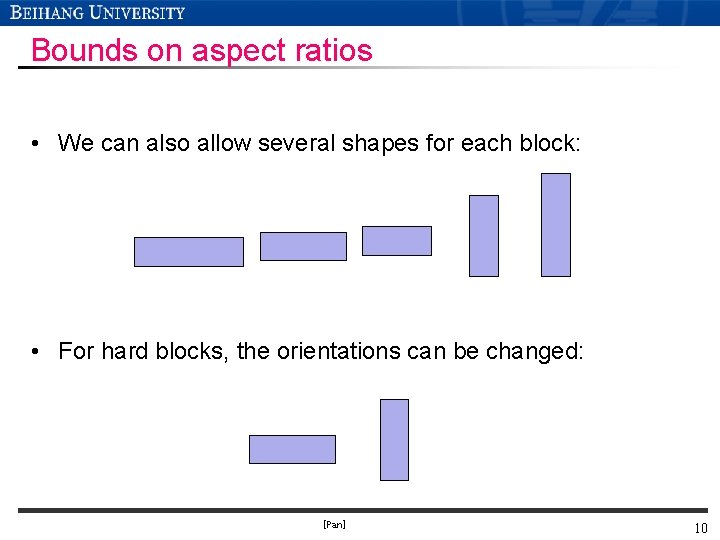

Bounds on aspect ratios • We can also allow several shapes for each block: • For hard blocks, the orientations can be changed: [Pan] 10

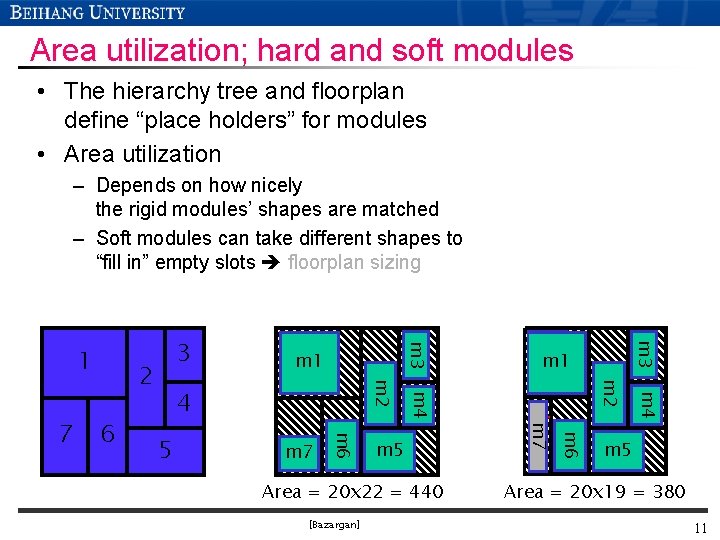

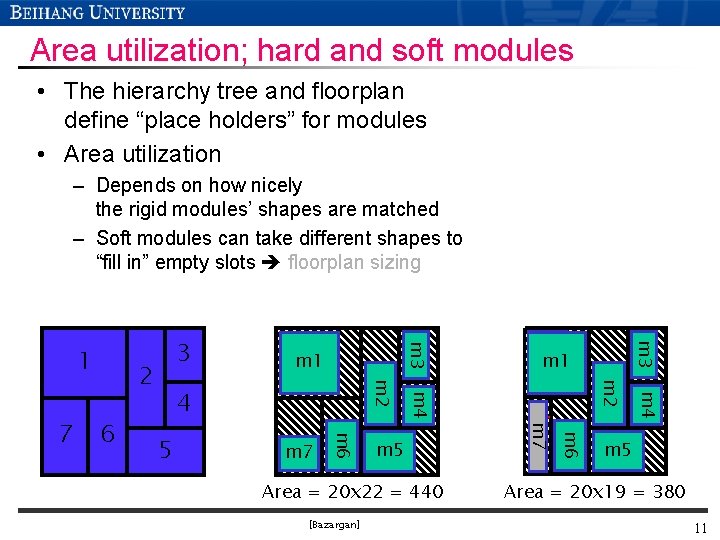

Area utilization; hard and soft modules • The hierarchy tree and floorplan define “place holders” for modules • Area utilization – Depends on how nicely the rigid modules’ shapes are matched – Soft modules can take different shapes to “fill in” empty slots floorplan sizing m 3 m 7 m 4 m 5 Area = 20 x 22 = 440 [Bazargan] m 2 m 7 m 6 5 m 7 4 m 1 m 4 6 m 3 2 m 1 m 6 7 3 m 2 1 m 5 Area = 20 x 19 = 380 11

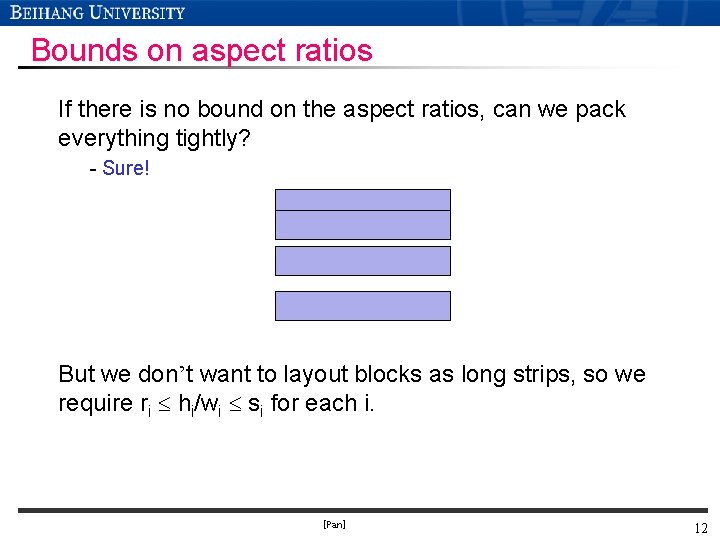

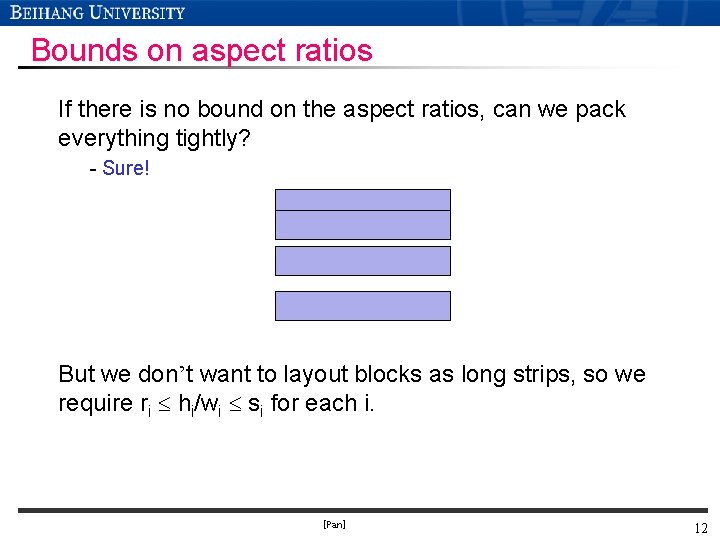

Bounds on aspect ratios If there is no bound on the aspect ratios, can we pack everything tightly? - Sure! But we don’t want to layout blocks as long strips, so we require ri hi/wi si for each i. [Pan] 12

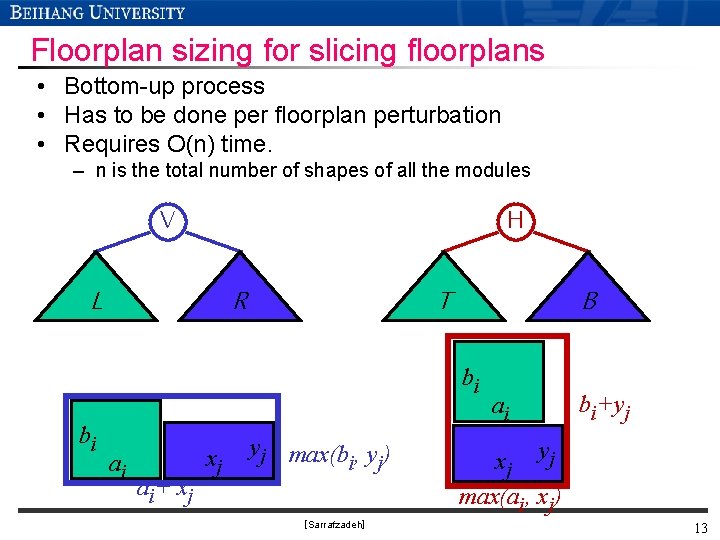

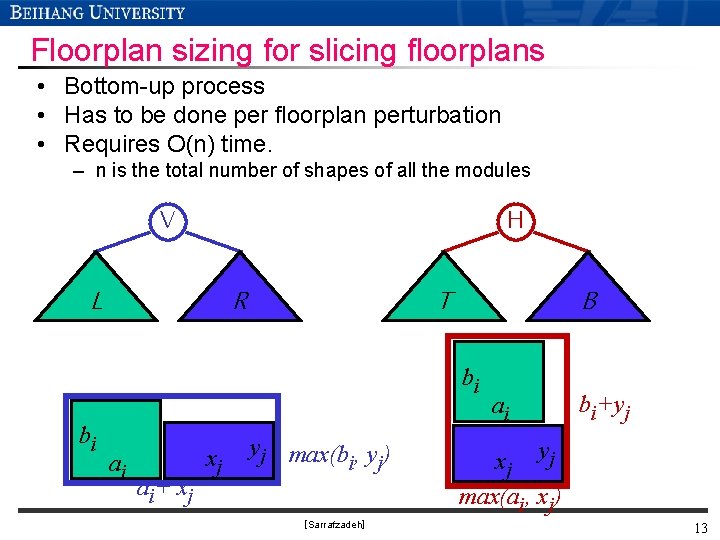

Floorplan sizing for slicing floorplans • Bottom-up process • Has to be done per floorplan perturbation • Requires O(n) time. – n is the total number of shapes of all the modules V H L R T B bi bi ai ai+ xj xj yj max(b , y ) i j [Sarrafzadeh] ai bi+yj xj yj max(ai, xj) 13

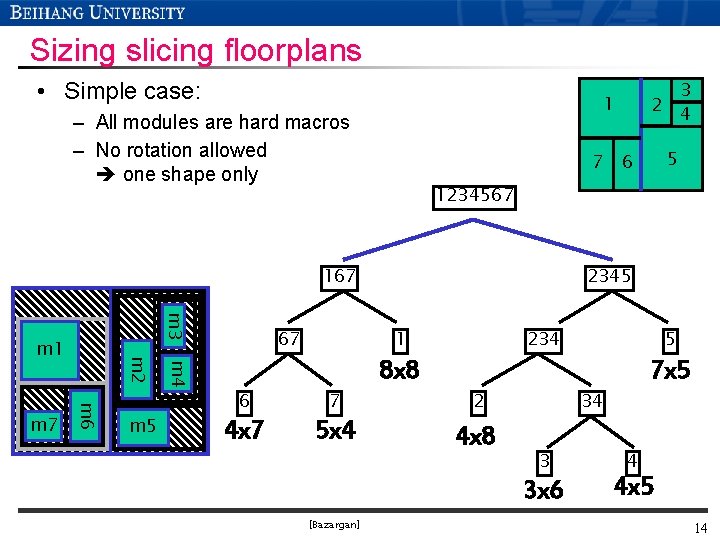

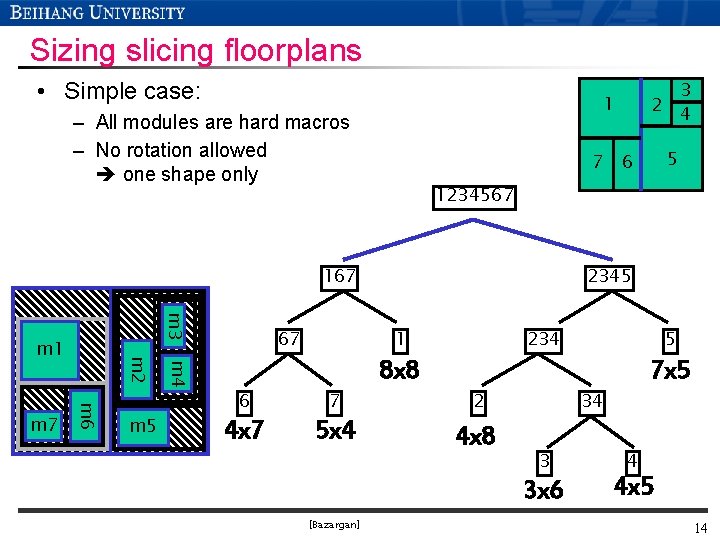

Sizing slicing floorplans • Simple case: – All modules are hard macros – No rotation allowed one shape only 9 x 15 m 3 m 5 m 4 m 6 m 7 m 2 m 1 7 5 2345 8 x 16 1 234 8 x 11 8 x 8 6 7 2 4 x 7 5 x 4 4 x 8 5 7 x 5 34 4 x 11 3 3 x 6 [Bazargan] 6 17 x 16 1234567 167 9 x 7 67 3 2 4 1 4 4 x 5 14

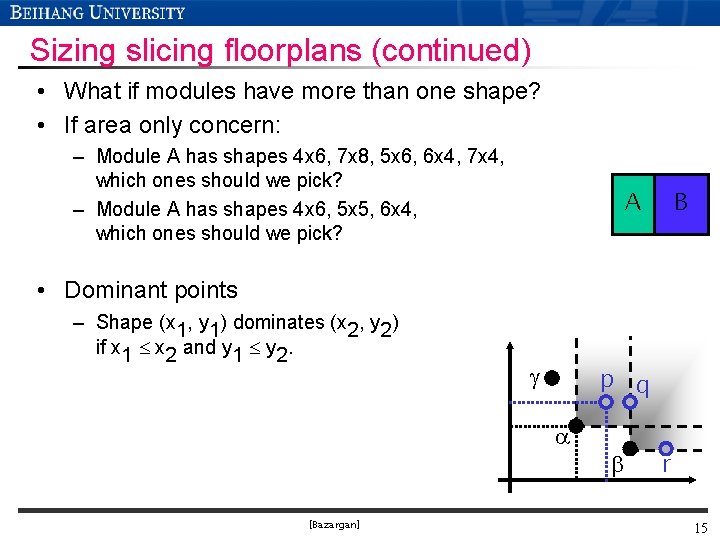

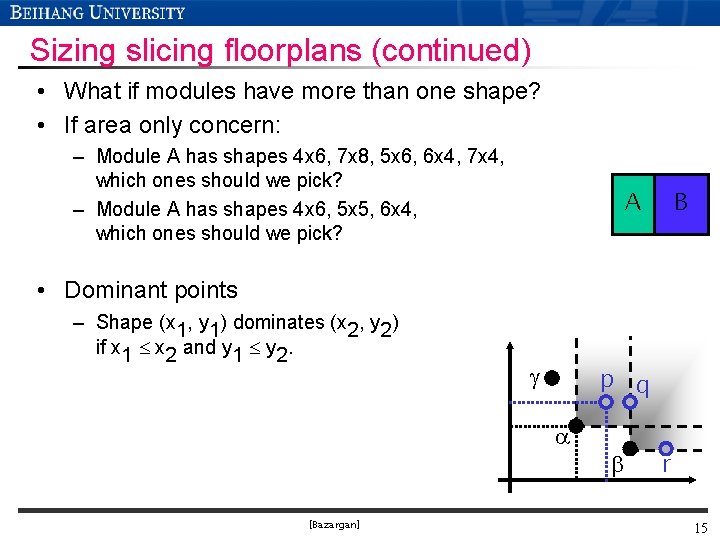

Sizing slicing floorplans (continued) • What if modules have more than one shape? • If area only concern: – Module A has shapes 4 x 6, 7 x 8, 5 x 6, 6 x 4, 7 x 4, which ones should we pick? – Module A has shapes 4 x 6, 5 x 5, 6 x 4, which ones should we pick? A B • Dominant points – Shape (x 1, y 1) dominates (x 2, y 2) if x 1 x 2 and y 1 y 2. a dominates p b dominates r b dominates q [Bazargan] g p q a b r 15

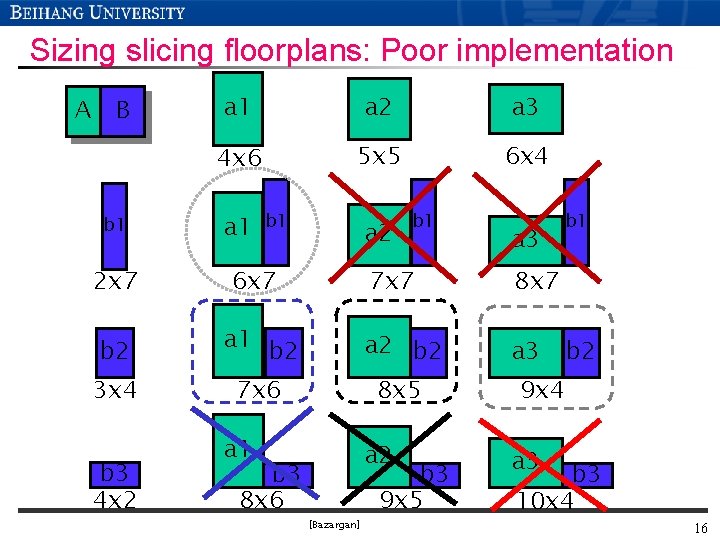

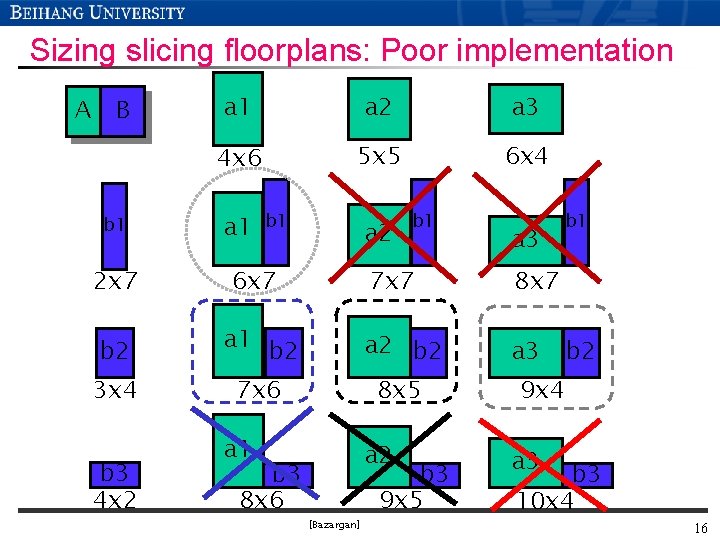

Sizing slicing floorplans: Poor implementation A B b 1 2 x 7 a 1 a 2 a 3 4 x 6 5 x 5 6 x 4 a 1 b 1 a 2 6 x 7 b 1 7 x 7 8 x 7 a 3 b 2 a 1 b 2 a 2 b 2 3 x 4 7 x 6 8 x 5 b 3 4 x 2 a 1 b 3 8 x 6 a 2 [Bazargan] a 3 b 3 9 x 5 b 1 b 2 9 x 4 a 3 b 3 10 x 4 16

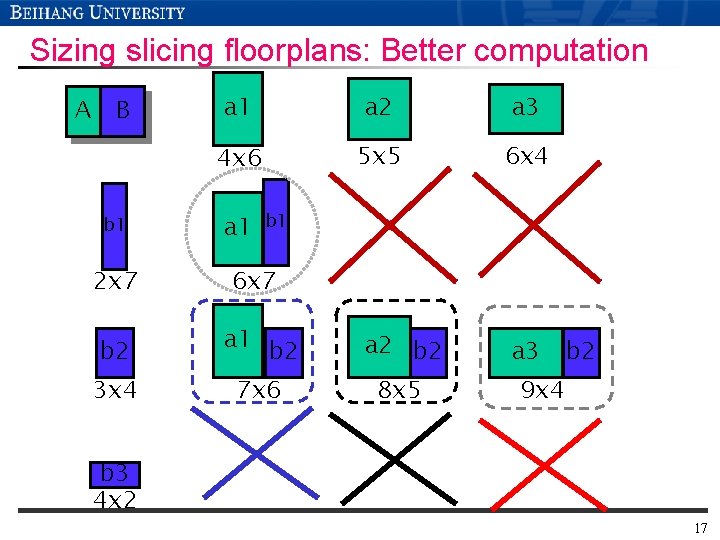

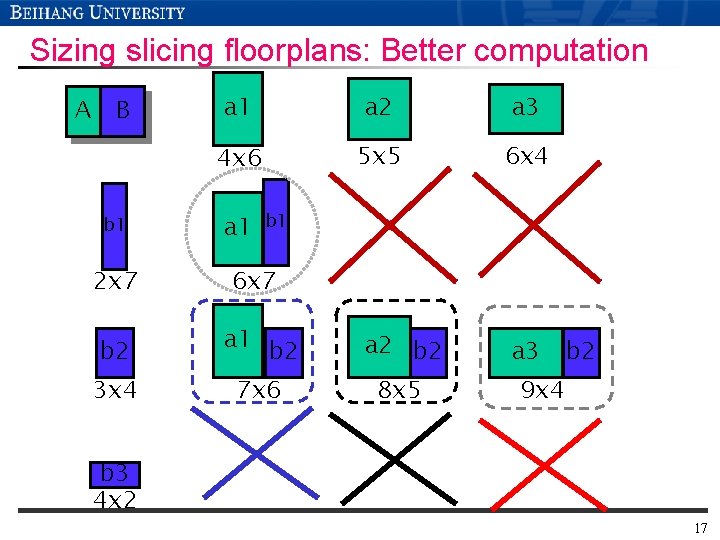

Sizing slicing floorplans: Better computation A B b 1 2 x 7 a 1 a 2 a 3 4 x 6 5 x 5 6 x 4 a 1 b 1 6 x 7 b 2 a 1 b 2 a 2 b 2 3 x 4 7 x 6 8 x 5 a 3 b 2 9 x 4 b 3 4 x 2 17

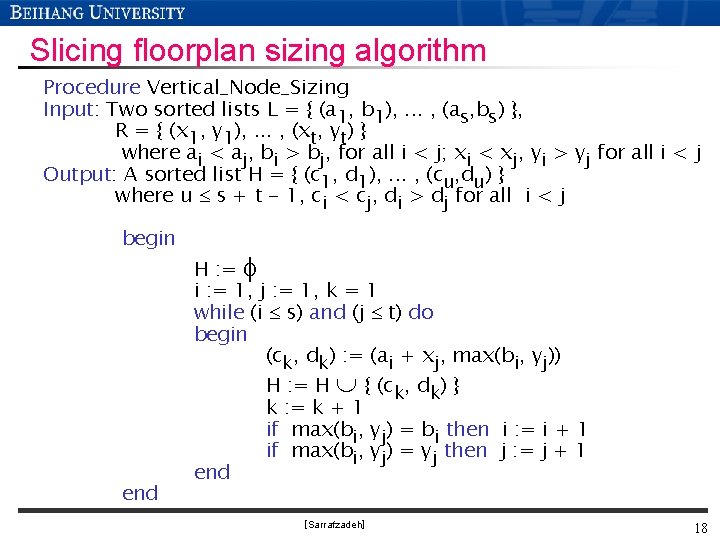

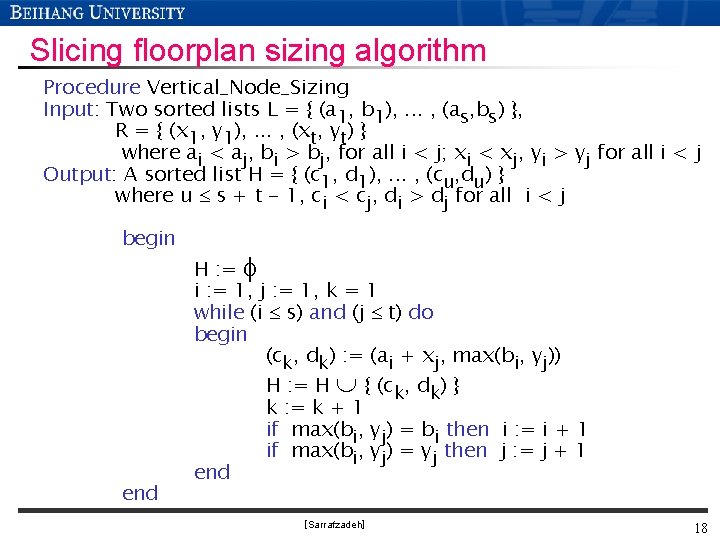

Slicing floorplan sizing algorithm Procedure Vertical_Node_Sizing Input: Two sorted lists L = { (a 1, b 1), . . . , (as, bs) }, R = { (x 1, y 1), . . . , (xt, yt) } where ai < aj, bi > bj, for all i < j; xi < xj, yi > yj for all i < j Output: A sorted list H = { (c 1, d 1), . . . , (cu, du) } where u s + t - 1, ci < cj, di > dj for all i < j begin end H : = i : = 1, j : = 1, k = 1 while (i s) and (j t) do begin (ck, dk) : = (ai + xj, max(bi, yj)) H : = H { (ck, dk) } k : = k + 1 if max(bi, yj) = bi then i : = i + 1 if max(bi, yj) = yj then j : = j + 1 end [Sarrafzadeh] 18

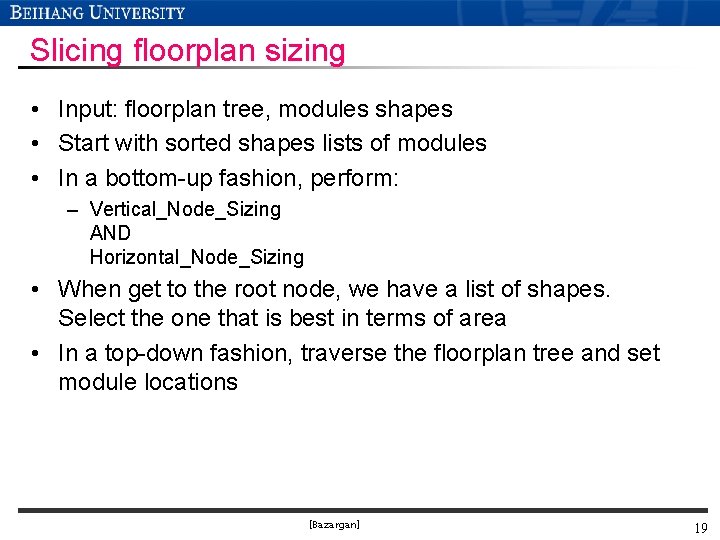

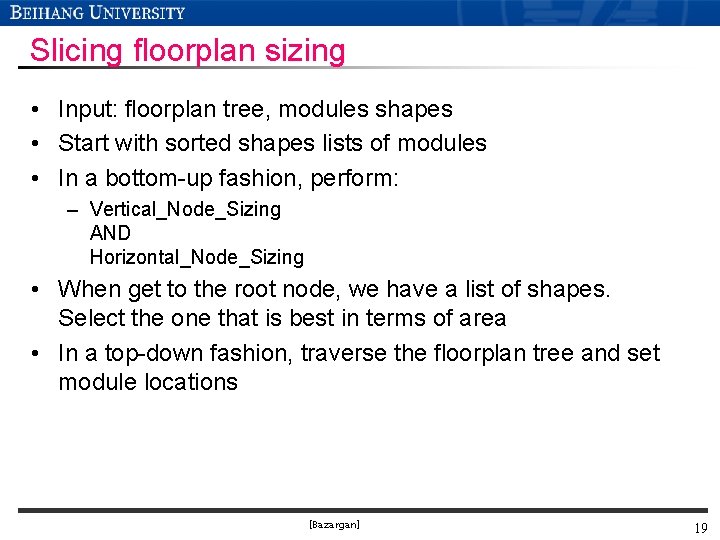

Slicing floorplan sizing • Input: floorplan tree, modules shapes • Start with sorted shapes lists of modules • In a bottom-up fashion, perform: – Vertical_Node_Sizing AND Horizontal_Node_Sizing • When get to the root node, we have a list of shapes. Select the one that is best in terms of area • In a top-down fashion, traverse the floorplan tree and set module locations [Bazargan] 19

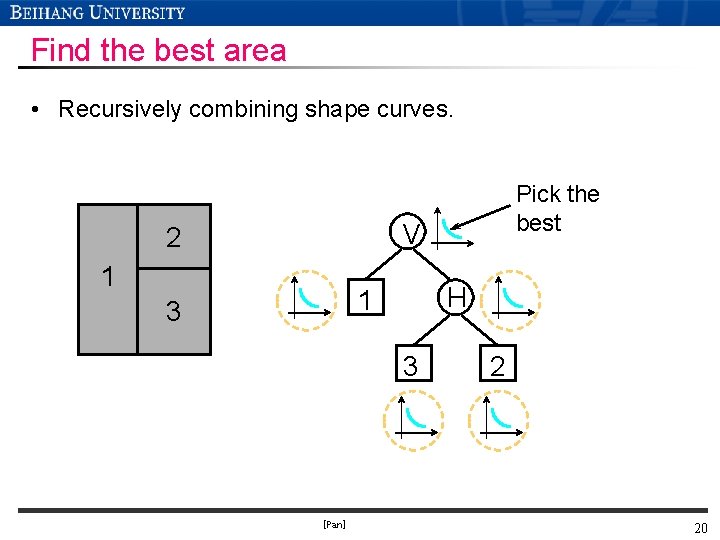

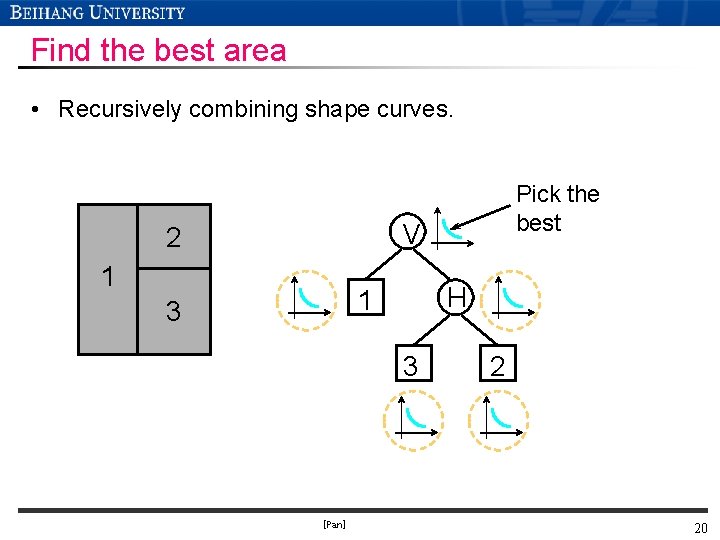

Find the best area • Recursively combining shape curves. Pick the best V 2 1 H 1 3 3 [Pan] 2 20

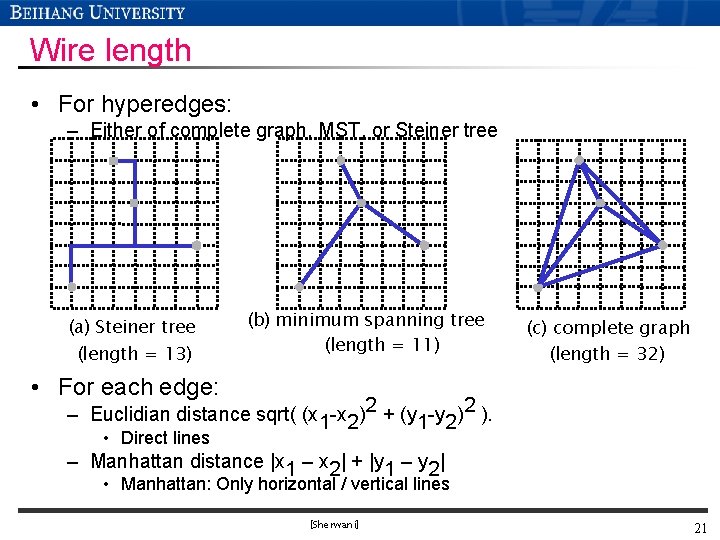

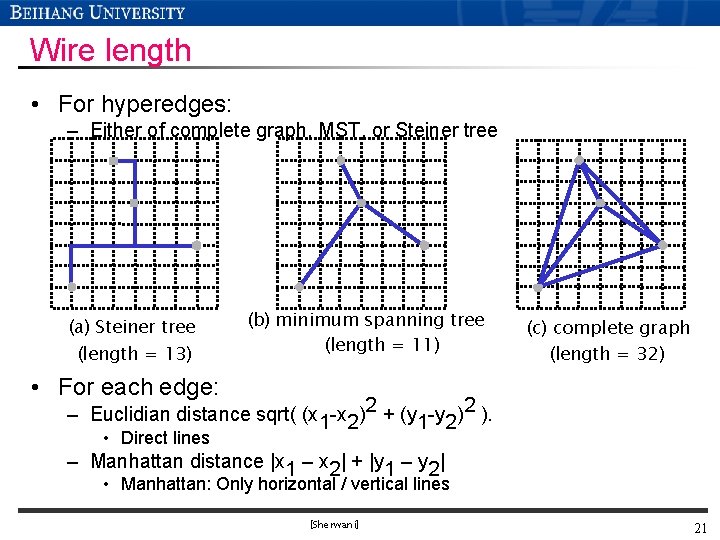

Wire length • For hyperedges: – Either of complete graph, MST, or Steiner tree (a) Steiner tree (length = 13) (b) minimum spanning tree (length = 11) (c) complete graph (length = 32) • For each edge: – Euclidian distance sqrt( (x 1 -x 2)2 + (y 1 -y 2)2 ). • Direct lines – Manhattan distance |x 1 – x 2| + |y 1 – y 2| • Manhattan: Only horizontal / vertical lines [Sherwani] 21

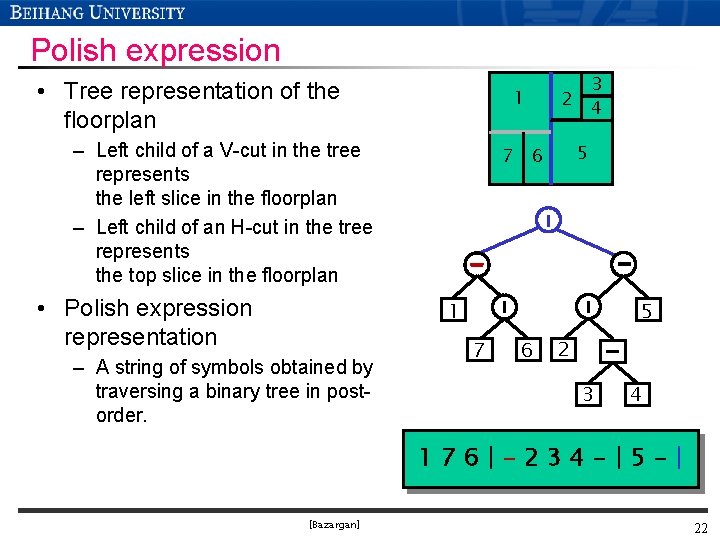

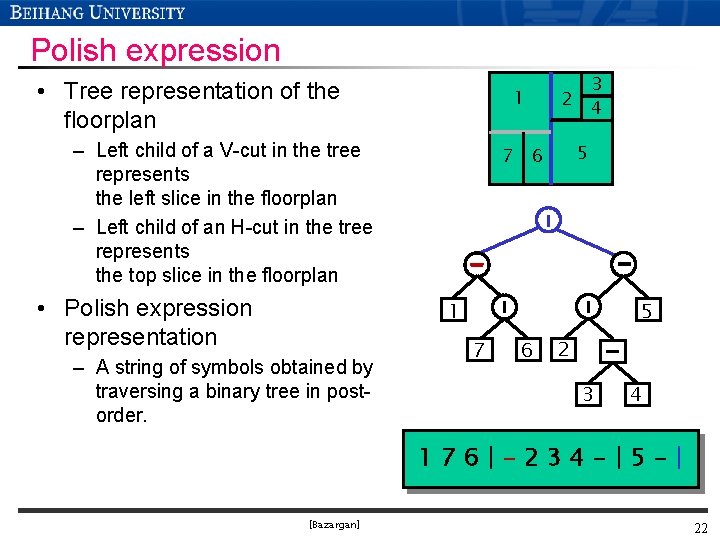

Polish expression • Tree representation of the floorplan 1 – Left child of a V-cut in the tree represents the left slice in the floorplan – Left child of an H-cut in the tree represents the top slice in the floorplan • Polish expression representation 3 2 4 7 5 6 1 – A string of symbols obtained by traversing a binary tree in postorder. 5 7 6 2 3 4 176|-234 -|5 -| [Bazargan] 22

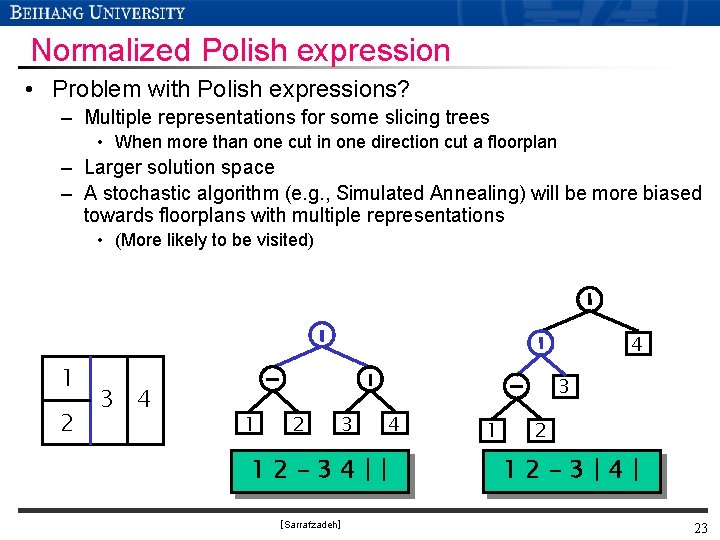

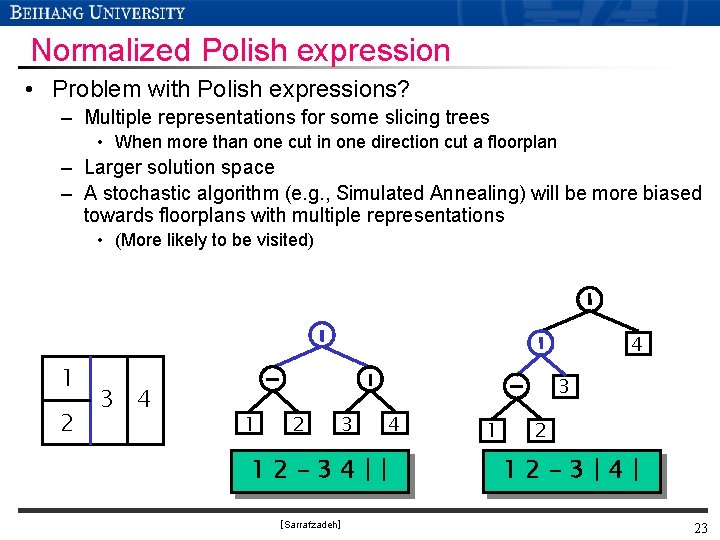

Normalized Polish expression • Problem with Polish expressions? – Multiple representations for some slicing trees • When more than one cut in one direction cut a floorplan – Larger solution space – A stochastic algorithm (e. g. , Simulated Annealing) will be more biased towards floorplans with multiple representations • (More likely to be visited) 4 1 2 3 4 3 1 2 3 4 12 -34|| [Sarrafzadeh] 1 2 12 -3|4| 23

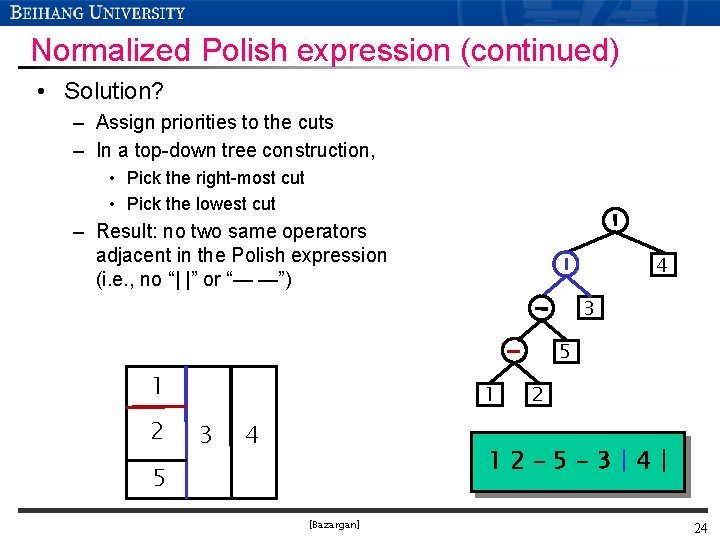

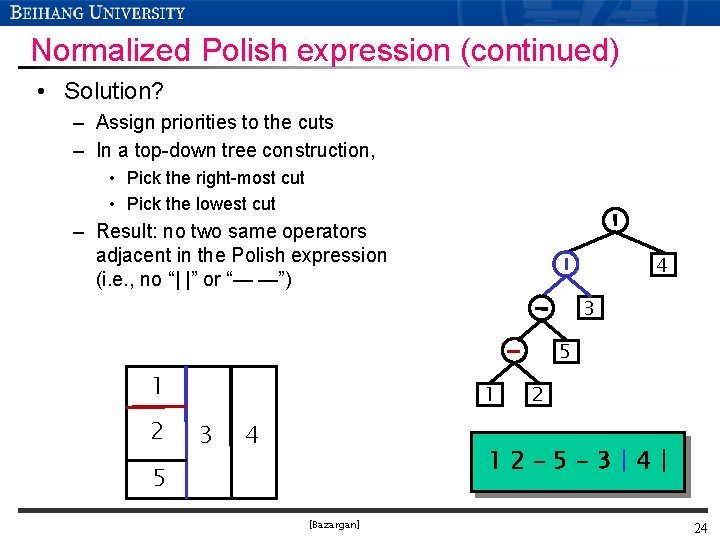

Normalized Polish expression (continued) • Solution? – Assign priorities to the cuts – In a top-down tree construction, • Pick the right-most cut • Pick the lowest cut – Result: no two same operators adjacent in the Polish expression (i. e. , no “| |” or “— —”) 4 3 5 1 2 1 3 4 2 12– 5 -3|4| 5 [Bazargan] 24

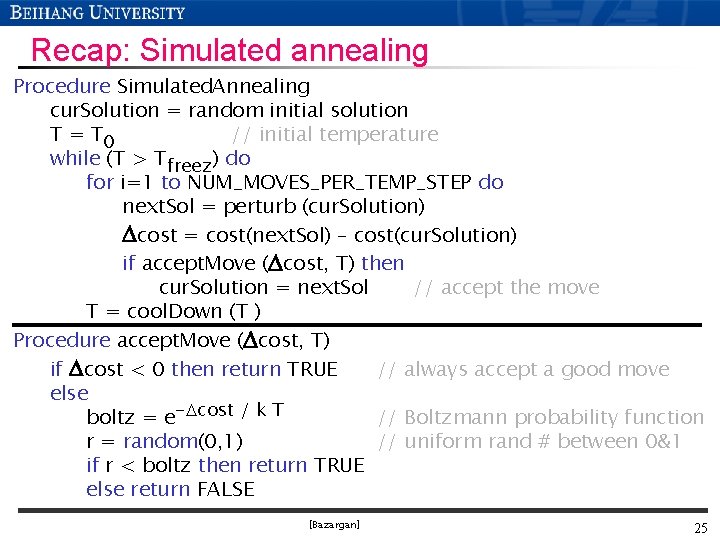

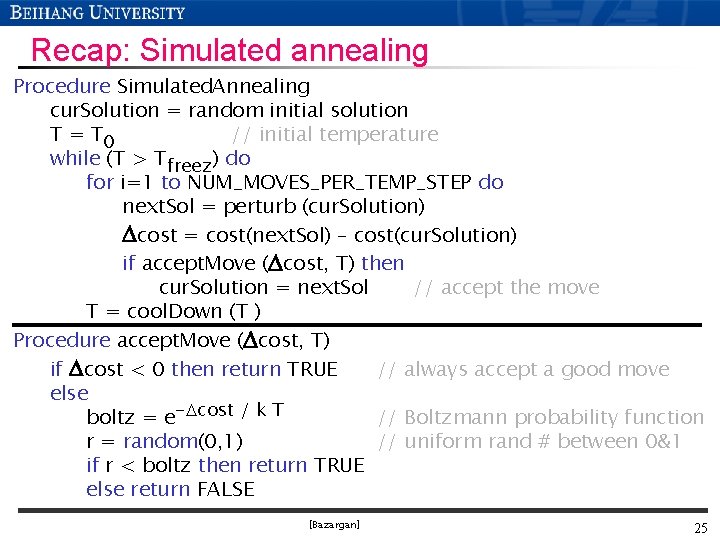

Recap: Simulated annealing Procedure Simulated. Annealing cur. Solution = random initial solution T = T 0 // initial temperature while (T > Tfreez) do for i=1 to NUM_MOVES_PER_TEMP_STEP do next. Sol = perturb (cur. Solution) Dcost = cost(next. Sol) – cost(cur. Solution) if accept. Move (Dcost, T) then cur. Solution = next. Sol // accept the move T = cool. Down (T ) Procedure accept. Move (Dcost, T) if Dcost < 0 then return TRUE // always accept a good move else boltz = e-Dcost / k T // Boltzmann probability function r = random(0, 1) // uniform rand # between 0&1 if r < boltz then return TRUE else return FALSE [Bazargan] 25