Wednesday November 25 2020 4 80868088 CPU Wednesday

Wednesday, November 25, 2020 4

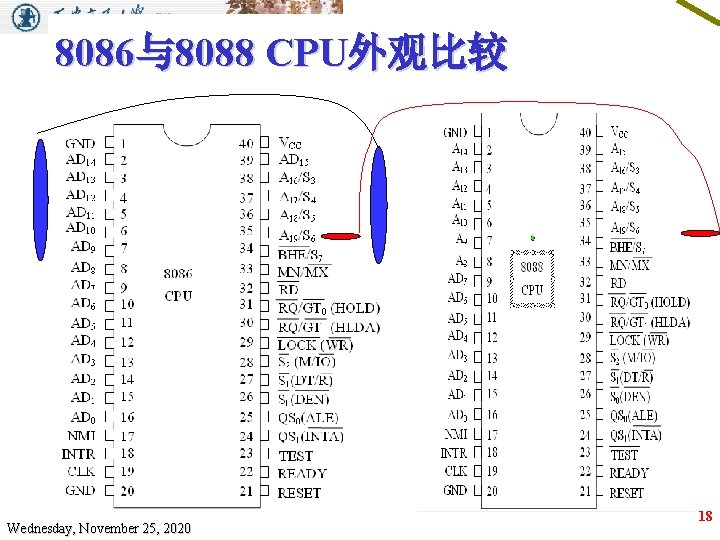

8086与8088 CPU外观比较 Wednesday, November 25, 2020 18

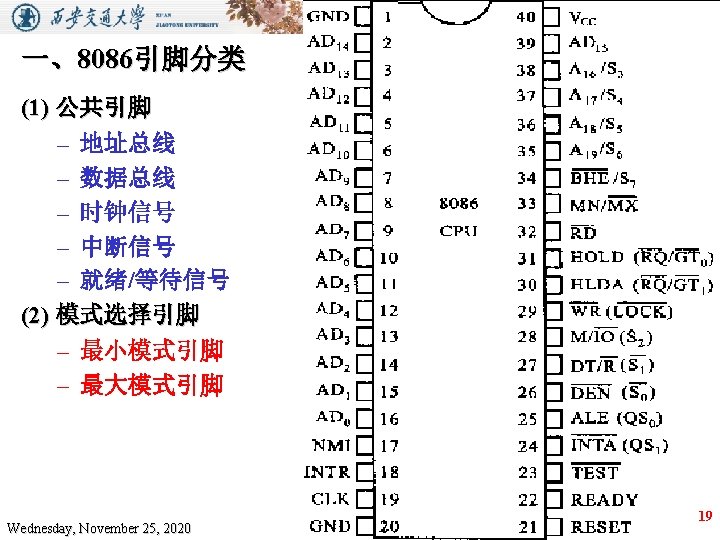

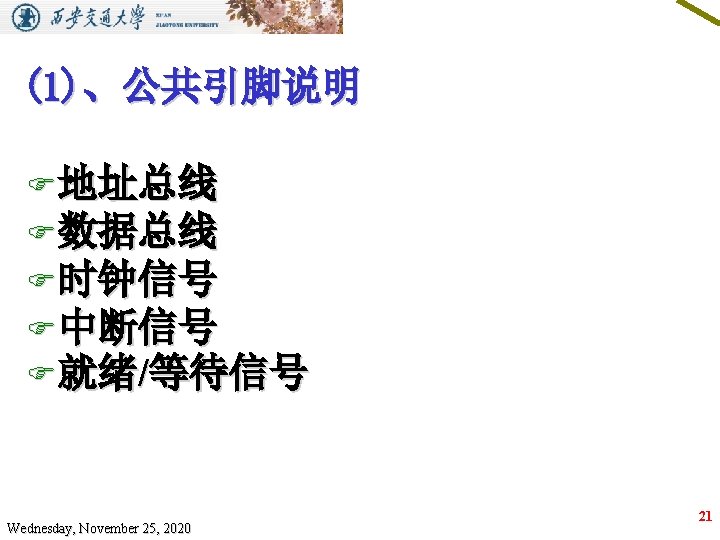

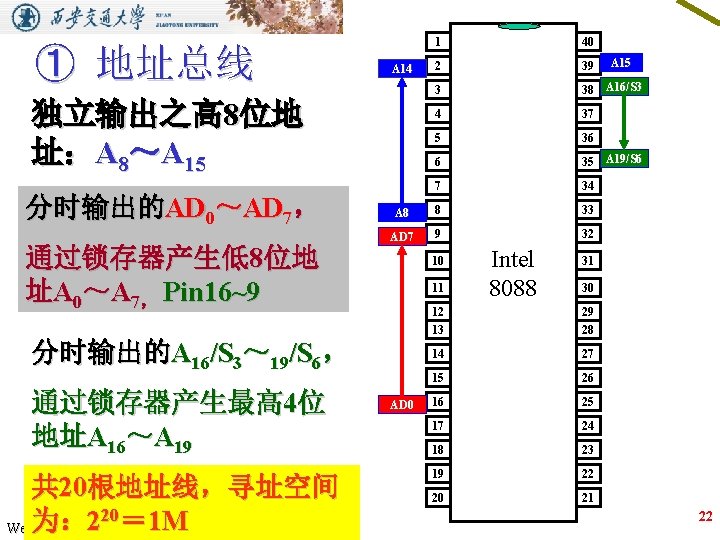

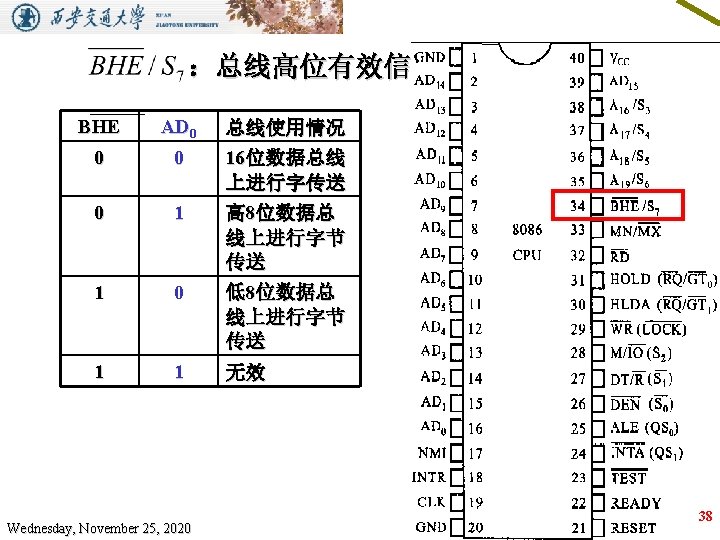

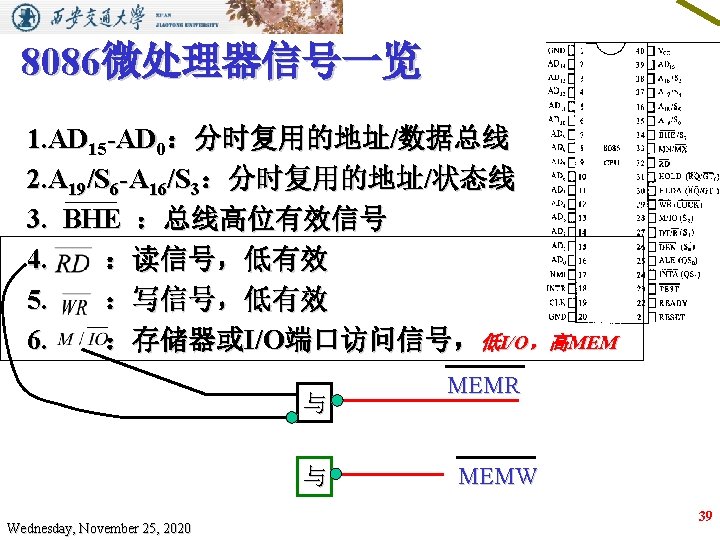

① 地址总线 1 40 2 39 3 38 A 16/S 3 4 37 5 36 6 35 A 19/S 6 7 34 A 8 8 33 AD 7 9 32 A 14 独立输出之高 8位地 址:A 8~A 15 分时输出的AD 0~AD 7, 通过锁存器产生低8位地 址A 0~A 7, Pin 16~9 10 11 分时输出的A 16/S 3~ 19/S 6, 通过锁存器产生最高 4位 地址A 16~A 19 共 20根地址线,寻址空间 为:November 220= 25, 1 M Wednesday, 2020 AD 0 Intel 8088 A 15 31 30 12 13 29 28 14 27 15 26 16 25 17 24 18 23 19 22 20 21 22

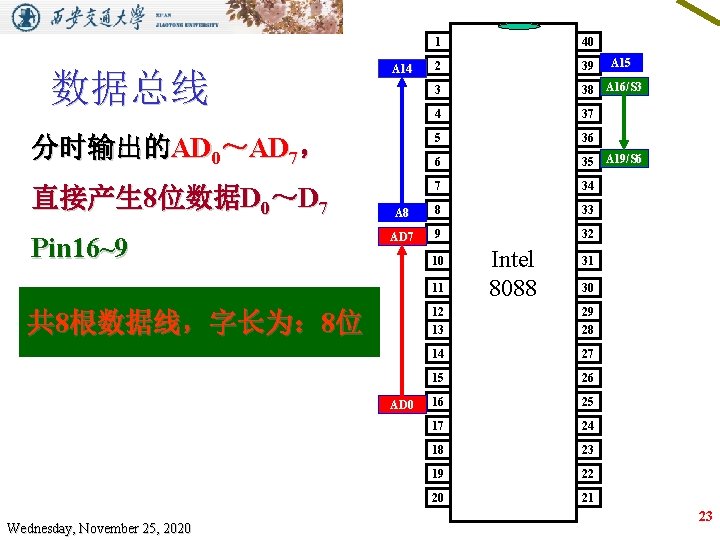

1 40 2 39 3 38 A 16/S 3 4 37 分时输出的AD 0~AD 7, 5 36 6 35 A 19/S 6 直接产生 8位数据D 0~D 7 7 34 A 8 8 33 AD 7 9 32 数据总线 Pin 16~9 A 14 10 11 共 8根数据线,字长为: 8位 AD 0 Wednesday, November 25, 2020 Intel 8088 A 15 31 30 12 13 29 28 14 27 15 26 16 25 17 24 18 23 19 22 20 21 23

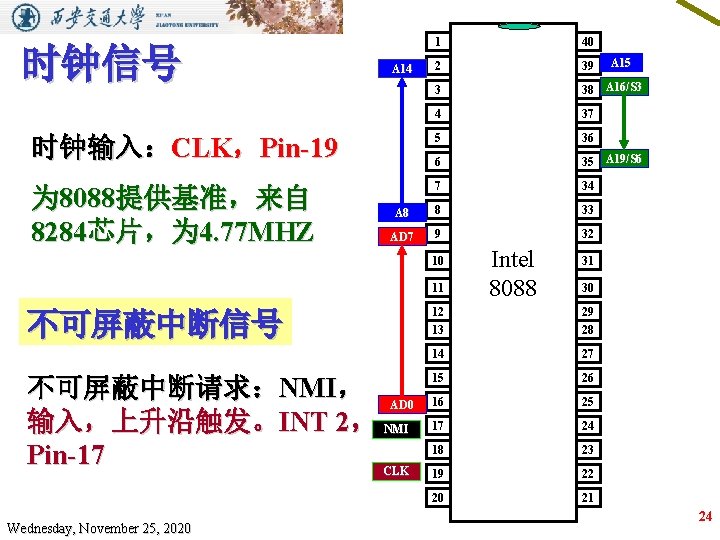

1 40 2 39 3 38 A 16/S 3 4 37 时钟输入:CLK,Pin-19 5 36 6 35 A 19/S 6 为 8088提供基准,来自 8284芯片,为 4. 77 MHZ 7 34 A 8 8 33 AD 7 9 32 时钟信号 A 14 10 11 不可屏蔽中断信号 不可屏蔽中断请求:NMI, AD 0 输入,上升沿触发。INT 2, NMI Pin-17 CLK Wednesday, November 25, 2020 Intel 8088 A 15 31 30 12 13 29 28 14 27 15 26 16 25 17 24 18 23 19 22 20 21 24

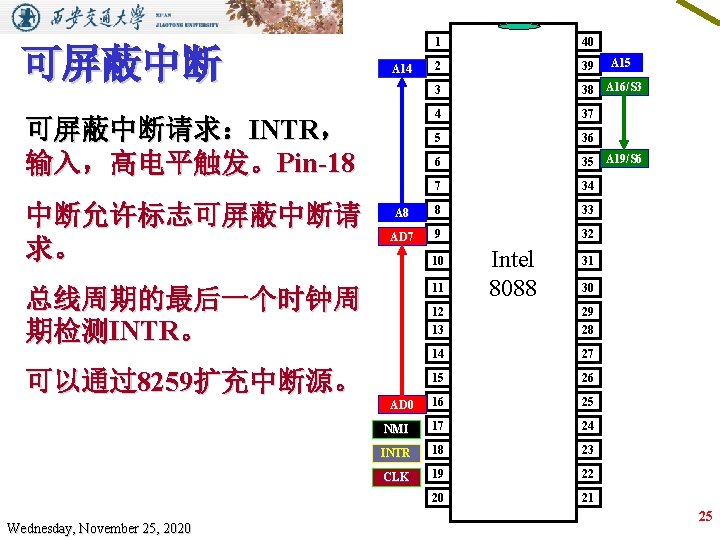

可屏蔽中断 1 40 2 39 3 38 A 16/S 3 4 37 5 36 6 35 A 19/S 6 7 34 A 8 8 33 AD 7 9 32 A 14 可屏蔽中断请求:INTR, 输入,高电平触发。Pin-18 中断允许标志可屏蔽中断请 求。 10 总线周期的最后一个时钟周 期检测INTR。 11 可以通过8259扩充中断源。 31 30 12 13 29 28 14 27 15 26 16 25 NMI 17 24 INTR 18 23 CLK 19 22 20 21 AD 0 Wednesday, November 25, 2020 Intel 8088 A 15 25

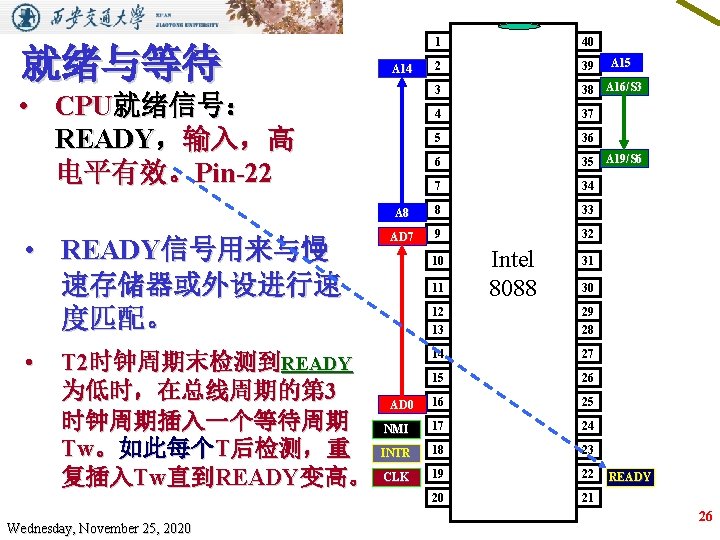

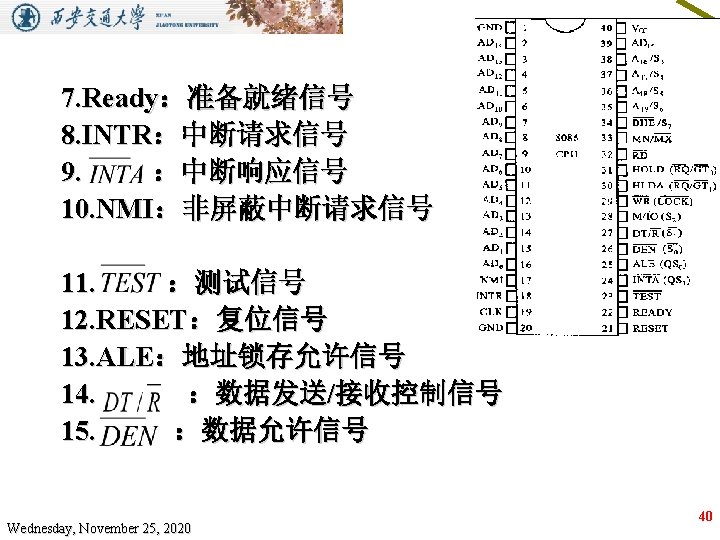

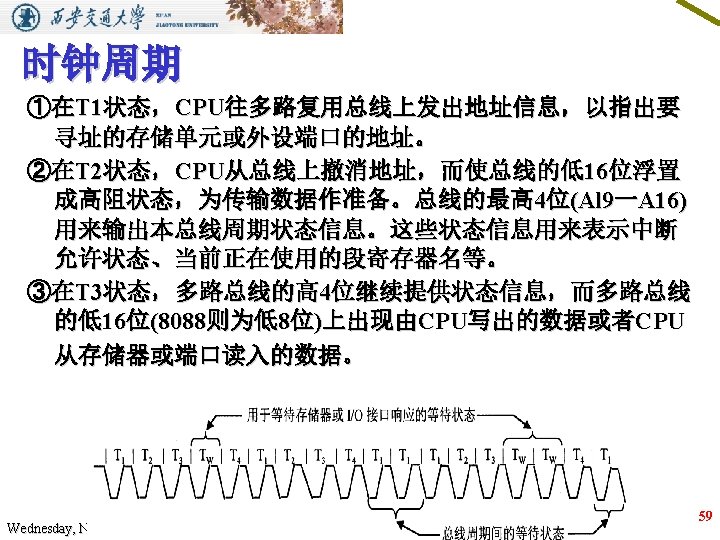

就绪与等待 1 40 2 39 3 38 A 16/S 3 4 37 5 36 6 35 A 19/S 6 7 34 A 8 8 33 AD 7 9 32 A 14 • CPU就绪信号: READY,输入,高 电平有效。Pin-22 • READY信号用来与慢 速存储器或外设进行速 度匹配。 • T 2时钟周期末检测到READY 为低时,在总线周期的第 3 时钟周期插入一个等待周期 Tw。如此每个T后检测,重 复插入Tw直到READY变高。 Wednesday, November 25, 2020 10 11 Intel 8088 31 30 12 13 29 28 14 27 15 26 16 25 NMI 17 24 INTR 18 23 CLK 19 22 20 21 AD 0 A 15 READY 26

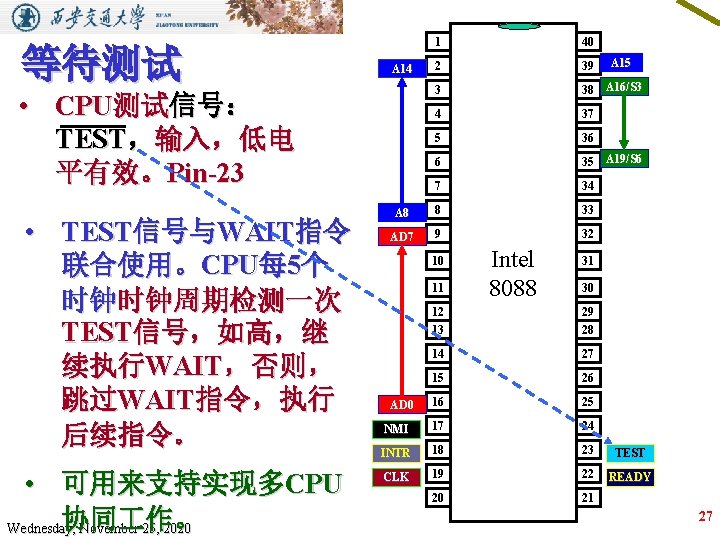

等待测试 1 40 2 39 3 38 A 16/S 3 4 37 5 36 6 35 A 19/S 6 7 34 A 8 8 33 AD 7 9 32 A 14 • CPU测试信号: TEST,输入,低电 平有效。Pin-23 • TEST信号与WAIT指令 联合使用。CPU每 5个 时钟时钟周期检测一次 TEST信号,如高,继 续执行WAIT,否则, 跳过WAIT指令,执行 后续指令。 • 可用来支持实现多CPU 协同 作。 Wednesday, November 25, 2020 10 11 Intel 8088 A 15 31 30 12 13 29 28 14 27 15 26 16 25 NMI 17 24 INTR 18 23 TEST CLK 19 22 READY 20 21 AD 0 27

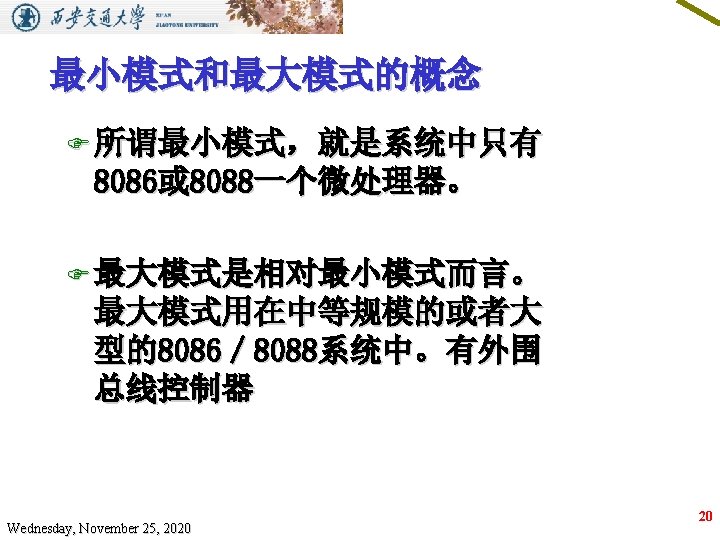

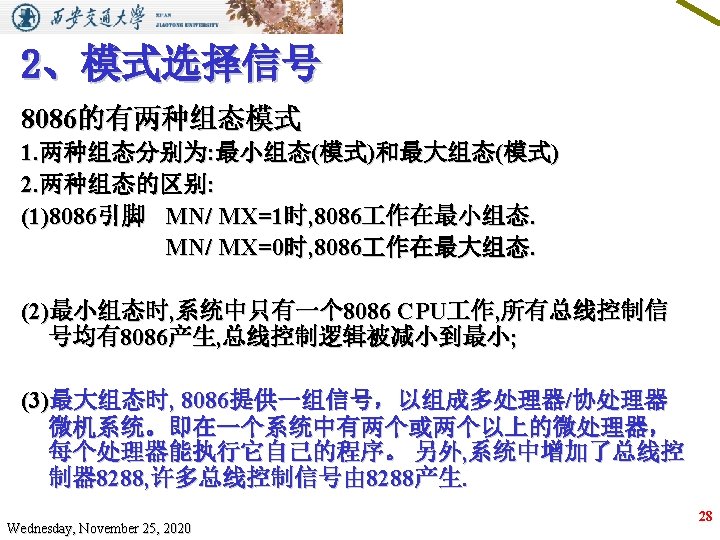

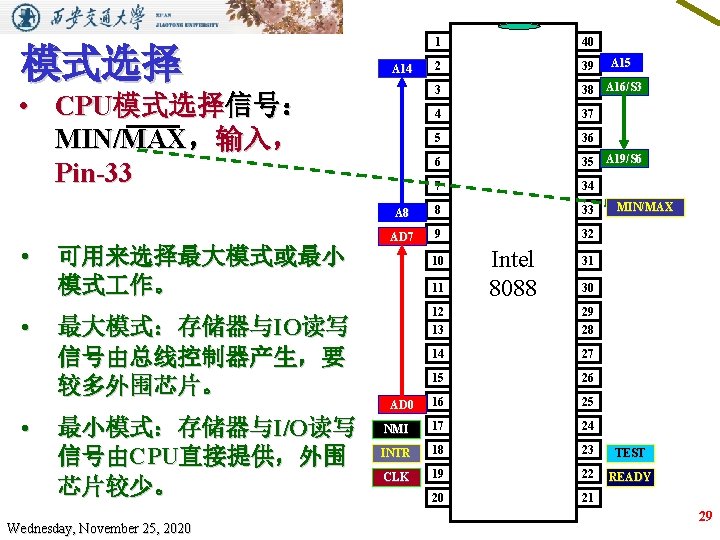

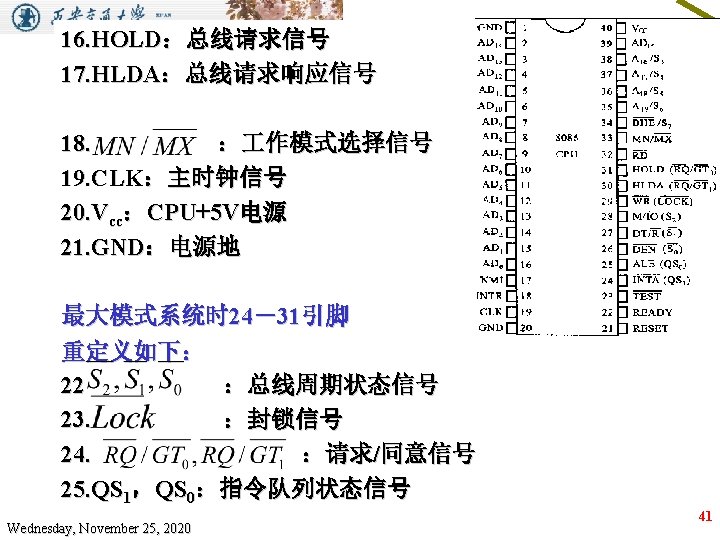

模式选择 1 40 2 39 3 38 A 16/S 3 4 37 5 36 6 35 A 19/S 6 7 34 A 8 8 33 AD 7 9 32 A 14 • CPU模式选择信号: MIN/MAX,输入, Pin-33 • • • 可用来选择最大模式或最小 模式 作。 最大模式:存储器与IO读写 信号由总线控制器产生,要 较多外围芯片。 最小模式:存储器与I/O读写 信号由CPU直接提供,外围 芯片较少。 Wednesday, November 25, 2020 10 11 Intel 8088 A 15 MIN/MAX 31 30 12 13 29 28 14 27 15 26 16 25 NMI 17 24 INTR 18 23 TEST CLK 19 22 READY 20 21 AD 0 29

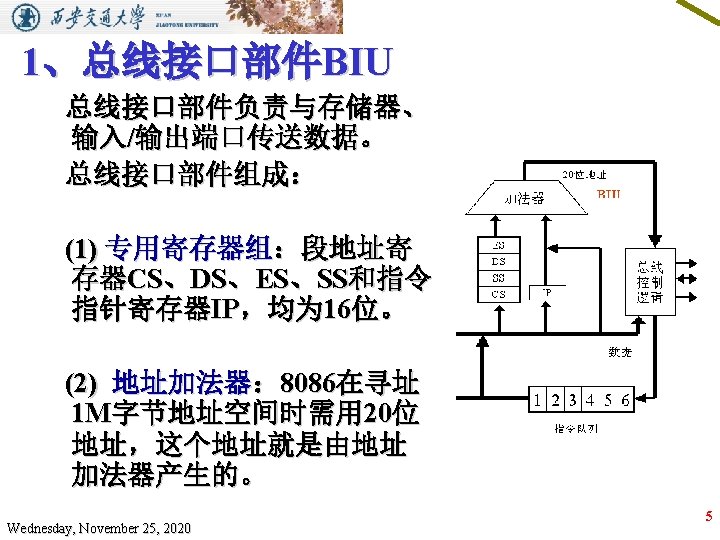

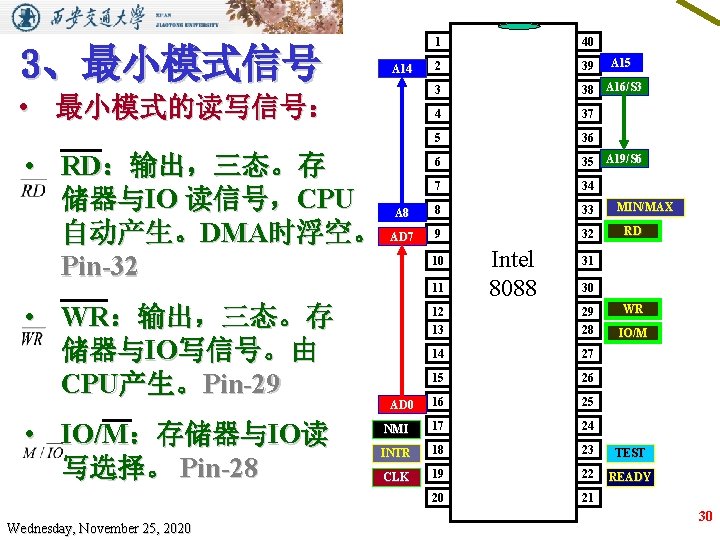

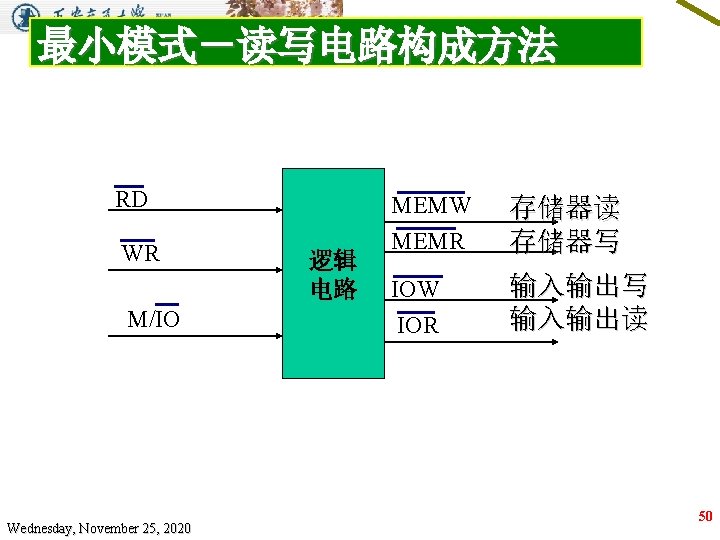

3、最小模式信号 1 40 2 39 3 38 A 16/S 3 4 37 5 36 6 35 A 19/S 6 7 34 A 8 8 33 AD 7 9 32 A 14 • 最小模式的读写信号: • RD:输出,三态。存 储器与IO 读信号,CPU 自动产生。DMA时浮空。 Pin-32 • WR:输出,三态。存 储器与IO写信号。由 CPU产生。Pin-29 • IO/M:存储器与IO读 写选择。 Pin-28 Wednesday, November 25, 2020 10 11 Intel 8088 A 15 MIN/MAX RD 31 30 WR 12 13 29 28 14 27 15 26 16 25 NMI 17 24 INTR 18 23 TEST CLK 19 22 READY 20 21 AD 0 IO/M 30

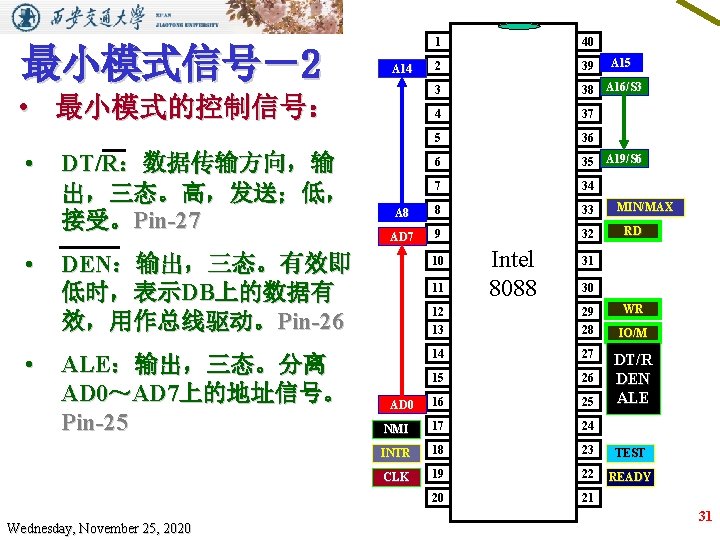

最小模式信号-2 1 40 2 39 3 38 A 16/S 3 4 37 5 36 6 35 A 19/S 6 7 34 A 8 8 33 AD 7 9 32 A 14 • 最小模式的控制信号: • • • DT/R:数据传输方向,输 出,三态。高,发送;低, 接受。Pin-27 Intel 8088 A 15 MIN/MAX RD DEN:输出,三态。有效即 低时,表示DB上的数据有 效,用作总线驱动。Pin-26 10 12 13 29 28 ALE:输出,三态。分离 AD 0~AD 7上的地址信号。 Pin-25 14 27 15 26 16 25 NMI 17 24 INTR 18 23 TEST CLK 19 22 READY 20 21 Wednesday, November 25, 2020 11 AD 0 31 30 WR IO/M DT/R DEN ALE 31

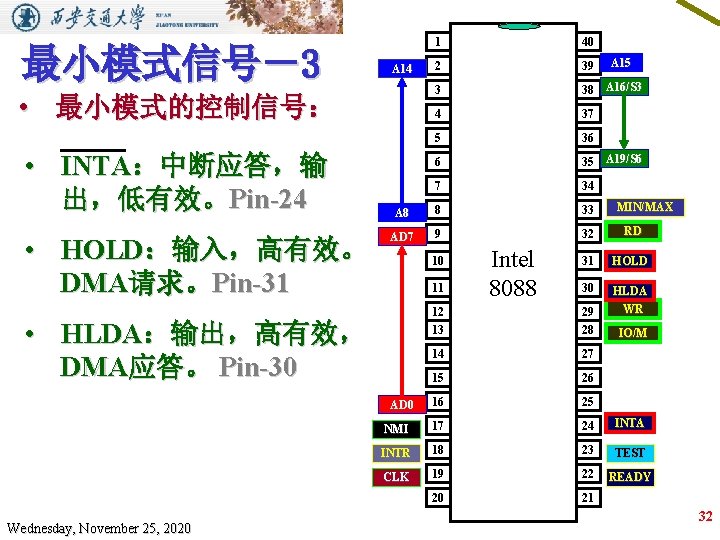

最小模式信号-3 1 40 2 39 3 38 A 16/S 3 4 37 5 36 6 35 A 19/S 6 7 34 A 8 8 33 AD 7 9 32 RD 31 HOLD 30 HLDA WR A 14 • 最小模式的控制信号: • INTA:中断应答,输 出,低有效。Pin-24 • HOLD:输入,高有效。 DMA请求。Pin-31 10 11 MIN/MAX 12 13 29 28 14 27 15 26 16 25 NMI 17 24 INTA INTR 18 23 TEST CLK 19 22 READY 20 21 • HLDA:输出,高有效, DMA应答。 Pin-30 AD 0 Wednesday, November 25, 2020 Intel 8088 A 15 IO/M 32

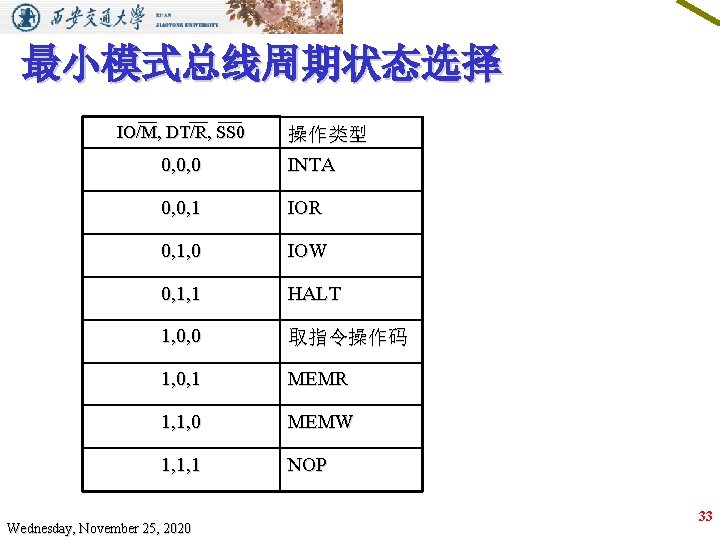

最小模式总线周期状态选择 IO/M, DT/R, SS 0 0, 0, 0 操作类型 INTA 0, 0, 1 IOR 0, 1, 0 IOW 0, 1, 1 HALT 1, 0, 0 取指令操作码 1, 0, 1 MEMR 1, 1, 0 MEMW 1, 1, 1 NOP Wednesday, November 25, 2020 33

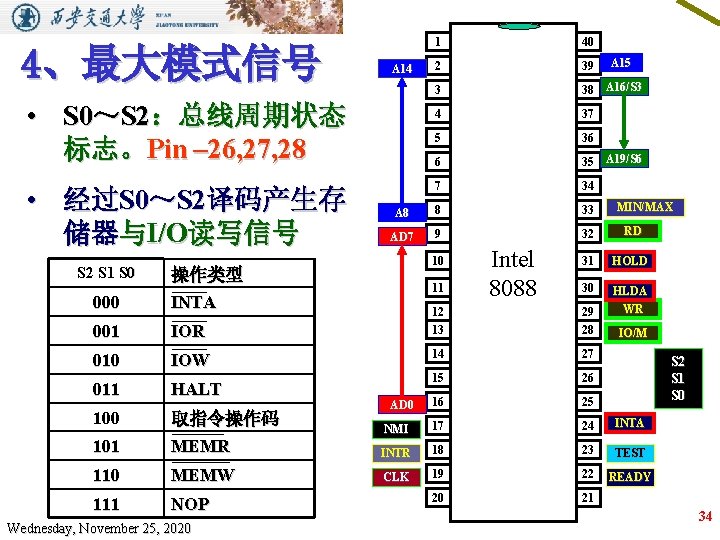

4、最大模式信号 1 40 2 39 3 38 A 16/S 3 4 37 5 36 6 35 A 19/S 6 7 34 A 8 8 33 AD 7 9 32 RD 31 HOLD 30 HLDA WR A 14 • S 0~S 2:总线周期状态 标志。Pin – 26, 27, 28 • 经过S 0~S 2译码产生存 储器与I/O读写信号 S 2 S 1 S 0 000 操作类型 INTA 001 IOR 010 IOW 011 HALT 100 101 取指令操作码 MEMR 110 MEMW 111 NOP Wednesday, November 25, 2020 10 11 Intel 8088 A 15 MIN/MAX 12 13 29 28 14 27 15 26 16 25 NMI 17 24 INTA INTR 18 23 TEST CLK 19 22 READY 20 21 AD 0 IO/M S 2 S 1 S 0 34

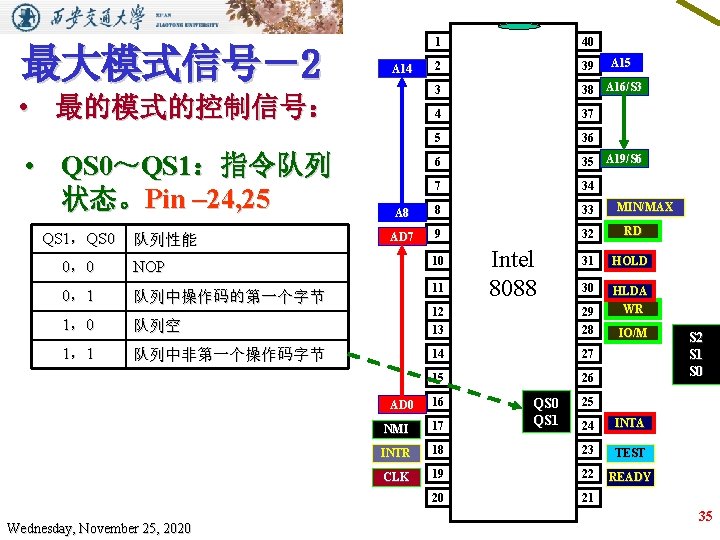

最大模式信号-2 1 40 2 39 3 38 A 16/S 3 4 37 5 36 6 35 A 19/S 6 7 34 A 8 8 33 AD 7 9 32 RD 31 HOLD 30 HLDA WR A 14 • 最的模式的控制信号: • QS 0~QS 1:指令队列 状态。Pin – 24, 25 QS 1,QS 0 队列性能 0,0 NOP 0,1 队列中操作码的第一个字节 1,0 1,1 10 11 Intel 8088 队列空 12 13 29 28 队列中非第一个操作码字节 14 27 15 26 AD 0 Wednesday, November 25, 2020 16 QS 0 QS 1 A 15 MIN/MAX IO/M 25 24 INTA 18 23 TEST 19 22 READY 20 21 NMI 17 INTR CLK S 2 S 1 S 0 35

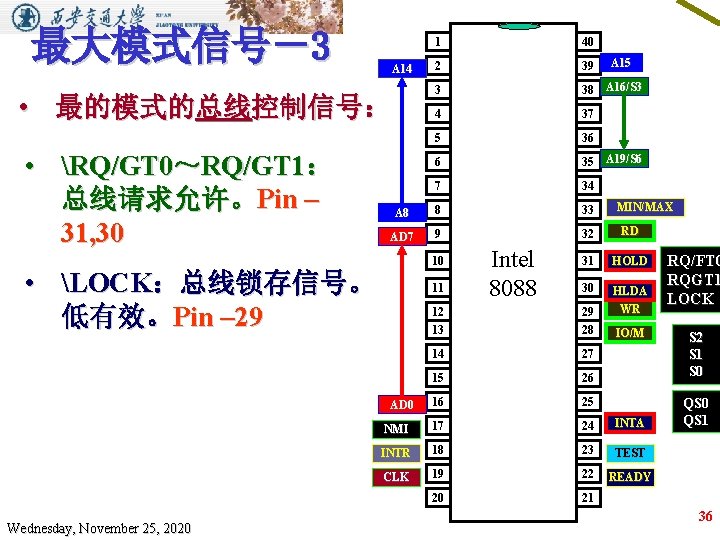

最大模式信号-3 1 40 2 39 3 38 A 16/S 3 4 37 5 36 6 35 A 19/S 6 7 34 A 8 8 33 AD 7 9 32 RD 31 HOLD 30 HLDA WR A 14 • 最的模式的总线控制信号: • RQ/GT 0~RQ/GT 1: 总线请求允许。Pin – 31, 30 10 • LOCK:总线锁存信号。 低有效。Pin – 29 11 MIN/MAX 12 13 29 28 14 27 15 26 16 25 NMI 17 24 INTA INTR 18 23 TEST CLK 19 22 READY 20 21 AD 0 Wednesday, November 25, 2020 Intel 8088 A 15 IO/M RQ/FT 0 RQGT 1 LOCK S 2 S 1 S 0 QS 1 36

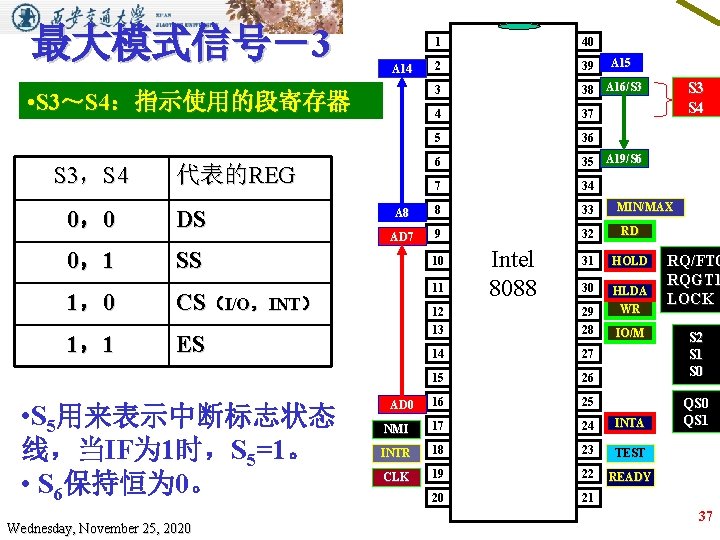

最大模式信号-3 1 40 2 39 3 38 A 16/S 3 4 37 5 36 6 35 A 19/S 6 7 34 A 8 8 33 AD 7 9 32 RD 31 HOLD 30 HLDA WR A 14 • S 3~S 4:指示使用的段寄存器 S 3,S 4 代表的REG 0,0 DS 0,1 SS 1,0 CS(I/O,INT) 1,1 ES • S 5用来表示中断标志状态 线,当IF为 1时,S 5=1。 • S 6保持恒为 0。 Wednesday, November 25, 2020 10 11 Intel 8088 A 15 MIN/MAX 12 13 29 28 14 27 15 26 16 25 NMI 17 24 INTA INTR 18 23 TEST CLK 19 22 READY 20 21 AD 0 S 3 S 4 IO/M RQ/FT 0 RQGT 1 LOCK S 2 S 1 S 0 QS 1 37

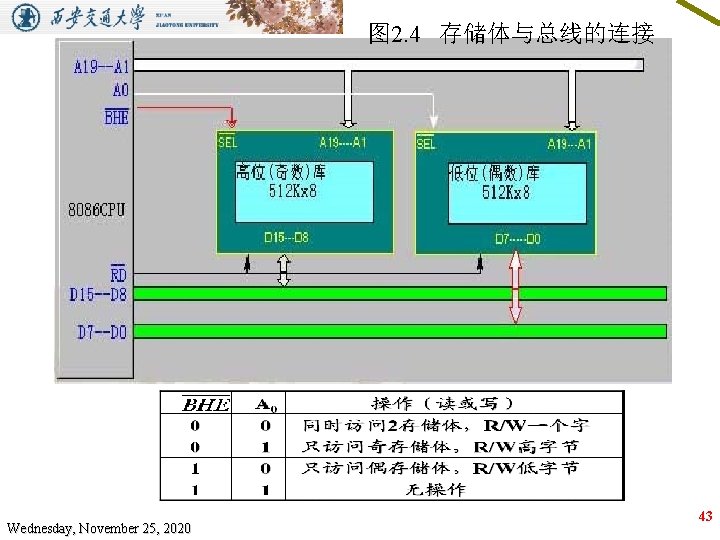

图 2. 4 存储体与总线的连接 Wednesday, November 25, 2020 43

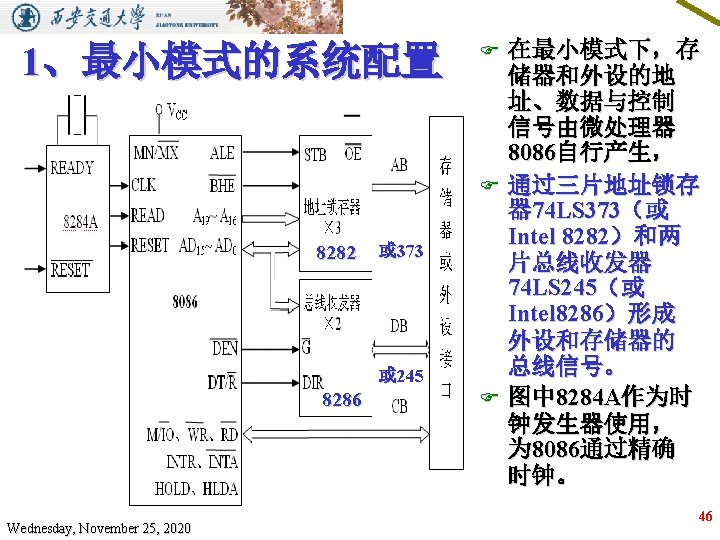

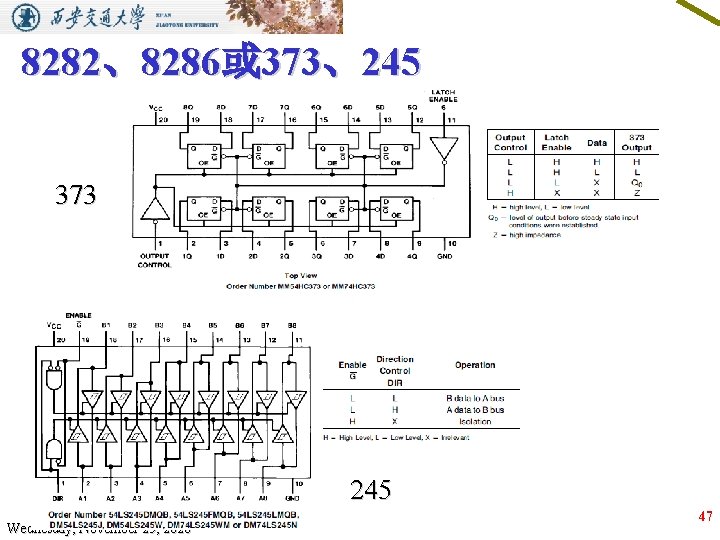

8282、8286或 373、245 373 245 Wednesday, November 25, 2020 47

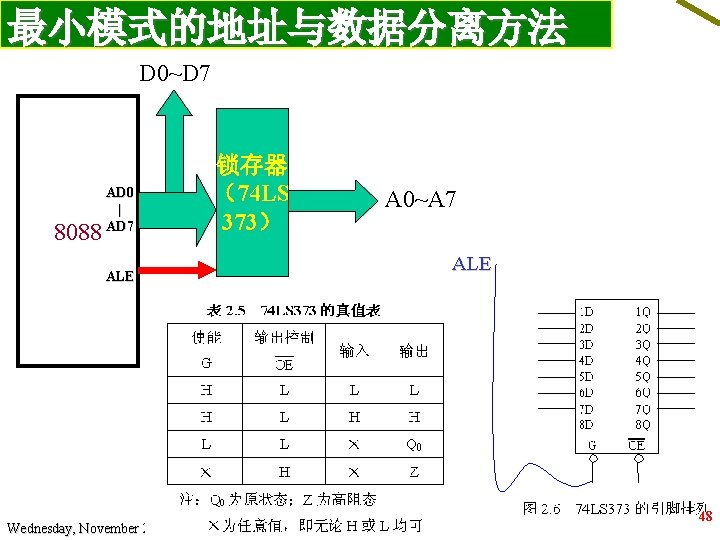

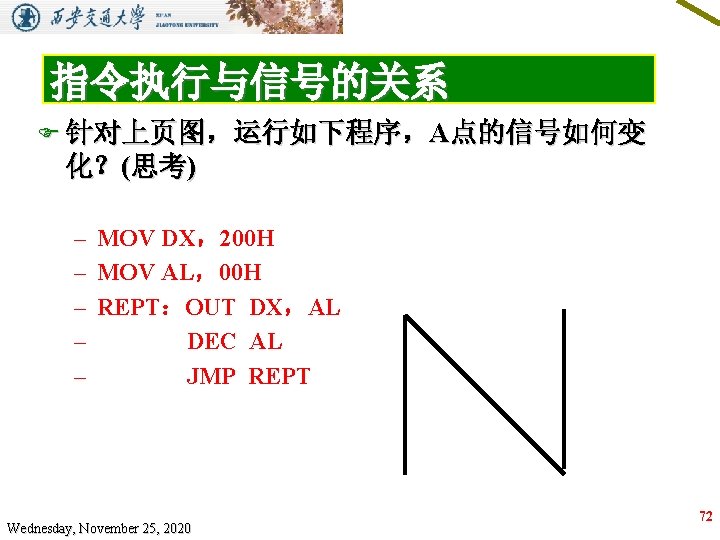

最小模式的地址与数据分离方法 D 0~D 7 8088 AD 0 | AD 7 ALE Wednesday, November 25, 2020 锁存器 (74 LS 373) A 0~A 7 ALE 48

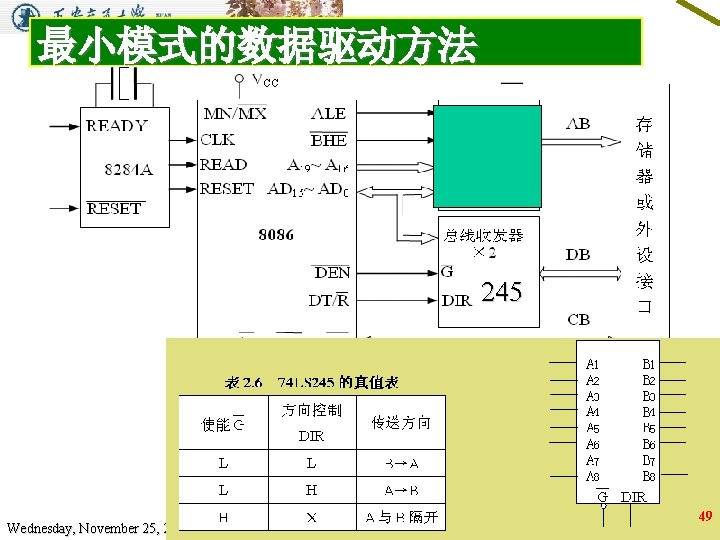

最小模式的数据驱动方法 245 Wednesday, November 25, 2020 49

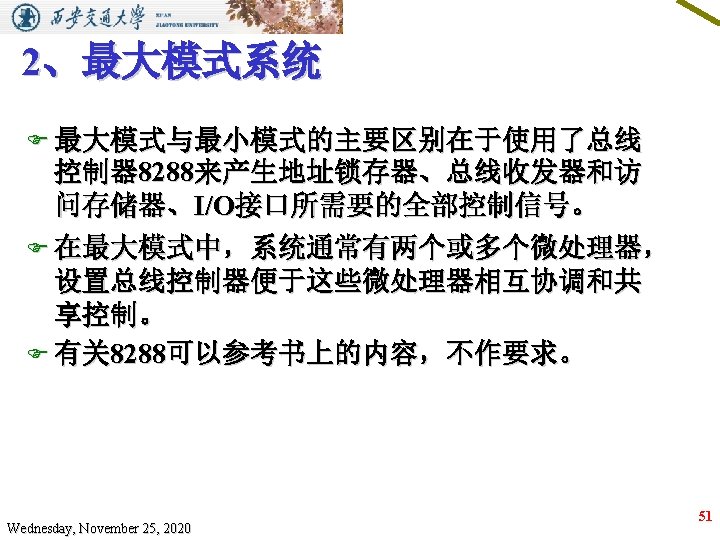

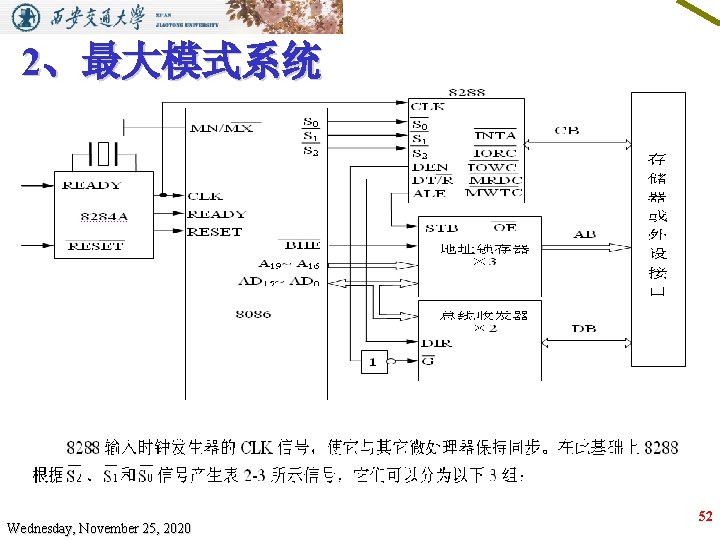

2、最大模式系统 Wednesday, November 25, 2020 52

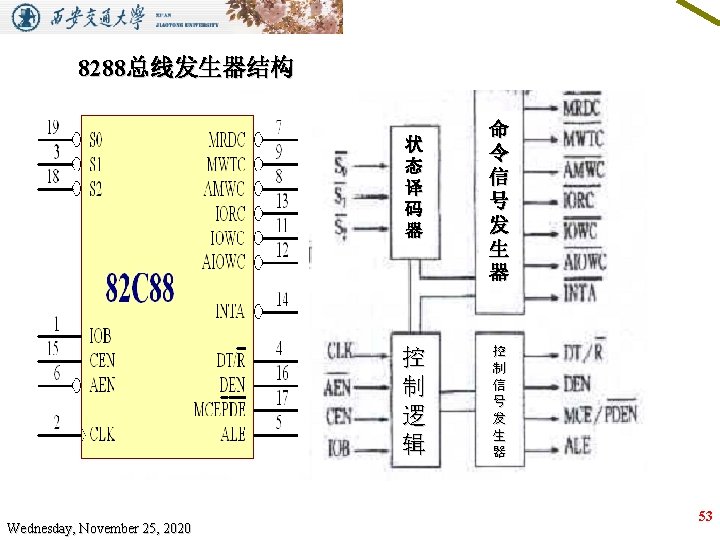

8288总线发生器的输出 S 2 S 1 S 0 8088输出 8288输出 000 INTA INTA 001 IOR IORC 010 IOW IOWC、AIOWC 011 HALT - 100 取指令操作码 MRDC 101 MEMR MRDC 110 MEMW MWTC、AMWTC 111 NOP - Wednesday, November 25, 2020 54

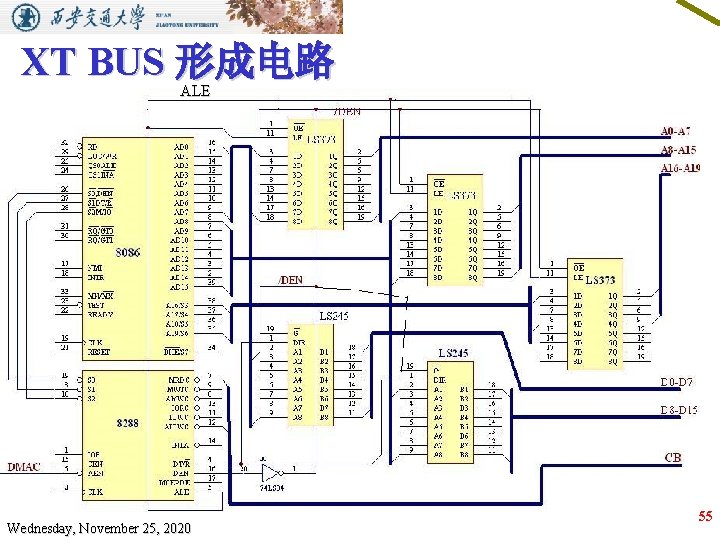

XT BUS 形成电路 ALE Wednesday, November 25, 2020 55

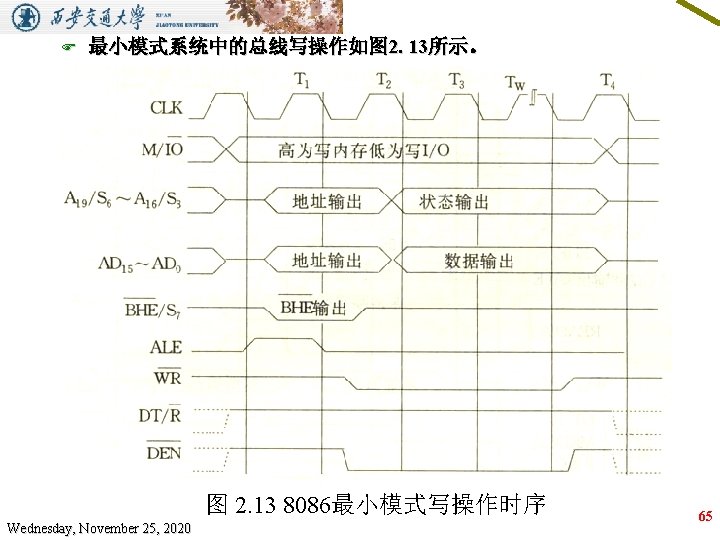

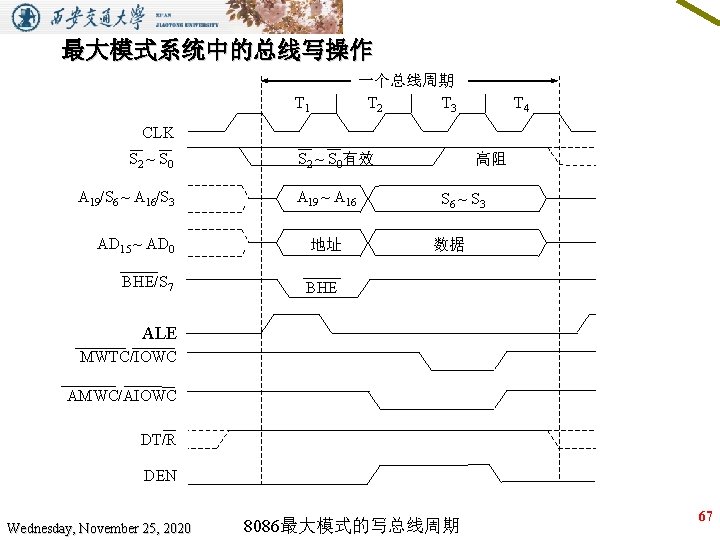

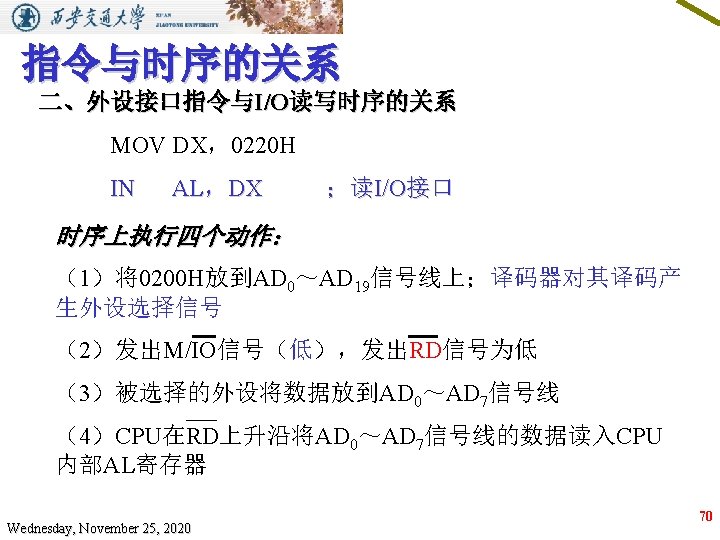

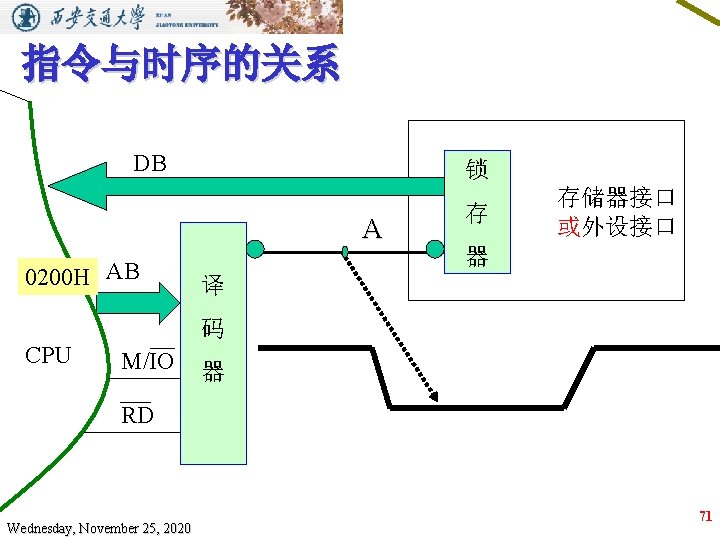

最大模式系统中的总线写操作 T 1 一个总线周期 T 2 T 3 T 4 CLK S 2 ~ S 0 A 19/S 6 ~ A 16/S 3 S 2 ~ S 0有效 A 19 ~ A 16 AD 15 ~ AD 0 地址 BHE/S 7 BHE 高阻 S 6 ~ S 3 数据 ALE MWTC/IOWC AMWC/AIOWC DT/R DEN Wednesday, November 25, 2020 8086最大模式的写总线周期 67

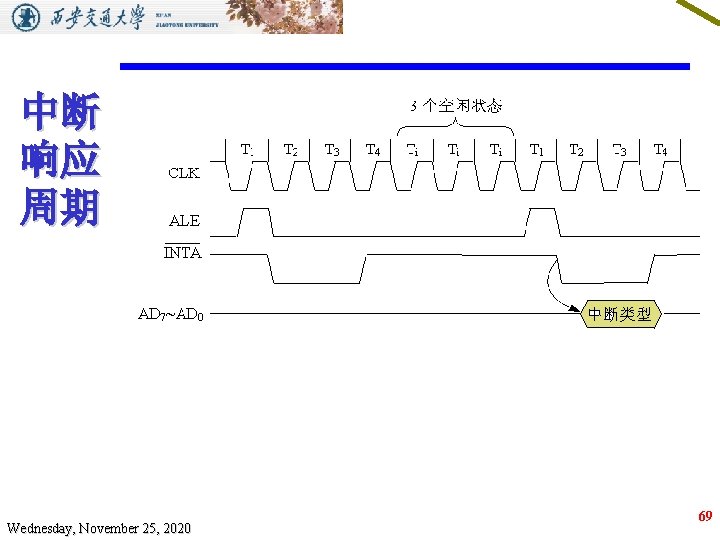

中断 响应 周期 Wednesday, November 25, 2020 69

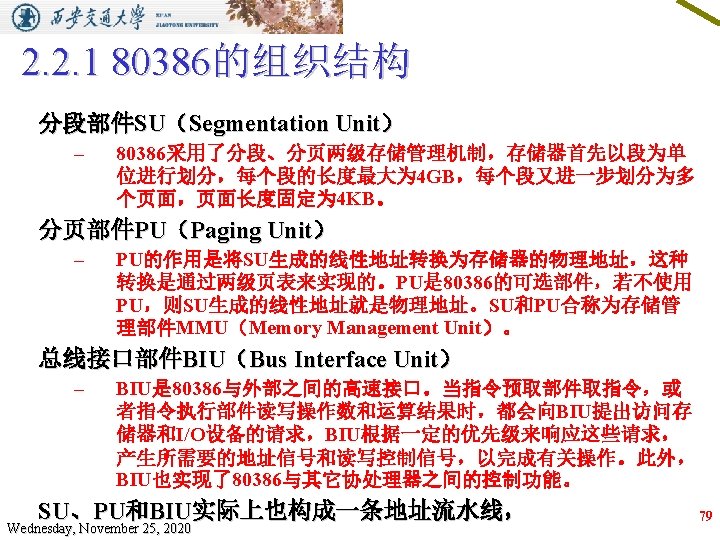

2. 2 80386微处理器 西安交通大学计算机系 桂小林 2011年 2月26日 Wednesday, November 25, 2020 74

目录 F 2. 2 80386微处理器 F 2. 3 双核微处理器 F 2. 4 80 x 8寻址方式 F 2. 5 80 x 86的指令系统 F 2. 6单片计算机 Wednesday, November 25, 2020 75

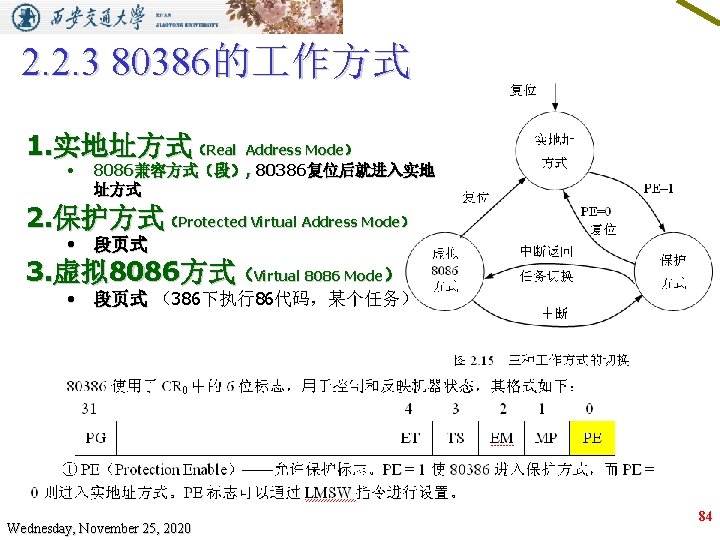

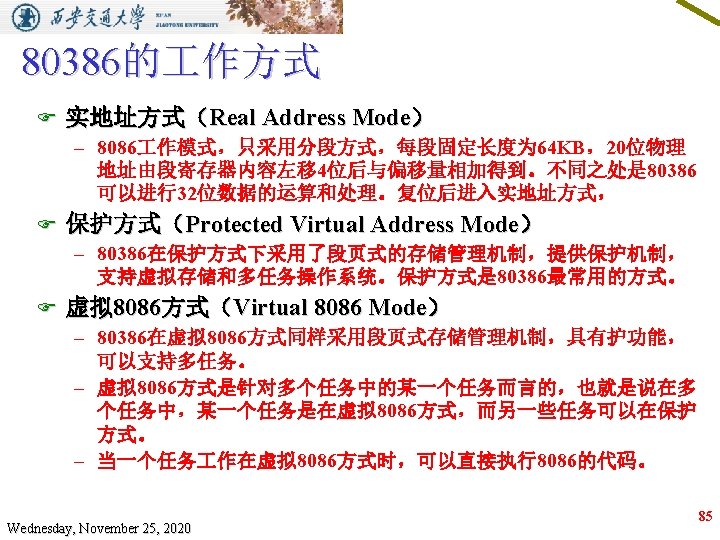

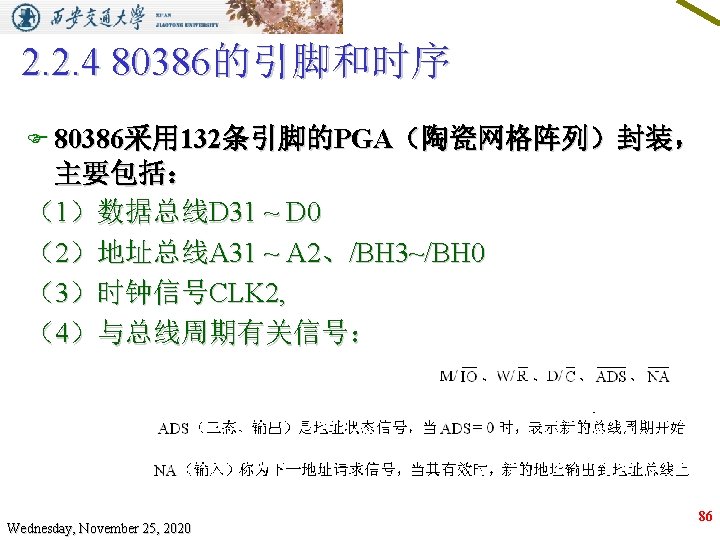

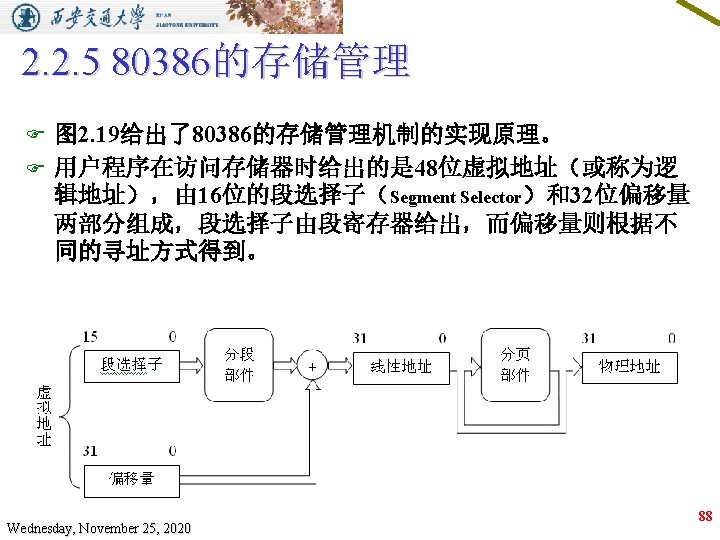

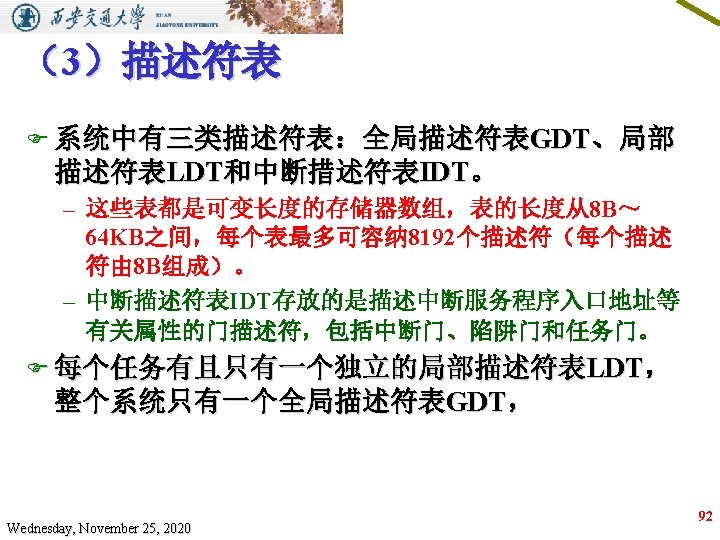

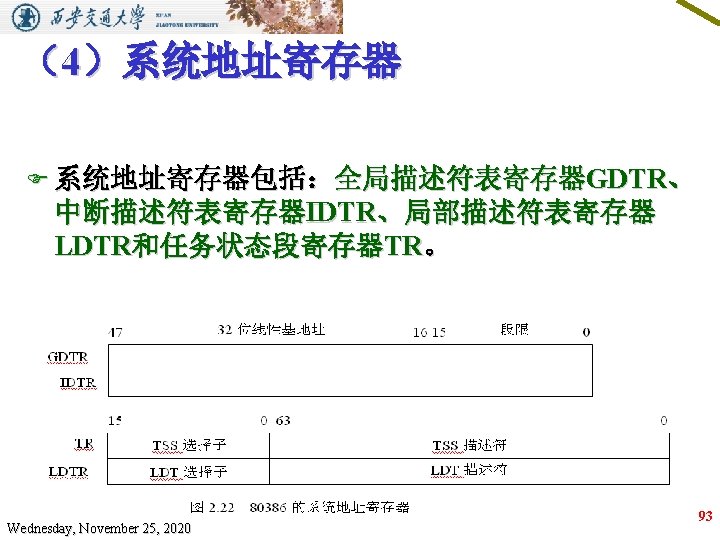

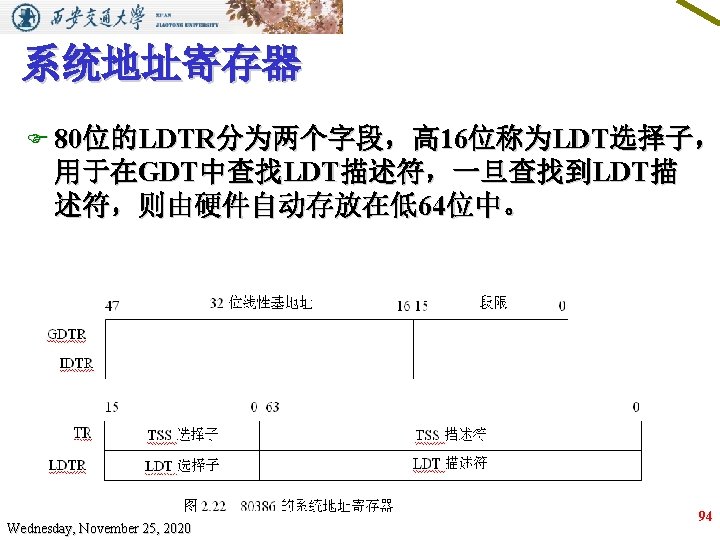

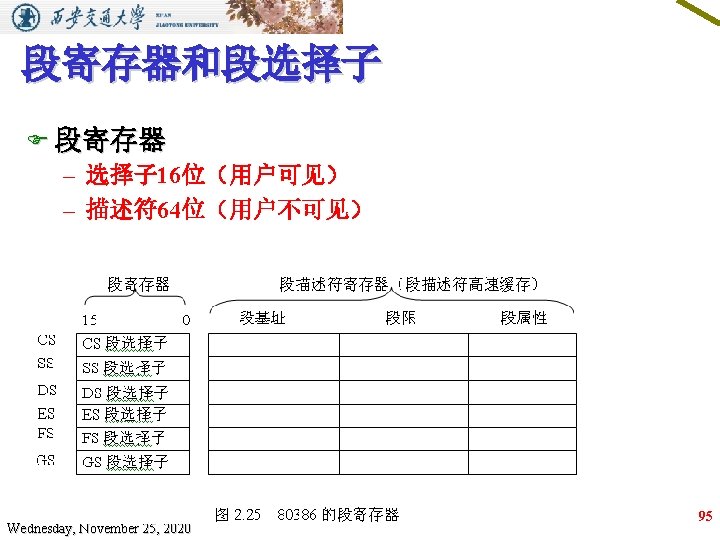

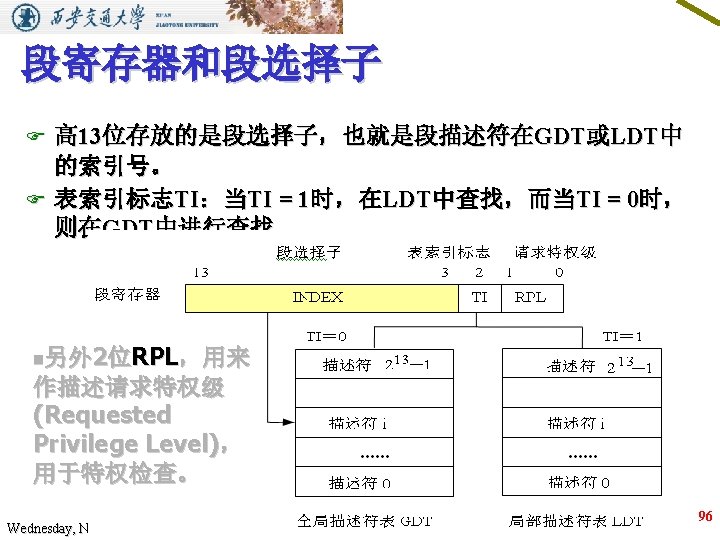

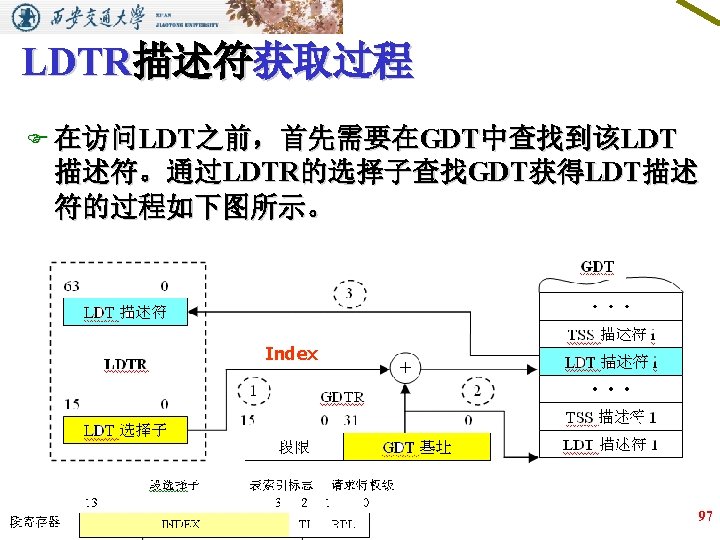

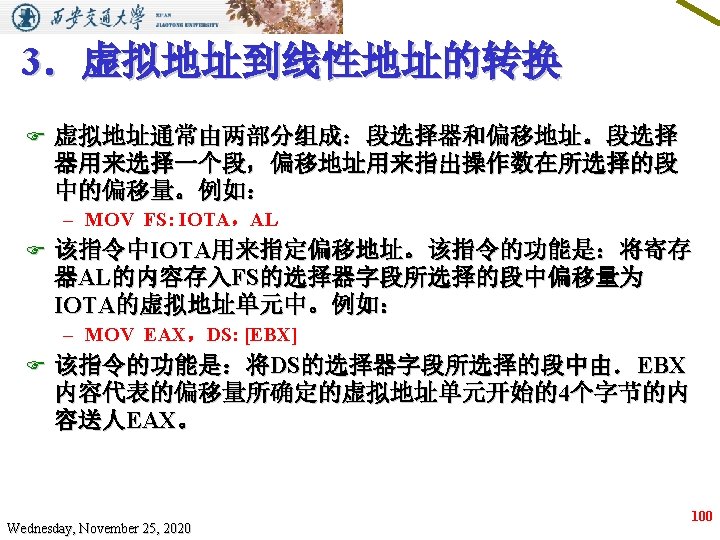

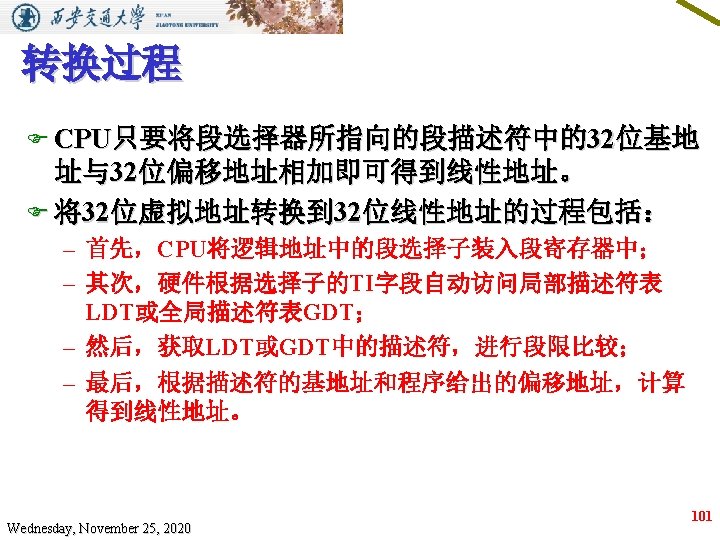

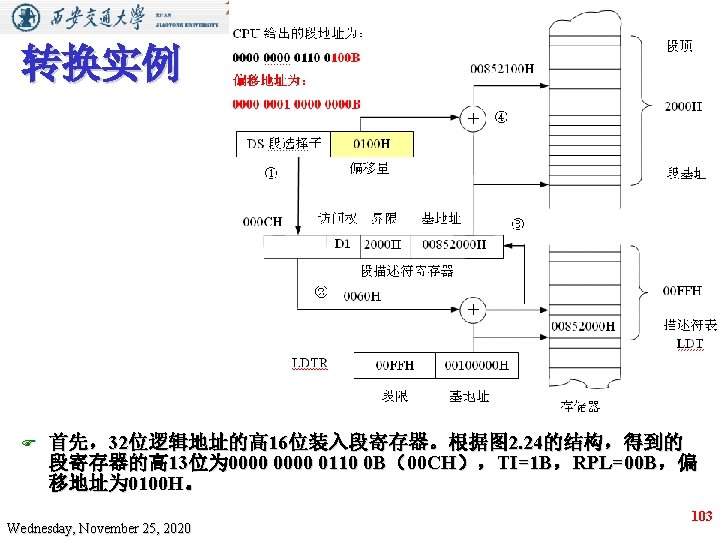

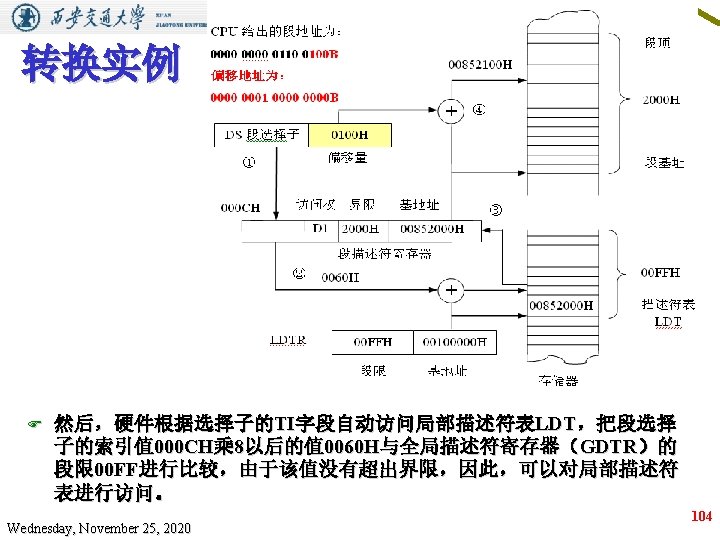

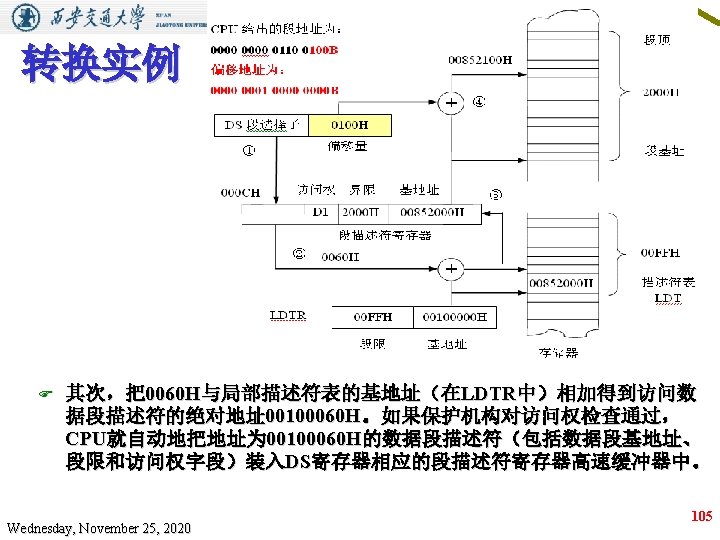

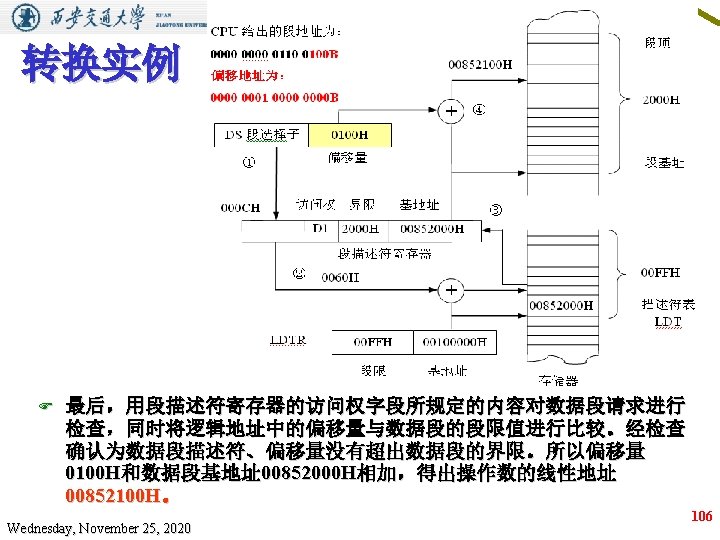

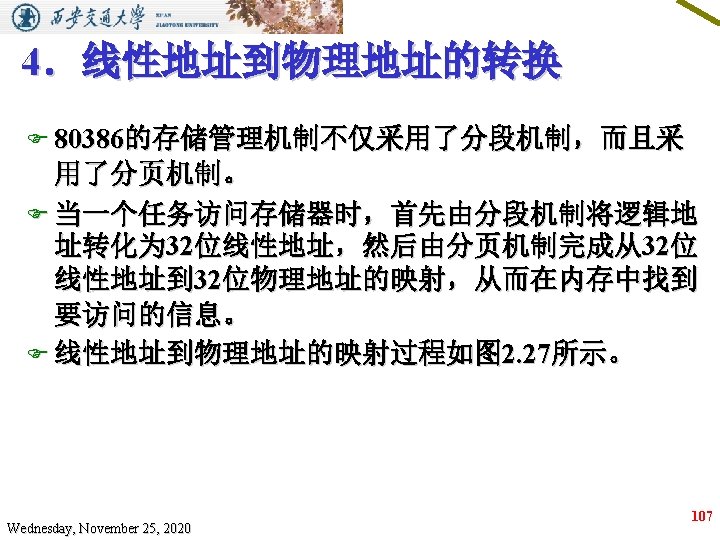

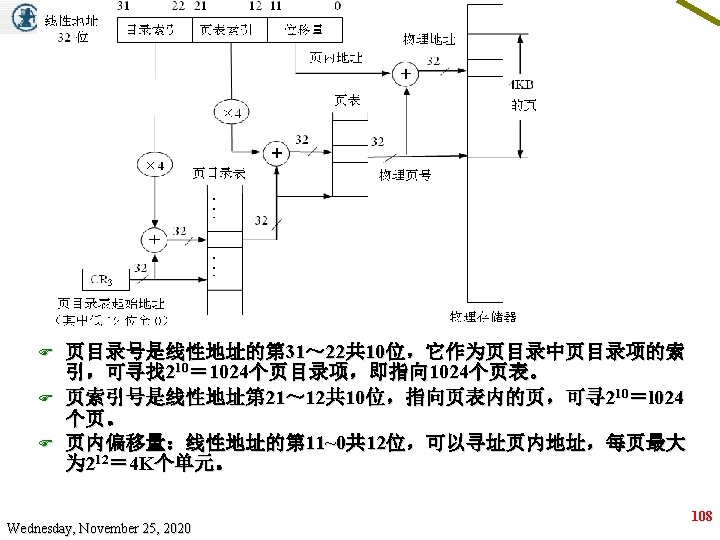

2. 2. 3 80386的 作方式 1. 实地址方式(Real Address Mode) • 8086兼容方式(段), 80386复位后就进入实地 址方式 2. 保护方式(Protected Virtual Address Mode) • 段页式 3. 虚拟 8086方式(Virtual 8086 Mode) • 段页式 (386下执行86代码,某个任务) Wednesday, November 25, 2020 84

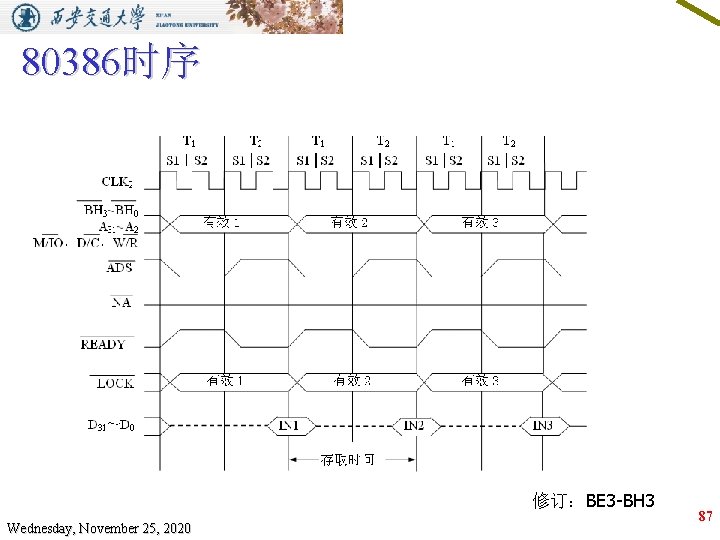

80386时序 修订:BE 3 -BH 3 Wednesday, November 25, 2020 87

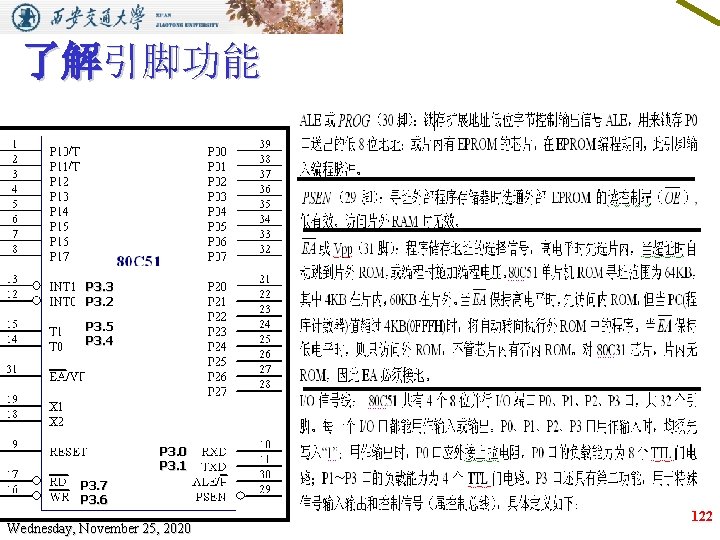

了解引脚功能 P 3. 3 P 3. 2 P 3. 5 P 3. 4 P 3. 0 P 3. 1 P 3. 7 P 3. 6 Wednesday, November 25, 2020 122

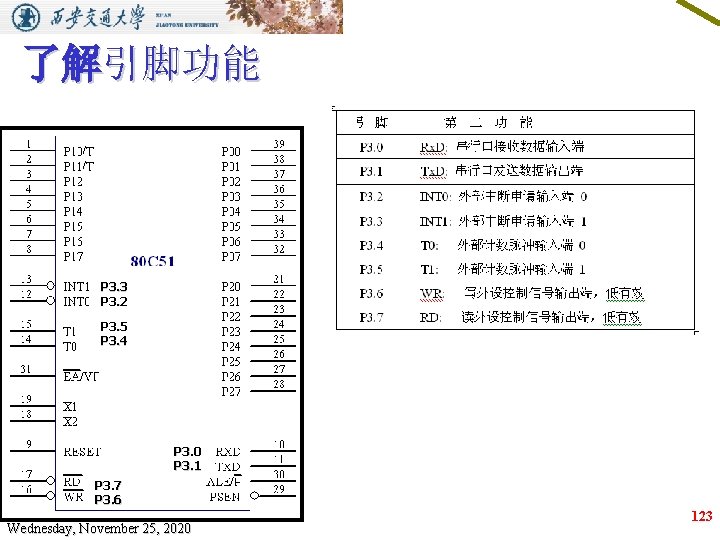

了解引脚功能 P 3. 3 P 3. 2 P 3. 5 P 3. 4 P 3. 0 P 3. 1 P 3. 7 P 3. 6 Wednesday, November 25, 2020 123

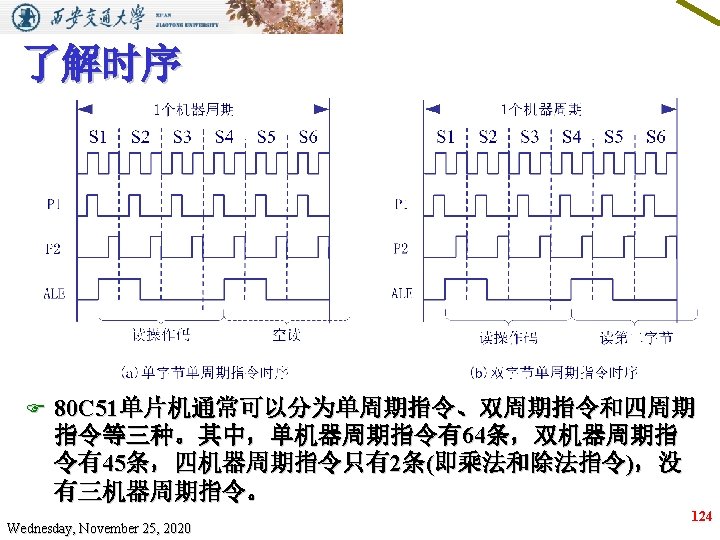

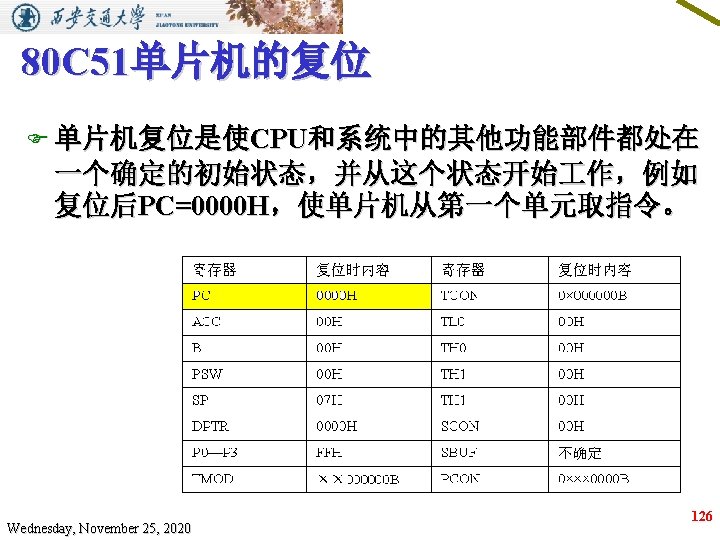

Wednesday, November 25, 2020 125

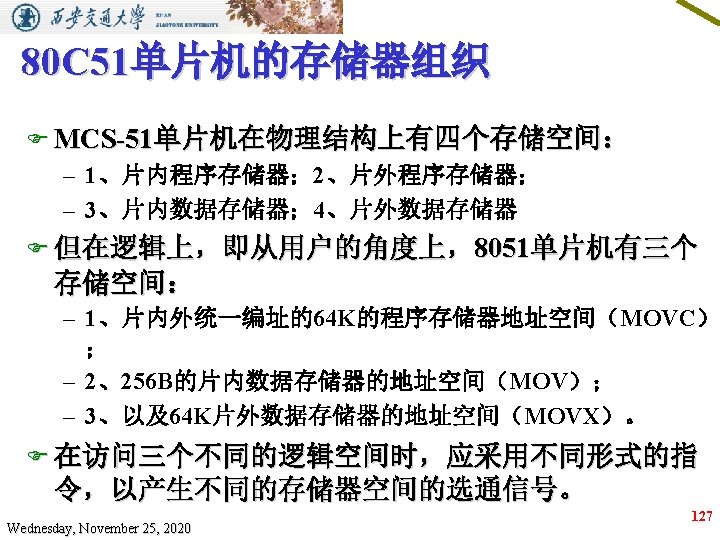

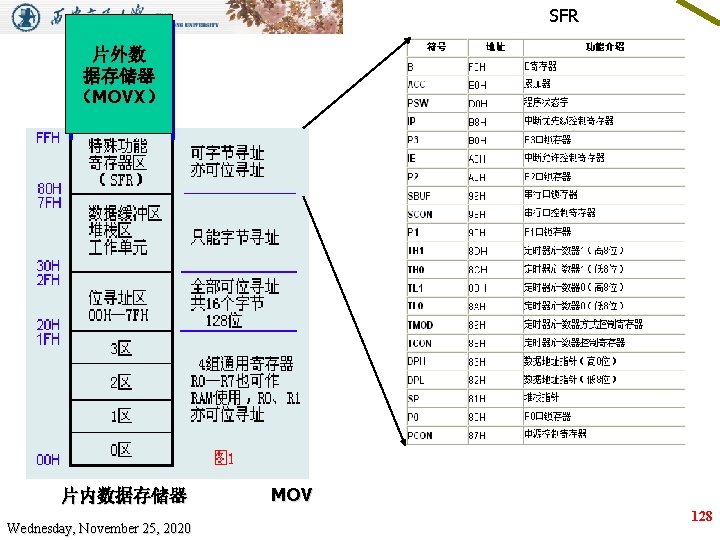

SFR 片外数 MOVX 据存储器 (MOVX) 片内数据存储器 Wednesday, November 25, 2020 MOV 128

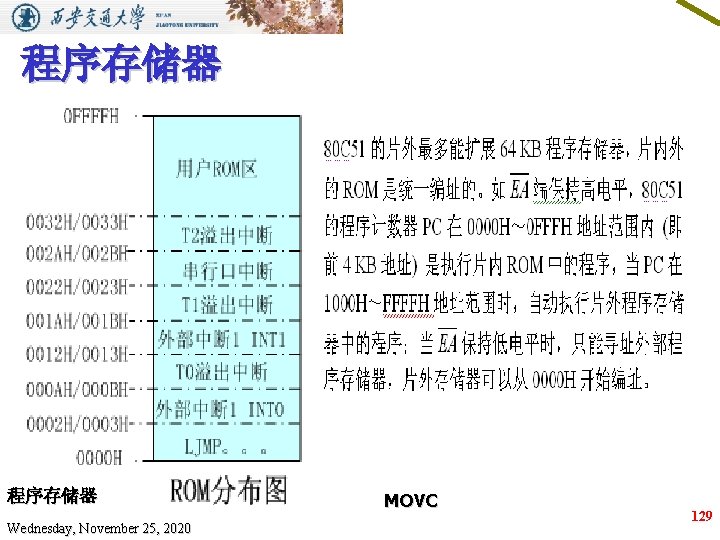

程序存储器 Wednesday, November 25, 2020 MOVC 129

阅读芯片手册 F 80 C 51_www. ic 37. com. pdf Wednesday, November 25, 2020 132

2. 6. 4 AVR单片机 F ATmega 128 AVR采用 64引脚TQFP和64引脚 MLF两 种封装模式, F 作电压为: 2. 7 -5. 5 V(ATmega 128 L)和4. 5 -5. 5 V( ATmega 128)。 F 作频率8 MHz(ATmega 128 L)或 16 MHz(ATmega 128)。 F 内部总线 32位,外部总线支持8位和16位两种模式。 Wednesday, November 25, 2020 133

作业 F P 91 -92 F 13、19、27、40 Wednesday, November 25, 2020 136

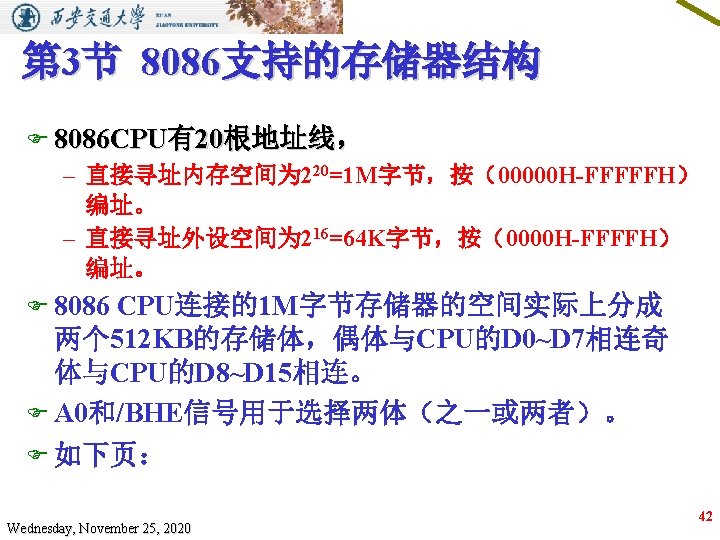

- Slides: 136