WEBENCH Power Designer Power Architect Basics 1 Objectives

WEBENCH® Power Designer & Power Architect Basics 1

Objectives WEBENCH Overview Walkthrough of WEBENCH Power Designer Electrical and Thermal Simulation Build it and Reporting

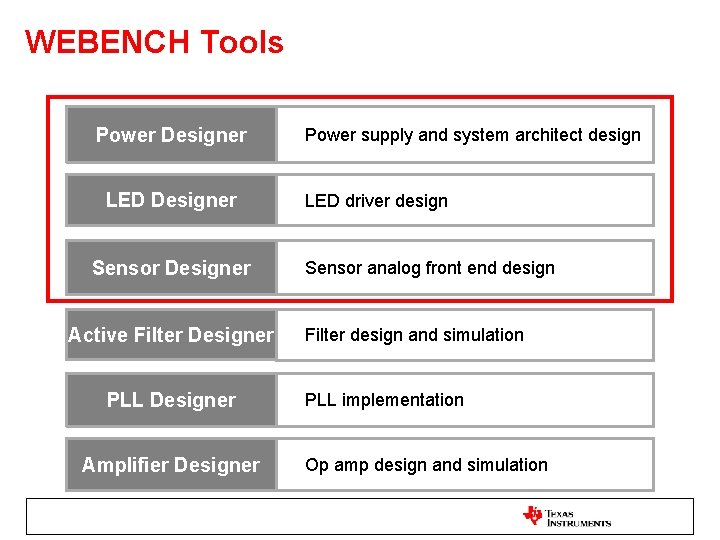

WEBENCH Tools Power Designer LED Designer Sensor Designer Active Filter Designer PLL Designer Amplifier Designer Power supply and system architect design LED driver design Sensor analog front end design Filter design and simulation PLL implementation Op amp design and simulation

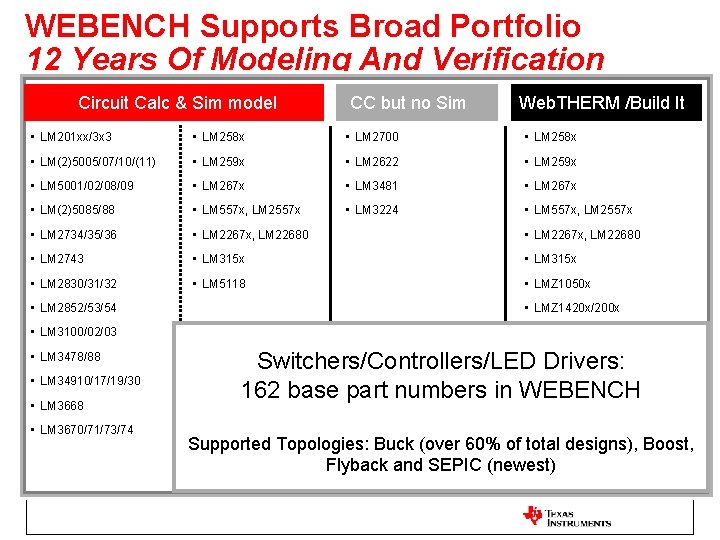

WEBENCH Supports Broad Portfolio 12 Years Of Modeling And Verification Circuit Calc & Sim model CC but no Sim Web. THERM /Build It • LM 201 xx/3 x 3 • LM 258 x • LM 2700 • LM 258 x • LM(2)5005/07/10/(11) • LM 259 x • LM 2622 • LM 259 x • LM 5001/02/08/09 • LM 267 x • LM 3481 • LM 267 x • LM(2)5085/88 • LM 557 x, LM 2557 x • LM 3224 • LM 557 x, LM 2557 x • LM 2734/35/36 • LM 2267 x, LM 22680 • LM 2743 • LM 315 x • LM 2830/31/32 • LM 5118 • LMZ 1050 x • LM 2852/53/54 • LMZ 1420 x/200 x • LM 3100/02/03 • LM 3478/88 • LM 34910/17/19/30 • LM 3668 • LM 3670/71/73/74 Switchers/Controllers/LED Drivers: 162 base part numbers in WEBENCH Supported Topologies: Buck (over 60% of total designs), Boost, Flyback and SEPIC (newest)

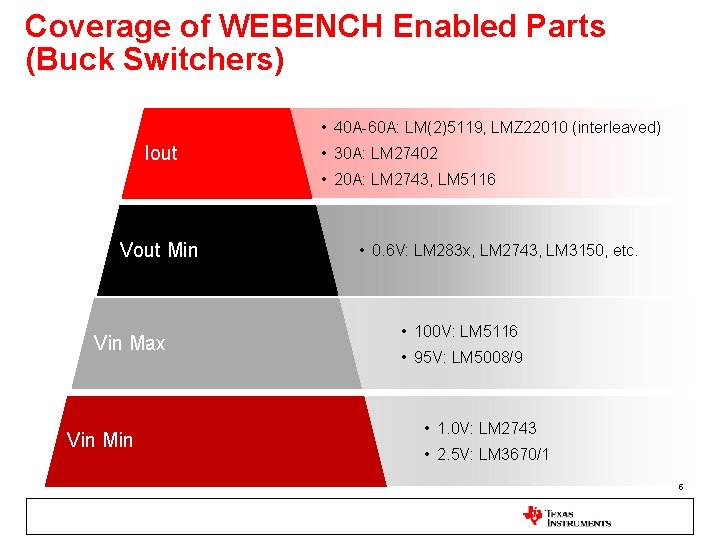

Coverage of WEBENCH Enabled Parts (Buck Switchers) • 40 A-60 A: LM(2)5119, LMZ 22010 (interleaved) Iout • 30 A: LM 27402 • 20 A: LM 2743, LM 5116 Vout Min Vin Max Vin Min • 0. 6 V: LM 283 x, LM 2743, LM 3150, etc. • 100 V: LM 5116 • 95 V: LM 5008/9 • 1. 0 V: LM 2743 • 2. 5 V: LM 3670/1 5

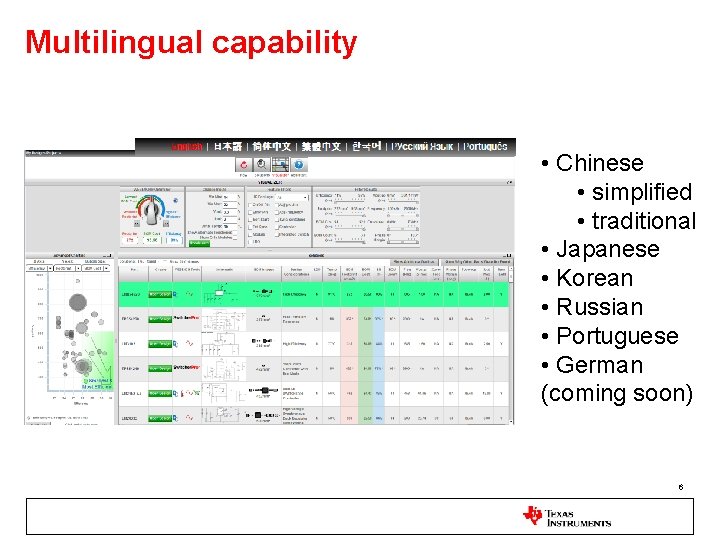

Multilingual capability • Chinese • simplified • traditional • Japanese • Korean • Russian • Portuguese • German (coming soon) 6

Distributor & vendor versions • Avago example • Only contains Avago LEDs And more… • >110 component manufacturers & distributors • >21, 000 components • Price and availability electronically updated hourly 7

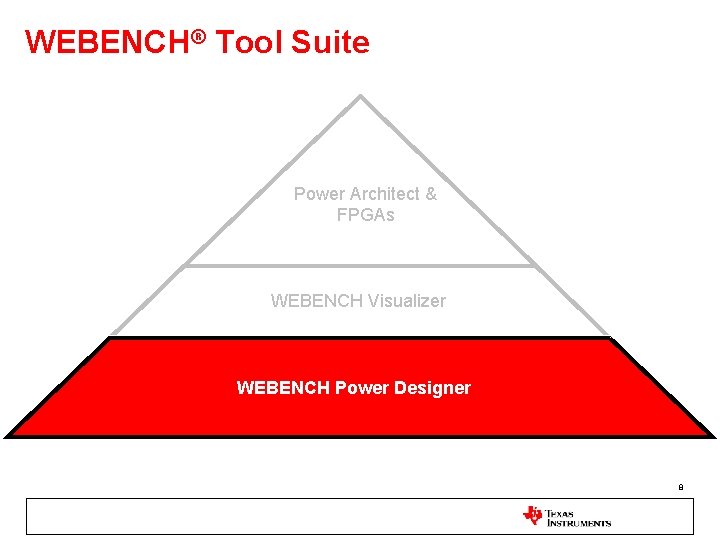

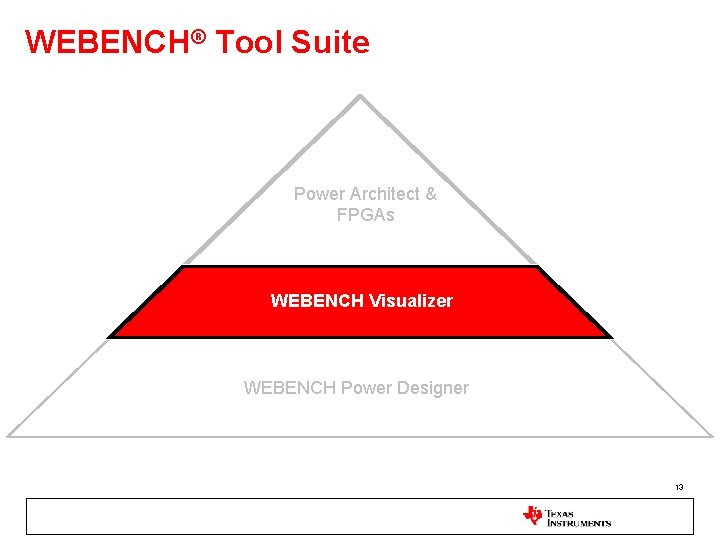

WEBENCH® Tool Suite Altera Power. Play Power Architect & FPGAs FPGA/Power Architect WEBENCH Visualizer WEBENCH Power Designer 8

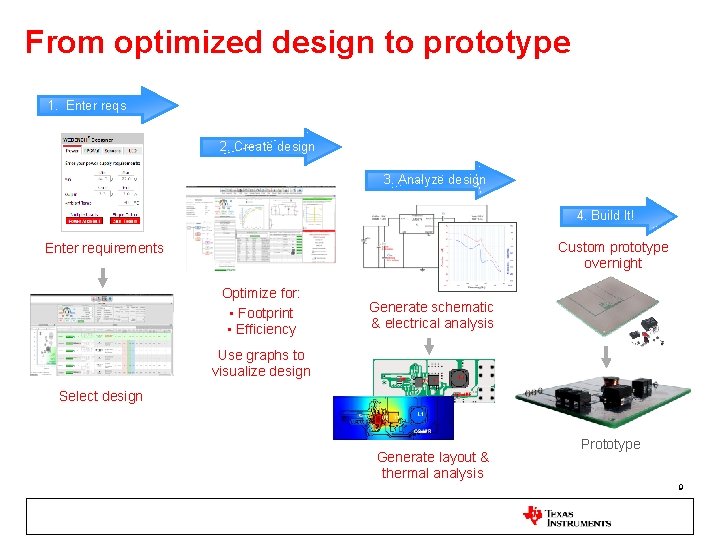

From optimized design to prototype 1. Enter reqs 2. Create design 3. Analyze design 4. Build It! Custom prototype overnight Enter requirements Optimize for: • Footprint • Efficiency Generate schematic & electrical analysis Use graphs to visualize design Select design Generate layout & thermal analysis Prototype 9

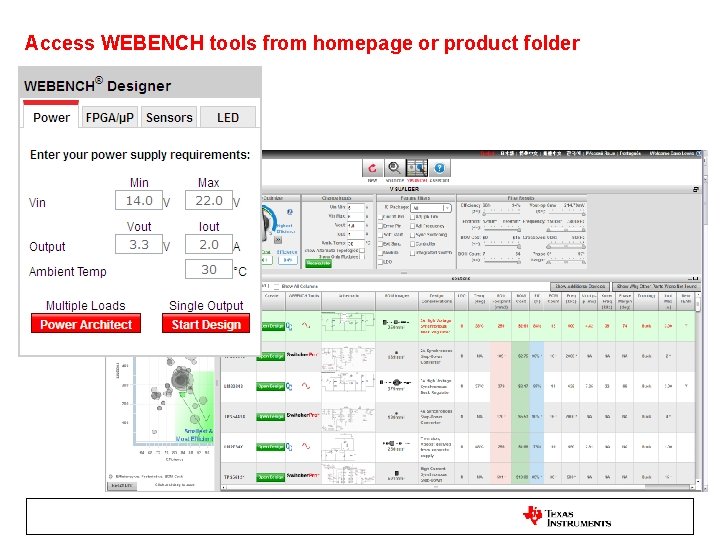

Access WEBENCH tools from homepage or product folder 10

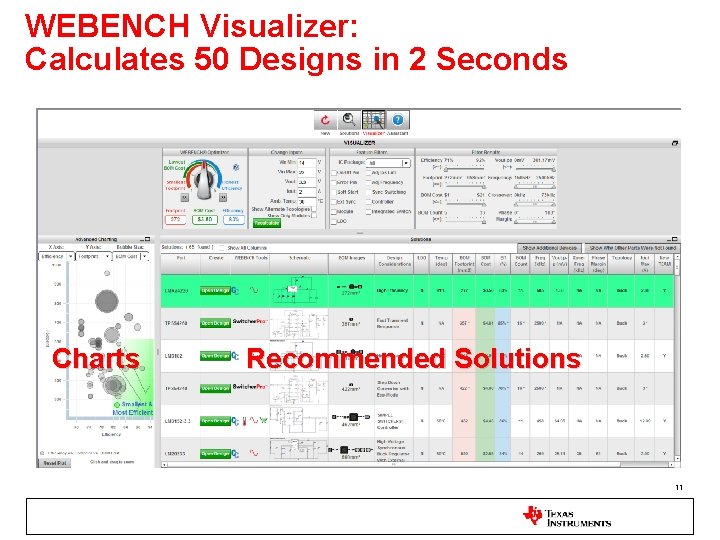

WEBENCH Visualizer: Calculates 50 Designs in 2 Seconds Charts Recommended Solutions 11

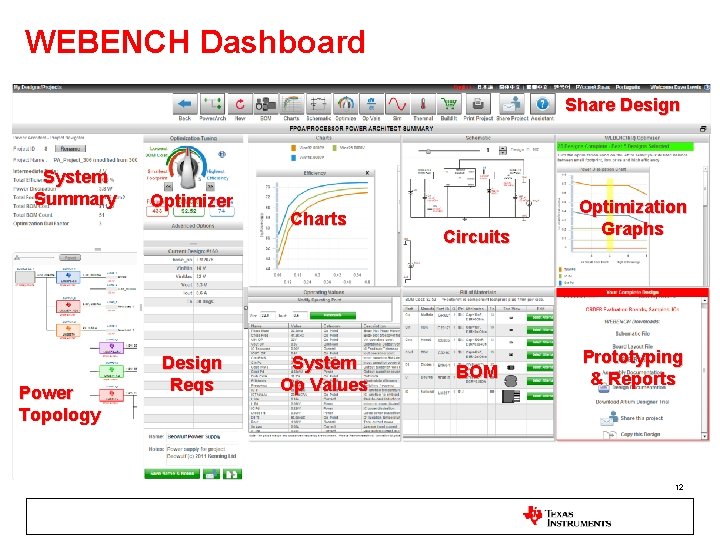

WEBENCH Dashboard Share Design System Summary Power Topology Optimizer Design Reqs Charts System Op Values Circuits Optimization Graphs BOM Prototyping & Reports 12

WEBENCH® Tool Suite Power Architect & FPGAs WEBENCH Visualizer WEBENCH Power Designer 13

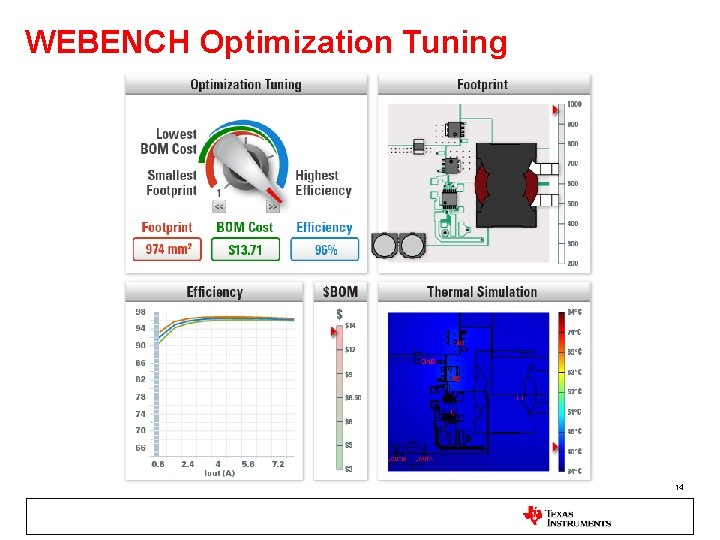

WEBENCH Optimization Tuning 14

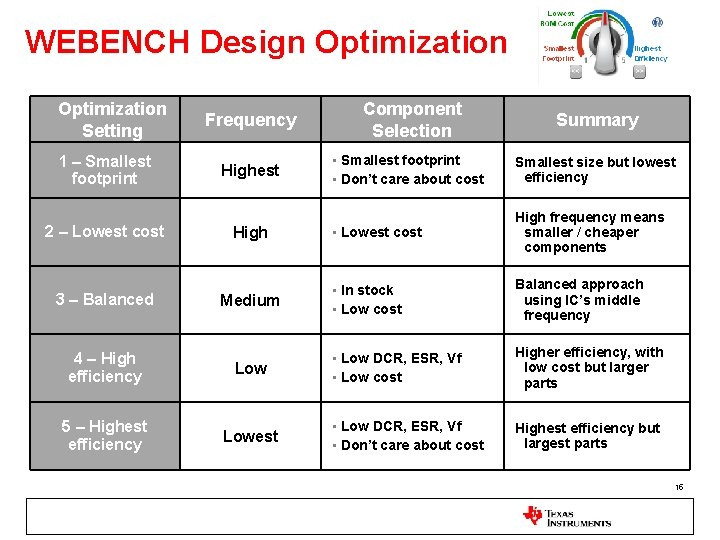

WEBENCH Design Optimization Setting 1 – Smallest footprint 2 – Lowest cost 3 – Balanced Frequency Highest High Medium 4 – High efficiency Low 5 – Highest efficiency Lowest Component Selection Summary • Smallest footprint • Don’t care about cost Smallest size but lowest efficiency • Lowest cost High frequency means smaller / cheaper components • In stock • Low cost Balanced approach using IC’s middle frequency • Low DCR, ESR, Vf • Low cost Higher efficiency, with low cost but larger parts • Low DCR, ESR, Vf • Don’t care about cost Highest efficiency but largest parts 15

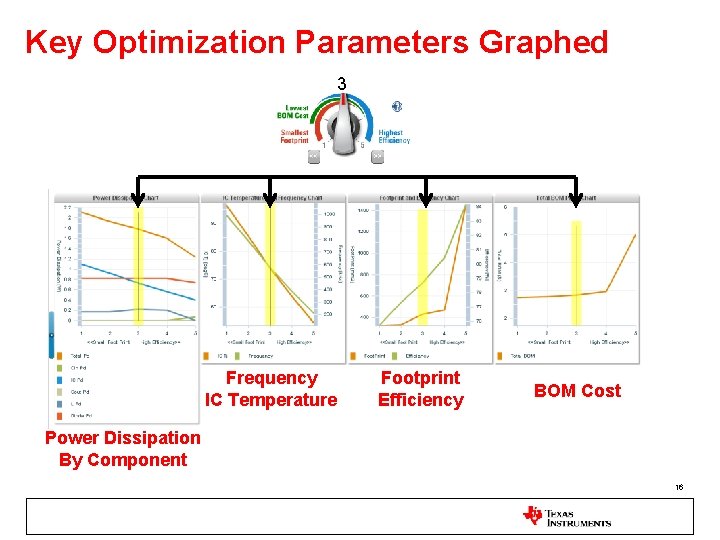

Key Optimization Parameters Graphed 3 Frequency IC Temperature Footprint Efficiency BOM Cost Power Dissipation By Component 16

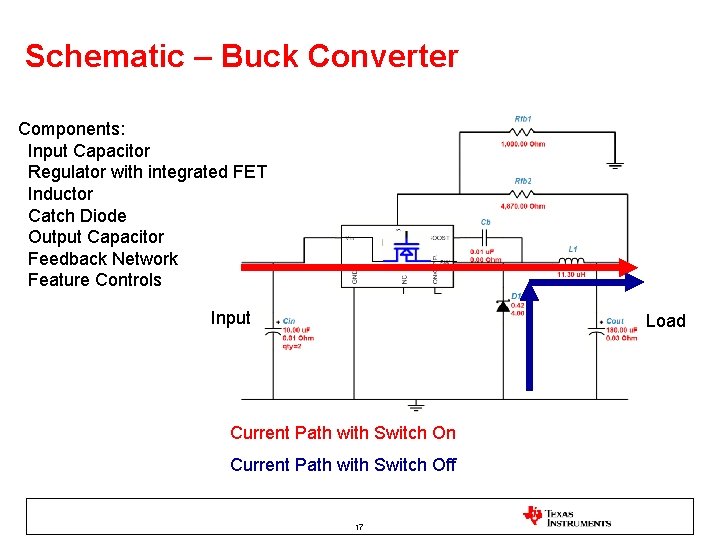

Schematic – Buck Converter Components: Input Capacitor Regulator with integrated FET Inductor Catch Diode Output Capacitor Feedback Network Feature Controls Input Load Current Path with Switch On Current Path with Switch Off 17

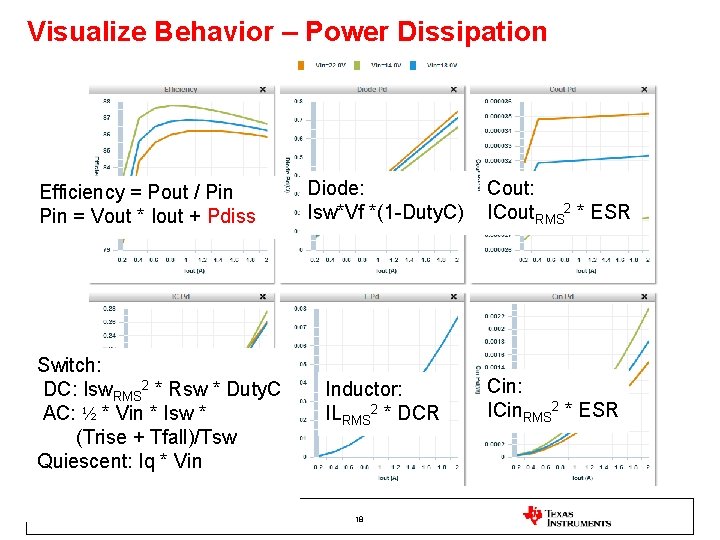

Visualize Behavior – Power Dissipation Efficiency = Pout / Pin = Vout * Iout + Pdiss Switch: DC: Isw. RMS 2 * Rsw * Duty. C AC: ½ * Vin * Isw * (Trise + Tfall)/Tsw Quiescent: Iq * Vin Diode: Isw*Vf *(1 -Duty. C) Inductor: ILRMS 2 * DCR 18 Cout: ICout. RMS 2 * ESR Cin: ICin. RMS 2 * ESR

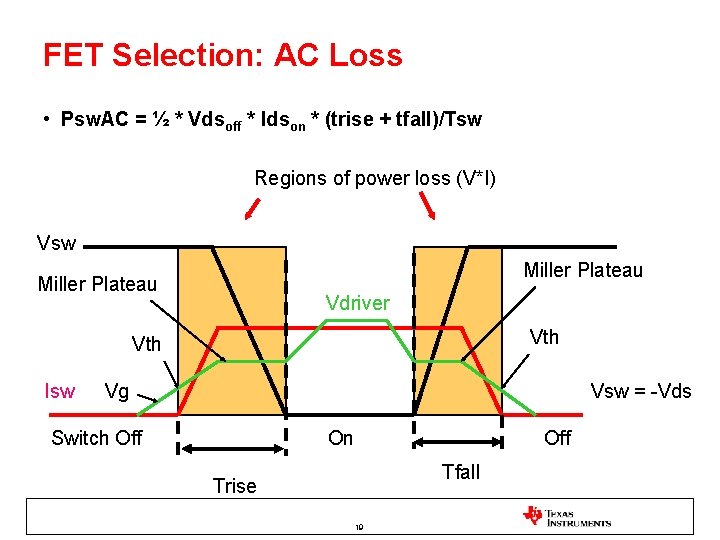

FET Selection: AC Loss • Psw. AC = ½ * Vdsoff * Idson * (trise + tfall)/Tsw Regions of power loss (V*I) Vsw Miller Plateau Vdriver Vth Isw Vg Vsw = -Vds Switch Off On Off Tfall Trise 19

FET Selection: AC Loss • Psw. AC = ½ * Vdsoff * Idson * (trise + tfall)/Tsw High Freq = High Loss Low Freq = Low Loss Regions of power loss (V*I) Vsw Miller Plateau Vdriver Vth Isw Vg Vsw = -Vds Switch Off On Off Trise Tfall 20

How To Reduce FET Power Loss • Choose a FET with low Rds. On • Choose a FET with low capacitance • Lower the switching frequency BUT • Lowering frequency affects the inductor selection • We want to keep the inductor ripple current constant – Because this changes the peak switch current and the Vout ripple 21

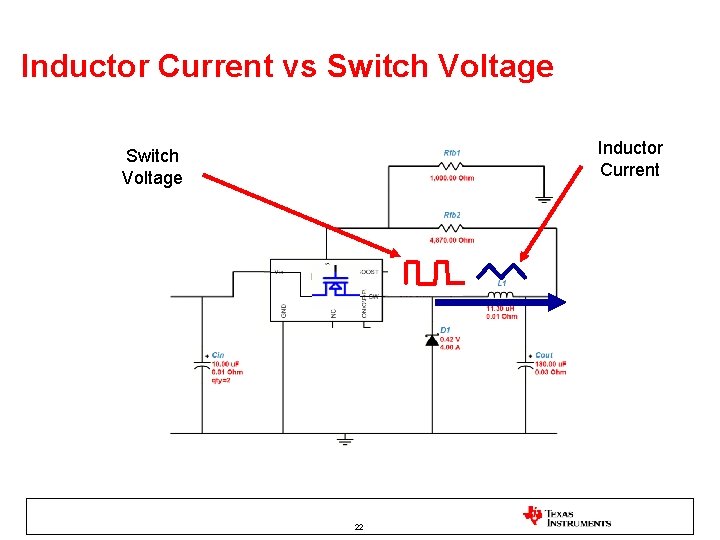

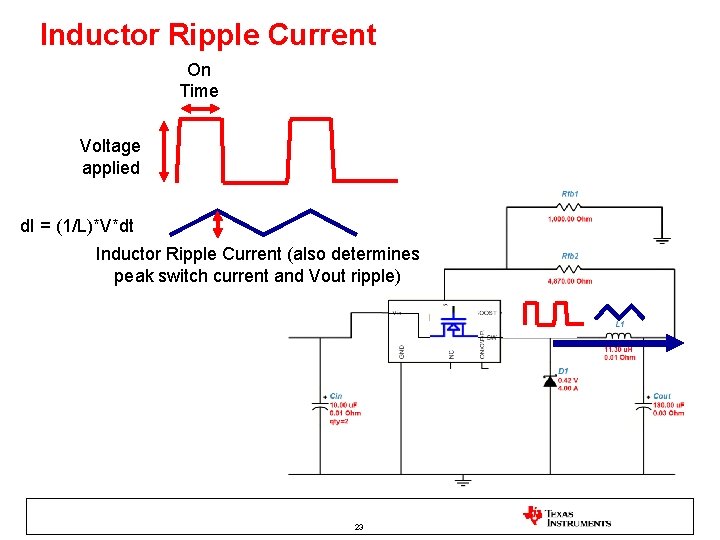

Inductor Current vs Switch Voltage Inductor Current Switch Voltage 22

Inductor Ripple Current On Time Voltage applied d. I = (1/L)*V*dt Inductor Ripple Current (also determines peak switch current and Vout ripple) 23

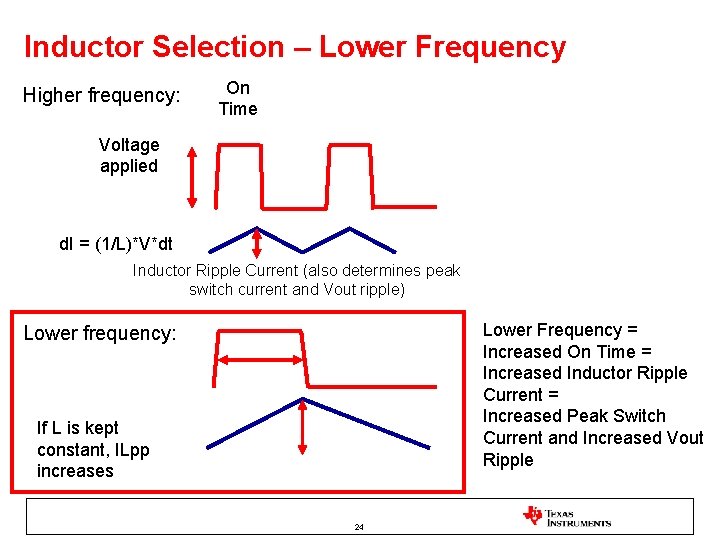

Inductor Selection – Lower Frequency Higher frequency: On Time Voltage applied d. I = (1/L)*V*dt Inductor Ripple Current (also determines peak switch current and Vout ripple) Lower Frequency = Increased On Time = Increased Inductor Ripple Current = Increased Peak Switch Current and Increased Vout Ripple Lower frequency: If L is kept constant, ILpp increases 24

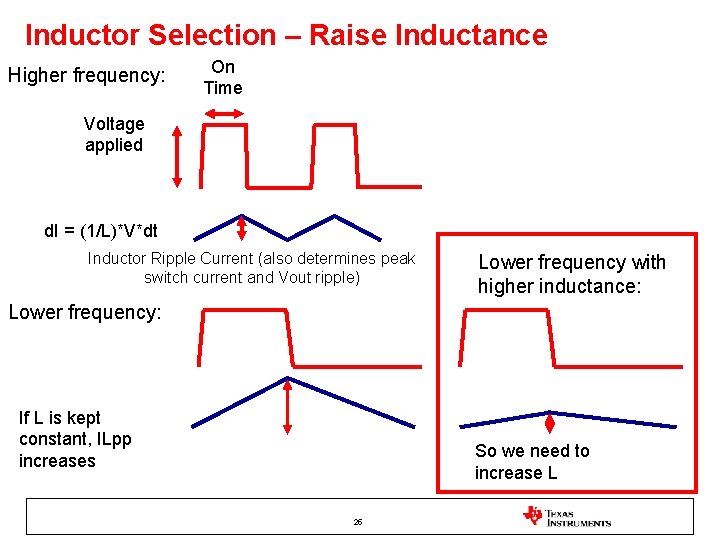

Inductor Selection – Raise Inductance Higher frequency: On Time Voltage applied d. I = (1/L)*V*dt Inductor Ripple Current (also determines peak switch current and Vout ripple) Lower frequency with higher inductance: Lower frequency: If L is kept constant, ILpp increases So we need to increase L 25

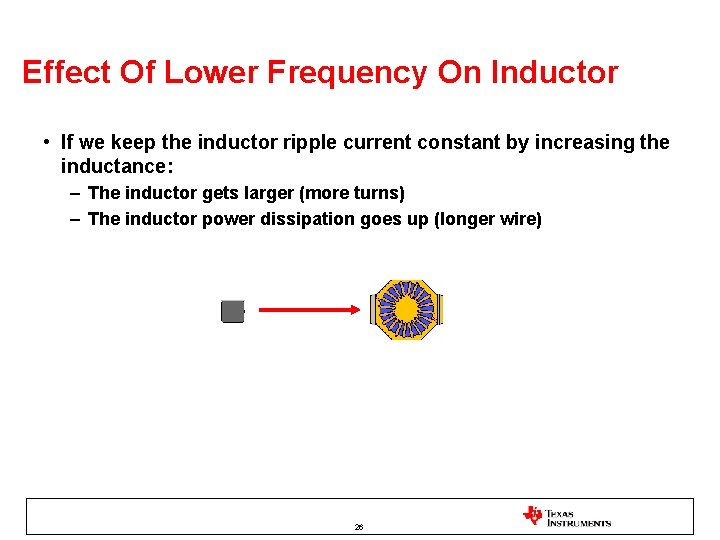

Effect Of Lower Frequency On Inductor • If we keep the inductor ripple current constant by increasing the inductance: – The inductor gets larger (more turns) – The inductor power dissipation goes up (longer wire) 26

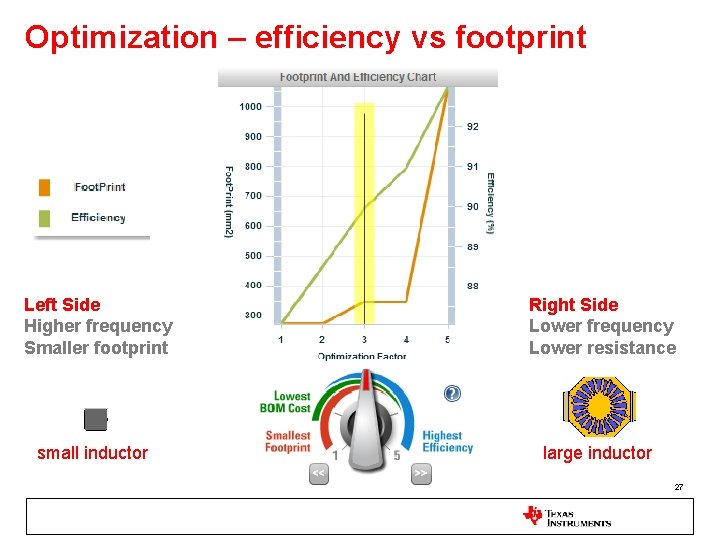

Optimization – efficiency vs footprint Left Side Higher frequency Smaller footprint small inductor Right Side Lower frequency Lower resistance large inductor 27

Optimization Summary • To get high efficiency – Decrease frequency to reduce AC losses – Choose components with low resistance • To get small footprint – Increase frequency to reduce inductor size – Choose components with small footprint • Cost • These parameters are at odds with each other and need to be balanced for a designer’s needs • Tools are available to visualize tradeoffs and make it easier to get to the best solution for your design requirements 28

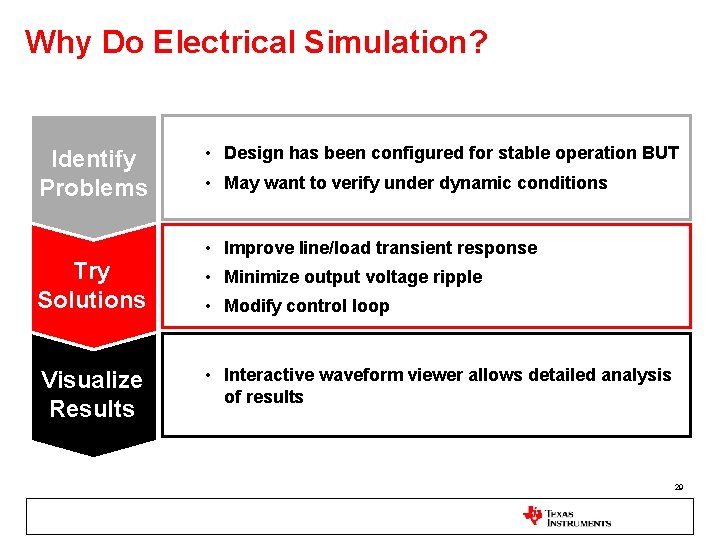

Why Do Electrical Simulation? Identify Problems Try Solutions Visualize Results • Design has been configured for stable operation BUT • May want to verify under dynamic conditions • Improve line/load transient response • Minimize output voltage ripple • Modify control loop • Interactive waveform viewer allows detailed analysis of results 29

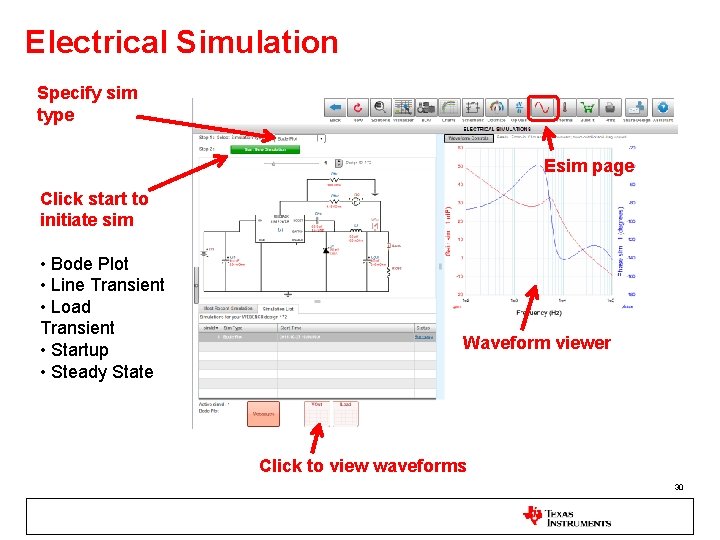

Electrical Simulation Specify sim type Esim page Click start to initiate sim • Bode Plot • Line Transient • Load Transient • Startup • Steady State Waveform viewer Click to view waveforms 30

Waveform Viewer Click and drag down and to the right to zoom in Click and drag up and to the left to zoom out Click on a tile to add a waveform 31

Evaluate Transient Response • LM 22680 – Voltage mode pulse width modulation control scheme (PWM) – Lower part count – SIMPLE SWITCHER® • LM 25576 – Emulated current mode (ECM) – Fast transient response • Will evaluate: – How does ECM compare with PWM – Vin: 14 -22 V, Vout: 3. 3 V, Iout: 2 A 32

Buck Schematics LM 22680 PWM LM 25576 ECM 33

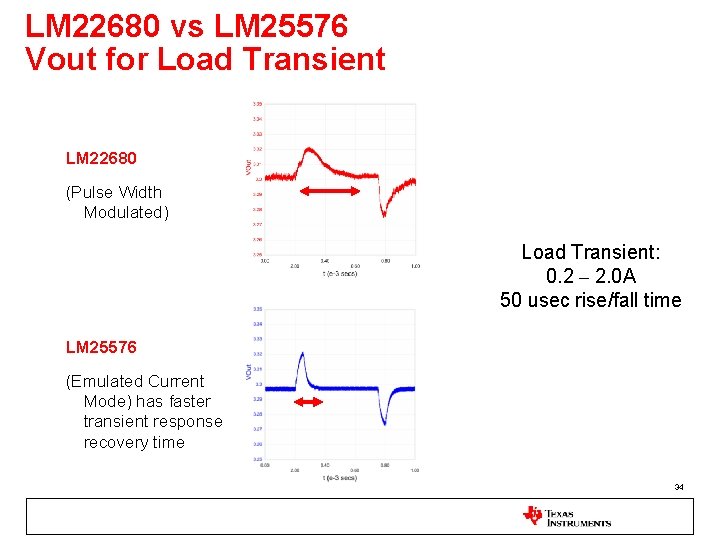

LM 22680 vs LM 25576 Vout for Load Transient LM 22680 (Pulse Width Modulated) Load Transient: 0. 2 – 2. 0 A 50 usec rise/fall time LM 25576 (Emulated Current Mode) has faster transient response recovery time 34

Overlay simulations • Red: LM 22680 (Pulse Width Modulated) • Blue: LM 25576 (Emulated Current Mode) has faster transient response recovery time 35

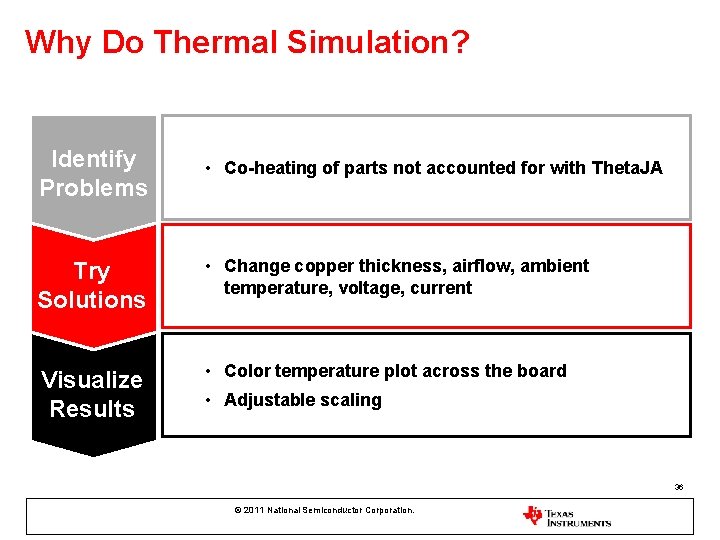

Why Do Thermal Simulation? Identify Problems • Co-heating of parts not accounted for with Theta. JA Try Solutions • Change copper thickness, airflow, ambient temperature, voltage, current Visualize Results • Color temperature plot across the board • Adjustable scaling 36 © 2011 National Semiconductor Corporation.

Why Do Thermal Simulation? • Identify and solve thermal issues – Co-heating of adjacent parts not taken into account with theta. JA • Different ways to solve thermal problems: – Heat sink – Fan – Copper area/thickness • Thermal simulation factors – Model Types: • Physical geometry/materials modeled for regulator • Lumped cuboid models for passive components • Board modeled as a separate part, with traces modeled explicitly – Simulation accuracy • 3 D conduction • Radiation • Convection 37

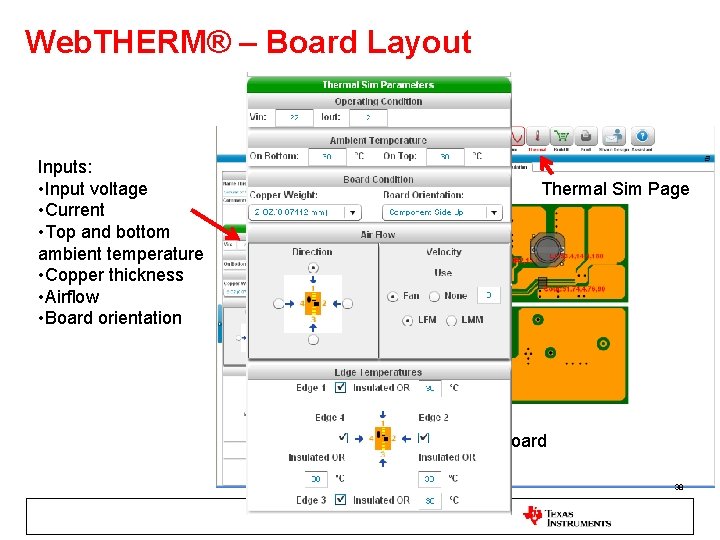

Web. THERM® – Board Layout Inputs: • Input voltage • Current • Top and bottom ambient temperature • Copper thickness • Airflow • Board orientation Thermal Sim Page PC Board 38

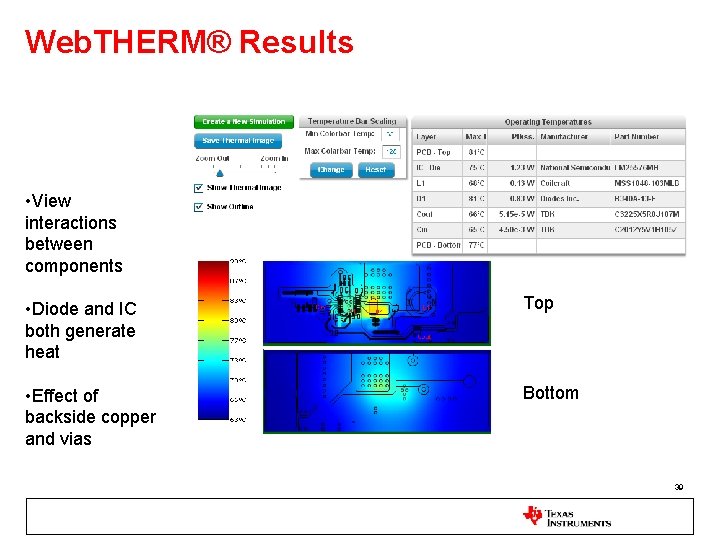

Web. THERM® Results • View interactions between components • Diode and IC both generate heat Top • Effect of backside copper and vias Bottom 39

LM 3150 Controller . 5 oz copper thickness Low side FET is 117 C 4 oz copper thickness Low side FET is 68 C Vin: 14 -22 V Vout: 3. 3 V Iout: 6 A 40

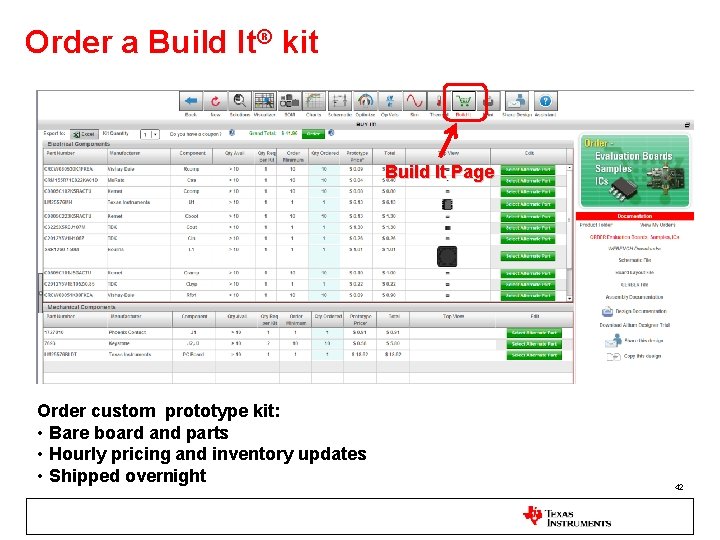

Order a Build It® kit Build It Page Order custom prototype kit: • Bare board and parts • Hourly pricing and inventory updates • Shipped overnight 42

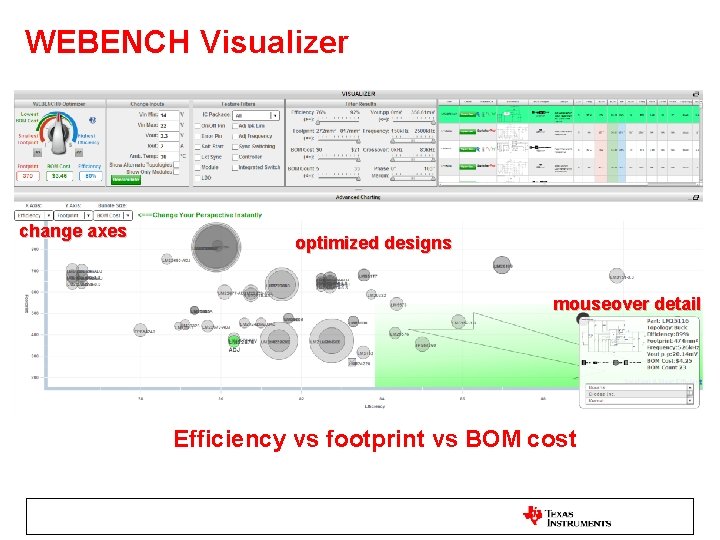

WEBENCH Visualizer change axes optimized designs mouseover detail Efficiency vs footprint vs BOM cost

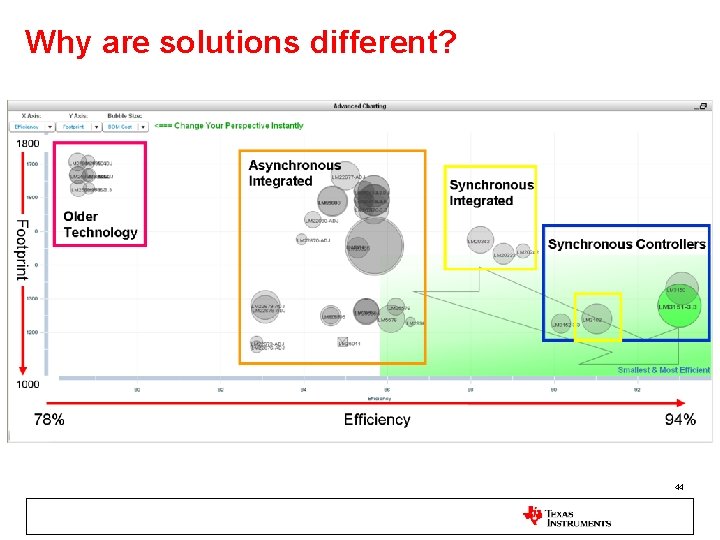

Why are solutions different? 44

WEBENCH® Tool Suite Power Architect WEBENCH Visualizer WEBENCH Power Designer 45

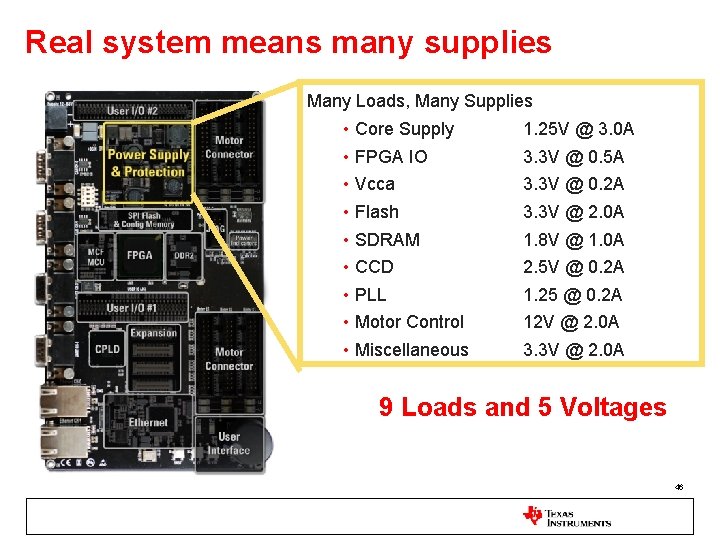

Real system means many supplies Many Loads, Many Supplies • Core Supply • FPGA IO • Vcca • Flash • SDRAM • CCD • PLL • Motor Control • Miscellaneous 1. 25 V @ 3. 0 A 3. 3 V @ 0. 5 A 3. 3 V @ 0. 2 A 3. 3 V @ 2. 0 A 1. 8 V @ 1. 0 A 2. 5 V @ 0. 2 A 1. 25 @ 0. 2 A 12 V @ 2. 0 A 3. 3 V @ 2. 0 A 9 Loads and 5 Voltages 46

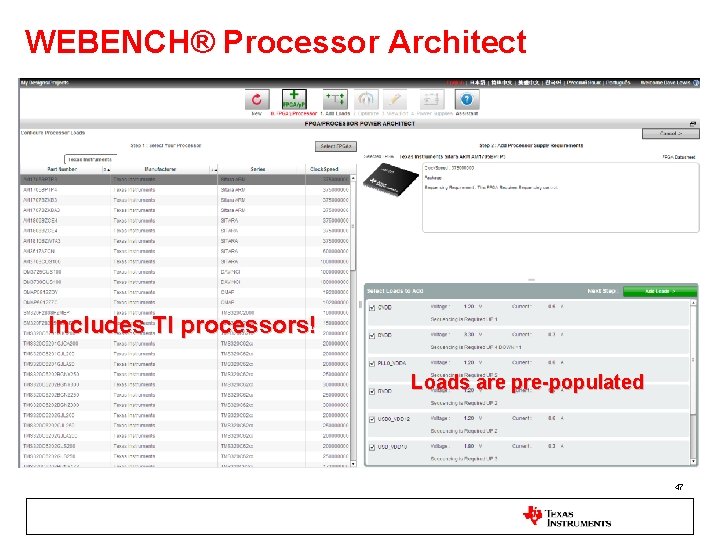

WEBENCH® Processor Architect Includes TI processors! Loads are pre-populated 47

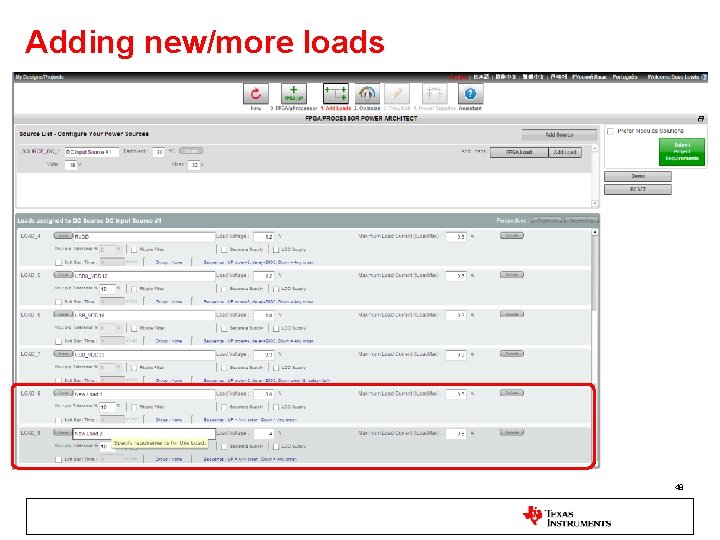

Adding new/more loads 48

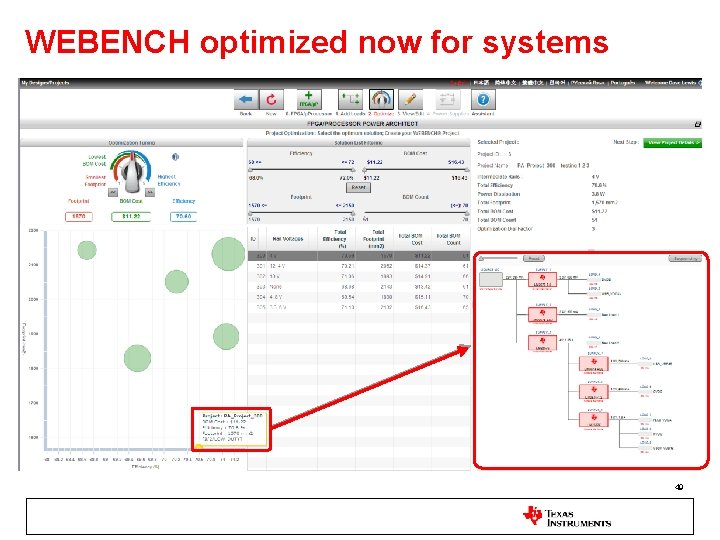

WEBENCH optimized now for systems 49

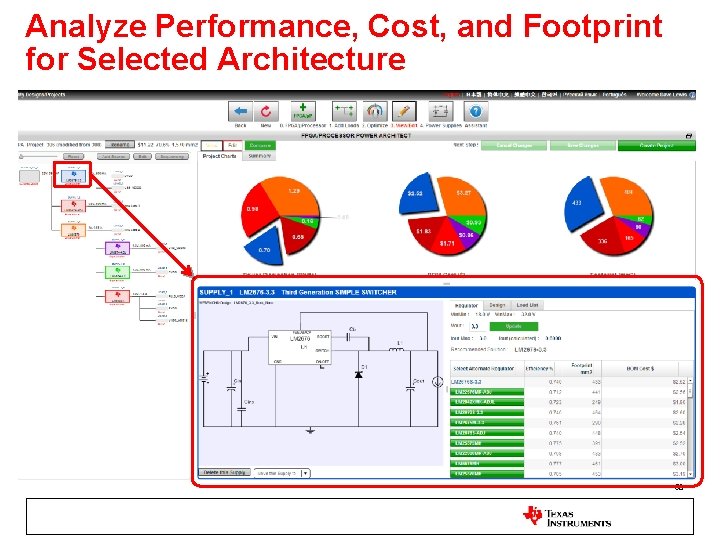

Analyze Performance, Cost, and Footprint for Selected Architecture 50

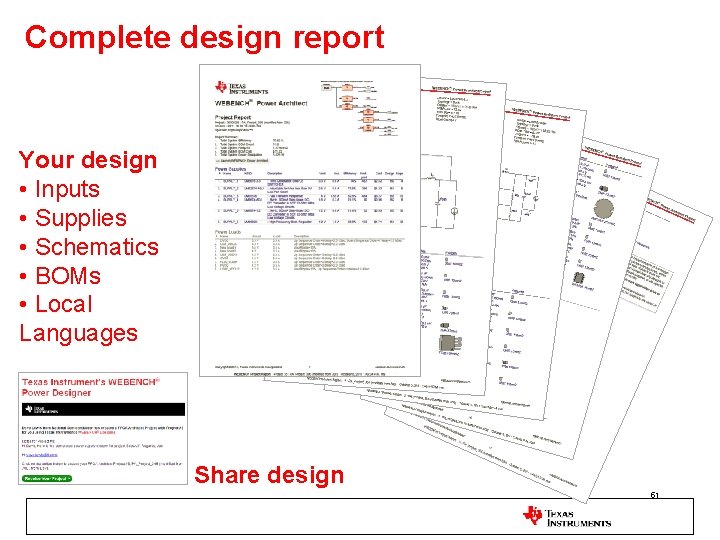

Complete design report Your design • Inputs • Supplies • Schematics • BOMs • Local Languages Share design 51

WEBENCH Power Designer Dynamic design optimization: Provides supply configuration/topology based on size, cost, efficiency Other Features (Not discussed today): Visualizer, Power Architect, LED Designer, FPGA/u. P Architect WEBENCH Design Tools save you time 52

Thanks 53

Appendix LED Lighting Gadgets 54

Phase (TRIAC) Dimmable LED Drivers 55

LM 3466 Multi-String LED Current Equalization 56

- Slides: 55