Washington University School of Engineering and Applied Science

- Slides: 21

Washington University School of Engineering and Applied Science Power Consumption of Customized Numerical Representations for Audio Signal Processing Roger Chamberlain, Yen Hsiang Chew, Varuna De. Alwis, Eric Hemmeter, John Lockwood, Robert Morley, Ed Richter, Jason White, and Huakai Zhang This research is supported by the NIH under grant 1 R 4 -3 DC 04028 -02. HPEC 2002 1

Outline • Audio Signal Requirements • Customized Numerical Representations • SNR and Dynamic Range • Design of Computation Structures • Power Consumption Results • Summary and Conclusions HPEC 2002 2

Audio Signal Applications • Music – MP 3 players • Speech – communications equipment – hearing aids (our target application) • Signal requirements to understand speech – ~30 d. B SNR over entire dynamic range – ~100 d. B dynamic range • Power consumption critical for all of above HPEC 2002 3

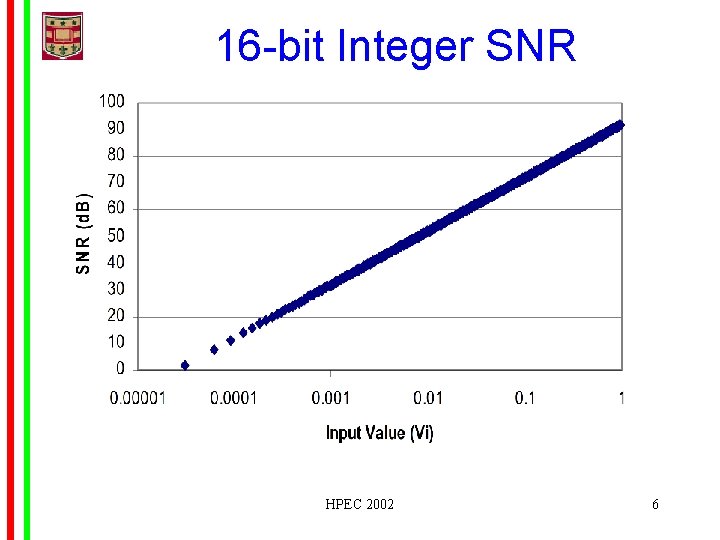

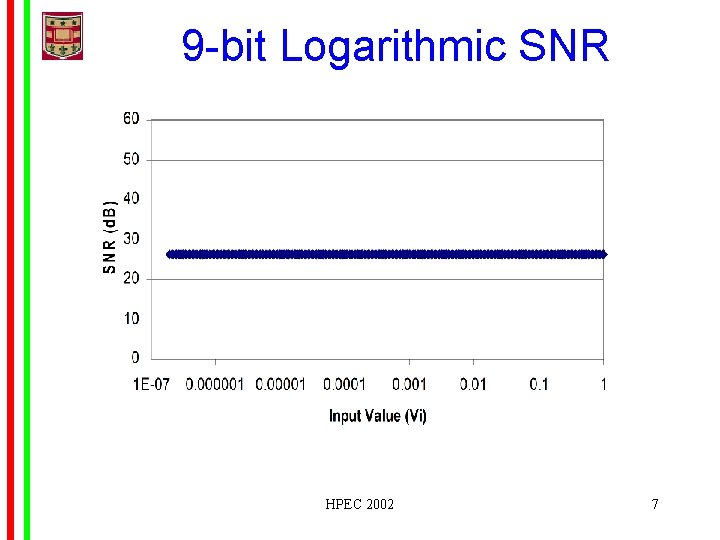

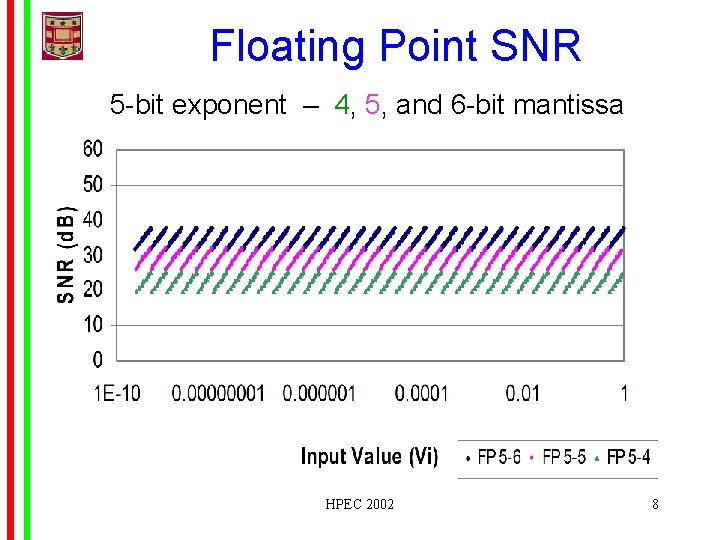

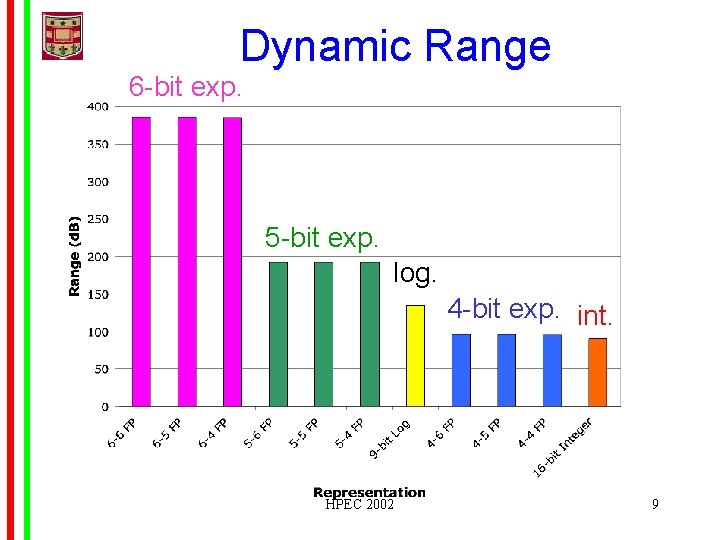

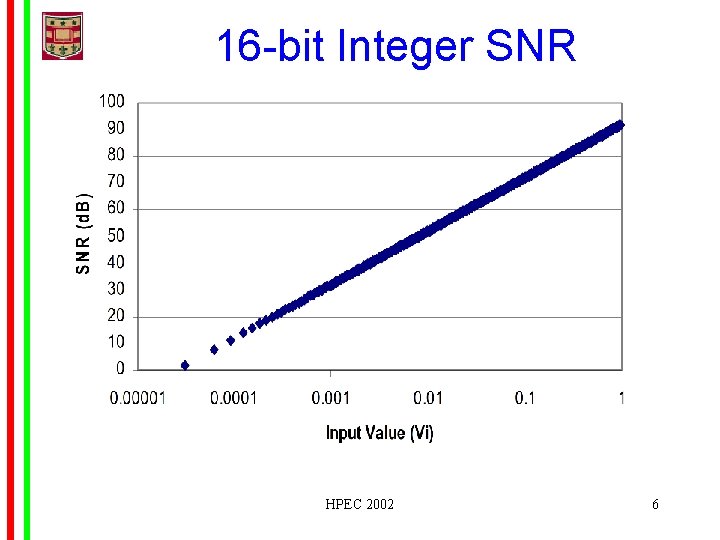

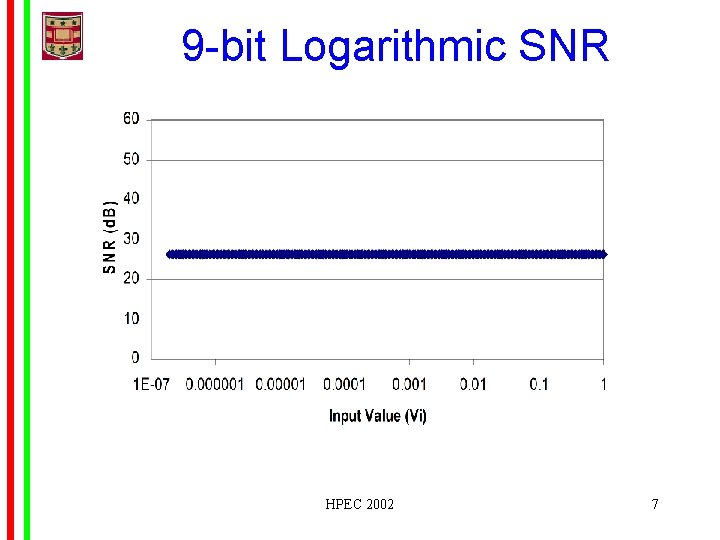

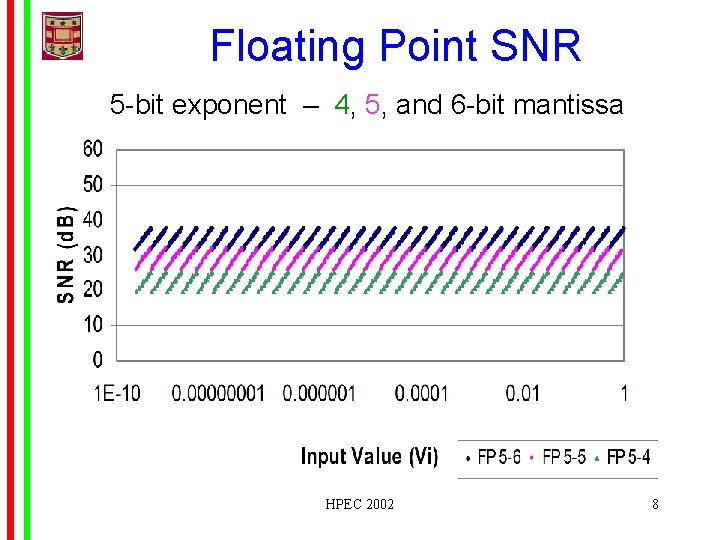

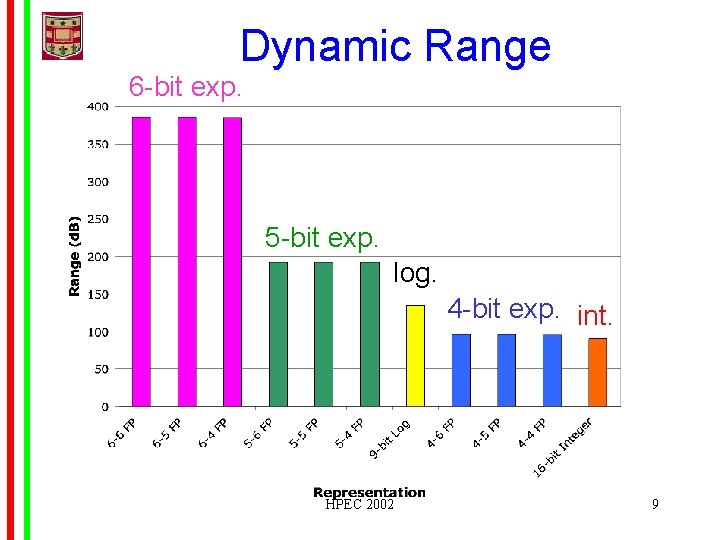

Customized Numerical Representations • 16 -bit integer is traditional for audio – 90 d. B dynamic range, SNR from 0 to 90 d. B • Logarithmic representation more closely mimics human perception – Loudness response is highly non-linear – SNR is relatively constant across dynamic range • Floating point representations are partially logarithmic and partially linear – 32 -bit IEEE standard is more than is needed – Tailor choice for number of bits in exponent and mantissa to needs of application HPEC 2002 4

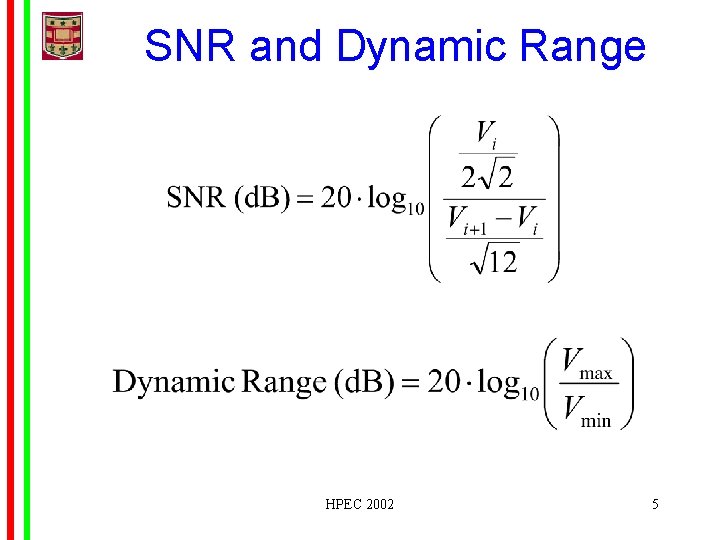

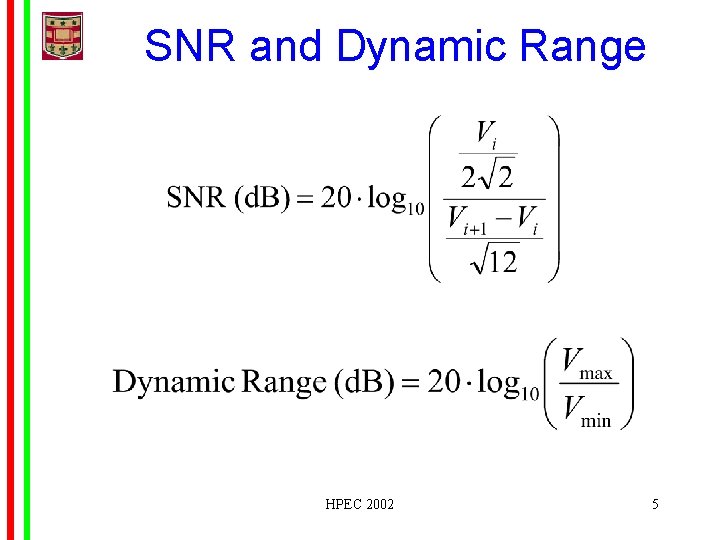

SNR and Dynamic Range HPEC 2002 5

16 -bit Integer SNR HPEC 2002 6

9 -bit Logarithmic SNR HPEC 2002 7

Floating Point SNR 5 -bit exponent – 4, 5, and 6 -bit mantissa HPEC 2002 8

Dynamic Range 6 -bit exp. 5 -bit exp. log. 4 -bit exp. int. HPEC 2002 9

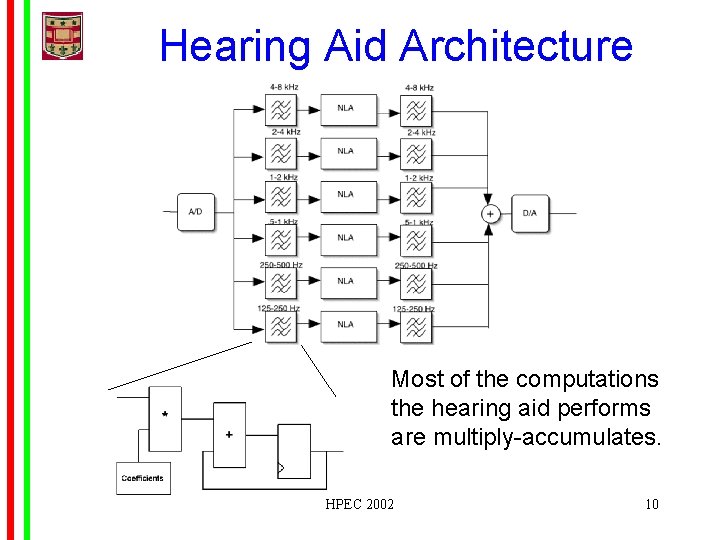

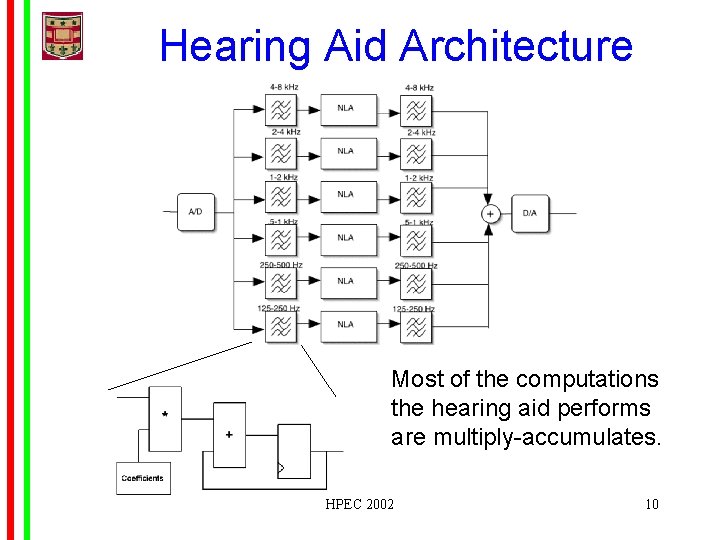

Hearing Aid Architecture Most of the computations the hearing aid performs are multiply-accumulates. HPEC 2002 10

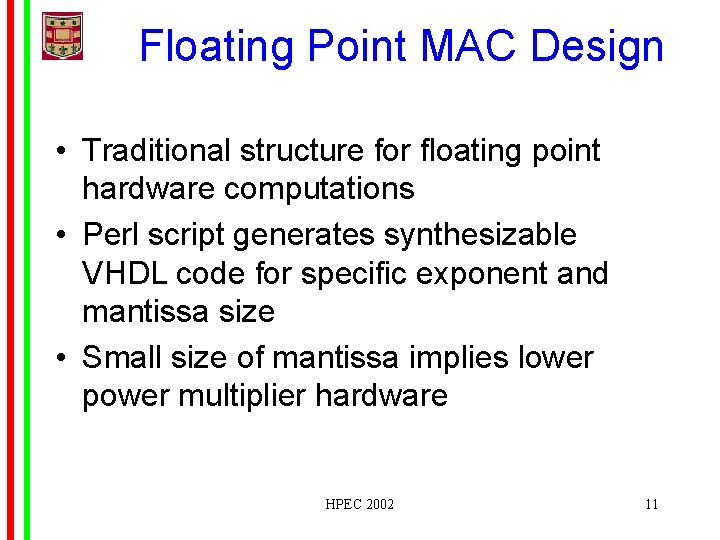

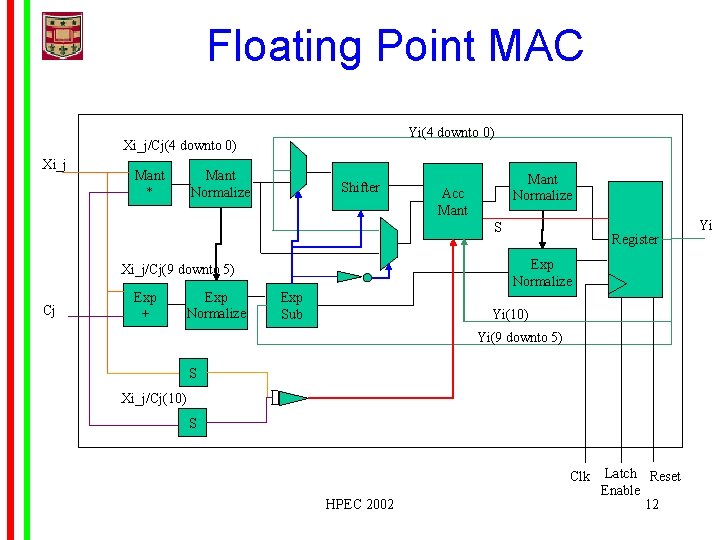

Floating Point MAC Design • Traditional structure for floating point hardware computations • Perl script generates synthesizable VHDL code for specific exponent and mantissa size • Small size of mantissa implies lower power multiplier hardware HPEC 2002 11

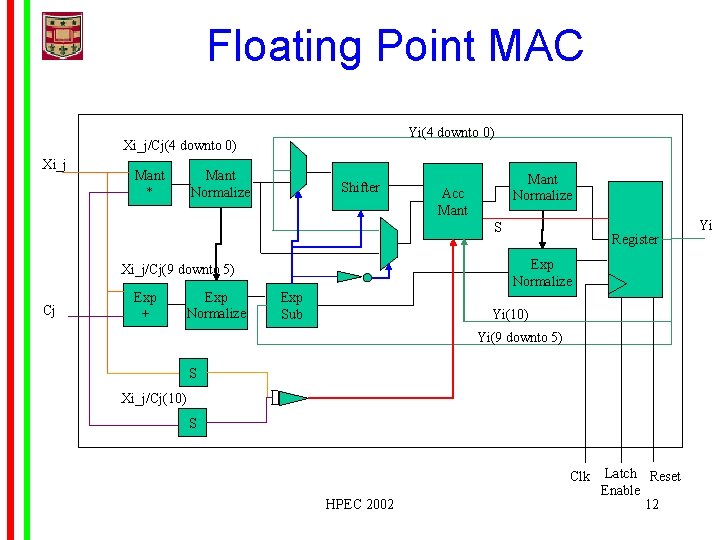

Floating Point MAC Yi(4 downto 0) Xi_j/Cj(4 downto 0) Xi_j Mant * Mant Normalize Shifter Mant Normalize Acc Mant S Exp Normalize Xi_j/Cj(9 downto 5) Cj Exp + Exp Normalize Register Exp Sub Yi(10) Yi(9 downto 5) S Xi_j/Cj(10) S Clk HPEC 2002 Latch Reset Enable 12 Yi

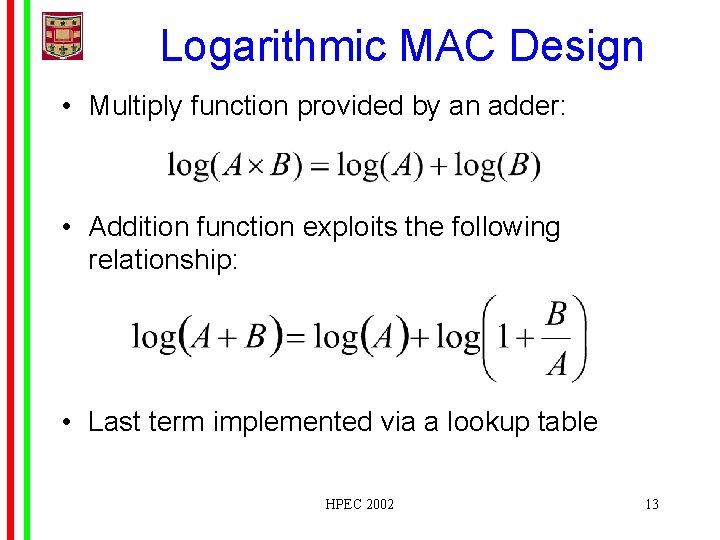

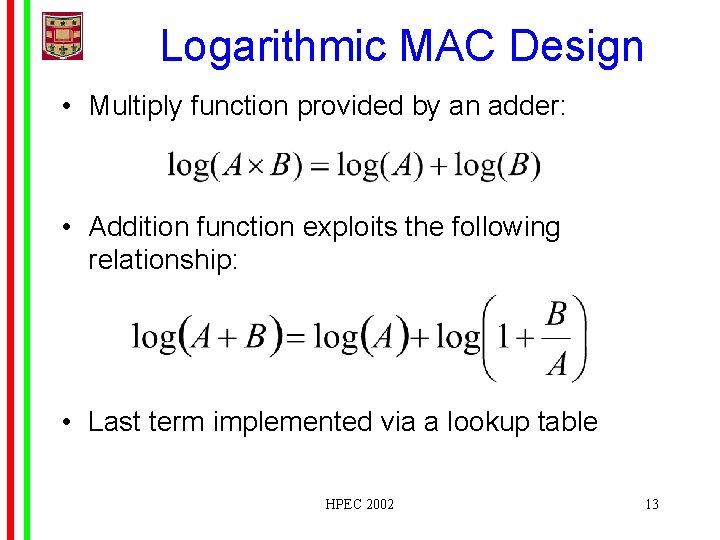

Logarithmic MAC Design • Multiply function provided by an adder: • Addition function exploits the following relationship: • Last term implemented via a lookup table HPEC 2002 13

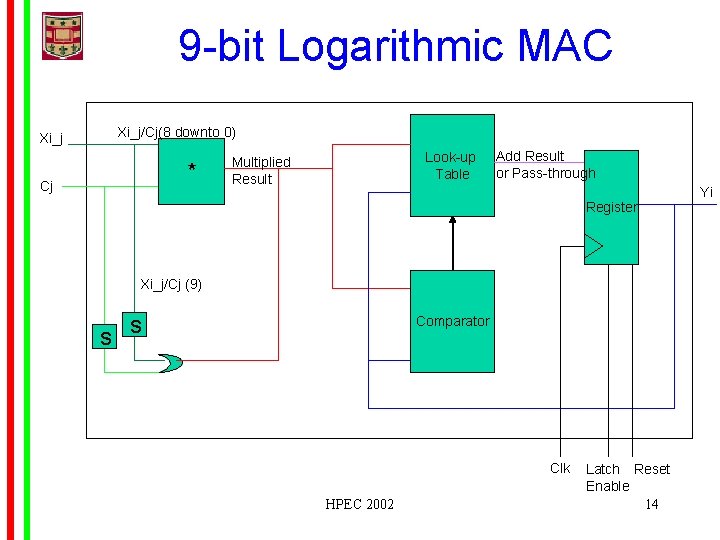

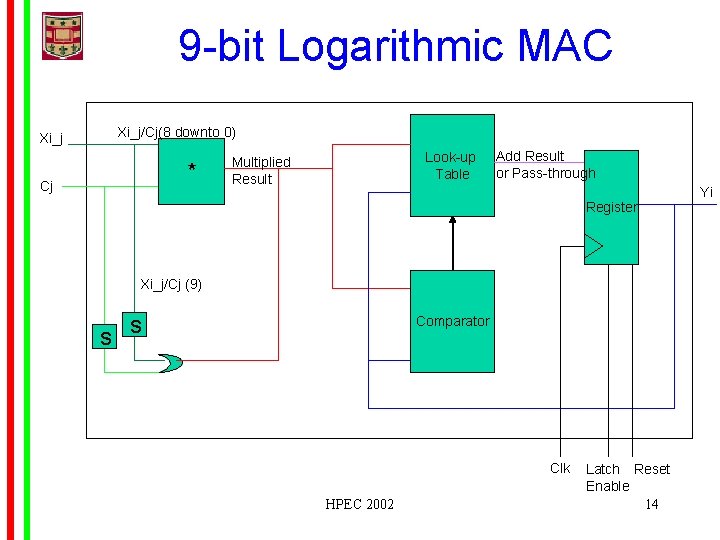

9 -bit Logarithmic MAC Xi_j/Cj(8 downto 0) * Cj Look-up Table Multiplied Result Add Result or Pass-through Register Xi_j/Cj (9) s s Comparator Clk HPEC 2002 Latch Reset Enable 14 Yi

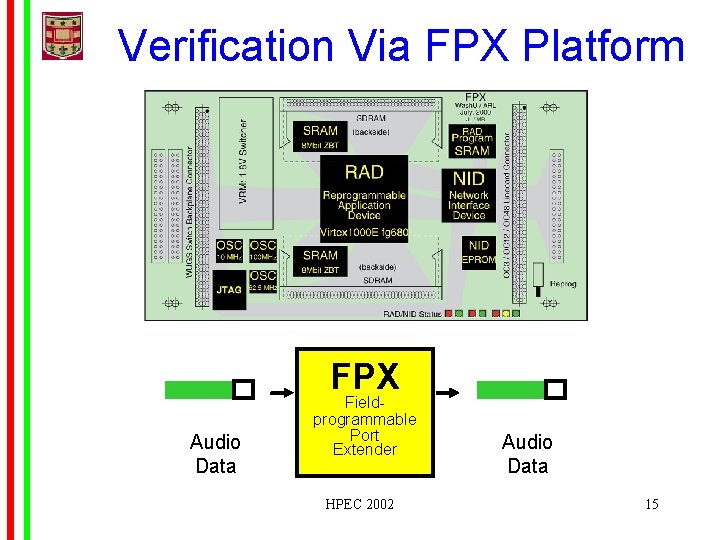

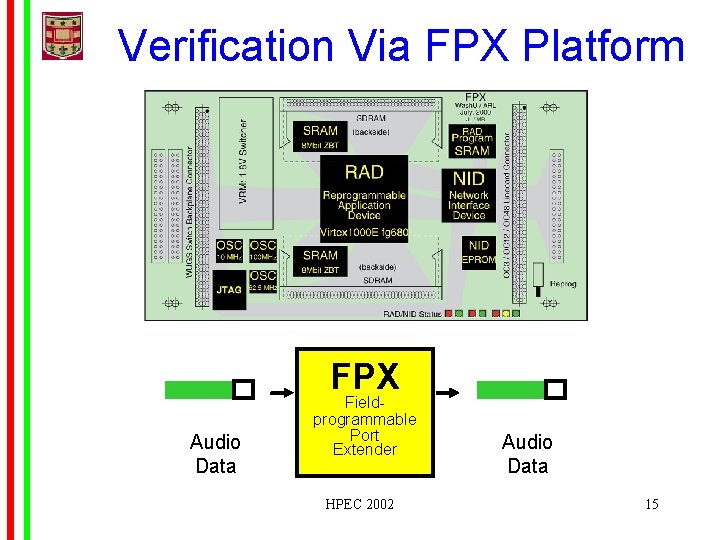

Verification Via FPX Platform FPX Audio Data Fieldprogrammable Port Extender HPEC 2002 Audio Data 15

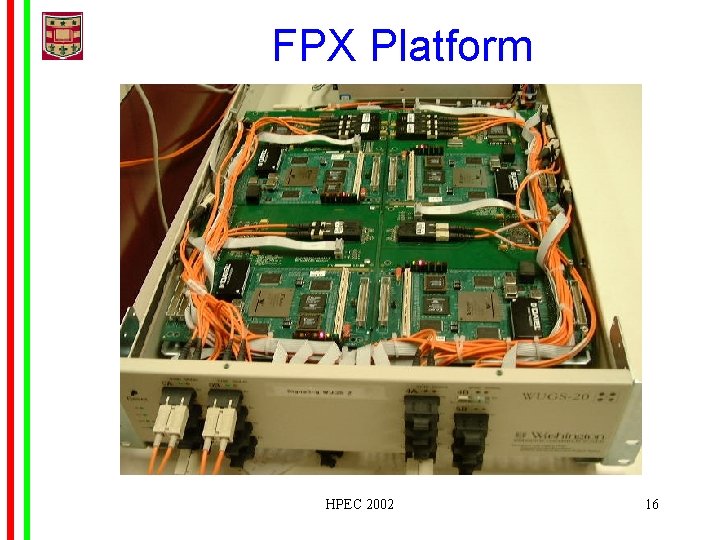

FPX Platform HPEC 2002 16

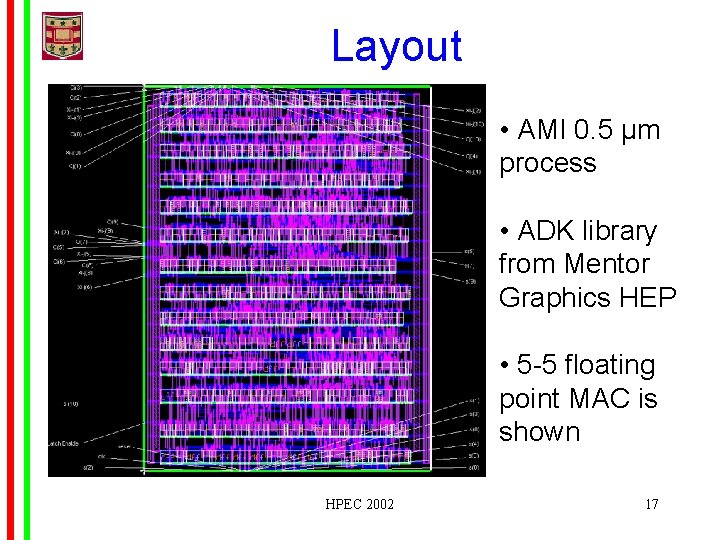

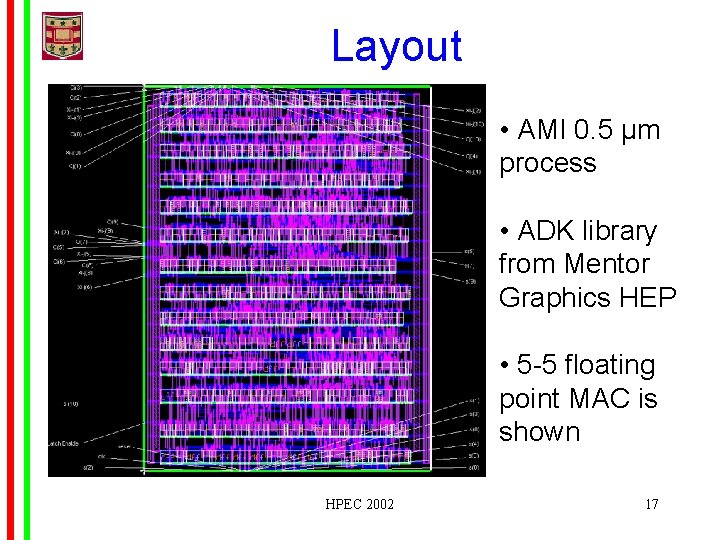

Layout • AMI 0. 5 μm process • ADK library from Mentor Graphics HEP • 5 -5 floating point MAC is shown HPEC 2002 17

Power Estimation via Simulation • Simulate using Mentor Graphics MACH-PA – Spice-level simulation tool – Driven by extracted layout • Focus on Multiply-Accumulate units – Random input vectors – Simulation provides current usage • P = IV provides power results HPEC 2002 18

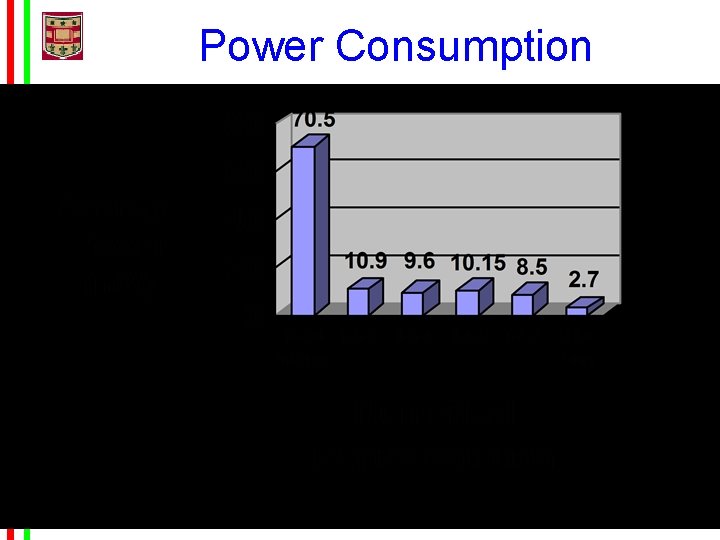

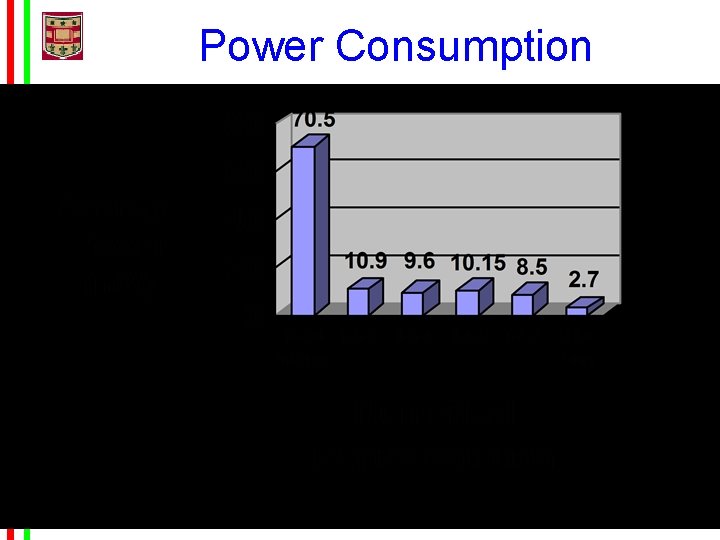

Power Consumption HPEC 2002 19

Summary and Conclusions • Customizing a numerical representation to the specific needs of an application can have tangible benefits • Several 9 or 10 -bit representations have improved SNR and dynamic range for audio speech applications relative to traditional 16 bit integers • Both customized floating point and logarithmic representations have been considered • Power savings are significant HPEC 2002 20

For Further Information http: //www. ccrc. wustl. edu/hearingaid or hearingaid@ccrc. wustl. edu HPEC 2002 21