VVp VVac VVdc RRz CCc CCL CCb RRb

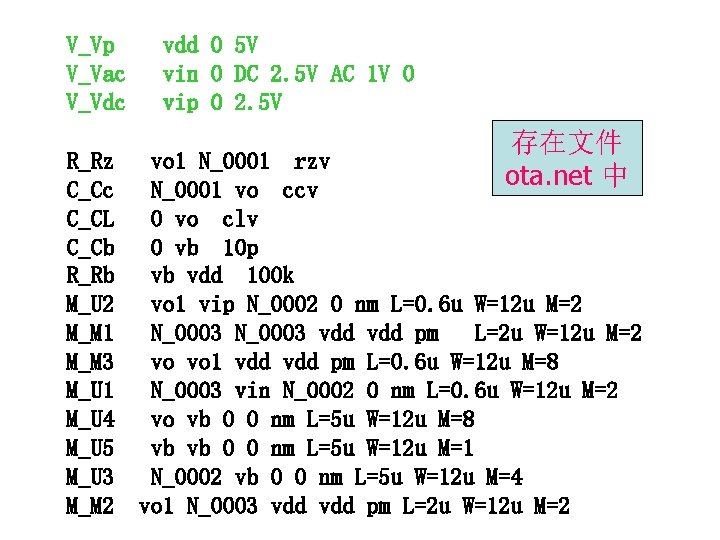

V_Vp V_Vac V_Vdc R_Rz C_Cc C_CL C_Cb R_Rb M_U 2 M_M 1 M_M 3 M_U 1 M_U 4 M_U 5 M_U 3 M_M 2 vdd 0 5 V vin 0 DC 2. 5 V AC 1 V 0 vip 0 2. 5 V 存在文件 ota. net 中 vo 1 N_0001 rzv N_0001 vo ccv 0 vo clv 0 vb 10 p vb vdd 100 k vo 1 vip N_0002 0 nm L=0. 6 u W=12 u M=2 N_0003 vdd pm L=2 u W=12 u M=2 vo vo 1 vdd pm L=0. 6 u W=12 u M=8 N_0003 vin N_0002 0 nm L=0. 6 u W=12 u M=2 vo vb 0 0 nm L=5 u W=12 u M=8 vb vb 0 0 nm L=5 u W=12 u M=1 N_0002 vb 0 0 nm L=5 u W=12 u M=4 vo 1 N_0003 vdd pm L=2 u W=12 u M=2

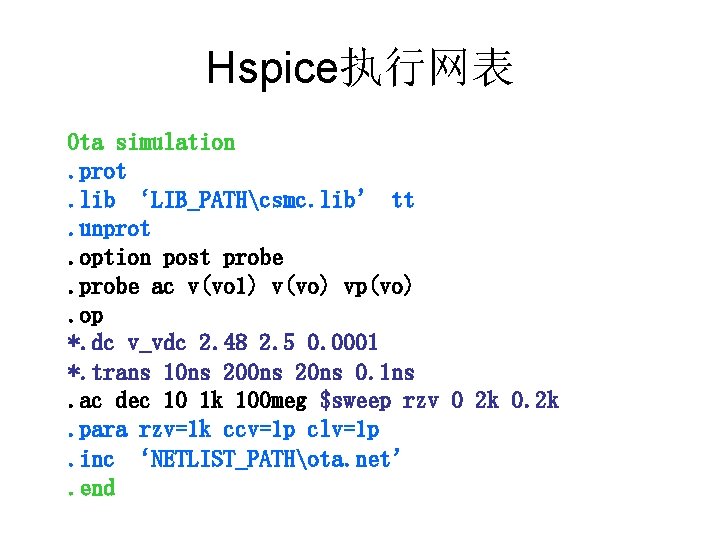

Hspice执行网表 Ota simulation. prot. lib ‘LIB_PATHcsmc. lib’ tt. unprot. option post probe ac v(vo 1) v(vo) vp(vo). op *. dc v_vdc 2. 48 2. 5 0. 0001 *. trans 10 ns 20 ns 0. 1 ns. ac dec 10 1 k 100 meg $sweep rzv 0 2 k 0. 2 k. para rzv=1 k ccv=1 p clv=1 p. inc ‘NETLIST_PATHota. net’. end

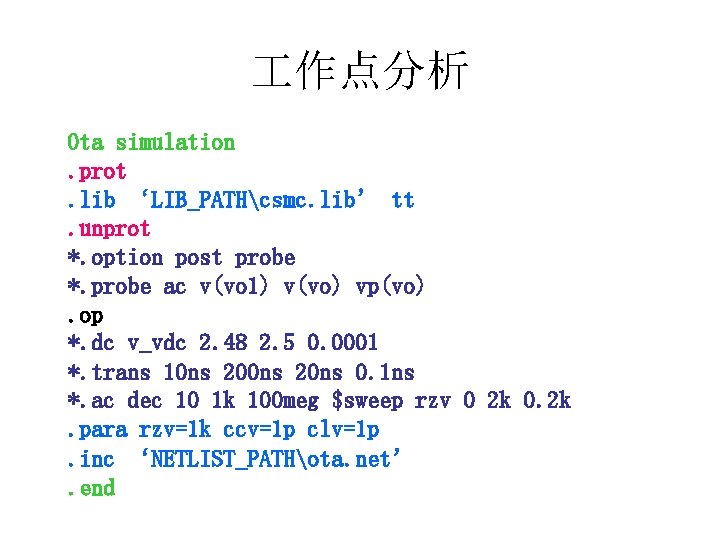

作点分析 Ota simulation. prot. lib ‘LIB_PATHcsmc. lib’ tt. unprot *. option post probe *. probe ac v(vo 1) v(vo) vp(vo). op *. dc v_vdc 2. 48 2. 5 0. 0001 *. trans 10 ns 20 ns 0. 1 ns *. ac dec 10 1 k 100 meg $sweep rzv 0 2 k 0. 2 k. para rzv=1 k ccv=1 p clv=1 p. inc ‘NETLIST_PATHota. net’. end

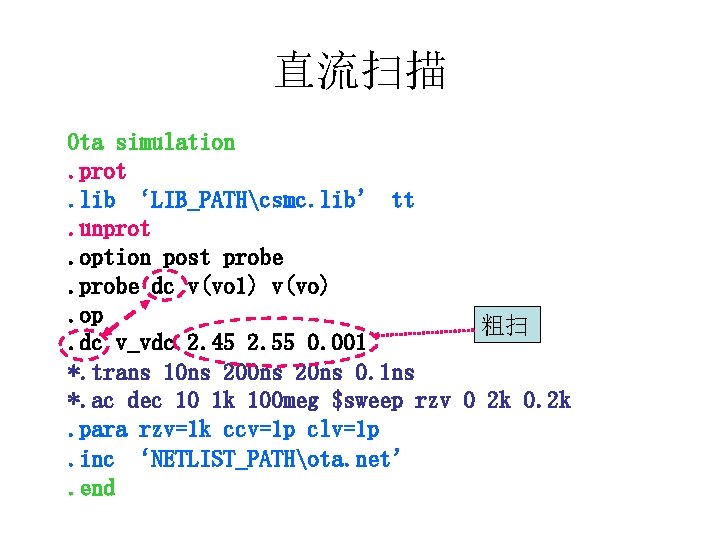

直流扫描 Ota simulation. prot. lib ‘LIB_PATHcsmc. lib’ tt. unprot. option post probe dc v(vo 1) v(vo). op 粗扫. dc v_vdc 2. 45 2. 55 0. 001 *. trans 10 ns 20 ns 0. 1 ns *. ac dec 10 1 k 100 meg $sweep rzv 0 2 k 0. 2 k. para rzv=1 k ccv=1 p clv=1 p. inc ‘NETLIST_PATHota. net’. end

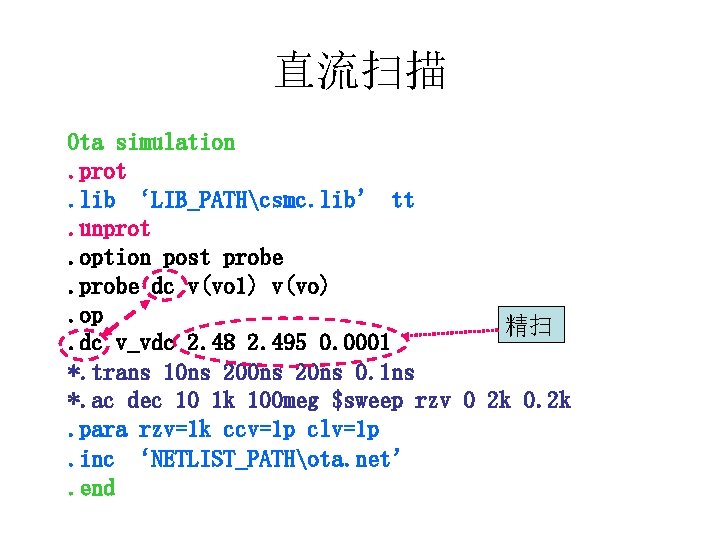

直流扫描 Ota simulation. prot. lib ‘LIB_PATHcsmc. lib’ tt. unprot. option post probe dc v(vo 1) v(vo). op 精扫. dc v_vdc 2. 48 2. 495 0. 0001 *. trans 10 ns 20 ns 0. 1 ns *. ac dec 10 1 k 100 meg $sweep rzv 0 2 k 0. 2 k. para rzv=1 k ccv=1 p clv=1 p. inc ‘NETLIST_PATHota. net’. end

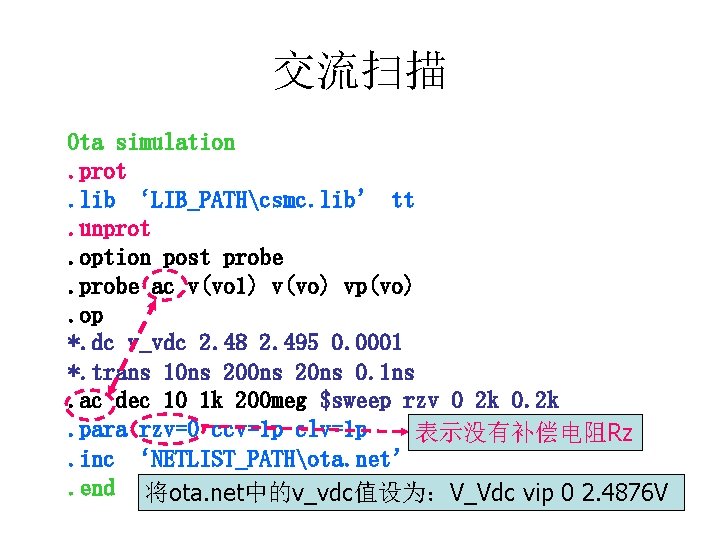

交流扫描 Ota simulation. prot. lib ‘LIB_PATHcsmc. lib’ tt. unprot. option post probe ac v(vo 1) v(vo) vp(vo). op *. dc v_vdc 2. 48 2. 495 0. 0001 *. trans 10 ns 20 ns 0. 1 ns. ac dec 10 1 k 200 meg $sweep rzv 0 2 k 0. 2 k. para rzv=0 ccv=1 p clv=1 p 表示没有补偿电阻Rz. inc ‘NETLIST_PATHota. net’. end 将ota. net中的v_vdc值设为:V_Vdc vip 0 2. 4876 V

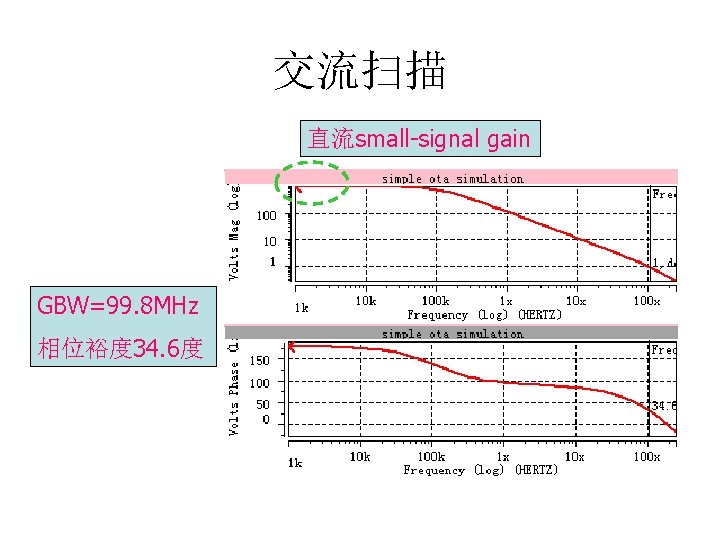

交流扫描 直流small-signal gain GBW=99. 8 MHz 相位裕度 34. 6度

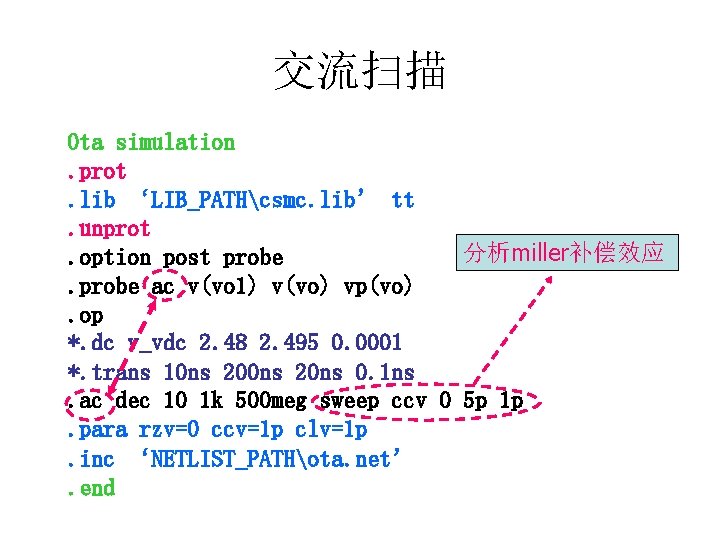

交流扫描 Ota simulation. prot. lib ‘LIB_PATHcsmc. lib’ tt. unprot 分析miller补偿效应. option post probe ac v(vo 1) v(vo) vp(vo). op *. dc v_vdc 2. 48 2. 495 0. 0001 *. trans 10 ns 20 ns 0. 1 ns. ac dec 10 1 k 500 meg sweep ccv 0 5 p 1 p. para rzv=0 ccv=1 p clv=1 p. inc ‘NETLIST_PATHota. net’. end

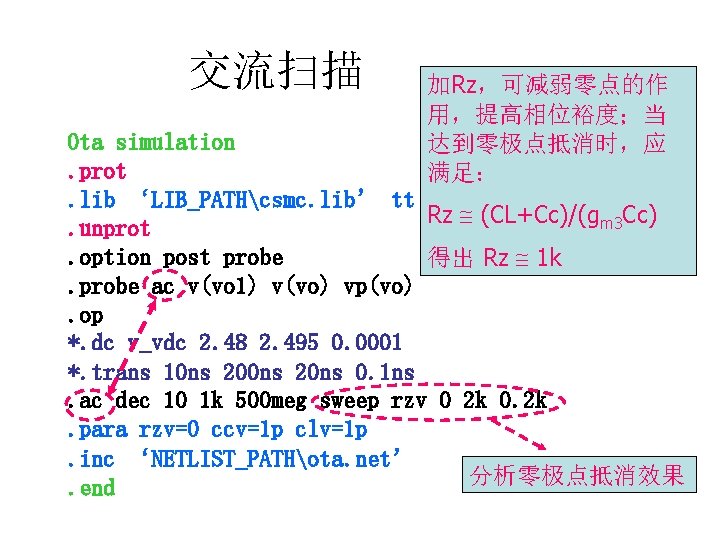

交流扫描 加Rz,可减弱零点的作 用,提高相位裕度;当 达到零极点抵消时,应 满足: Ota simulation. prot. lib ‘LIB_PATHcsmc. lib’ tt Rz (CL+Cc)/(gm 3 Cc). unprot. option post probe 得出 Rz 1 k. probe ac v(vo 1) v(vo) vp(vo). op *. dc v_vdc 2. 48 2. 495 0. 0001 *. trans 10 ns 20 ns 0. 1 ns. ac dec 10 1 k 500 meg sweep rzv 0 2 k 0. 2 k. para rzv=0 ccv=1 p clv=1 p. inc ‘NETLIST_PATHota. net’ 分析零极点抵消效果. end

噪声分析 Ota simulation. prot. lib ‘LIB_PATHcsmc. lib’ tt. unprot. option post probe 分析热噪声. probe ac v(vo 1) v(vo) vp(vo). op *. dc v_vdc 2. 48 2. 495 0. 0001 *. trans 10 ns 20 ns 0. 1 ns. ac dec 10 1 k 500 meg $sweep rzv 0 2 k 0. 2 k. noise v(vo) v_vac 10. para rzv=1 k ccv=1 p clv=1 p. inc ‘NETLIST_PATHota. net’. end

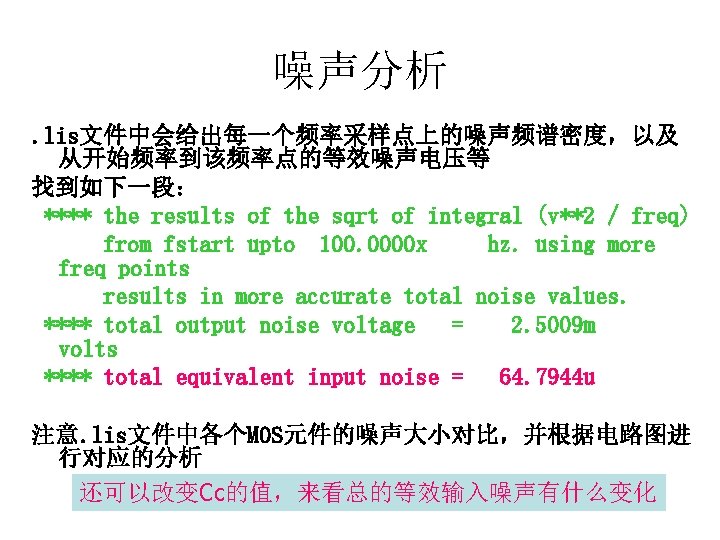

噪声分析. lis文件中会给出每一个频率采样点上的噪声频谱密度,以及 从开始频率到该频率点的等效噪声电压等 找到如下一段: **** the results of the sqrt of integral (v**2 / freq) from fstart upto 100. 0000 x hz. using more freq points results in more accurate total noise values. **** total output noise voltage = 2. 5009 m volts **** total equivalent input noise = 64. 7944 u 注意. lis文件中各个MOS元件的噪声大小对比,并根据电路图进 行对应的分析 还可以改变Cc的值,来看总的等效输入噪声有什么变化

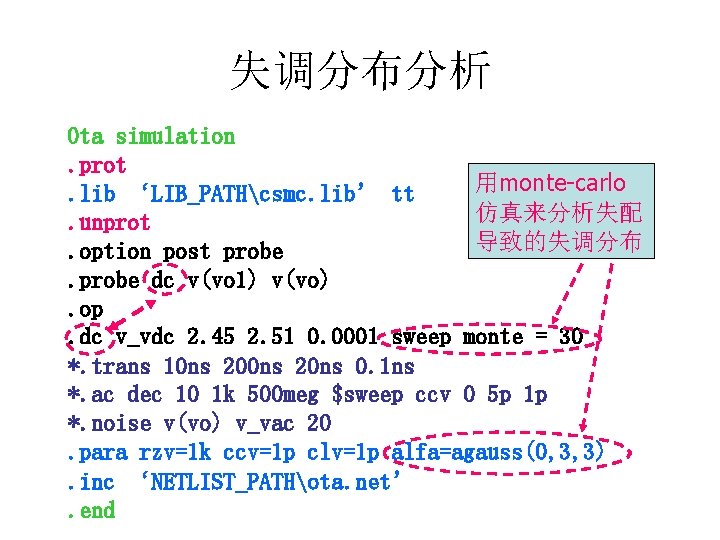

失调分布分析 Ota simulation. prot 用monte-carlo. lib ‘LIB_PATHcsmc. lib’ tt 仿真来分析失配. unprot 导致的失调分布. option post probe dc v(vo 1) v(vo). op. dc v_vdc 2. 45 2. 51 0. 0001 sweep monte = 30 *. trans 10 ns 20 ns 0. 1 ns *. ac dec 10 1 k 500 meg $sweep ccv 0 5 p 1 p *. noise v(vo) v_vac 20. para rzv=1 k ccv=1 p clv=1 p alfa=agauss(0, 3, 3). inc ‘NETLIST_PATHota. net’. end

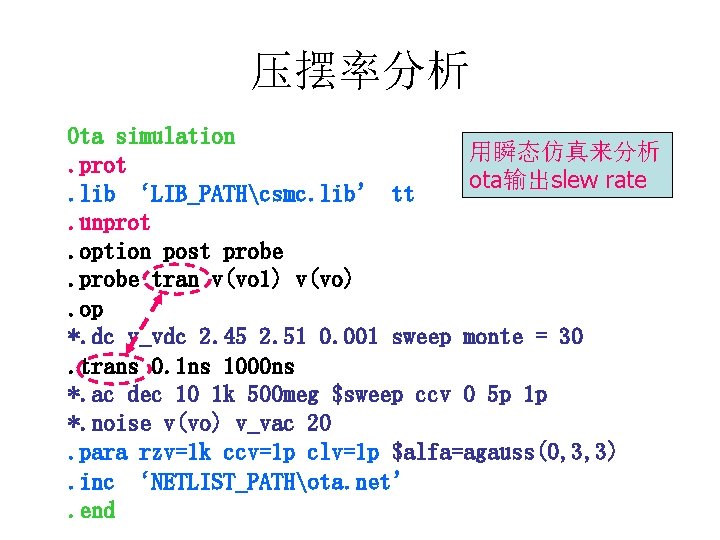

压摆率分析 Ota simulation 用瞬态仿真来分析. prot ota输出slew rate. lib ‘LIB_PATHcsmc. lib’ tt. unprot. option post probe tran v(vo 1) v(vo). op *. dc v_vdc 2. 45 2. 51 0. 001 sweep monte = 30. trans 0. 1 ns 1000 ns *. ac dec 10 1 k 500 meg $sweep ccv 0 5 p 1 p *. noise v(vo) v_vac 20. para rzv=1 k ccv=1 p clv=1 p $alfa=agauss(0, 3, 3). inc ‘NETLIST_PATHota. net’. end

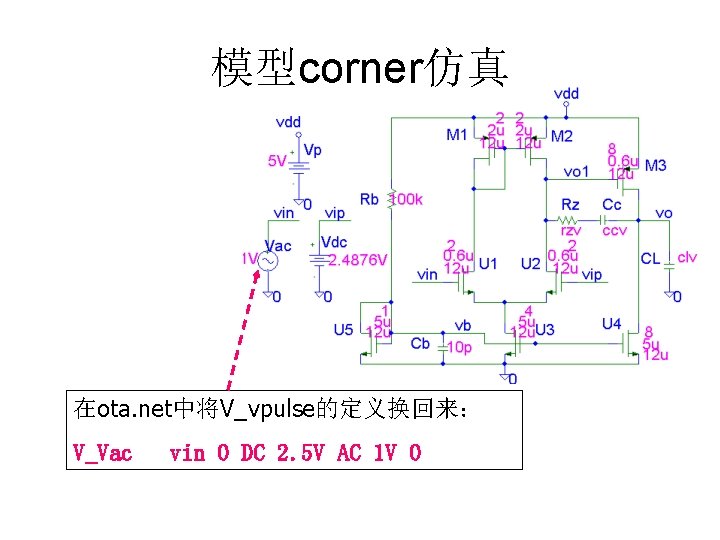

模型corner仿真 在ota. net中将V_vpulse的定义换回来: V_Vac vin 0 DC 2. 5 V AC 1 V 0

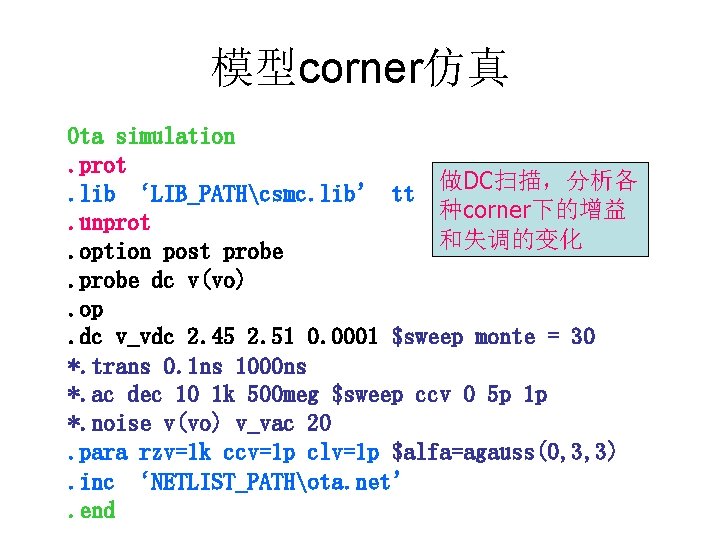

模型corner仿真 Ota simulation. prot. lib ‘LIB_PATHcsmc. lib’ tt 做DC扫描,分析各 种corner下的增益. unprot 和失调的变化. option post probe dc v(vo). op. dc v_vdc 2. 45 2. 51 0. 0001 $sweep monte = 30 *. trans 0. 1 ns 1000 ns *. ac dec 10 1 k 500 meg $sweep ccv 0 5 p 1 p *. noise v(vo) v_vac 20. para rzv=1 k ccv=1 p clv=1 p $alfa=agauss(0, 3, 3). inc ‘NETLIST_PATHota. net’. end

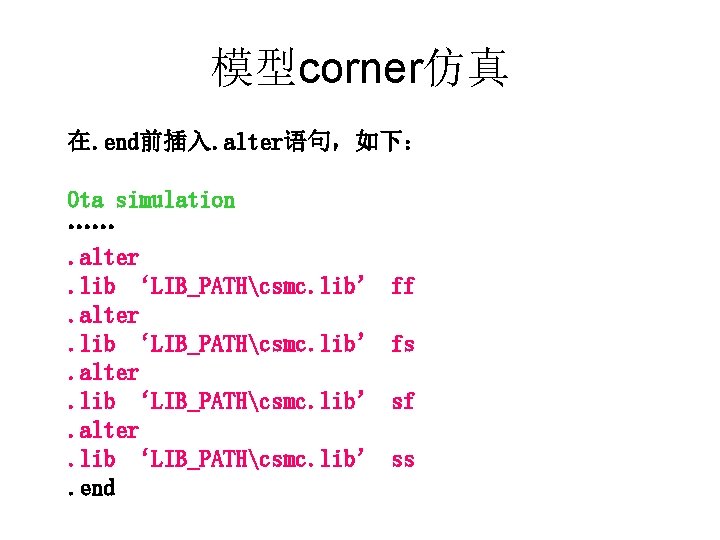

模型corner仿真 在. end前插入. alter语句,如下: Ota simulation ……. alter. lib ‘LIB_PATHcsmc. lib’. end ff fs sf ss

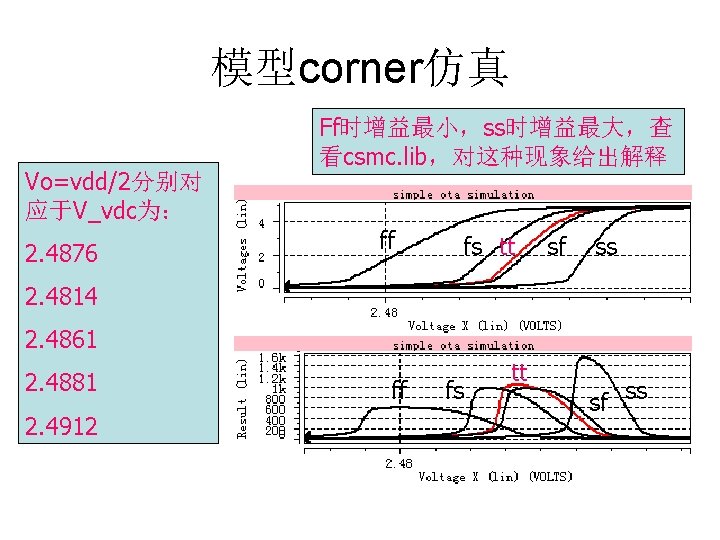

模型corner仿真 Vo=vdd/2分别对 应于V_vdc为: 2. 4876 Ff时增益最小,ss时增益最大,查 看csmc. lib,对这种现象给出解释 ff fs tt sf ss 2. 4814 2. 4861 2. 4881 2. 4912 ff fs tt sf ss

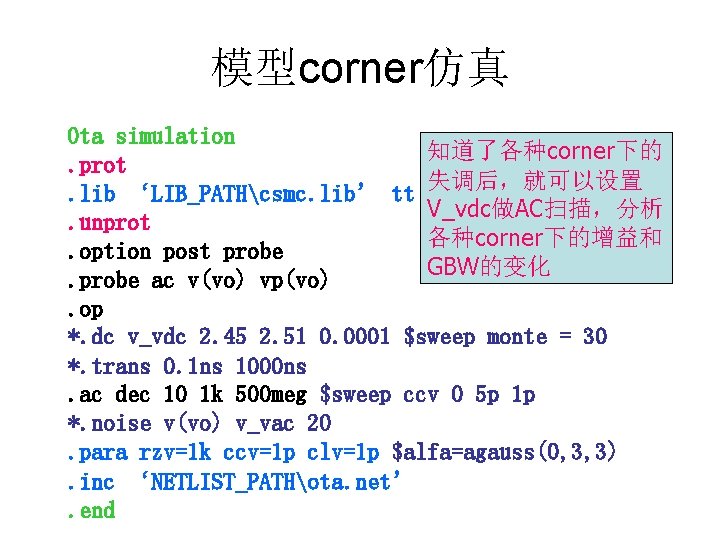

模型corner仿真 Ota simulation 知道了各种corner下的. prot. lib ‘LIB_PATHcsmc. lib’ tt 失调后,就可以设置 V_vdc做AC扫描,分析. unprot 各种corner下的增益和. option post probe GBW的变化. probe ac v(vo) vp(vo). op *. dc v_vdc 2. 45 2. 51 0. 0001 $sweep monte = 30 *. trans 0. 1 ns 1000 ns. ac dec 10 1 k 500 meg $sweep ccv 0 5 p 1 p *. noise v(vo) v_vac 20. para rzv=1 k ccv=1 p clv=1 p $alfa=agauss(0, 3, 3). inc ‘NETLIST_PATHota. net’. end

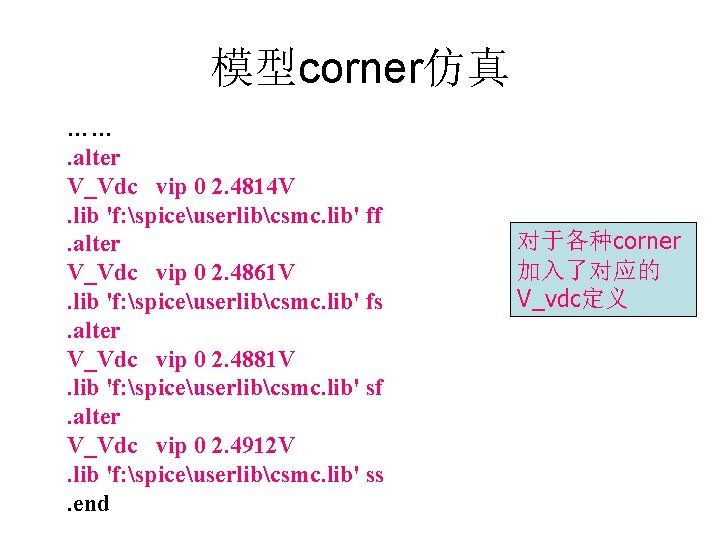

模型corner仿真 ……. alter V_Vdc vip 0 2. 4814 V. lib 'f: spiceuserlibcsmc. lib' ff. alter V_Vdc vip 0 2. 4861 V. lib 'f: spiceuserlibcsmc. lib' fs. alter V_Vdc vip 0 2. 4881 V. lib 'f: spiceuserlibcsmc. lib' sf. alter V_Vdc vip 0 2. 4912 V. lib 'f: spiceuserlibcsmc. lib' ss. end 对于各种corner 加入了对应的 V_vdc定义

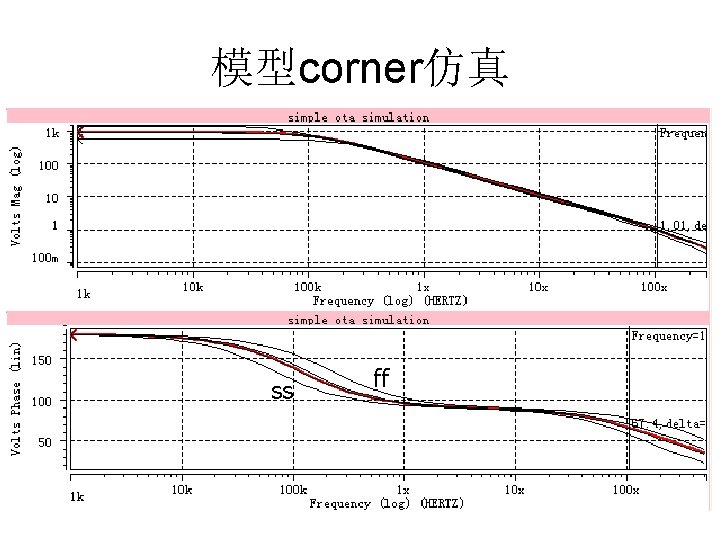

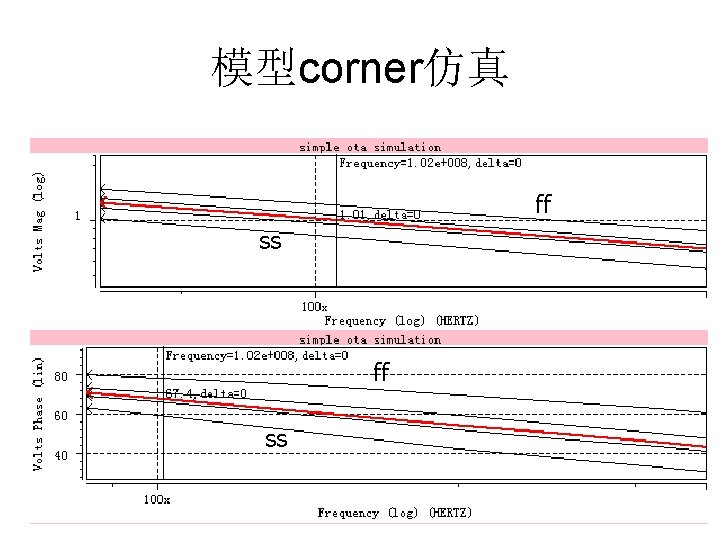

模型corner仿真 ss ff

模型corner仿真 ff ss

模型corner仿真 由仿真结果可测得: tt ff fs sf ss gain 989 585 922 939 1. 46 k GBW 103 MHz 122 MHz 108 MHz 97. 9 MHz 87. 4 MHz Phase margin 67. 2 75. 9 64. 8 71. 2 62. 4

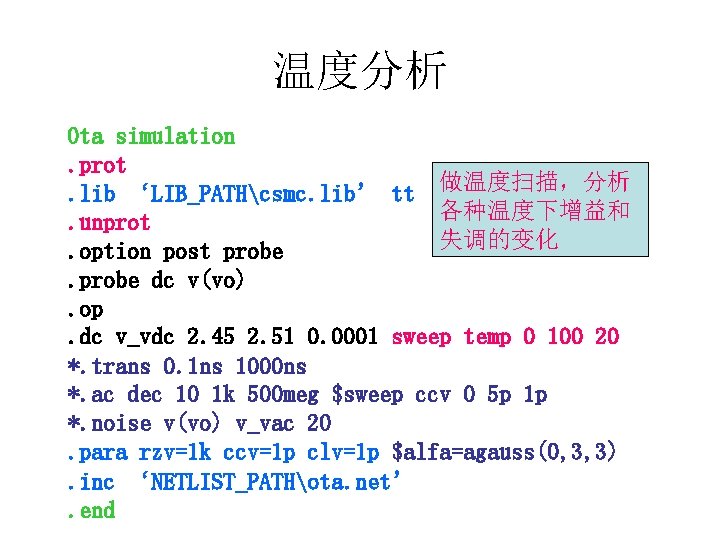

温度分析 Ota simulation. prot. lib ‘LIB_PATHcsmc. lib’ tt 做温度扫描,分析 各种温度下增益和. unprot 失调的变化. option post probe dc v(vo). op. dc v_vdc 2. 45 2. 51 0. 0001 sweep temp 0 100 20 *. trans 0. 1 ns 1000 ns *. ac dec 10 1 k 500 meg $sweep ccv 0 5 p 1 p *. noise v(vo) v_vac 20. para rzv=1 k ccv=1 p clv=1 p $alfa=agauss(0, 3, 3). inc ‘NETLIST_PATHota. net’. end

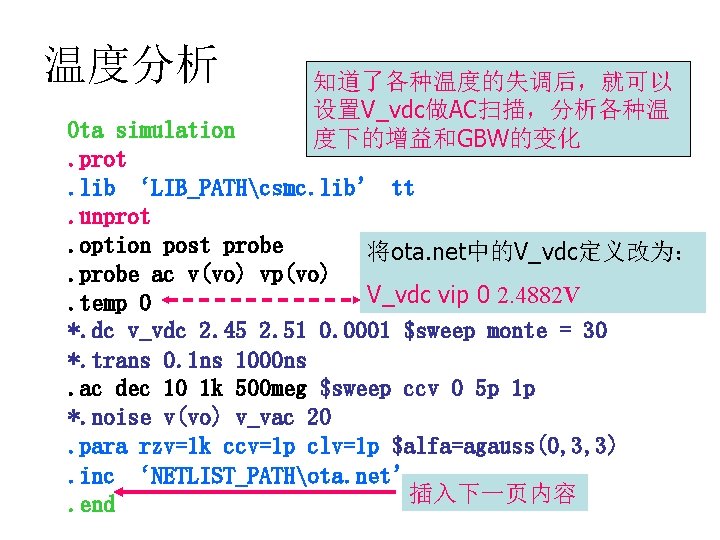

温度分析 知道了各种温度的失调后,就可以 设置V_vdc做AC扫描,分析各种温 度下的增益和GBW的变化 Ota simulation. prot. lib ‘LIB_PATHcsmc. lib’ tt. unprot. option post probe 将ota. net中的V_vdc定义改为:. probe ac v(vo) vp(vo) V_vdc vip 0 2. 4882 V. temp 0 *. dc v_vdc 2. 45 2. 51 0. 0001 $sweep monte = 30 *. trans 0. 1 ns 1000 ns. ac dec 10 1 k 500 meg $sweep ccv 0 5 p 1 p *. noise v(vo) v_vac 20. para rzv=1 k ccv=1 p clv=1 p $alfa=agauss(0, 3, 3). inc ‘NETLIST_PATHota. net’ 插入下一页内容. end

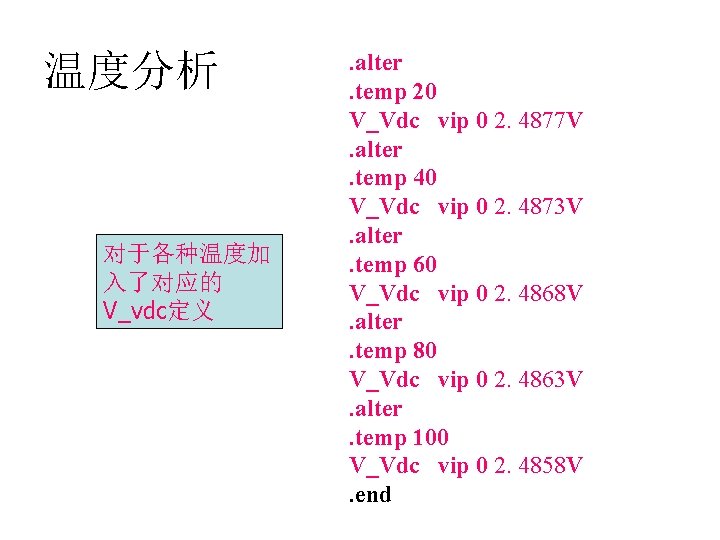

温度分析 对于各种温度加 入了对应的 V_vdc定义 . alter. temp 20 V_Vdc vip 0 2. 4877 V. alter. temp 40 V_Vdc vip 0 2. 4873 V. alter. temp 60 V_Vdc vip 0 2. 4868 V. alter. temp 80 V_Vdc vip 0 2. 4863 V. alter. temp 100 V_Vdc vip 0 2. 4858 V. end

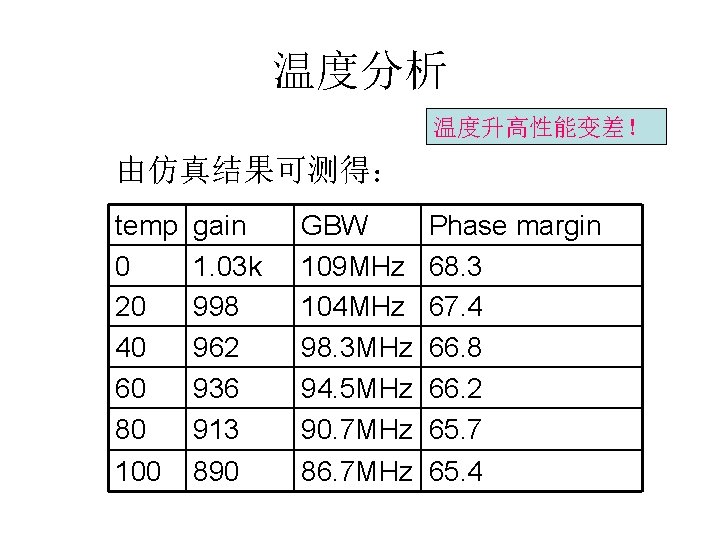

温度分析 温度升高性能变差! 由仿真结果可测得: temp 0 20 40 60 80 gain 1. 03 k 998 962 936 913 GBW 109 MHz 104 MHz 98. 3 MHz 94. 5 MHz 90. 7 MHz Phase margin 68. 3 67. 4 66. 8 66. 2 65. 7 100 890 86. 7 MHz 65. 4

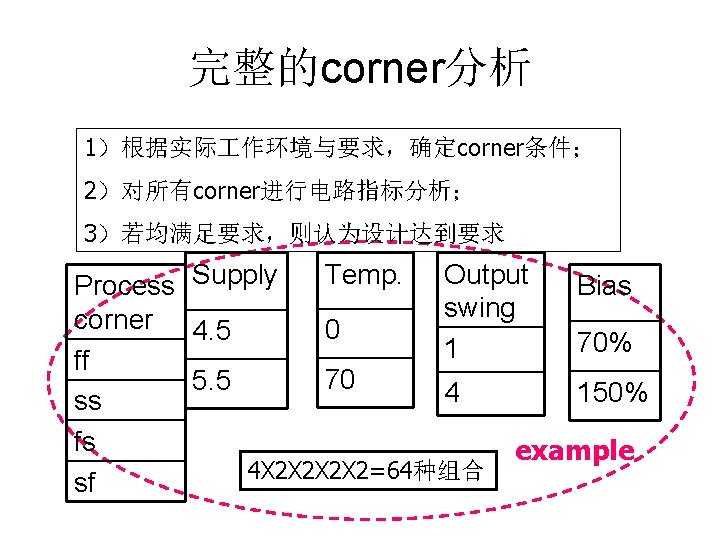

完整的corner分析 1)根据实际 作环境与要求,确定corner条件; 2)对所有corner进行电路指标分析; 3)若均满足要求,则认为设计达到要求 Temp. Output Process Supply Bias swing corner 4. 5 0 70% 1 ff 70 5. 5 150% 4 ss fs example 4 X 2 X 2=64种组合 sf

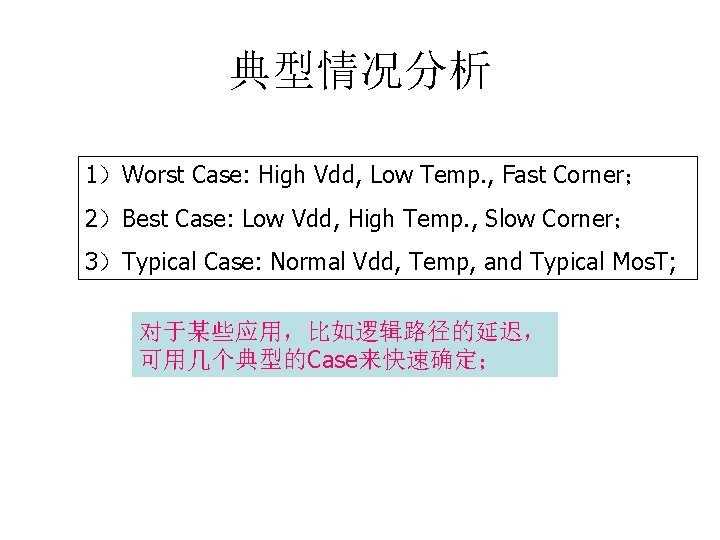

典型情况分析 1)Worst Case: High Vdd, Low Temp. , Fast Corner; 2)Best Case: Low Vdd, High Temp. , Slow Corner; 3)Typical Case: Normal Vdd, Temp, and Typical Mos. T; 对于某些应用,比如逻辑路径的延迟, 可用几个典型的Case来快速确定;

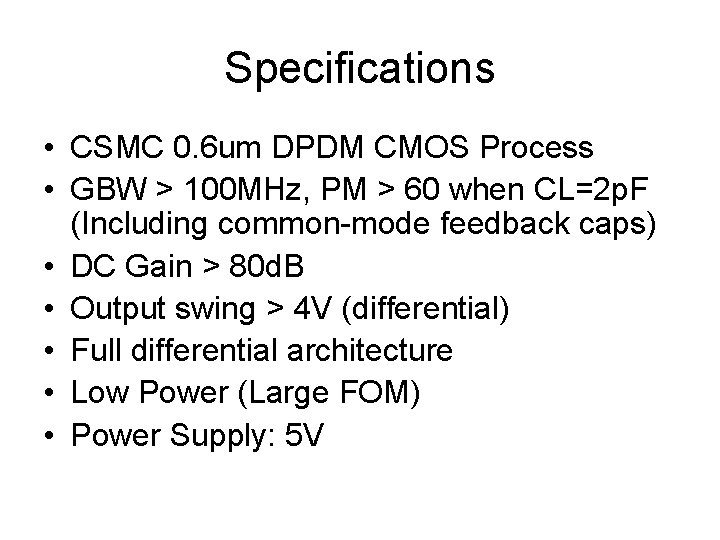

Specifications • CSMC 0. 6 um DPDM CMOS Process • GBW > 100 MHz, PM > 60 when CL=2 p. F (Including common-mode feedback caps) • DC Gain > 80 d. B • Output swing > 4 V (differential) • Full differential architecture • Low Power (Large FOM) • Power Supply: 5 V

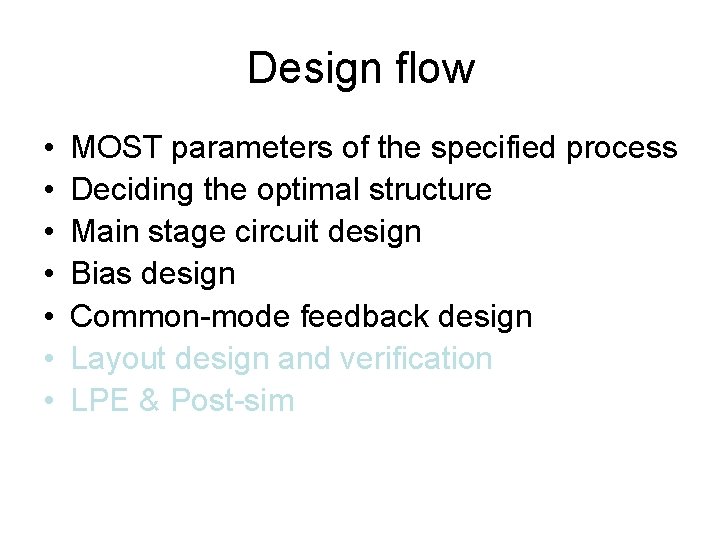

Design flow • • MOST parameters of the specified process Deciding the optimal structure Main stage circuit design Bias design Common-mode feedback design Layout design and verification LPE & Post-sim

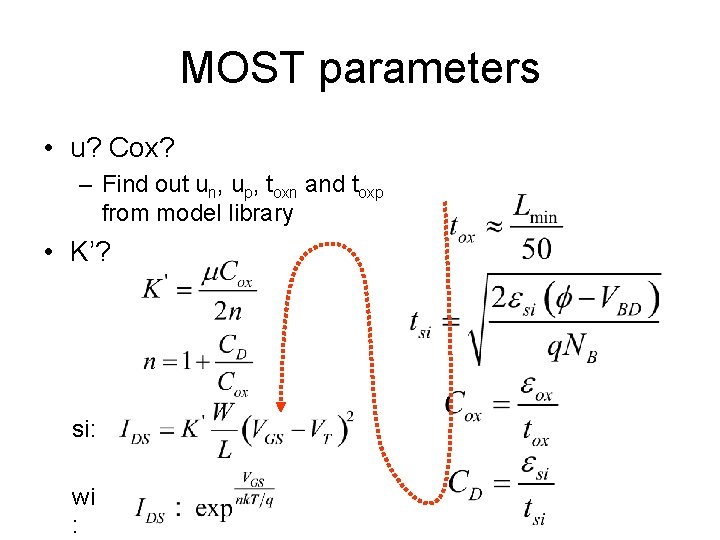

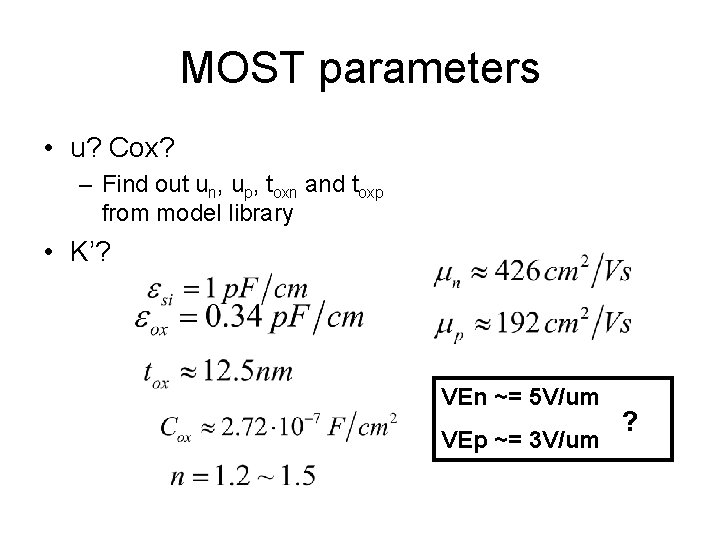

MOST parameters • u? Cox? – Find out un, up, toxn and toxp from model library • K’? si: wi :

MOST parameters • u? Cox? – Find out un, up, toxn and toxp from model library • K’? VEn ~= 5 V/um VEp ~= 3 V/um ?

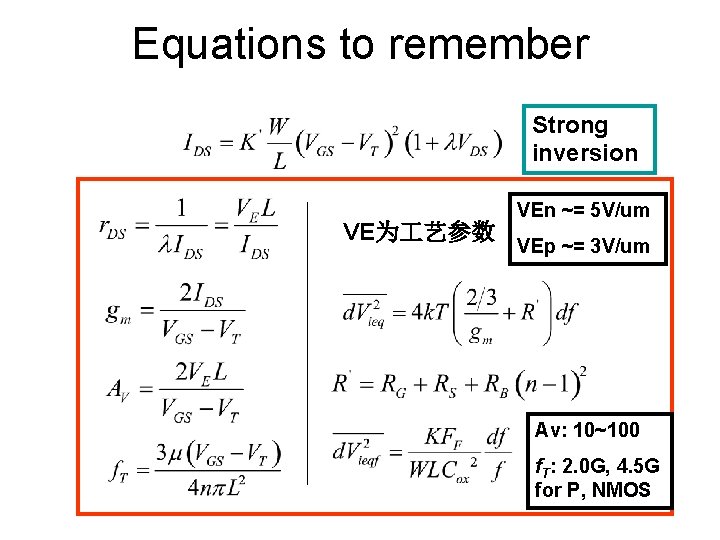

Equations to remember Strong inversion VE为 艺参数 VEn ~= 5 V/um VEp ~= 3 V/um Av: 10~100 f. T: 2. 0 G, 4. 5 G for P, NMOS

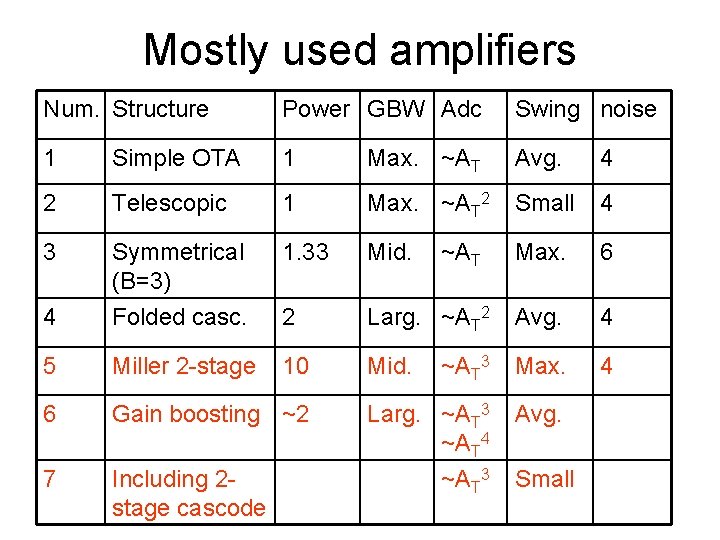

Mostly used amplifiers Num. Structure Power GBW Adc Swing noise 1 Simple OTA 1 Max. ~AT Avg. 4 2 Telescopic 1 Max. ~AT 2 Small 4 3 Symmetrical (B=3) 1. 33 Mid. Max. 6 4 Folded casc. 2 Larg. ~AT 2 Avg. 4 5 Miller 2 -stage 10 Mid. ~AT 3 Max. 4 6 Gain boosting ~2 Larg. ~AT 3 ~AT 4 Avg. 7 Including 2 stage cascode ~AT 3 Small

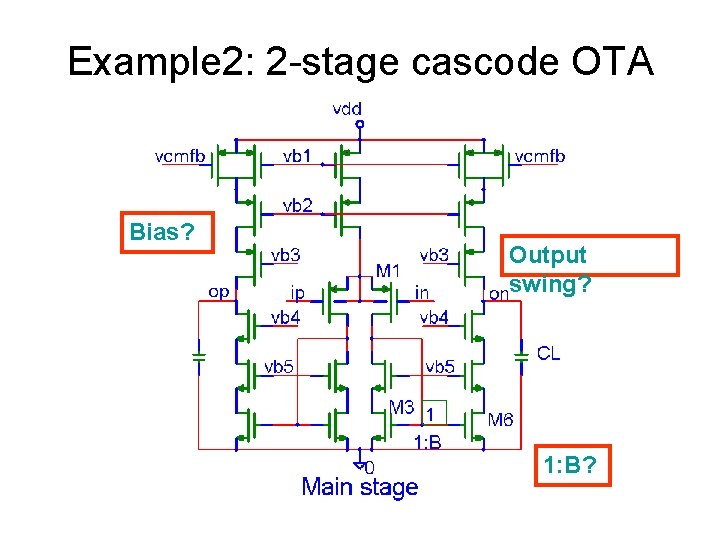

Example 2: 2 -stage cascode OTA Bias? Output swing? 1: B?

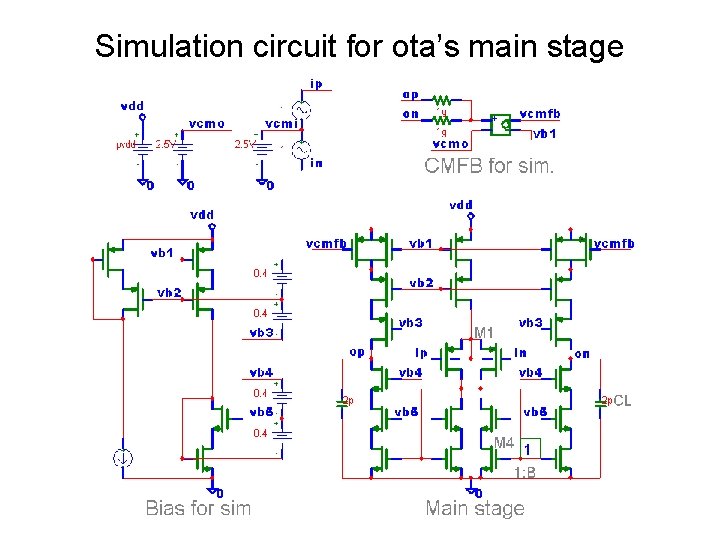

Simulation circuit for ota’s main stage

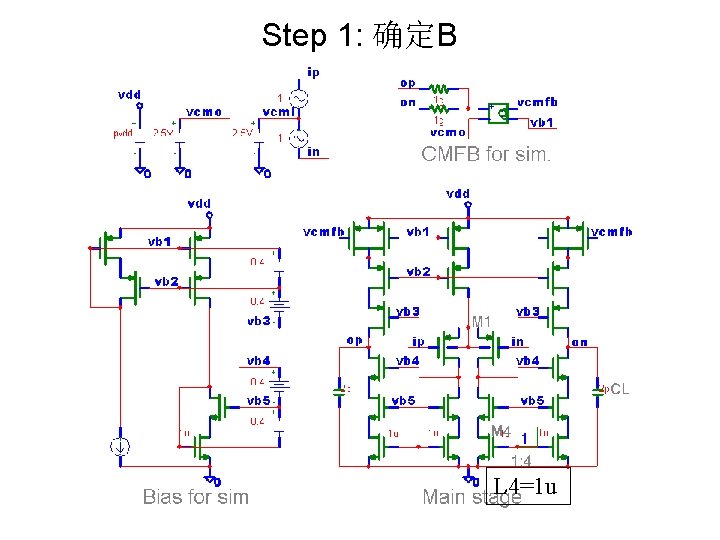

Step 1: 确定B L 4=1 u

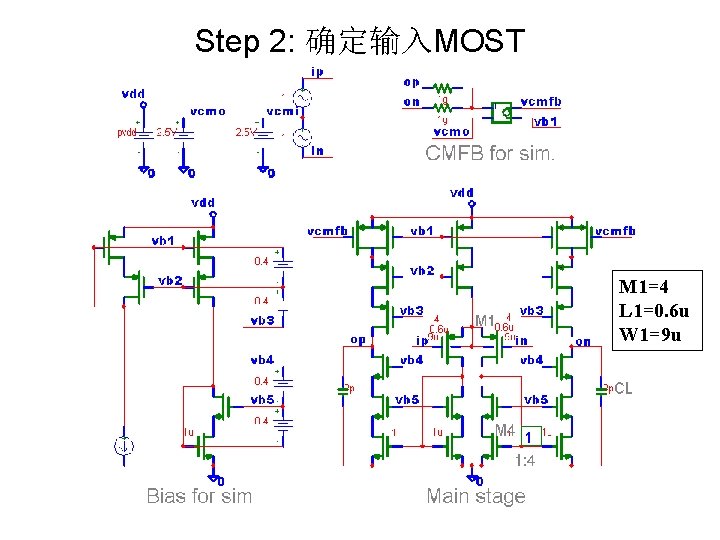

Step 2: 确定输入MOST M 1=4 L 1=0. 6 u W 1=9 u

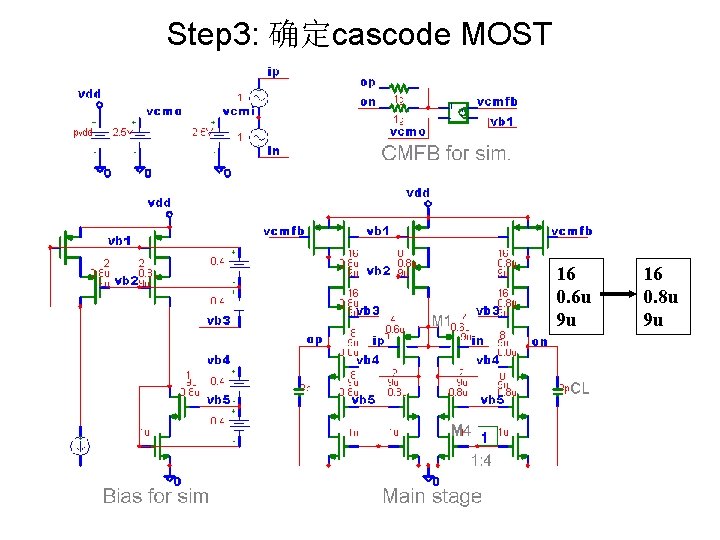

Step 3: 确定cascode MOST 16 0. 6 u 9 u 16 0. 8 u 9 u

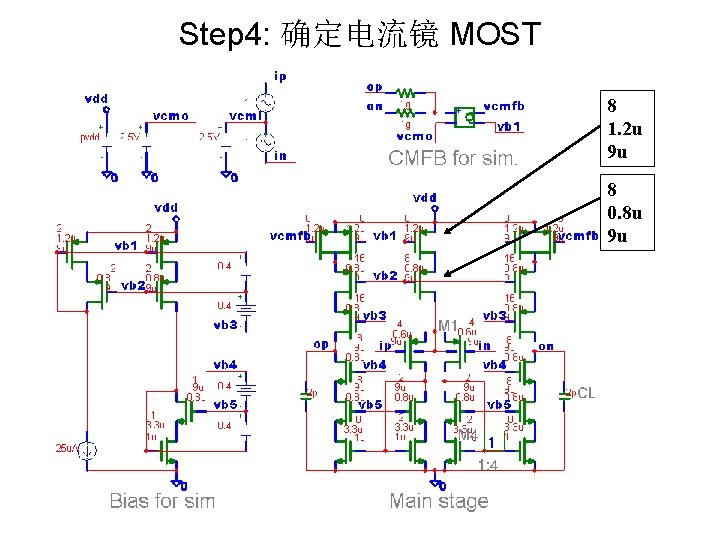

Step 4: 确定电流镜 MOST 8 1. 2 u 9 u 8 0. 8 u 9 u

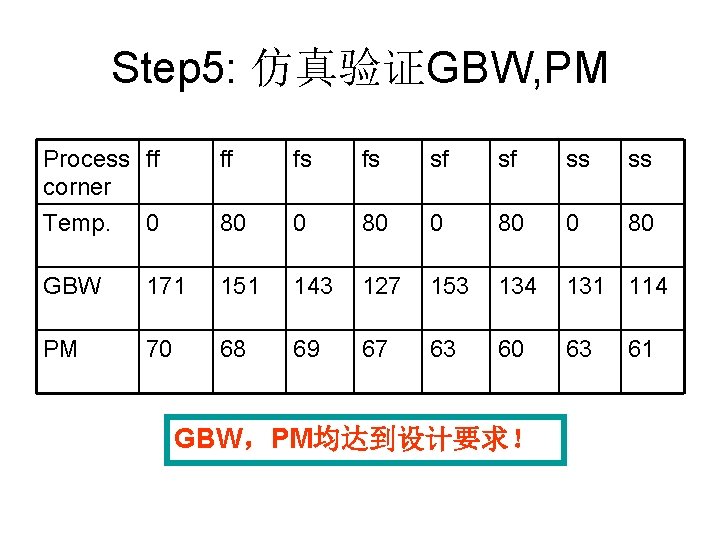

Step 5: 仿真验证GBW, PM Process ff corner ff fs fs sf sf ss ss Temp. 0 80 GBW 171 151 143 127 153 134 131 114 PM 70 68 69 67 63 60 63 GBW,PM均达到设计要求! 61

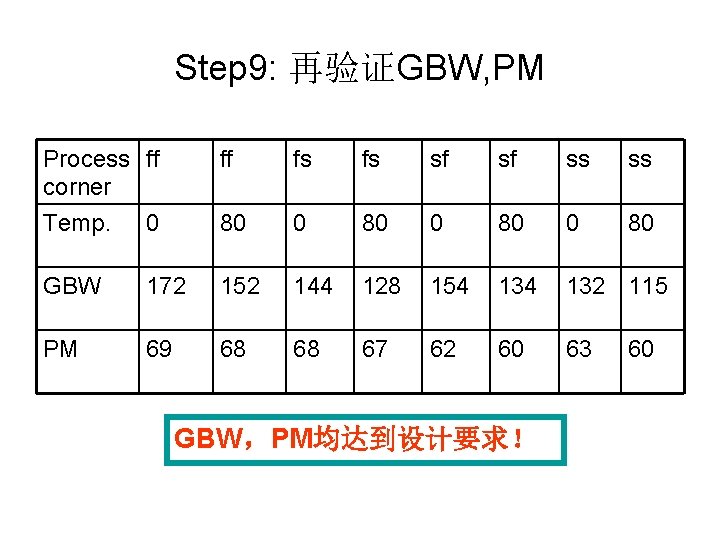

Step 9: 再验证GBW, PM Process ff corner ff fs fs sf sf ss ss Temp. 0 80 GBW 172 152 144 128 154 132 115 PM 69 68 68 67 62 60 63 GBW,PM均达到设计要求! 60

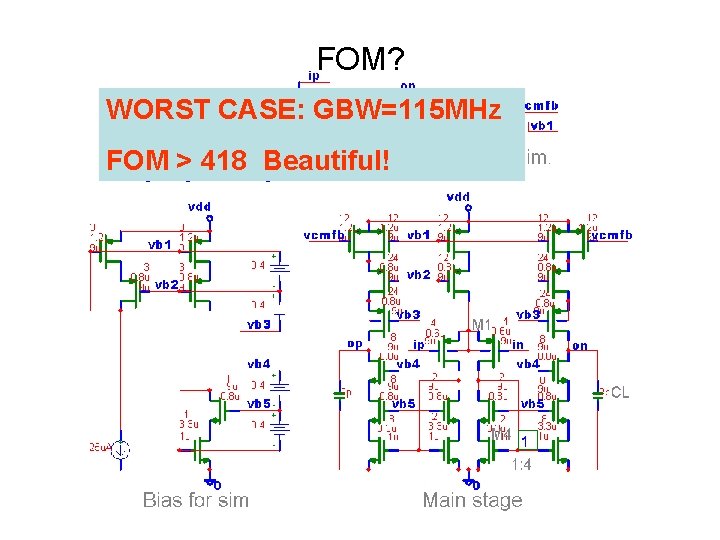

FOM? WORST CASE: GBW=115 MHz FOM > 418 Beautiful!

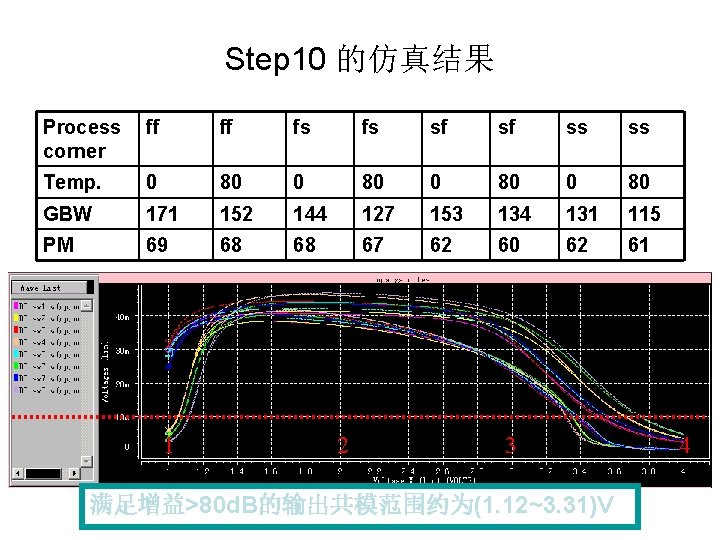

Step 10 的仿真结果 Process corner ff ff fs fs sf sf ss ss Temp. 0 80 GBW 171 152 144 127 153 134 131 115 PM 69 68 68 67 62 60 62 61 1 2 3 满足增益>80 d. B的输出共模范围约为(1. 12~3. 31)V 4

The end

- Slides: 79