VT Novi Sad Elektronika 2 Digitalna elektronika 6

- Slides: 27

VTŠ Novi Sad Elektronika 2 - Digitalna elektronika 6. IMPLEMENTACIJA SEKVENCIJALNE LOGIKE dr Zoran Mitrović

Implementacija sekvencijalne logike z Sekvencijalna kola y Osnovni sekvencijalni elementi y Kombinaciona logika z Modeli za predstavljanje sekvencijalnih kola y Metoda konačnih stanja (Finite-state machines) y Predstavljanje memorije (stanja) y Promene stanja (tranzicije) z Osnovna sekvencijalna kola y Pomerački registri y Brojači z Procedura projektovanja y Dijagrami stanja y Tabela tranzicija y Funkcije sledećeg stanja VTŠ Novi Sad Elektronika 2 - Digitalna elektronika 2

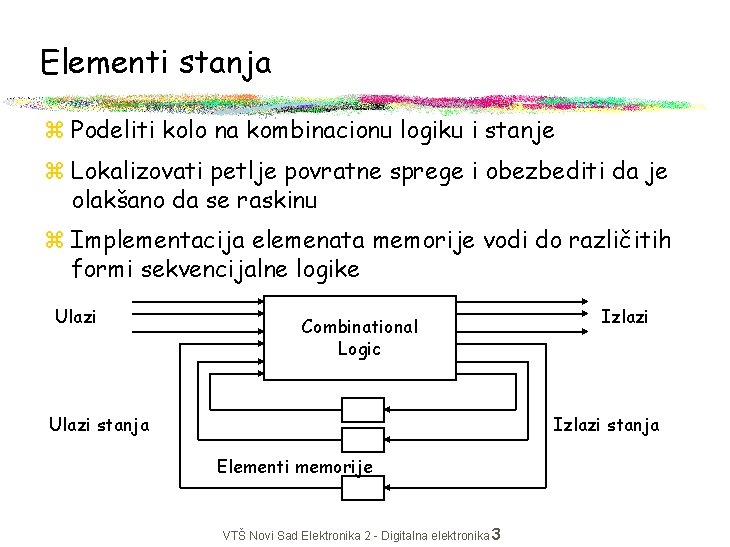

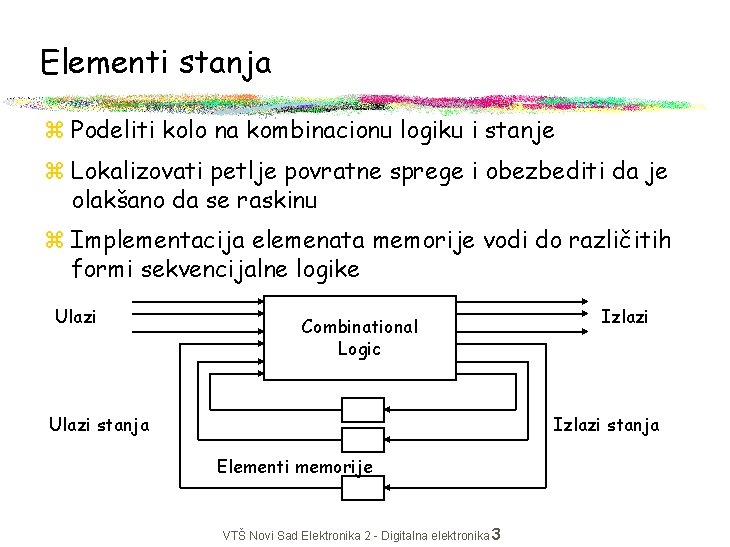

Elementi stanja z Podeliti kolo na kombinacionu logiku i stanje z Lokalizovati petlje povratne sprege i obezbediti da je olakšano da se raskinu z Implementacija elemenata memorije vodi do različitih formi sekvencijalne logike Ulazi Combinational Logic Ulazi stanja Izlazi stanja Elementi memorije VTŠ Novi Sad Elektronika 2 - Digitalna elektronika 3

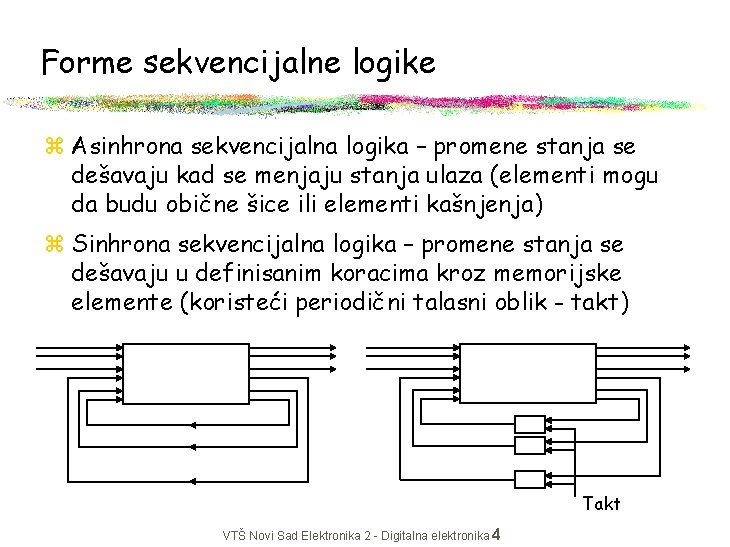

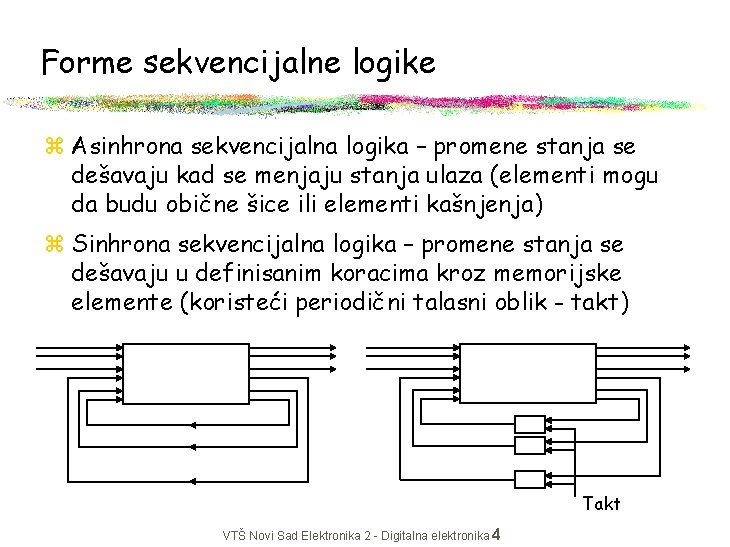

Forme sekvencijalne logike z Asinhrona sekvencijalna logika – promene stanja se dešavaju kad se menjaju stanja ulaza (elementi mogu da budu obične šice ili elementi kašnjenja) z Sinhrona sekvencijalna logika – promene stanja se dešavaju u definisanim koracima kroz memorijske elemente (koristeći periodični talasni oblik - takt) Takt VTŠ Novi Sad Elektronika 2 - Digitalna elektronika 4

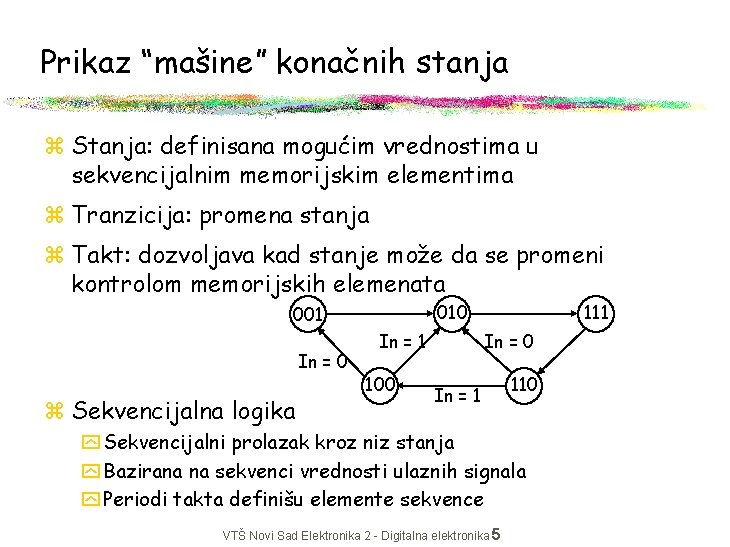

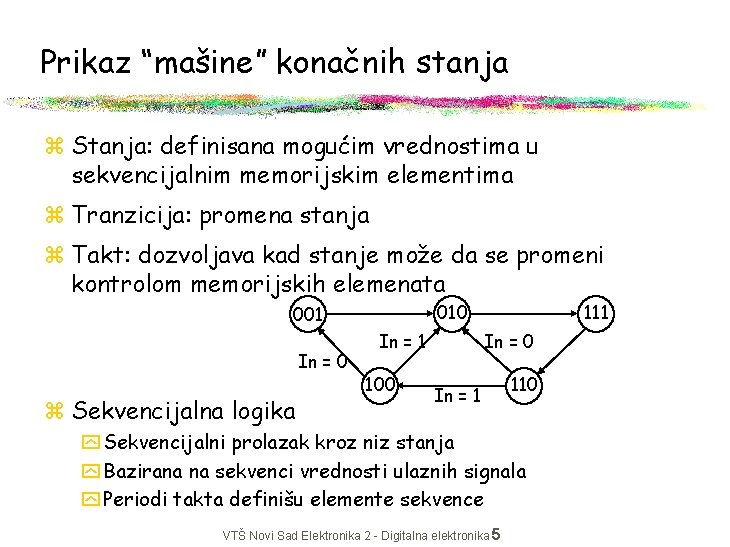

Prikaz “mašine” konačnih stanja z Stanja: definisana mogućim vrednostima u sekvencijalnim memorijskim elementima z Tranzicija: promena stanja z Takt: dozvoljava kad stanje može da se promeni kontrolom memorijskih elemenata 010 001 In = 0 z Sekvencijalna logika In = 1 100 111 In = 0 In = 1 110 y Sekvencijalni prolazak kroz niz stanja y Bazirana na sekvenci vrednosti ulaznih signala y Periodi takta definišu elemente sekvence VTŠ Novi Sad Elektronika 2 - Digitalna elektronika 5

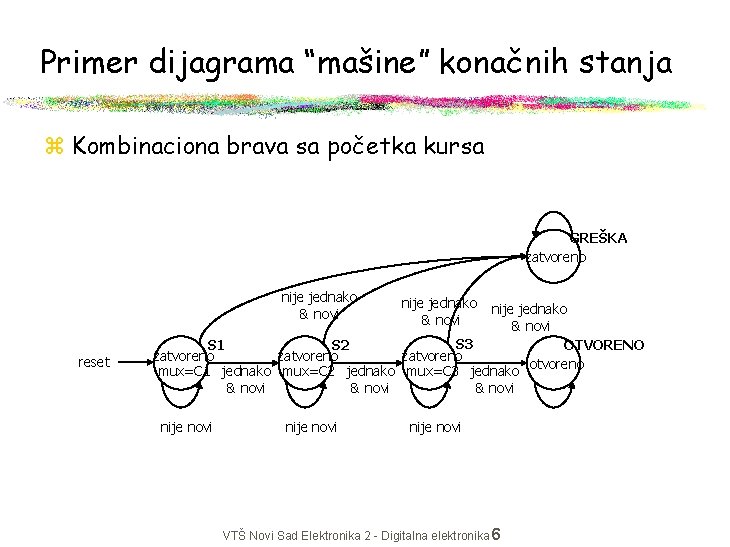

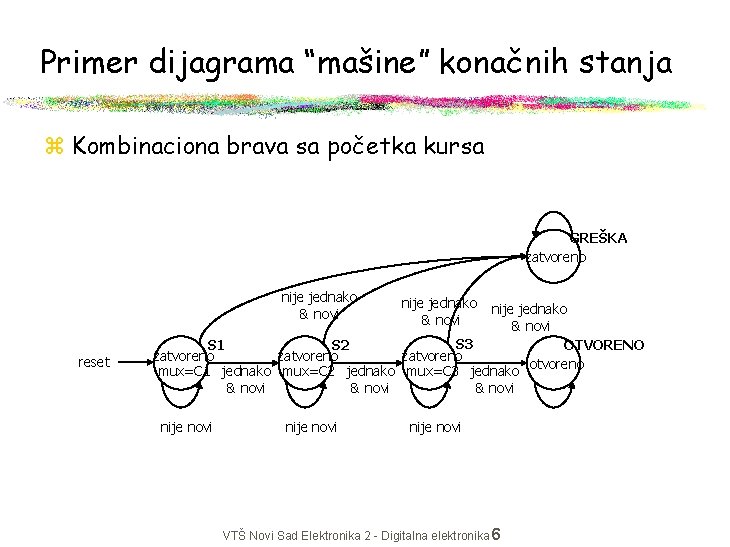

Primer dijagrama “mašine” konačnih stanja z Kombinaciona brava sa početka kursa GREŠKA zatvoreno nije jednako & novi reset nije jednako & novi S 3 S 1 S 2 OTVORENO zatvoreno otvoreno mux=C 1 jednako mux=C 2 jednako mux=C 3 jednako & novi nije novi VTŠ Novi Sad Elektronika 2 - Digitalna elektronika 6

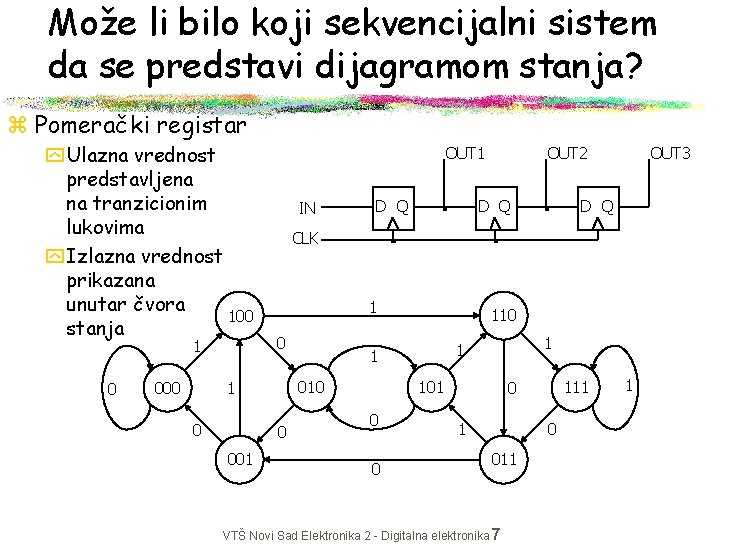

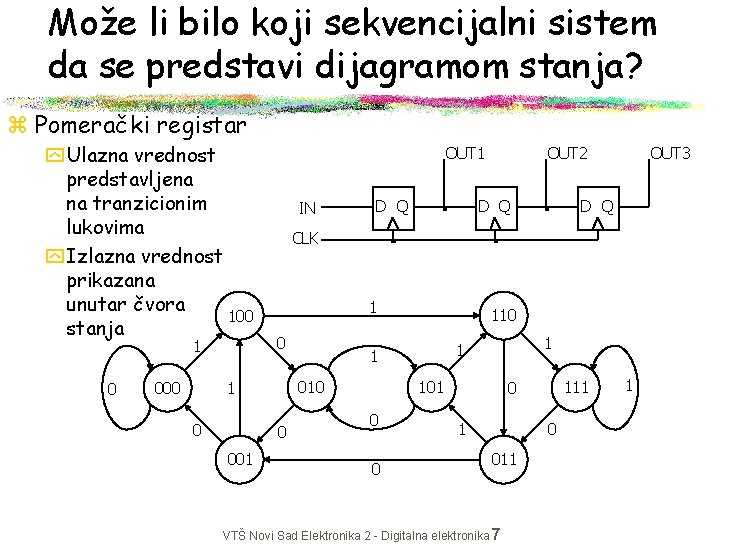

Može li bilo koji sekvencijalni sistem da se predstavi dijagramom stanja? z Pomerački registar y Ulazna vrednost predstavljena na tranzicionim lukovima y Izlazna vrednost prikazana unutar čvora 100 stanja 1 0 OUT 1 IN 0 1 0 D Q 110 1 1 1 010 0 001 D Q OUT 3 CLK 1 000 D Q OUT 2 101 0 0 111 0 011 VTŠ Novi Sad Elektronika 2 - Digitalna elektronika 7 1

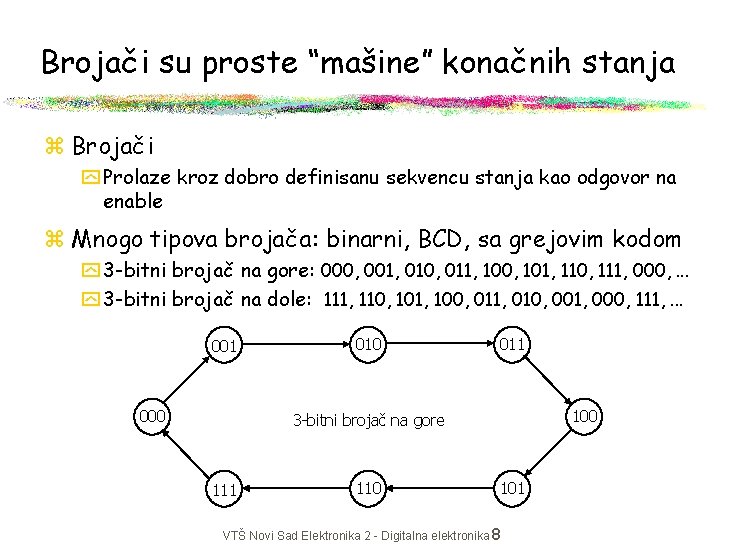

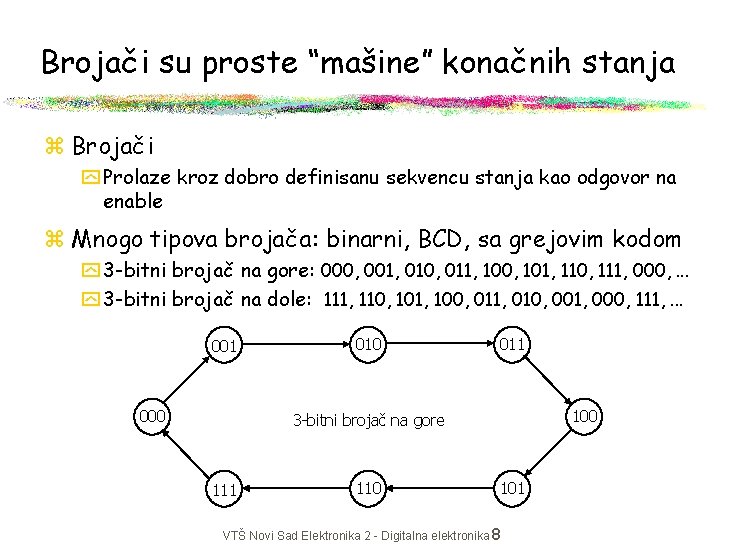

Brojači su proste “mašine” konačnih stanja z Brojači y Prolaze kroz dobro definisanu sekvencu stanja kao odgovor na enable z Mnogo tipova brojača: binarni, BCD, sa grejovim kodom y 3 -bitni brojač na gore: 000, 001, 010, 011, 100, 101, 110, 111, 000, . . . y 3 -bitni brojač na dole: 111, 110, 101, 100, 011, 010, 001, 000, 111, . . . 001 000 011 100 3 -bitni brojač na gore 111 110 101 VTŠ Novi Sad Elektronika 2 - Digitalna elektronika 8

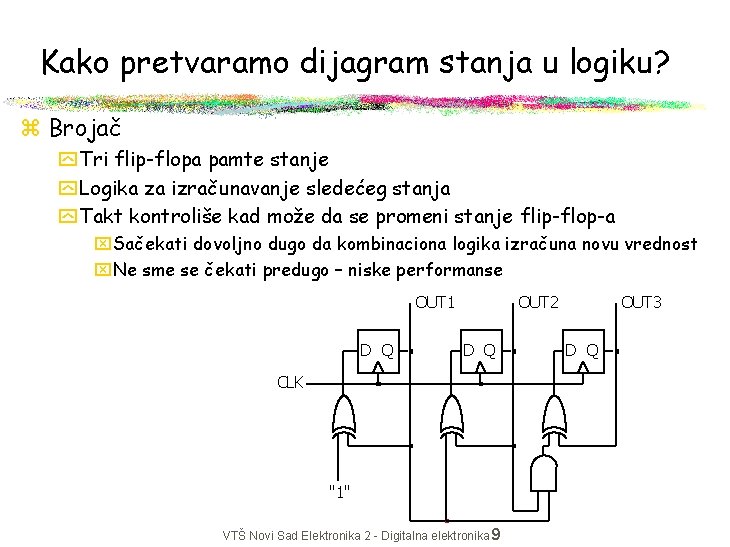

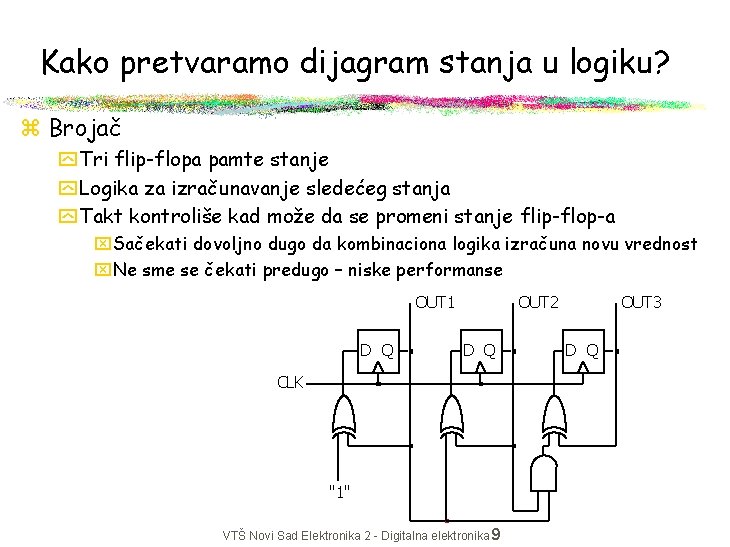

Kako pretvaramo dijagram stanja u logiku? z Brojač y Tri flip-flopa pamte stanje y Logika za izračunavanje sledećeg stanja y Takt kontroliše kad može da se promeni stanje flip-flop-a x. Sačekati dovoljno dugo da kombinaciona logika izračuna novu vrednost x. Ne sme se čekati predugo – niske performanse OUT 1 D Q OUT 2 D Q CLK "1" VTŠ Novi Sad Elektronika 2 - Digitalna elektronika 9 OUT 3 D Q

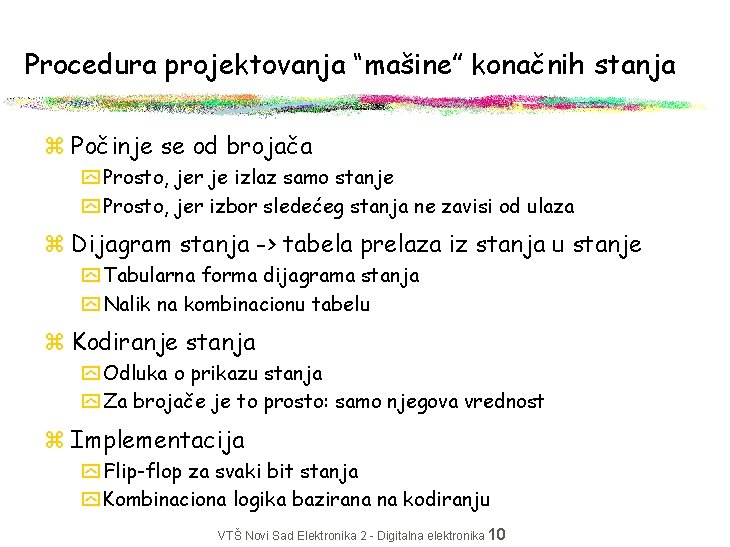

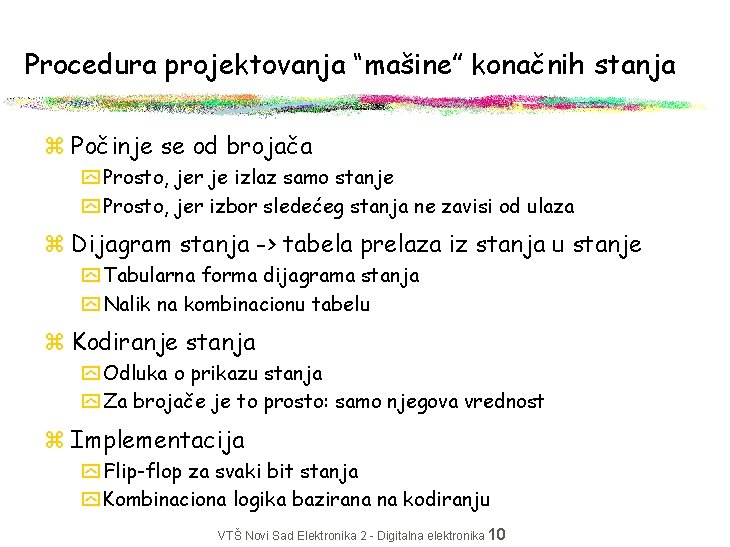

Procedura projektovanja “mašine” konačnih stanja z Počinje se od brojača y Prosto, jer je izlaz samo stanje y Prosto, jer izbor sledećeg stanja ne zavisi od ulaza z Dijagram stanja -> tabela prelaza iz stanja u stanje y Tabularna forma dijagrama stanja y Nalik na kombinacionu tabelu z Kodiranje stanja y Odluka o prikazu stanja y Za brojače je to prosto: samo njegova vrednost z Implementacija y Flip-flop za svaki bit stanja y Kombinaciona logika bazirana na kodiranju VTŠ Novi Sad Elektronika 2 - Digitalna elektronika 10

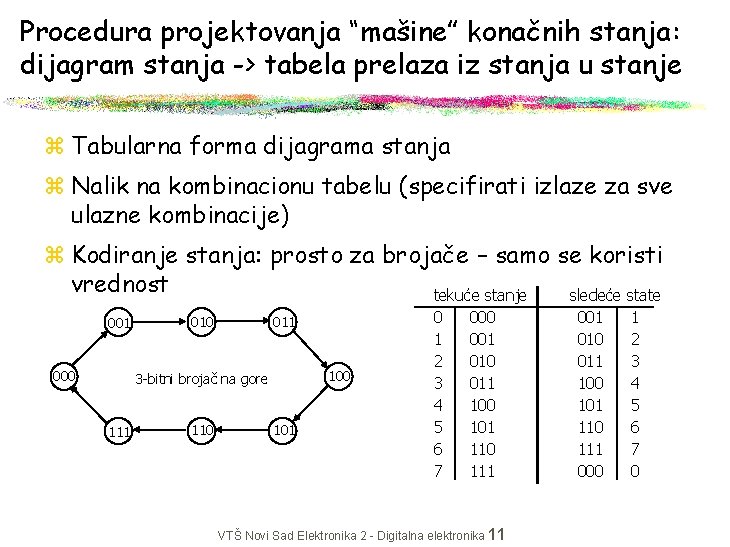

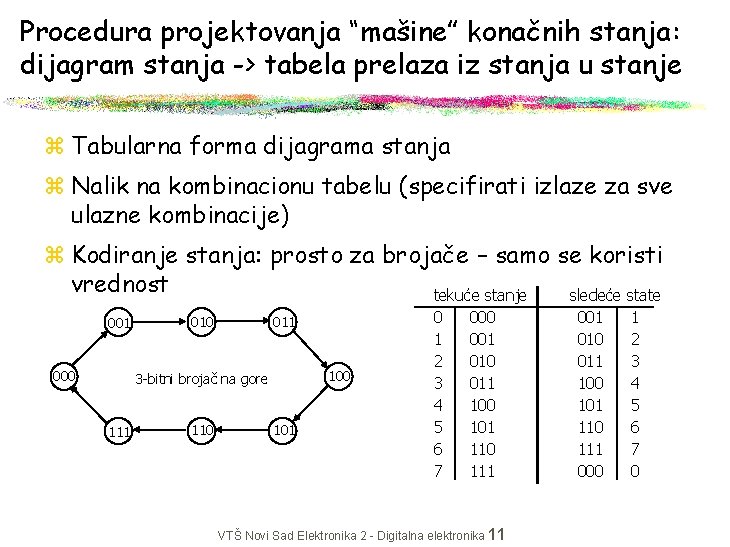

Procedura projektovanja “mašine” konačnih stanja: dijagram stanja -> tabela prelaza iz stanja u stanje z Tabularna forma dijagrama stanja z Nalik na kombinacionu tabelu (specifirati izlaze za sve ulazne kombinacije) z Kodiranje stanja: prosto za brojače – samo se koristi vrednost tekuće stanje sledeće state 001 000 011 100 3 -bitni brojač na gore 111 110 101 0 1 2 3 4 5 6 7 000 001 010 011 100 101 110 111 VTŠ Novi Sad Elektronika 2 - Digitalna elektronika 11 001 010 011 100 101 110 111 000 1 2 3 4 5 6 7 0

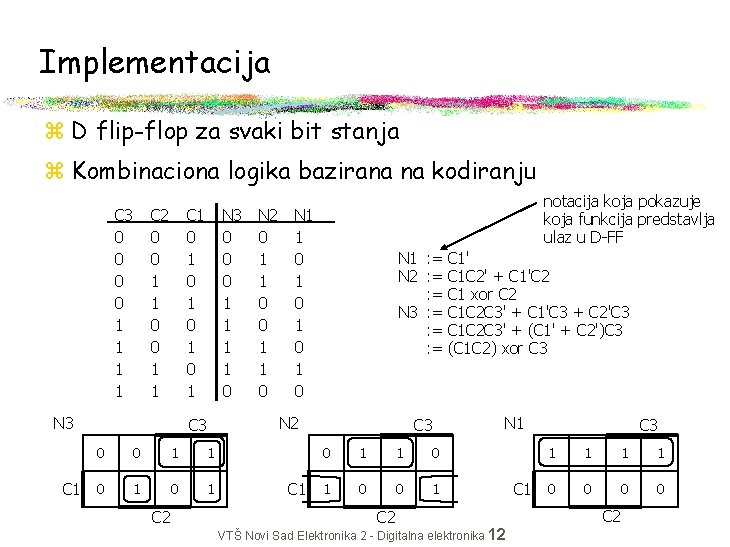

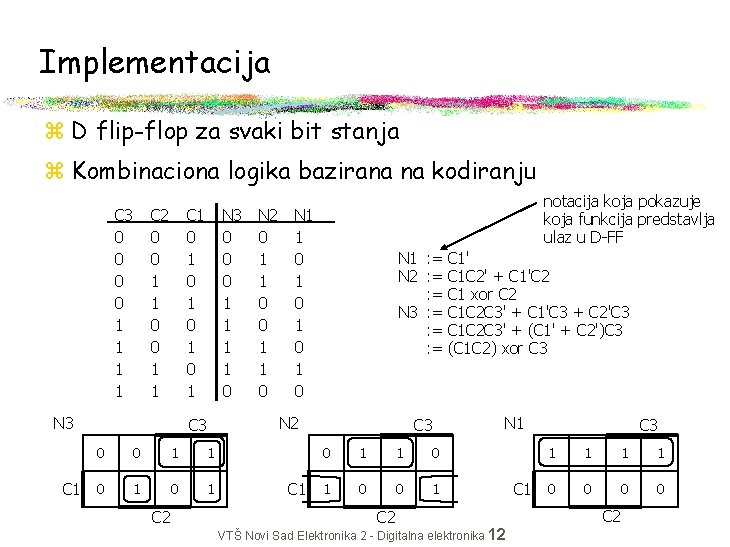

Implementacija z D flip-flop za svaki bit stanja z Kombinaciona logika bazirana na kodiranju C 3 0 0 1 1 C 2 0 0 1 1 C 1 0 1 0 1 N 3 C 1 N 3 0 0 0 1 1 0 C 3 0 0 1 1 0 1 C 2 N 2 0 1 1 0 notacija koja pokazuje koja funkcija predstavlja ulaz u D-FF N 1 1 0 1 0 N 1 : = C 1' N 2 : = C 1 C 2' + C 1'C 2 : = C 1 xor C 2 N 3 : = C 1 C 2 C 3' + C 1'C 3 + C 2'C 3 : = C 1 C 2 C 3' + (C 1' + C 2')C 3 : = (C 1 C 2) xor C 3 N 2 C 1 C 3 0 1 1 0 0 1 C 2 N 1 VTŠ Novi Sad Elektronika 2 - Digitalna elektronika 12 C 1 C 3 1 1 0 0 C 2

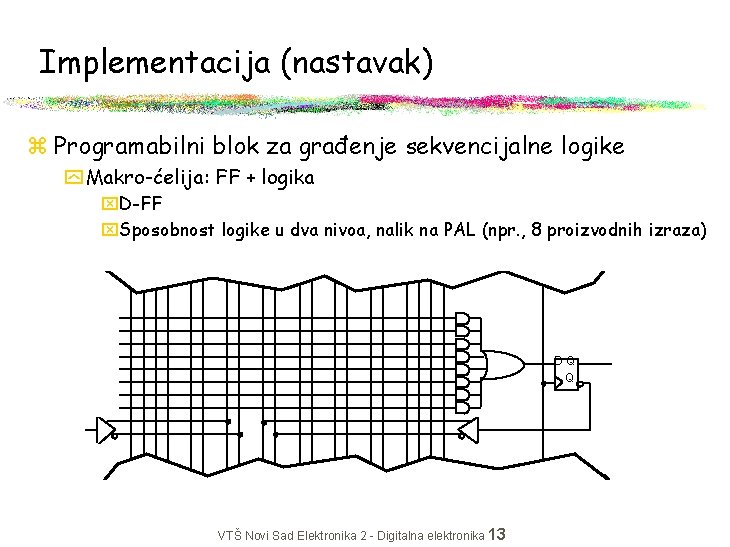

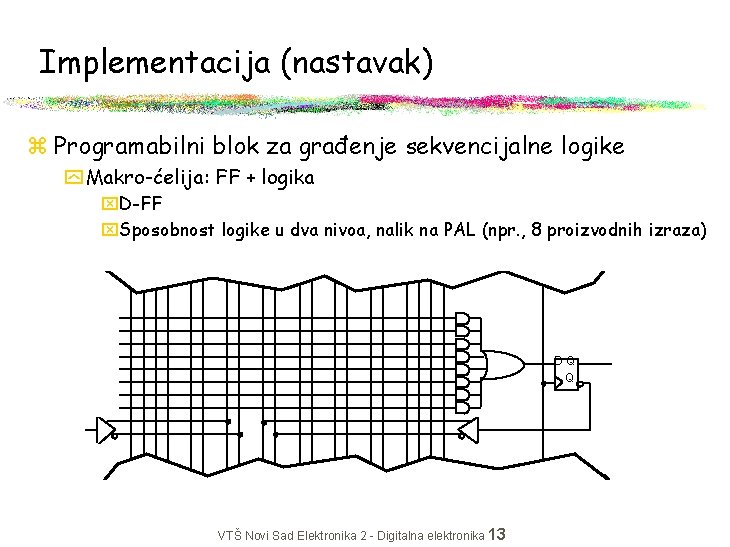

Implementacija (nastavak) z Programabilni blok za građenje sekvencijalne logike y Makro-ćelija: FF + logika x. D-FF x. Sposobnost logike u dva nivoa, nalik na PAL (npr. , 8 proizvodnih izraza) DQ Q VTŠ Novi Sad Elektronika 2 - Digitalna elektronika 13

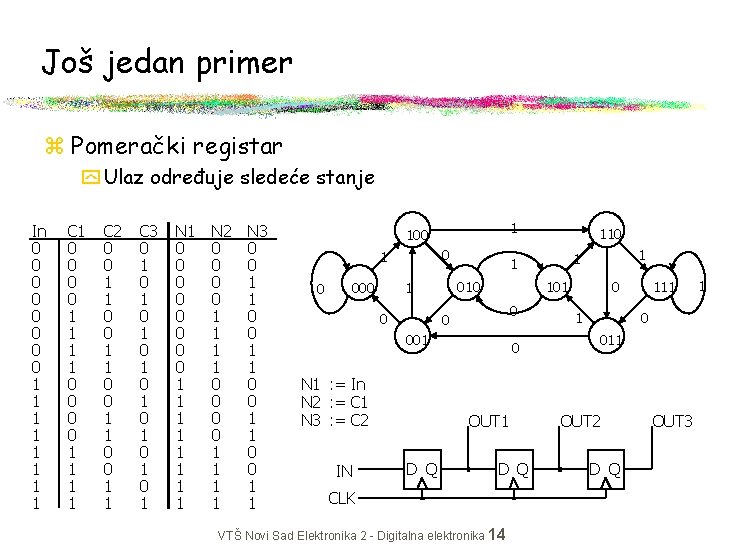

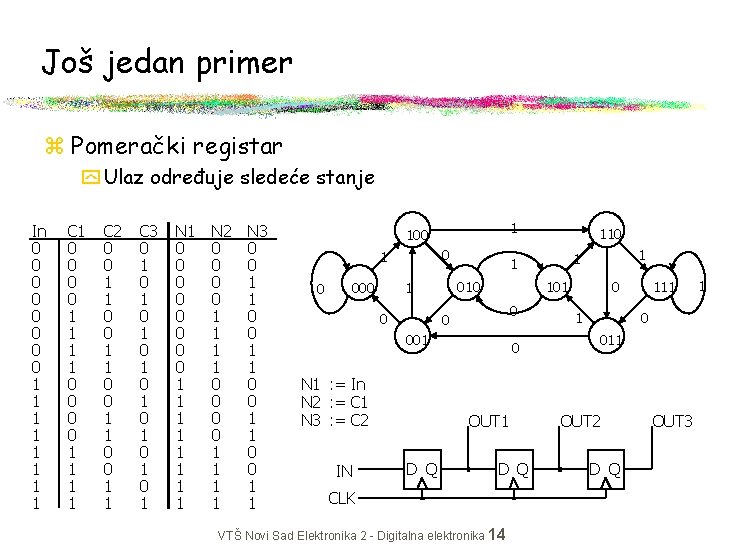

Još jedan primer z Pomerački registar y Ulaz određuje sledeće stanje In 0 0 0 0 1 1 1 1 C 1 0 0 0 0 1 1 1 1 C 2 0 0 1 1 C 3 0 1 0 1 N 1 0 0 0 0 1 1 1 1 N 2 0 0 0 0 1 1 1 1 N 3 0 0 1 1 1 100 0 101 0 0 001 N 1 : = In N 2 : = C 1 N 3 : = C 2 IN 0 OUT 1 D Q 1 1 1 010 1 000 110 D Q CLK VTŠ Novi Sad Elektronika 2 - Digitalna elektronika 14 111 0 011 OUT 2 D Q OUT 3 1

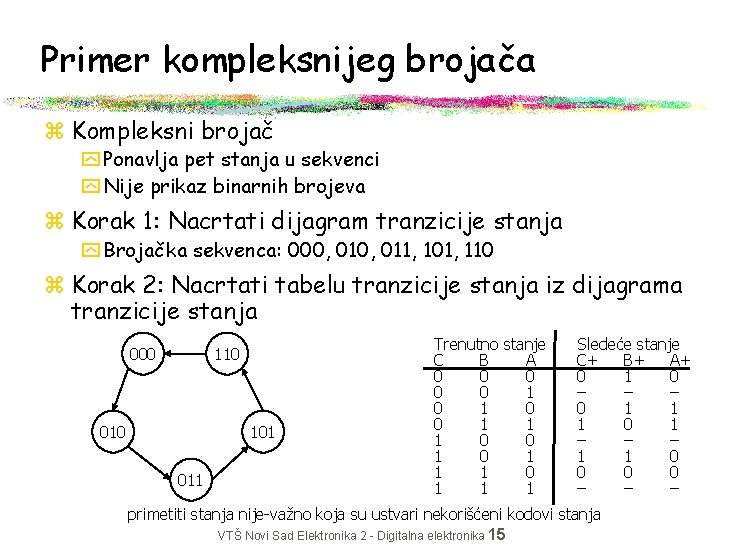

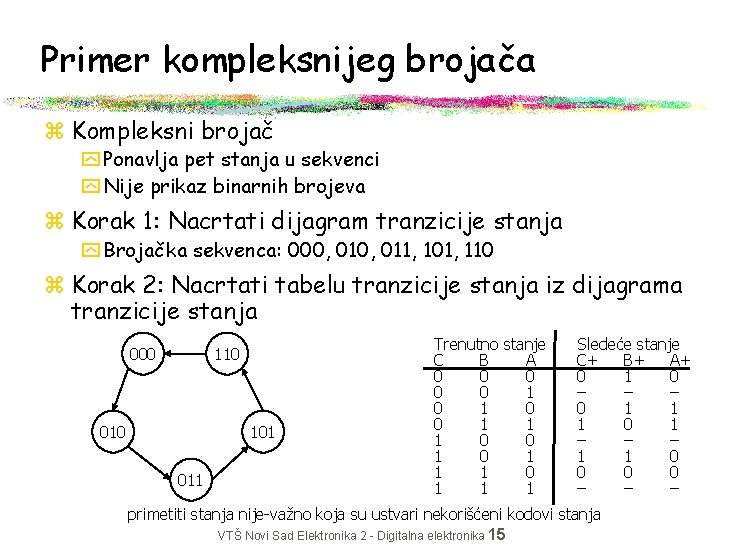

Primer kompleksnijeg brojača z Kompleksni brojač y Ponavlja pet stanja u sekvenci y Nije prikaz binarnih brojeva z Korak 1: Nacrtati dijagram tranzicije stanja y Brojačka sekvenca: 000, 011, 101, 110 z Korak 2: Nacrtati tabelu tranzicije stanja iz dijagrama tranzicije stanja 000 110 010 101 011 Trenutno stanje C B A 0 0 0 1 1 1 0 0 1 1 1 Sledeće stanje C+ B+ A+ 0 1 0 – – – 0 1 1 1 0 1 – – – 1 1 0 0 – – – primetiti stanja nije-važno koja su ustvari nekorišćeni kodovi stanja VTŠ Novi Sad Elektronika 2 - Digitalna elektronika 15

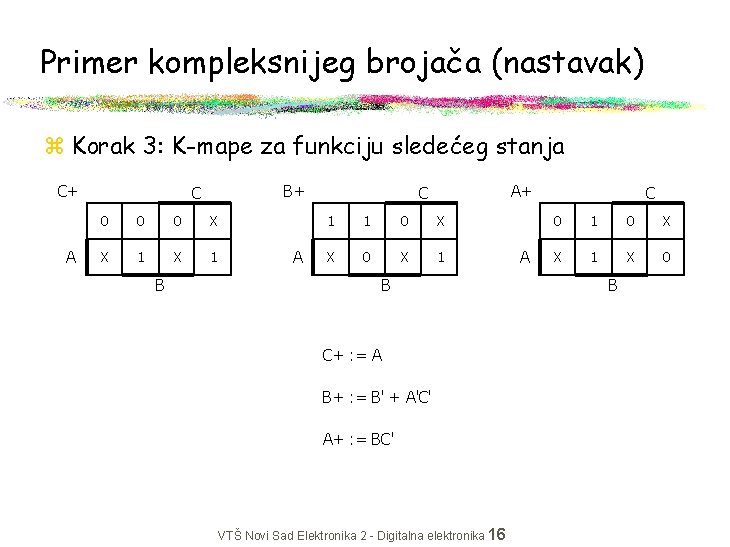

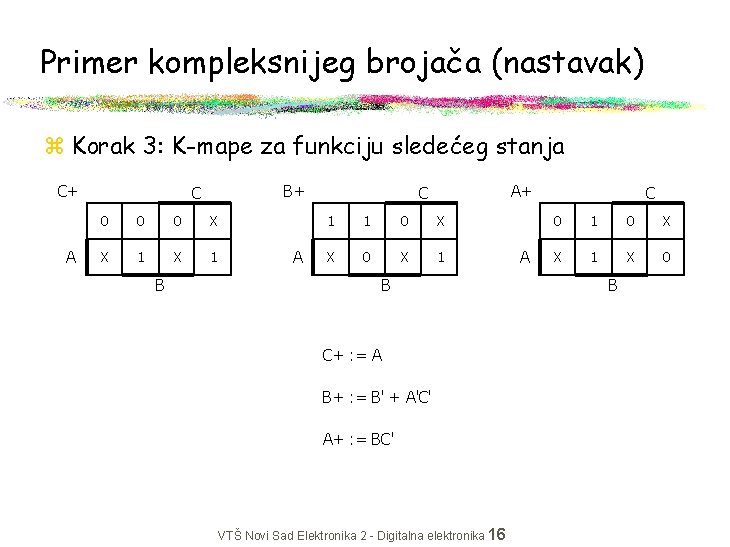

Primer kompleksnijeg brojača (nastavak) z Korak 3: K-mape za funkciju sledećeg stanja C+ A B+ C 0 0 0 X X 1 A A+ C 1 1 0 X X 0 X 1 B B C+ : = A B+ : = B' + A'C' A+ : = BC' VTŠ Novi Sad Elektronika 2 - Digitalna elektronika 16 A C 0 1 0 X X 1 X 0 B

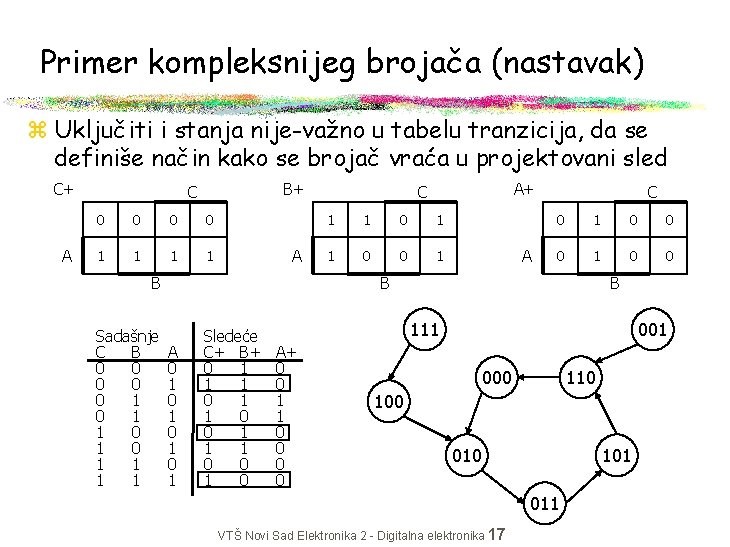

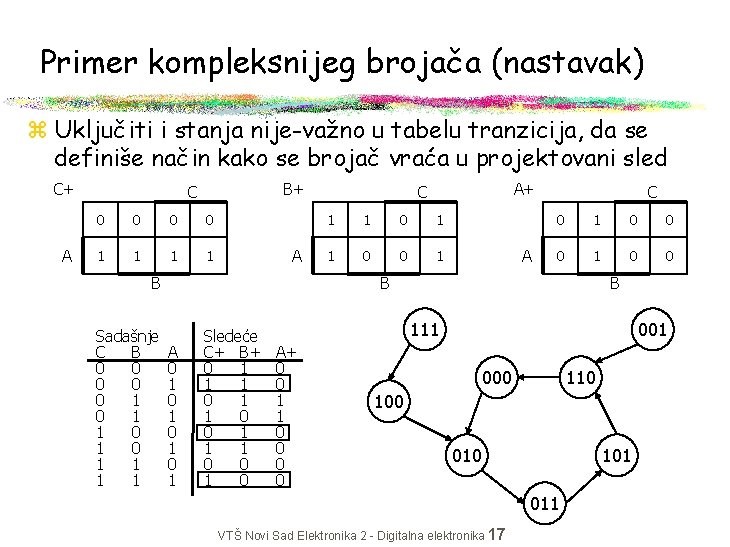

Primer kompleksnijeg brojača (nastavak) z Uključiti i stanja nije-važno u tabelu tranzicija, da se definiše način kako se brojač vraća u projektovani sled C+ A B+ C 0 0 1 1 A 1 1 0 0 1 A C 0 1 0 0 B B Sadašnje C B 0 0 0 1 0 1 1 1 1 A+ C A 0 1 0 1 Sledeće C+ B+ 0 1 1 1 0 0 1 0 B 111 A+ 0 0 1 1 0 0 001 000 110 100 010 101 011 VTŠ Novi Sad Elektronika 2 - Digitalna elektronika 17

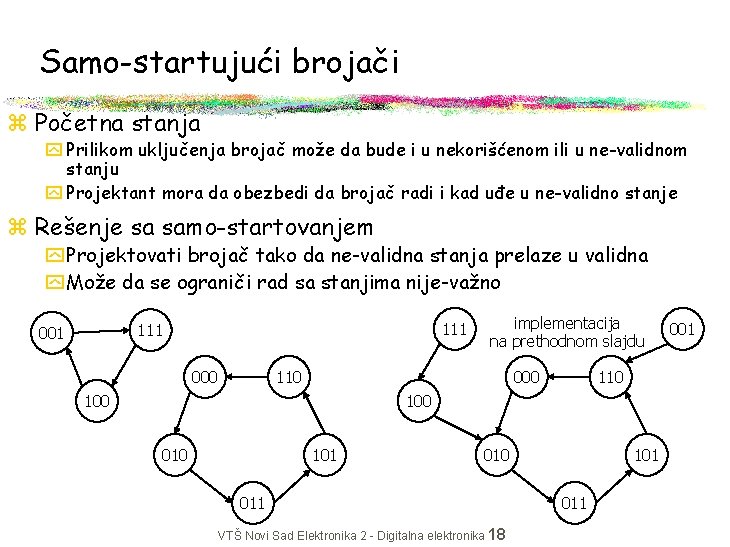

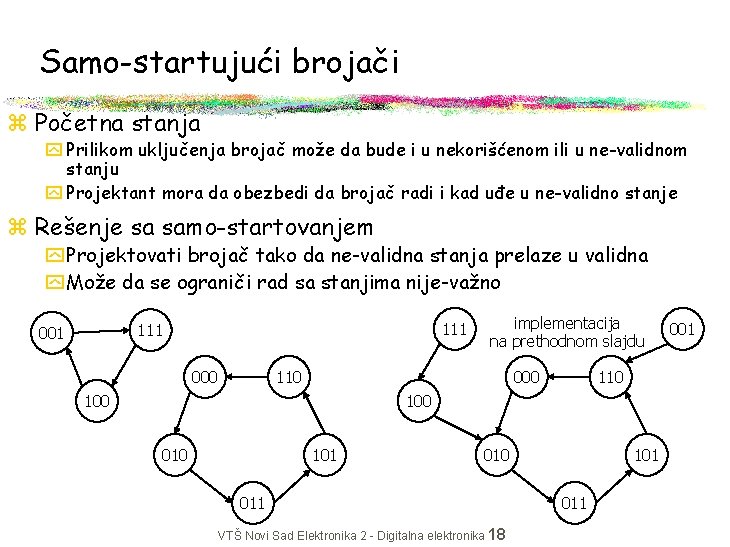

Samo-startujući brojači z Početna stanja y Prilikom uključenja brojač može da bude i u nekorišćenom ili u ne-validnom stanju y Projektant mora da obezbedi da brojač radi i kad uđe u ne-validno stanje z Rešenje sa samo-startovanjem y Projektovati brojač tako da ne-validna stanja prelaze u validna y Može da se ograniči rad sa stanjima nije-važno 111 001 000 implementacija na prethodnom slajdu 000 110 100 010 101 010 011 VTŠ Novi Sad Elektronika 2 - Digitalna elektronika 18 101 011 001

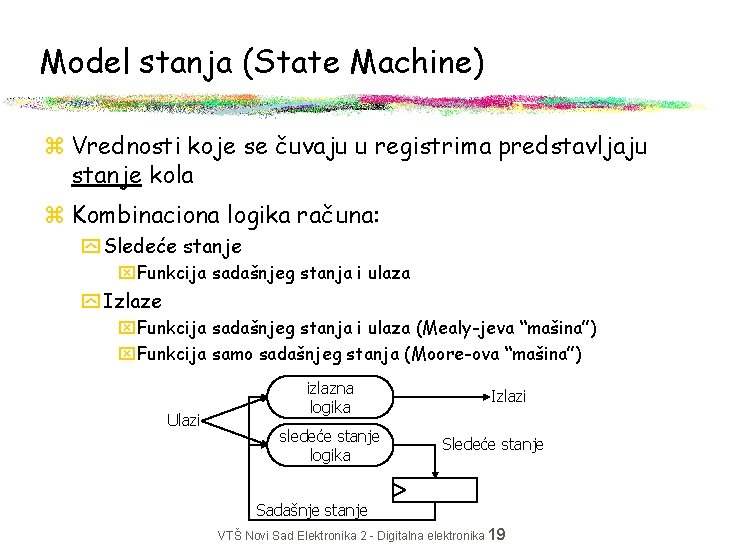

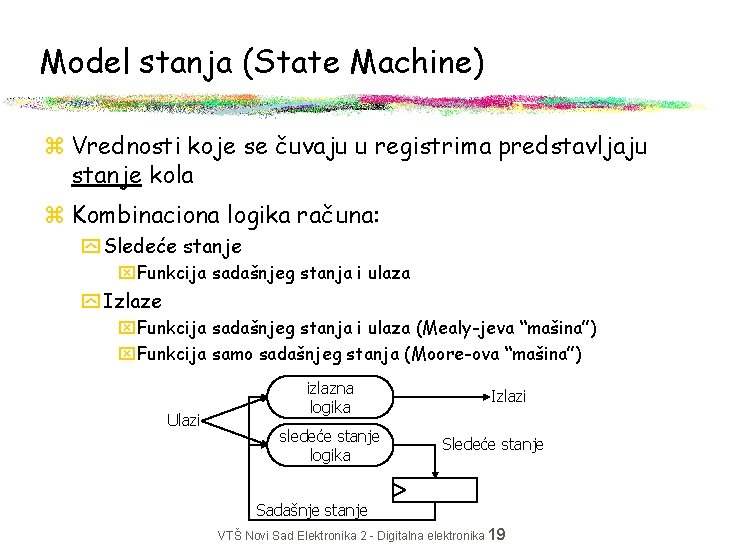

Model stanja (State Machine) z Vrednosti koje se čuvaju u registrima predstavljaju stanje kola z Kombinaciona logika računa: y Sledeće stanje x. Funkcija sadašnjeg stanja i ulaza y Izlaze x. Funkcija sadašnjeg stanja i ulaza (Mealy-jeva “mašina”) x. Funkcija samo sadašnjeg stanja (Moore-ova “mašina”) Ulazi izlazna logika sledeće stanje logika Izlazi Sledeće stanje Sadašnje stanje VTŠ Novi Sad Elektronika 2 - Digitalna elektronika 19

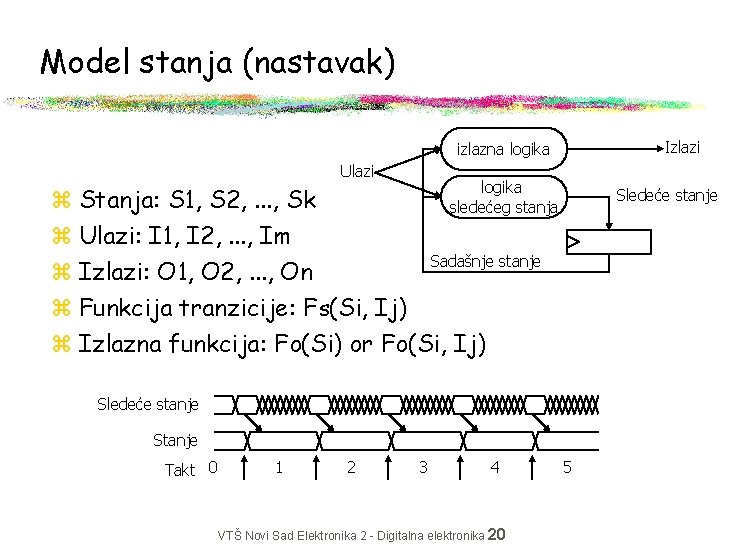

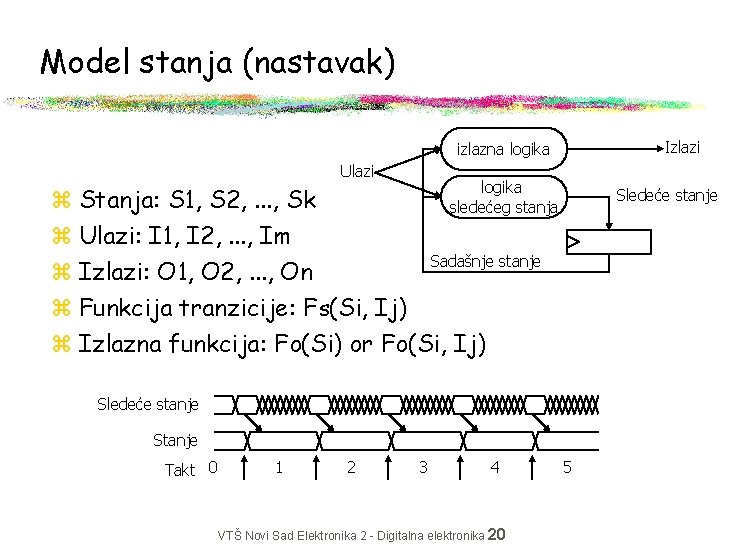

Model stanja (nastavak) Izlazi izlazna logika Ulazi logika sledećeg stanja z Stanja: S 1, S 2, . . . , Sk z Ulazi: I 1, I 2, . . . , Im Sadašnje stanje z Izlazi: O 1, O 2, . . . , On z Funkcija tranzicije: Fs(Si, Ij) z Izlazna funkcija: Fo(Si) or Fo(Si, Ij) Sledeće stanje Stanje Takt 0 1 2 3 4 VTŠ Novi Sad Elektronika 2 - Digitalna elektronika 20 5

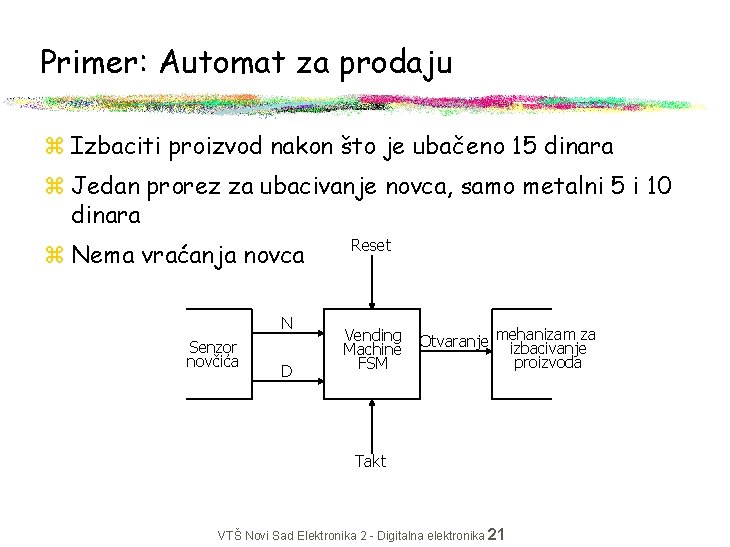

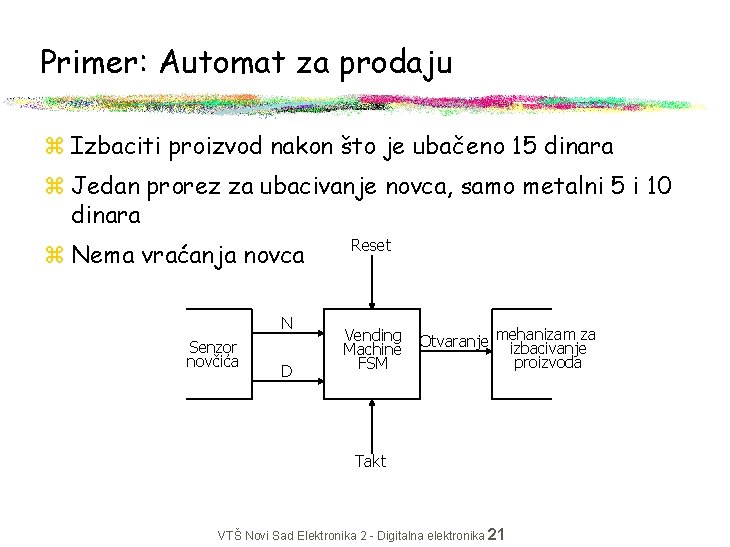

Primer: Automat za prodaju z Izbaciti proizvod nakon što je ubačeno 15 dinara z Jedan prorez za ubacivanje novca, samo metalni 5 i 10 dinara z Nema vraćanja novca N Senzor novčića D Reset Vending Machine FSM za Otvaranje mehanizam izbacivanje proizvoda Takt VTŠ Novi Sad Elektronika 2 - Digitalna elektronika 21

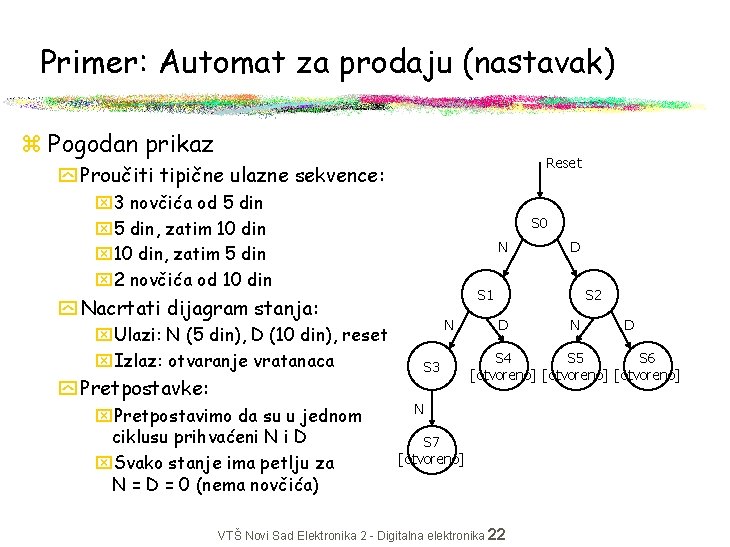

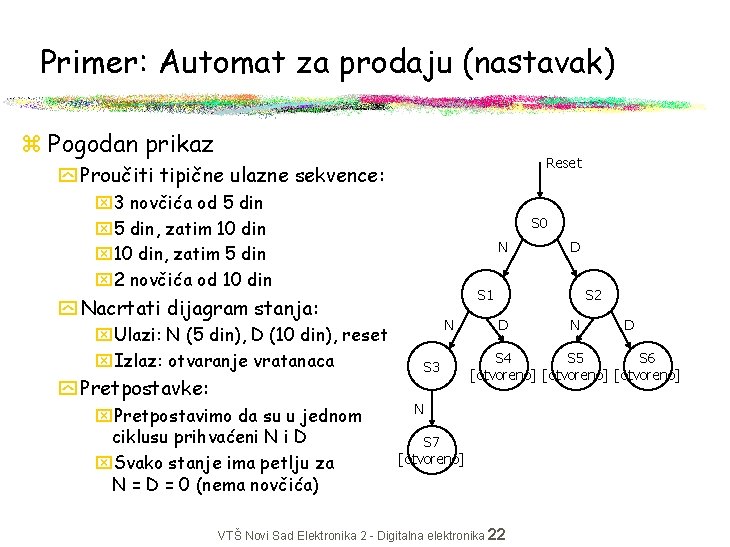

Primer: Automat za prodaju (nastavak) z Pogodan prikaz Reset y Proučiti tipične ulazne sekvence: x 3 novčića od 5 din x 5 din, zatim 10 din x 10 din, zatim 5 din x 2 novčića od 10 din S 0 N S 1 y Nacrtati dijagram stanja: x. Ulazi: N (5 din), D (10 din), reset x. Izlaz: otvaranje vratanaca y Pretpostavke: x. Pretpostavimo da su u jednom ciklusu prihvaćeni N i D x. Svako stanje ima petlju za N = D = 0 (nema novčića) D N S 3 S 2 D N D S 4 S 5 S 6 [otvoreno] N S 7 [otvoreno] VTŠ Novi Sad Elektronika 2 - Digitalna elektronika 22

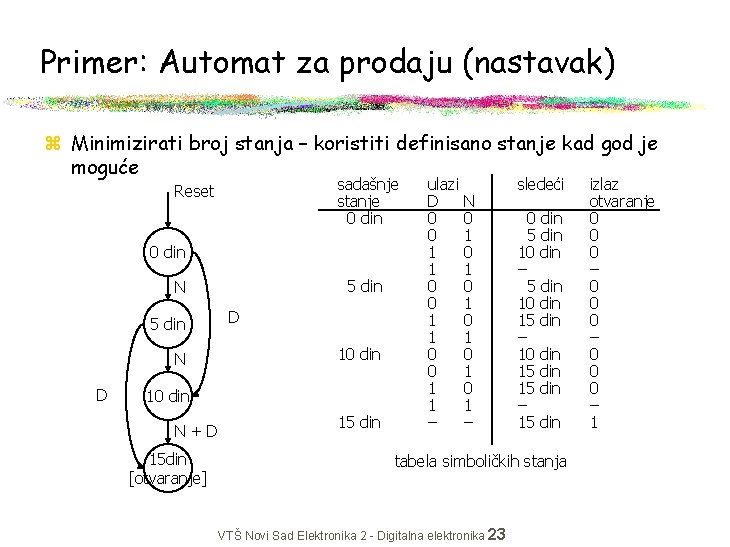

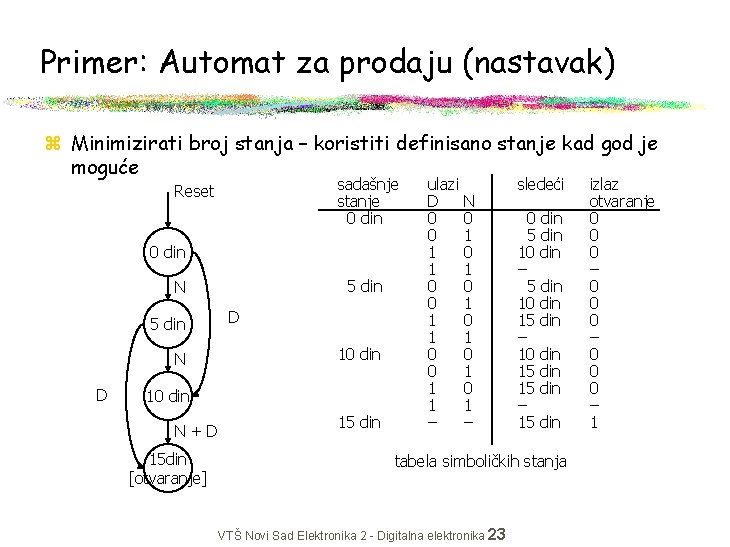

Primer: Automat za prodaju (nastavak) z Minimizirati broj stanja – koristiti definisano stanje kad god je moguće sadašnje stanje 0 din Reset 0 din 5 din N D D 10 din N+D 15 din [otvaranje] 15 din ulazi D N 0 0 0 1 1 0 0 0 1 1 – – sledeći 0 din 5 din 10 din – 5 din 10 din 15 din – 15 din tabela simboličkih stanja VTŠ Novi Sad Elektronika 2 - Digitalna elektronika 23 izlaz otvaranje 0 0 0 – 1

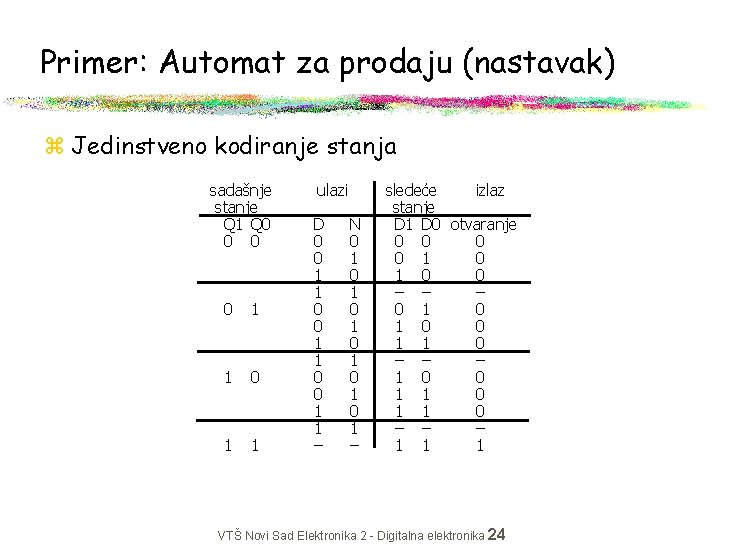

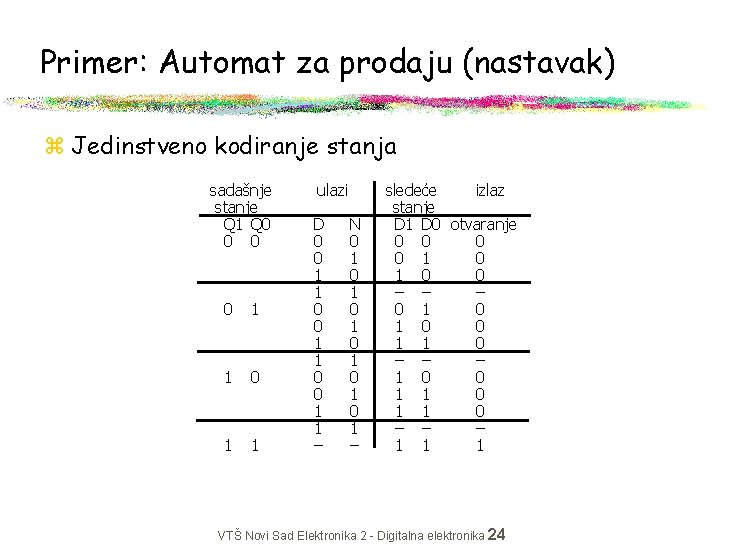

Primer: Automat za prodaju (nastavak) z Jedinstveno kodiranje stanja sadašnje stanje Q 1 Q 0 0 1 1 ulazi D 0 0 1 1 – N 0 1 0 1 0 1 – sledeće izlaz stanje D 1 D 0 otvaranje 0 0 1 0 0 – – – 0 1 0 0 1 1 0 – – – 1 1 1 VTŠ Novi Sad Elektronika 2 - Digitalna elektronika 24

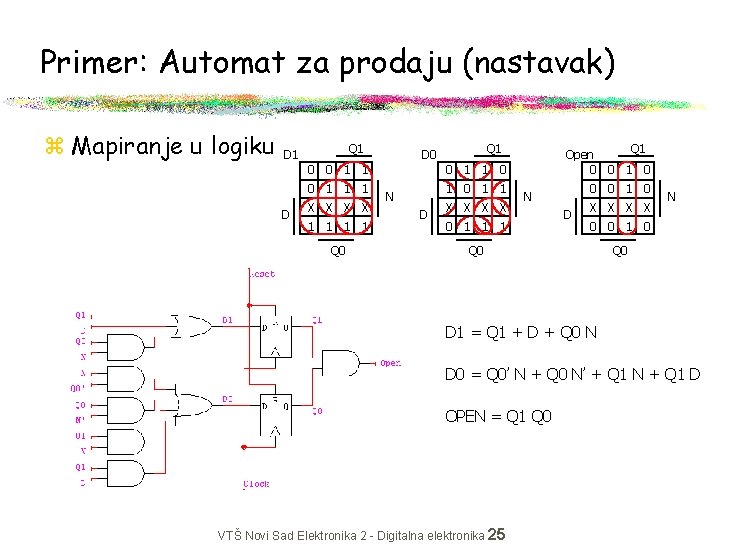

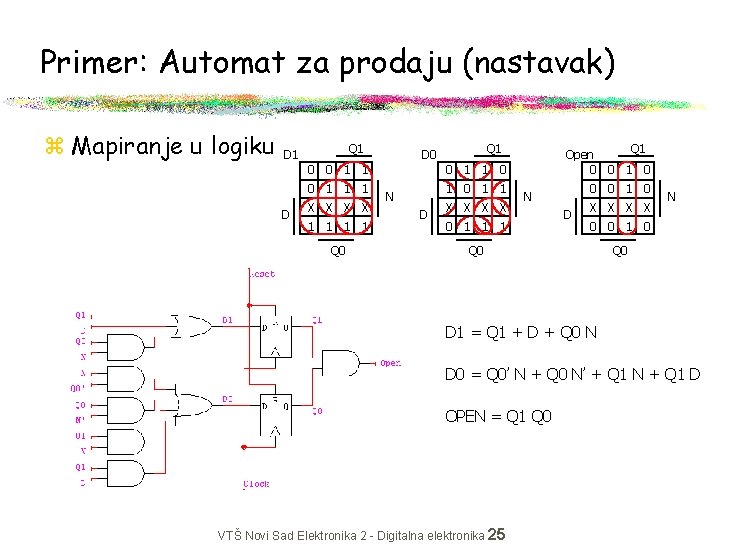

Primer: Automat za prodaju (nastavak) z Mapiranje u logiku Q 1 D 1 0 0 1 1 1 D X X 1 1 Q 0 Q 1 D 0 Q 1 Open 0 0 1 1 N D X X 0 0 1 0 N 0 1 1 1 D X X N 0 0 1 0 Q 0 D 1 = Q 1 + D + Q 0 N D 0 = Q 0’ N + Q 0 N’ + Q 1 N + Q 1 D OPEN = Q 1 Q 0 VTŠ Novi Sad Elektronika 2 - Digitalna elektronika 25

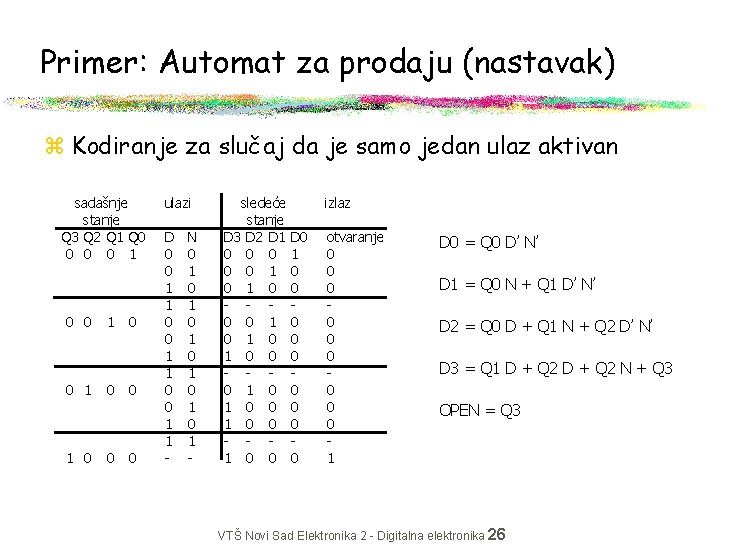

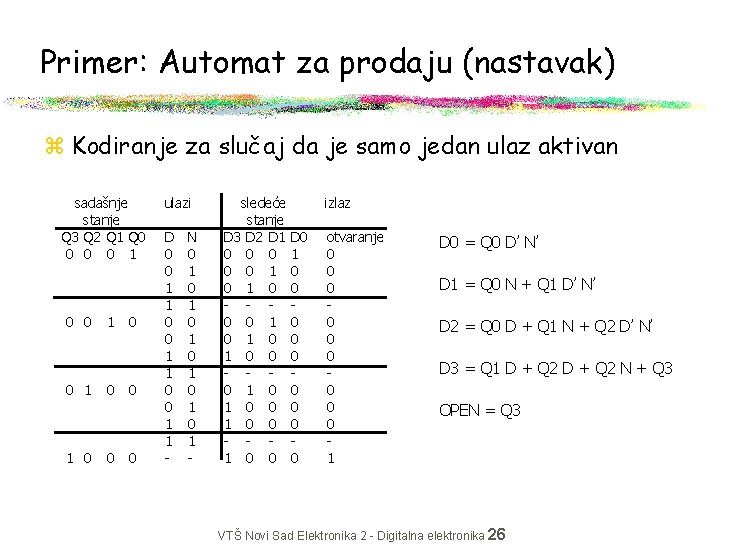

Primer: Automat za prodaju (nastavak) z Kodiranje za slučaj da je samo jedan ulaz aktivan sadašnje stanje Q 3 Q 2 Q 1 Q 0 0 1 0 0 0 1 1 0 0 0 ulazi D 0 0 1 1 - N 0 1 0 1 0 1 - sledeće stanje D 3 D 2 D 1 D 0 0 1 0 0 - - - 0 0 1 0 0 0 - - - 0 1 0 0 0 - - - 1 0 0 0 izlaz otvaranje 0 0 0 0 0 1 D 0 = Q 0 D’ N’ D 1 = Q 0 N + Q 1 D’ N’ D 2 = Q 0 D + Q 1 N + Q 2 D’ N’ D 3 = Q 1 D + Q 2 N + Q 3 OPEN = Q 3 VTŠ Novi Sad Elektronika 2 - Digitalna elektronika 26

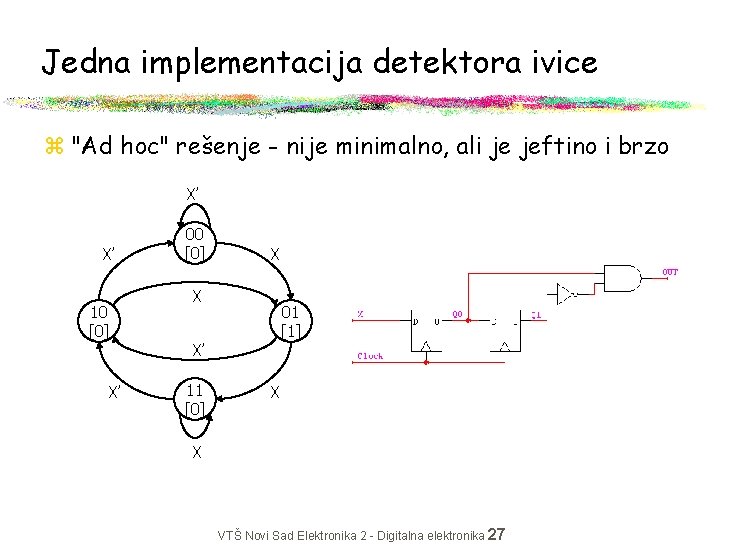

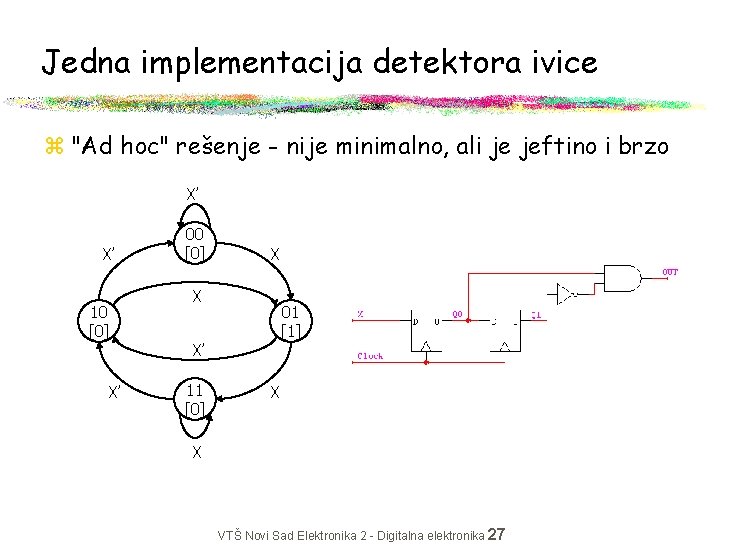

Jedna implementacija detektora ivice z "Ad hoc" rešenje - nije minimalno, ali je jeftino i brzo X’ X’ 10 [0] X’ 00 [0] X X 01 [1] X’ 11 [0] X X VTŠ Novi Sad Elektronika 2 - Digitalna elektronika 27