VonNewman Machine p p Input Output 5 1

![指令運作原理 CISC: Complex Instruction Set Computer 複雜 指令 集 ADD AX, 100[BX] 六階段 Fetch 指令運作原理 CISC: Complex Instruction Set Computer 複雜 指令 集 ADD AX, 100[BX] 六階段 Fetch](https://slidetodoc.com/presentation_image/300aa854a55d2609231733fed0958c4a/image-13.jpg)

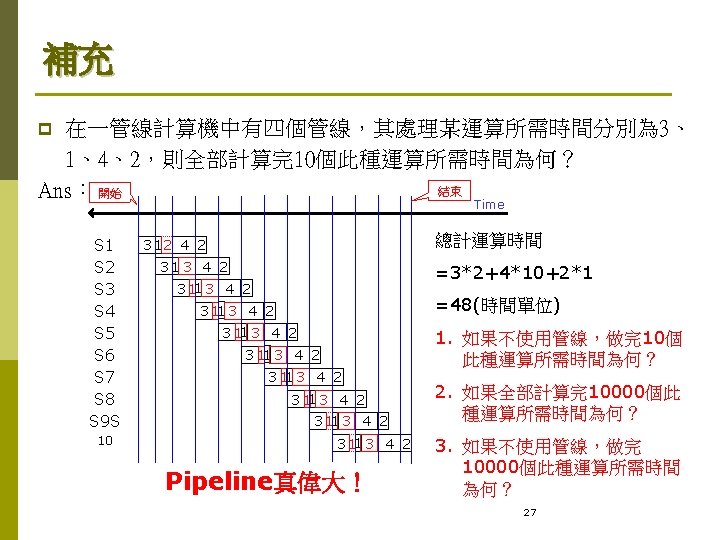

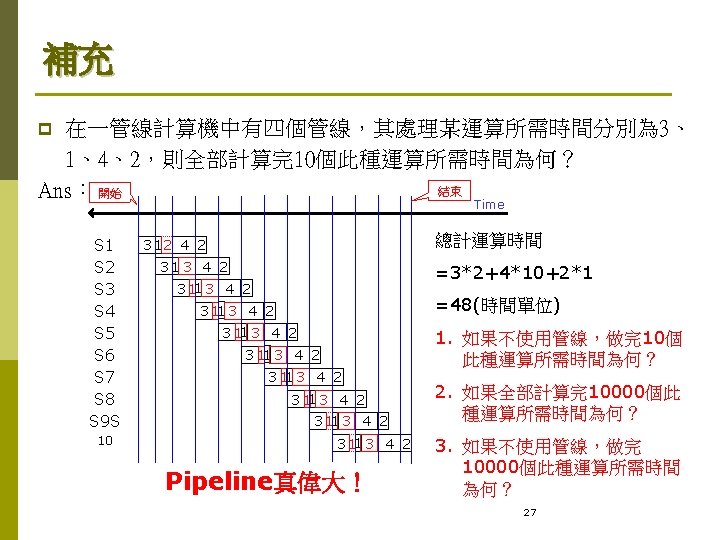

- Slides: 27

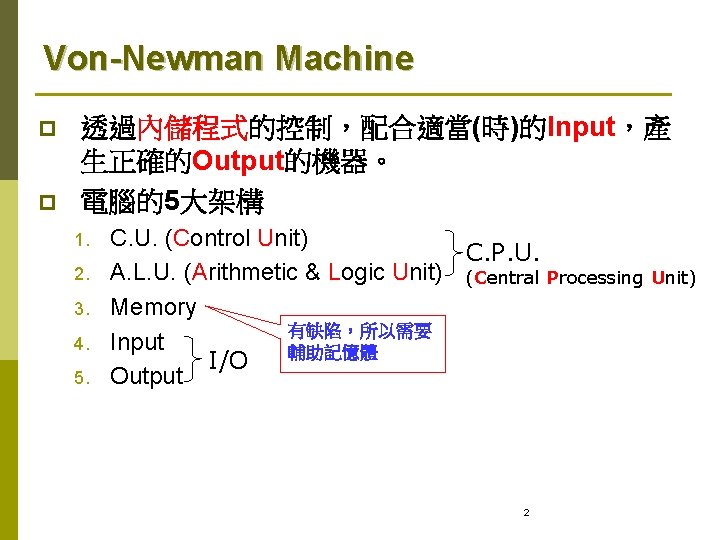

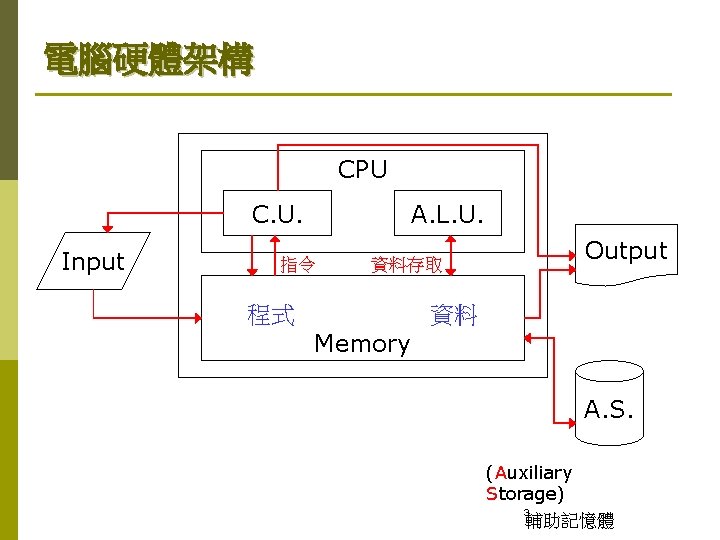

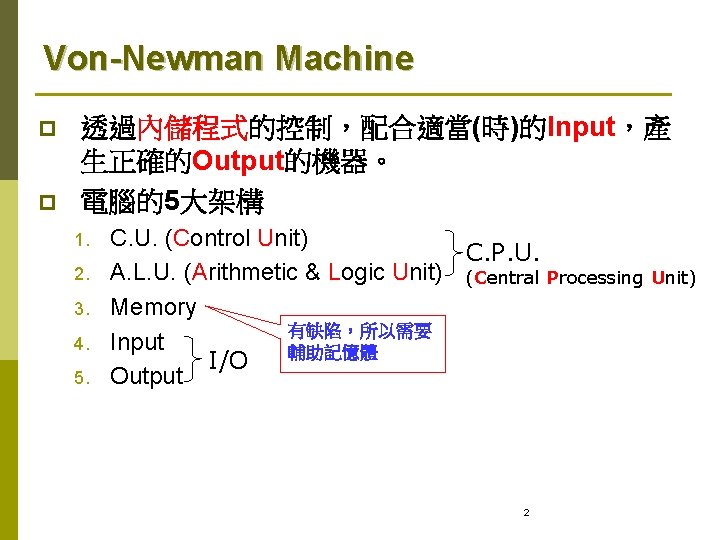

Von-Newman Machine p p 透過內儲程式的控制,配合適當(時)的Input,產 生正確的Output的機器。 電腦的5大架構 1. 2. 3. 4. 5. C. U. (Control Unit) C. P. U. A. L. U. (Arithmetic & Logic Unit) (Central Processing Unit) Memory 有缺陷,所以需要 Input 輔助記憶體 I/O Output 2

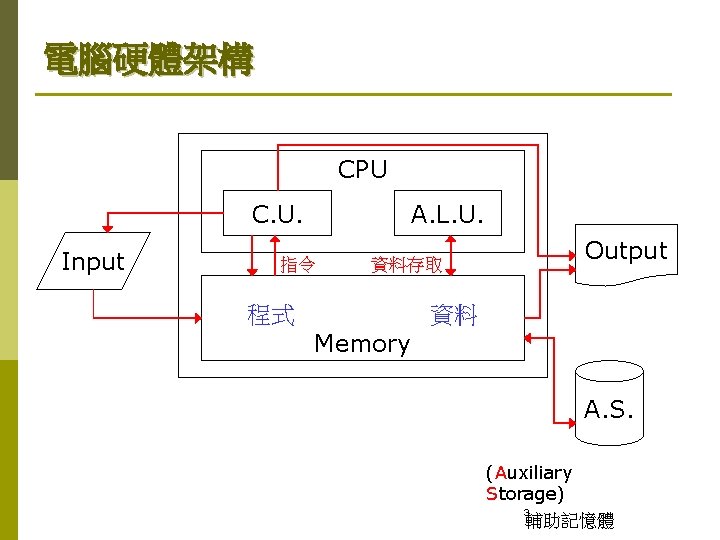

電腦硬體架構 CPU C. U. Input A. L. U. 指令 資料存取 程式 Output 資料 Memory A. S. (Auxiliary Storage) 3 輔助記憶體

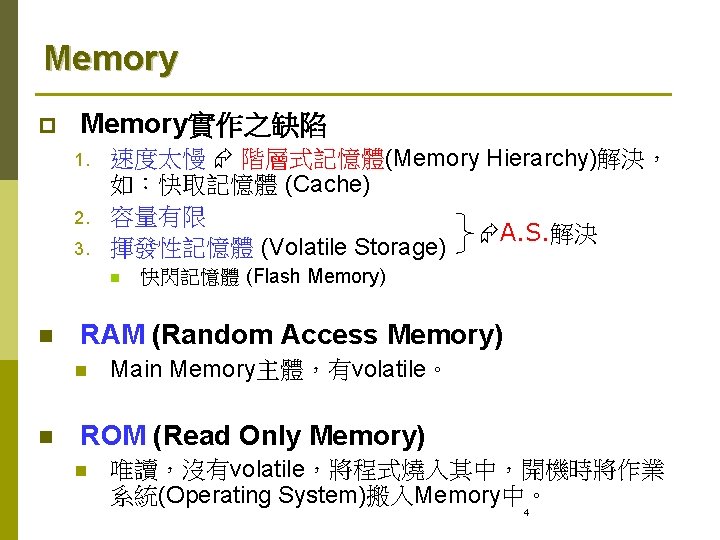

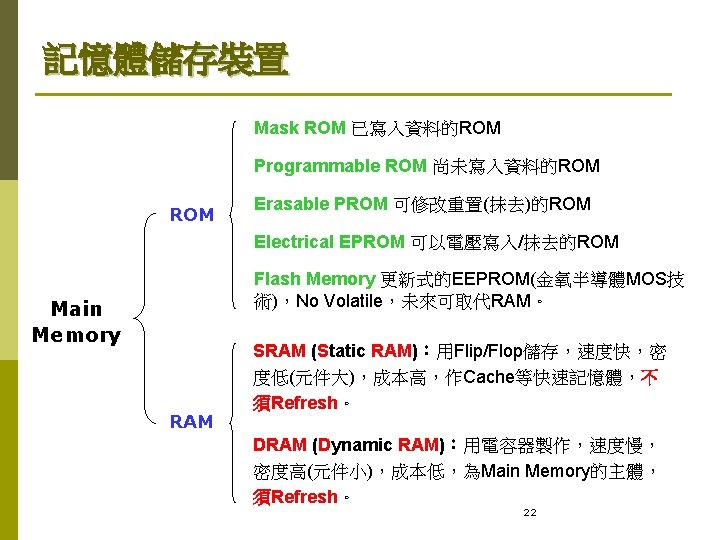

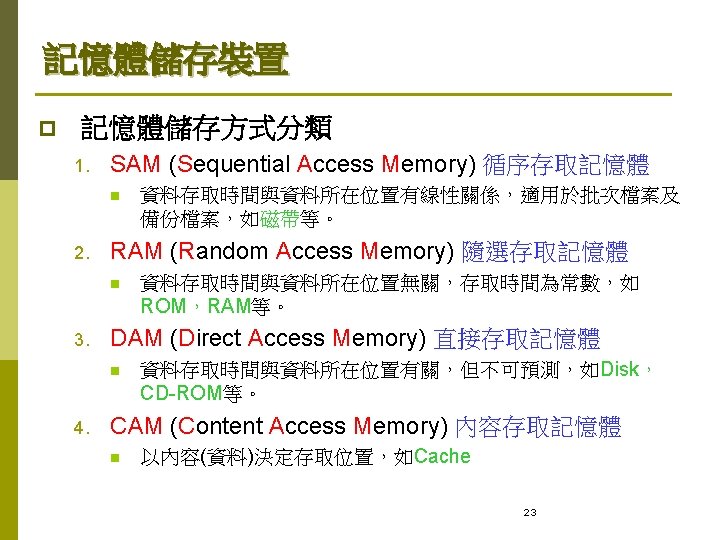

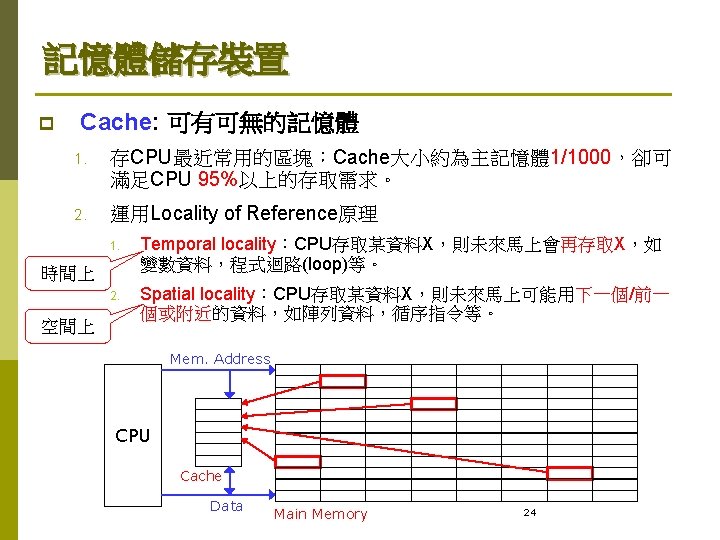

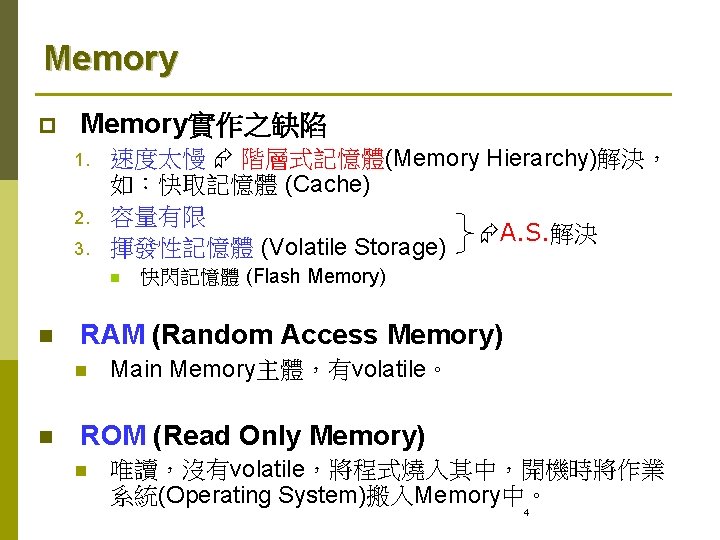

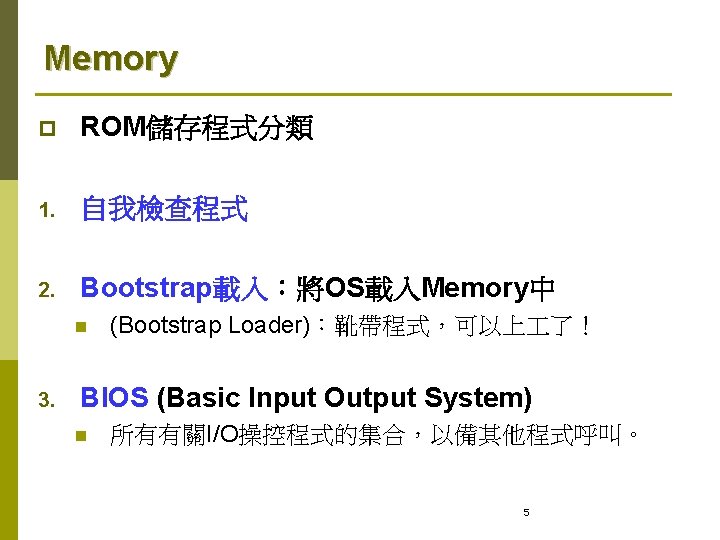

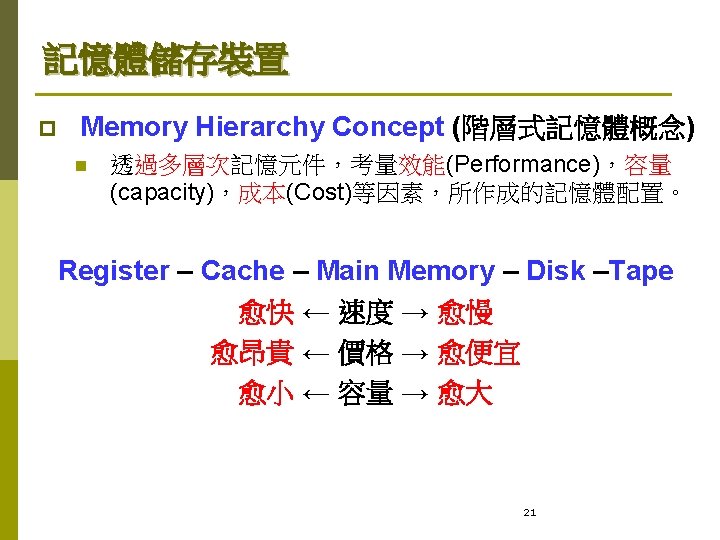

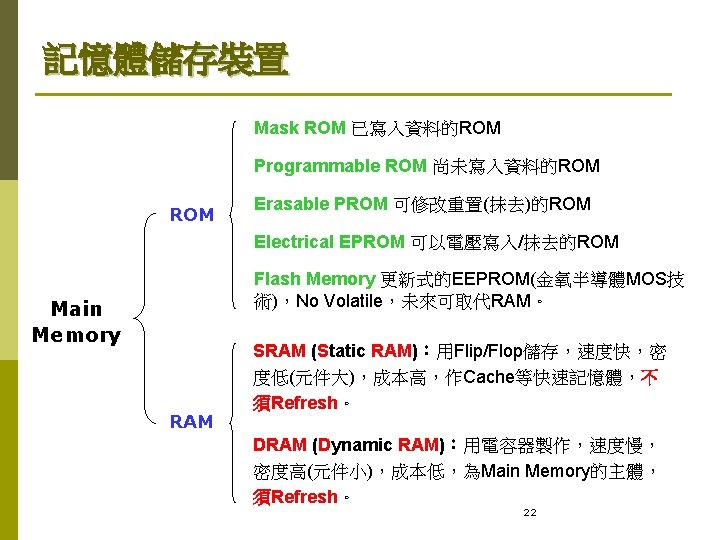

Memory p Memory實作之缺陷 1. 2. 3. 速度太慢 階層式記憶體(Memory Hierarchy)解決, 如:快取記憶體 (Cache) 容量有限 A. S. 解決 揮發性記憶體 (Volatile Storage) n n RAM (Random Access Memory) n n 快閃記憶體 (Flash Memory) Main Memory主體,有volatile。 ROM (Read Only Memory) n 唯讀,沒有volatile,將程式燒入其中,開機時將作業 系統(Operating System)搬入Memory中。 4

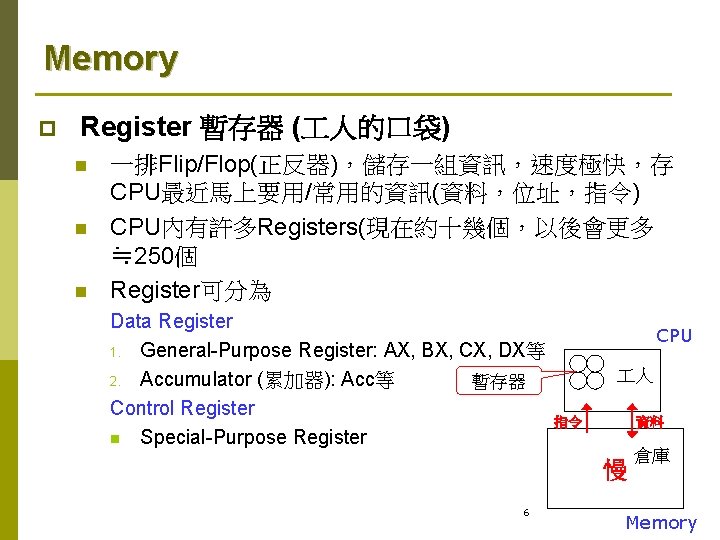

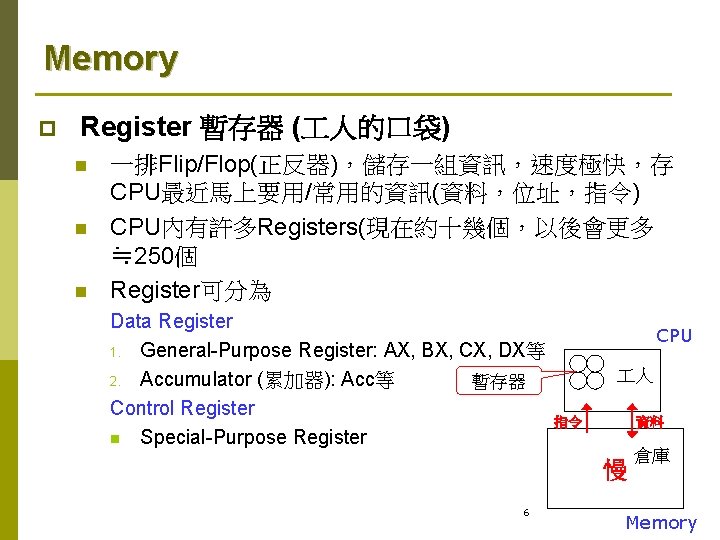

Memory p Register 暫存器 ( 人的口袋) n n n 一排Flip/Flop(正反器),儲存一組資訊,速度極快,存 CPU最近馬上要用/常用的資訊(資料,位址,指令) CPU內有許多Registers(現在約十幾個,以後會更多 ≒ 250個 Register可分為 Data Register 1. General-Purpose Register: AX, BX, CX, DX等 2. Accumulator (累加器): Acc等 暫存器 Control Register n Special-Purpose Register CPU 人 指令 資料 慢 6 倉庫 Memory

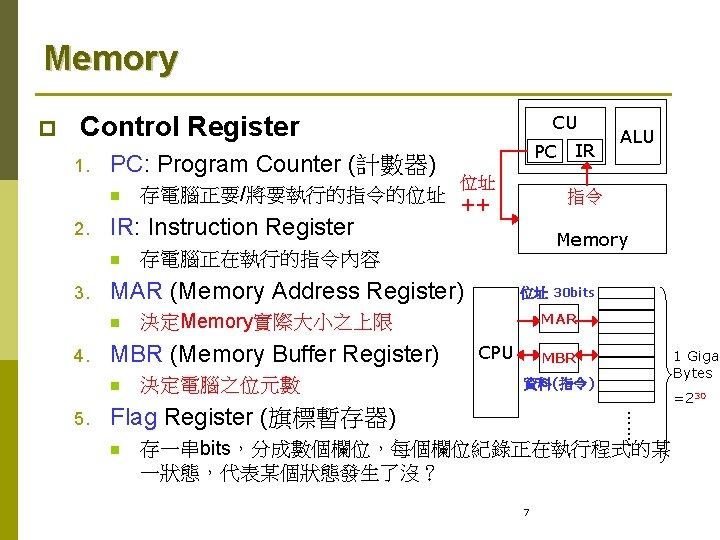

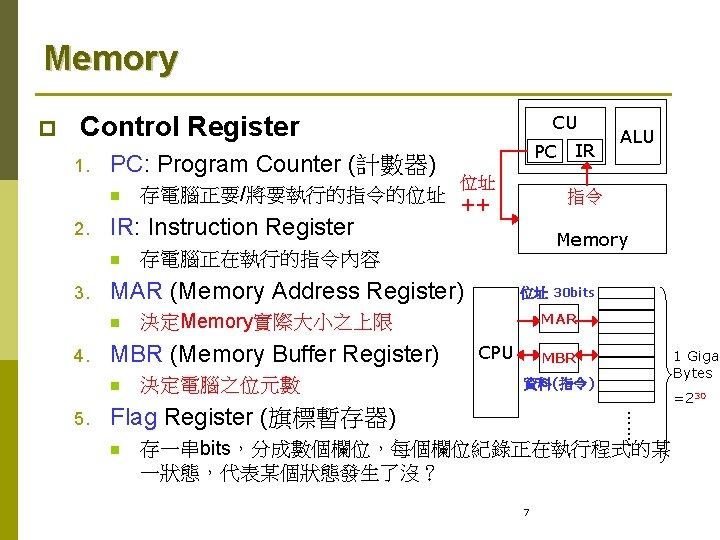

Memory p Control Register 1. PC: Program Counter (計數器) n 2. Memory 位址 30 bits MAR 決定Memory實際大小之上限 決定電腦之位元數 CPU 1 Giga Bytes MBR 資料(指令) =230 ……. Flag Register (旗標暫存器) n ALU 指令 存電腦正在執行的指令內容 MBR (Memory Buffer Register) n 5. 位址 存電腦正要/將要執行的指令的位址 ++ MAR (Memory Address Register) n 4. PC IR IR: Instruction Register n 3. CU 存一串bits,分成數個欄位,每個欄位紀錄正在執行程式的某 一狀態,代表某個狀態發生了沒? 7

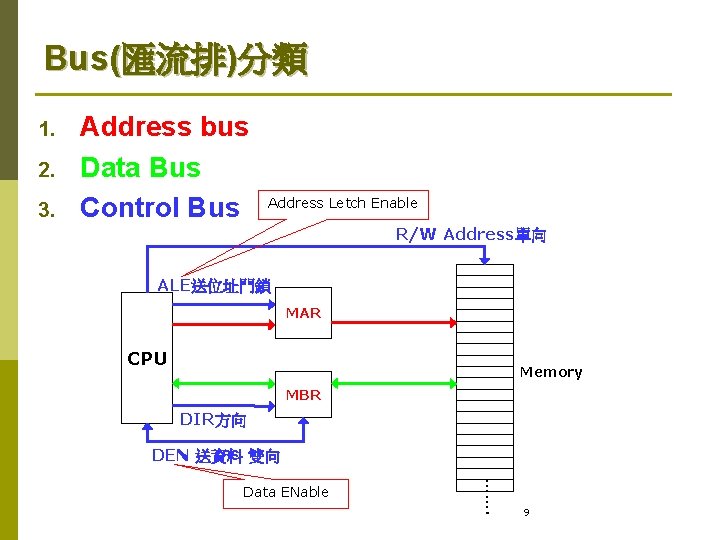

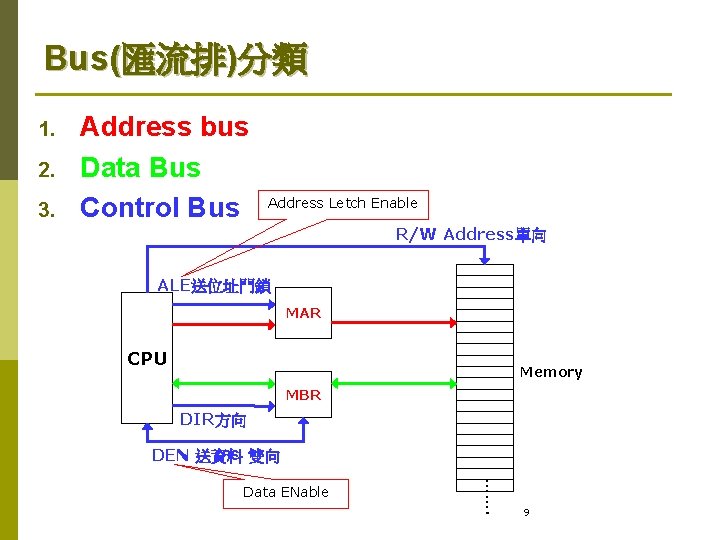

Bus(匯流排)分類 1. 2. 3. Address bus Data Bus Control Bus Address Letch Enable R/W Address單向 ALE送位址門鎖 MAR CPU Memory MBR DIR方向 DEN 送資料 雙向 ……. Data ENable 9

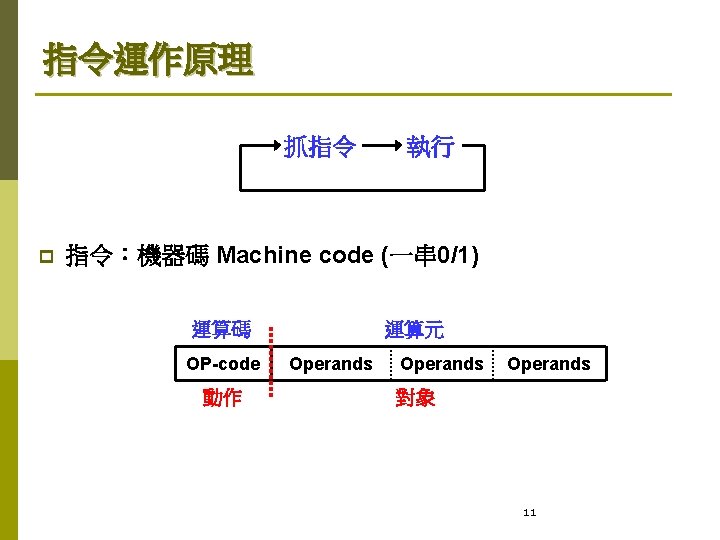

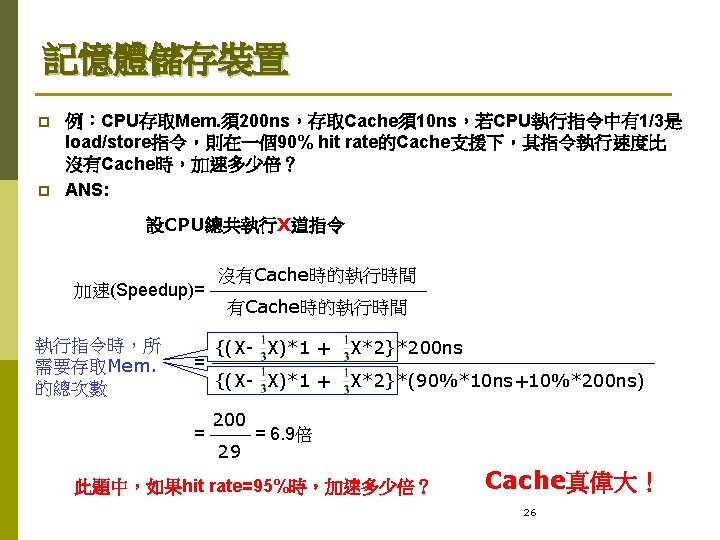

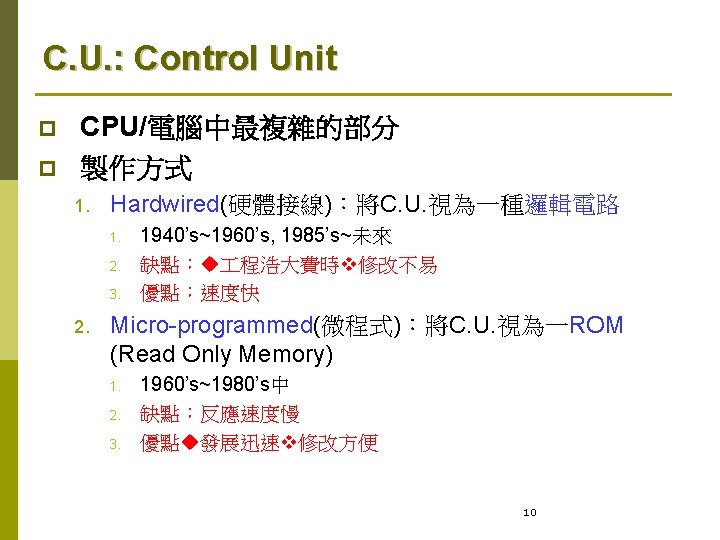

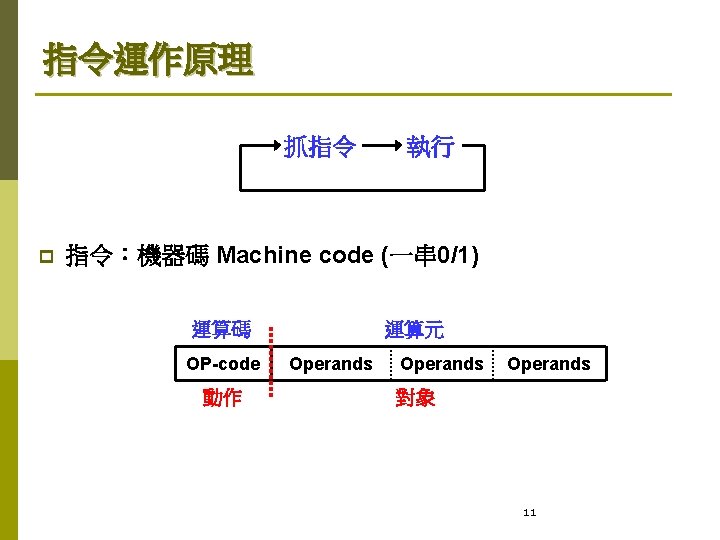

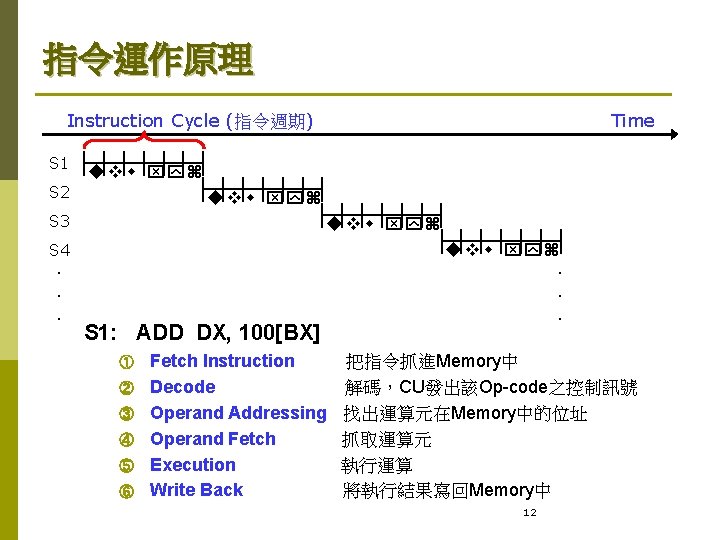

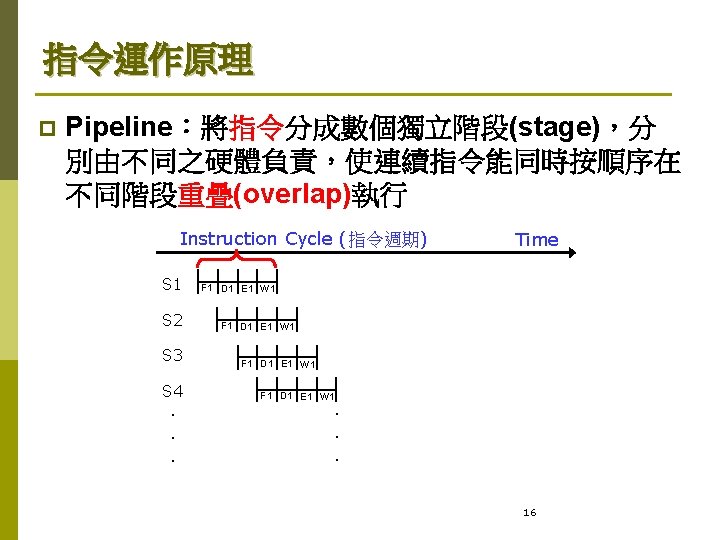

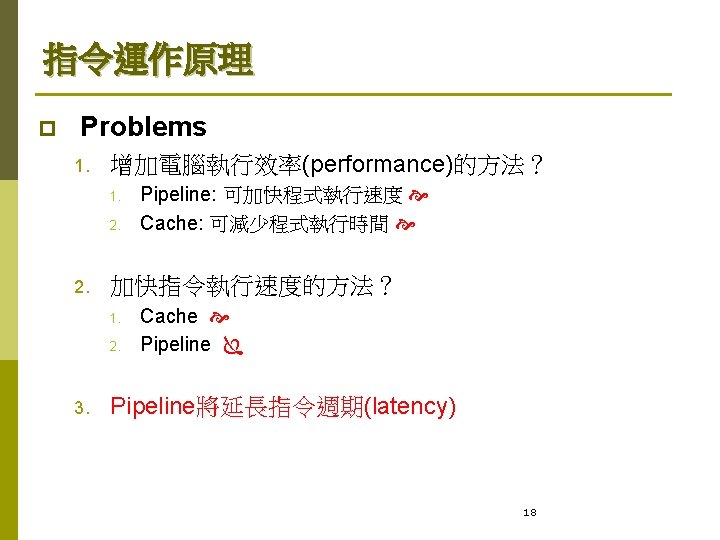

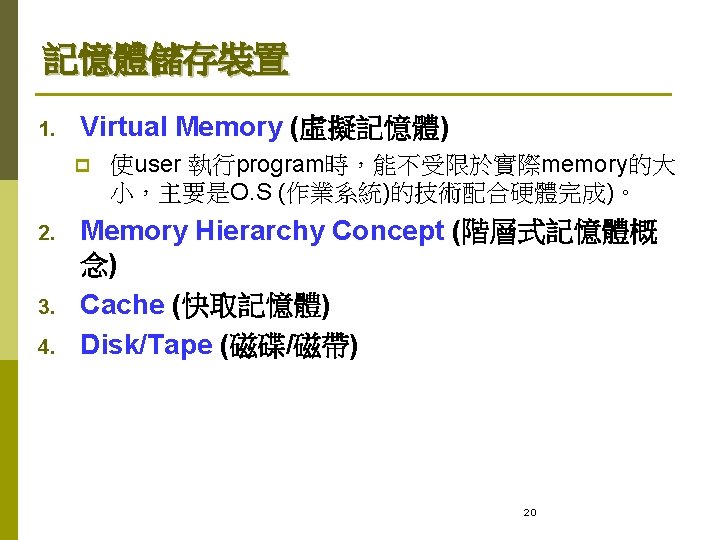

指令運作原理 Instruction Cycle (指令週期) S 1 S 2 S 3 S 4 . . . Time . . . S 1: ADD DX, 100[BX] ① ② ③ ④ ⑤ ⑥ Fetch Instruction Decode Operand Addressing Operand Fetch Execution Write Back 把指令抓進Memory中 解碼,CU發出該Op-code之控制訊號 找出運算元在Memory中的位址 抓取運算元 執行運算 將執行結果寫回Memory中 12

![指令運作原理 CISC Complex Instruction Set Computer 複雜 指令 集 ADD AX 100BX 六階段 Fetch 指令運作原理 CISC: Complex Instruction Set Computer 複雜 指令 集 ADD AX, 100[BX] 六階段 Fetch](https://slidetodoc.com/presentation_image/300aa854a55d2609231733fed0958c4a/image-13.jpg)

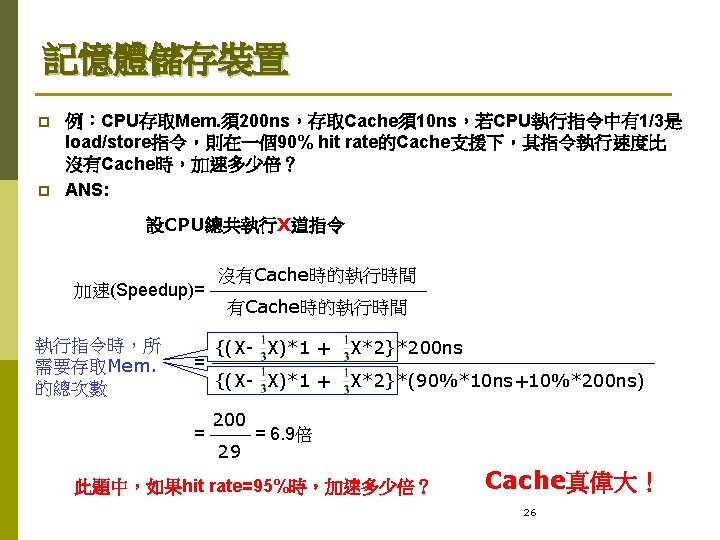

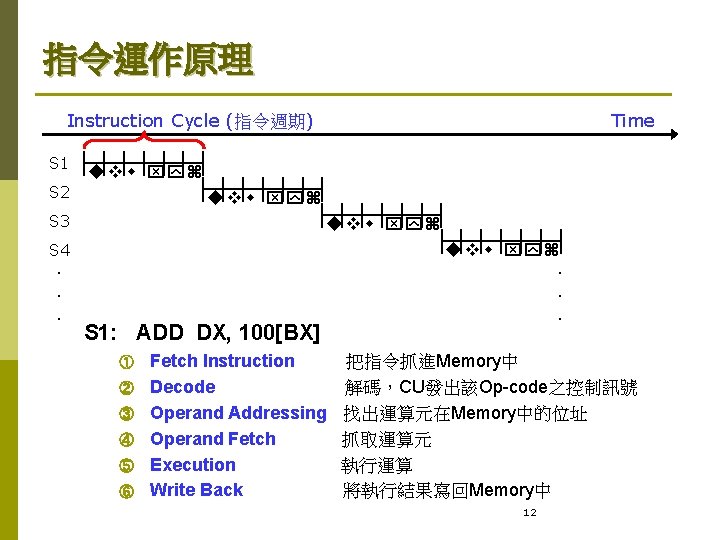

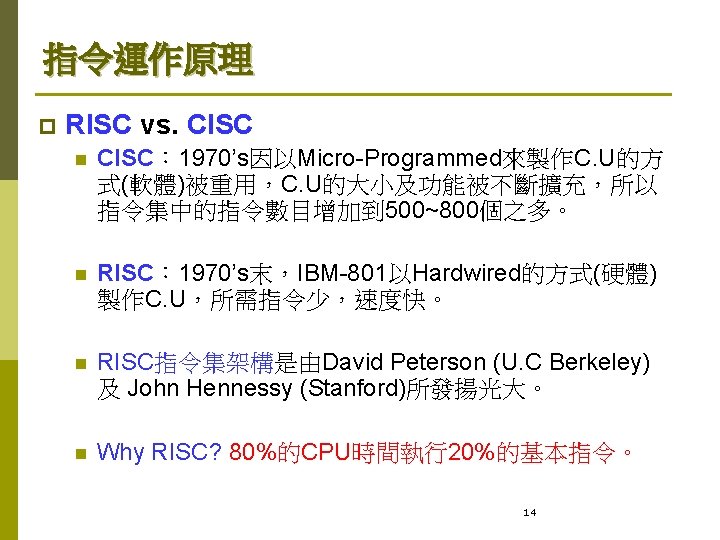

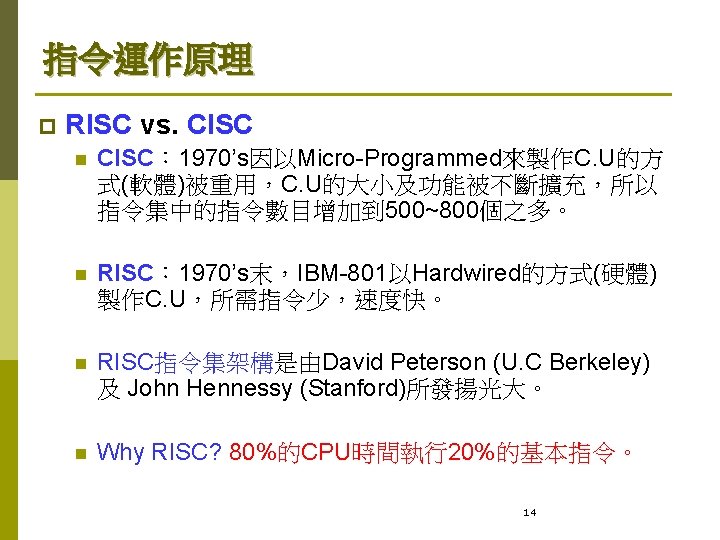

指令運作原理 CISC: Complex Instruction Set Computer 複雜 指令 集 ADD AX, 100[BX] 六階段 Fetch Ins. Decode Operand Addressing 電腦 AX←AX+Mem[100+BX] Operand Fetch Execution RISC: Reduced Instruction Set Computer 簡單 指令 集 電腦 四階段 Fetch Decode Execution Write back 13 Write back

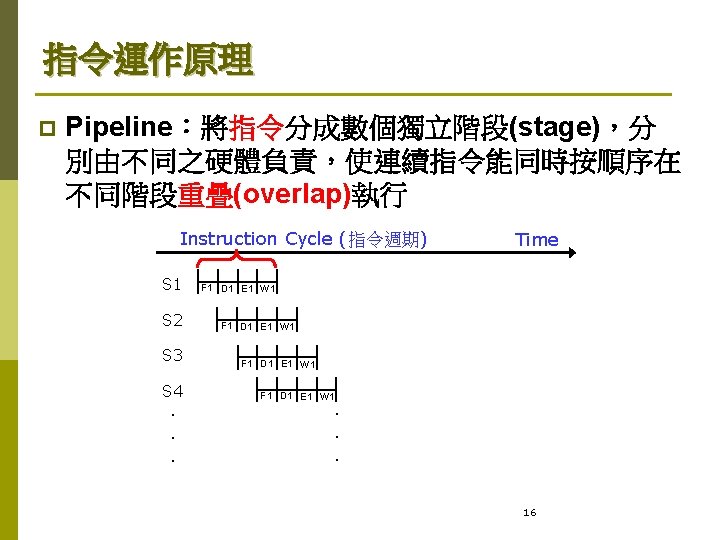

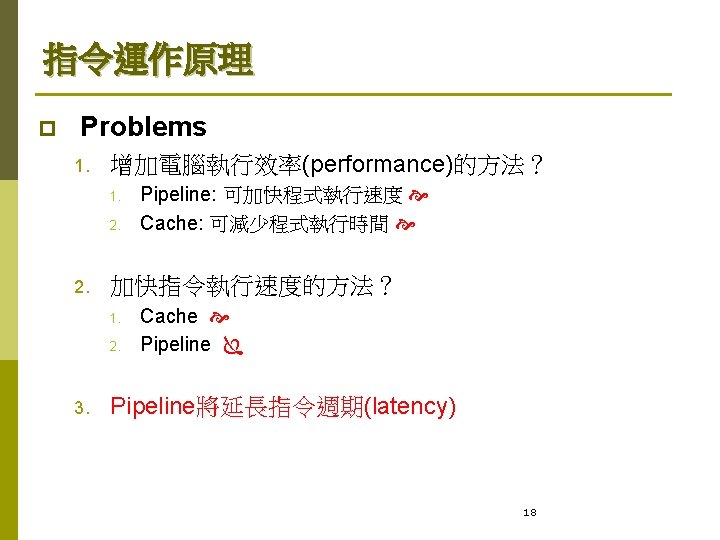

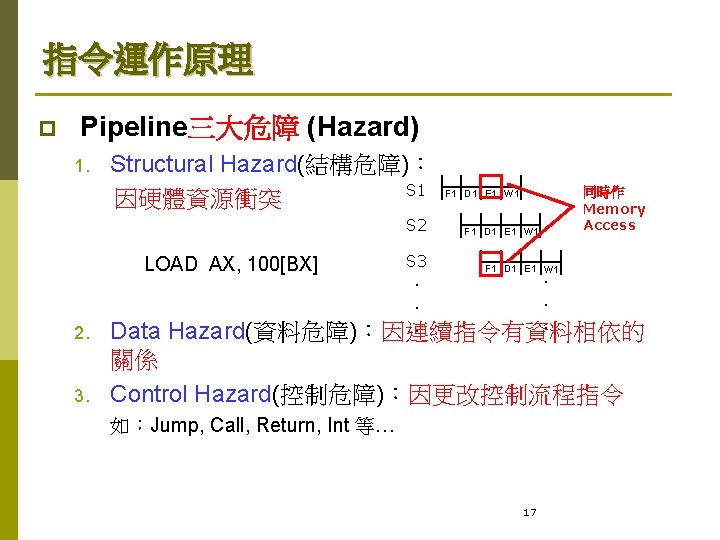

指令運作原理 p Pipeline三大危障 (Hazard) 1. Structural Hazard(結構危障): S 1 因硬體資源衝突 S 2 F 1 D 1 E 1 W 1 同時作 Memory Access S 3 F 1 D 1 E 1 W 1 . . . Hazard(資料危障):因連續指令有資料相依的 LOAD AX, 100[BX] 2. 3. Data 關係 Control Hazard(控制危障):因更改控制流程指令 如:Jump, Call, Return, Int 等… 17

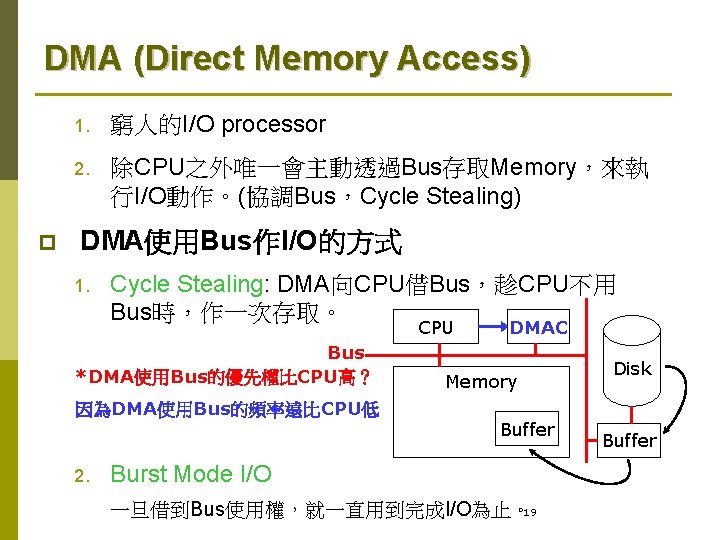

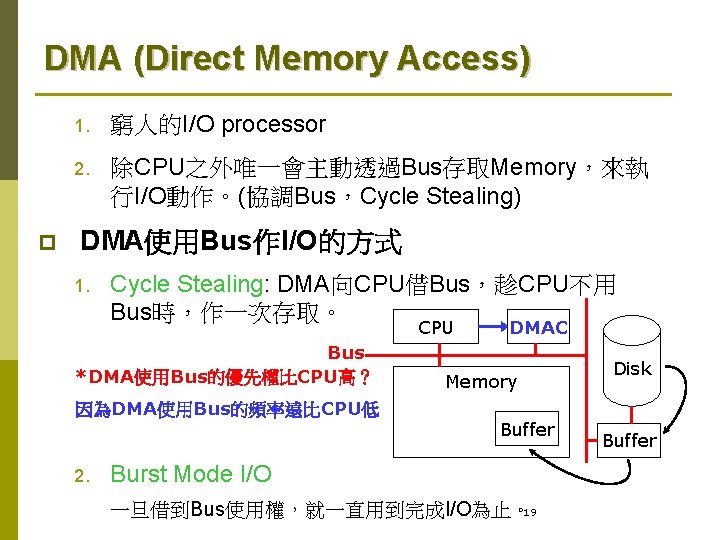

DMA (Direct Memory Access) p 1. 窮人的I/O processor 2. 除CPU之外唯一會主動透過Bus存取Memory,來執 行I/O動作。(協調Bus,Cycle Stealing) DMA使用Bus作I/O的方式 1. Cycle Stealing: DMA向CPU借Bus,趁CPU不用 Bus時,作一次存取。 CPU Bus *DMA使用Bus的優先權比CPU高? 因為DMA使用Bus的頻率遠比CPU低 2. DMAC Memory Buffer Burst Mode I/O 一旦借到Bus使用權,就一直用到完成I/O為止。19 Disk Buffer

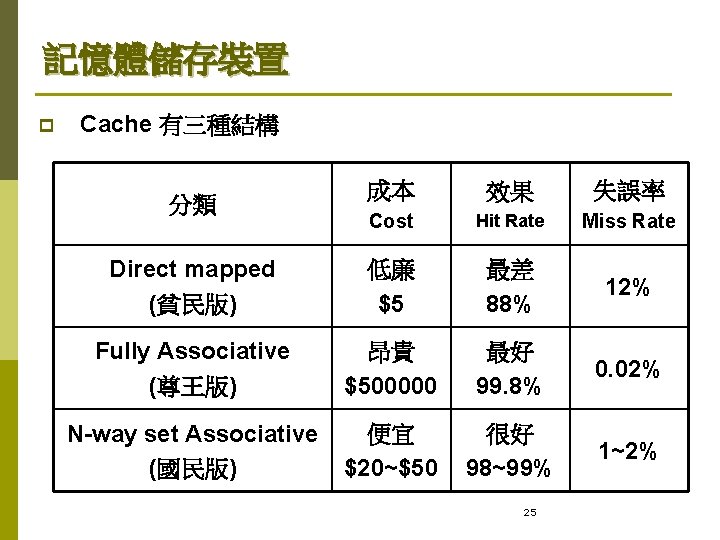

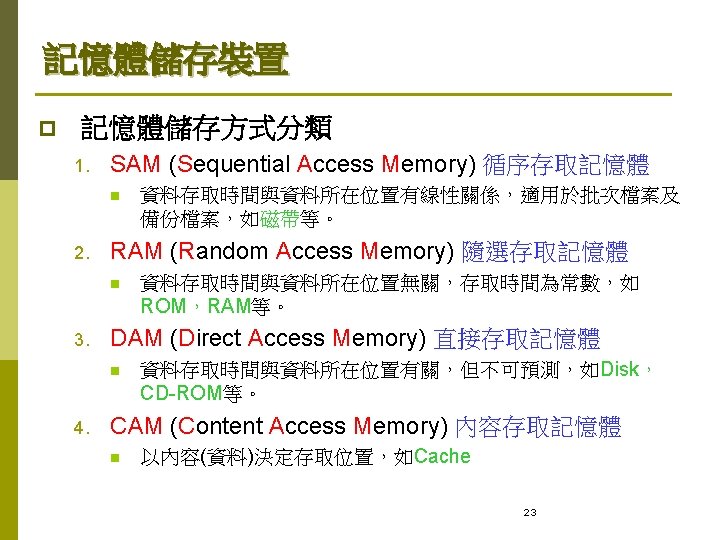

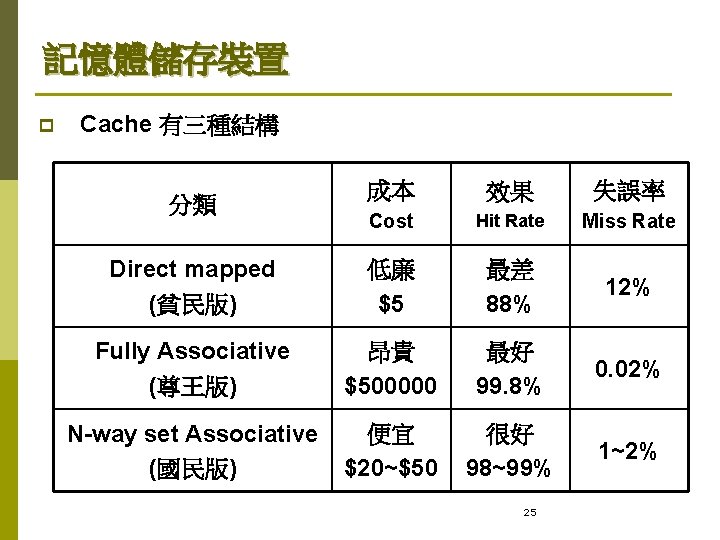

記憶體儲存裝置 p Cache 有三種結構 成本 效果 失誤率 Cost Hit Rate Miss Rate Direct mapped (貧民版) 低廉 $5 最差 88% 12% Fully Associative (尊王版) 昂貴 $500000 最好 99. 8% 0. 02% N-way set Associative (國民版) 便宜 $20~$50 很好 98~99% 1~2% 分類 25