Von Neumann Computers Article Authors Rudolf Eigenman David

- Slides: 19

Von Neumann Computers Article Authors: Rudolf Eigenman & David Lilja Presenter: Kimberly Nguyen April 03, 2008

Objective o o o John Von Neumann’s Contribution Von Neumann Architecture Fundamental concepts that led up to today’s computing world

John Von Neumann o o o Born in Hungary on 1903 A chemical engineer and mathematician with a concentration in physics and applied mathematics Became a consultant for ENIAC (Electronic Numerical Integrator and Computer) project- first modern electronic computer Interested in the logical structure and mathematical description of ENIAC Developed EDVAC (Electronic Discrete Variable Automatic Computer) with Eckert and Mauchly as a successor of ENIAC Later designed his own machine at the Institute for Advanced Study at Princeton University hence, Von Neumann architecture and Princeton architecture became synonymous

Von Neumann Contribution o o o Von Neumann “stored-program” concept was developed in 1940 s Originated from Babbage’s simple pegged-cylinder automata (1830) – has 2 logical units (memory, I/O, Arithmetic units & decision mechanism based on result) Babbage’s concepts materialized to the electromechanical relays (1940) and vacuum tubes (1946) - principal elements in the computer's advancement

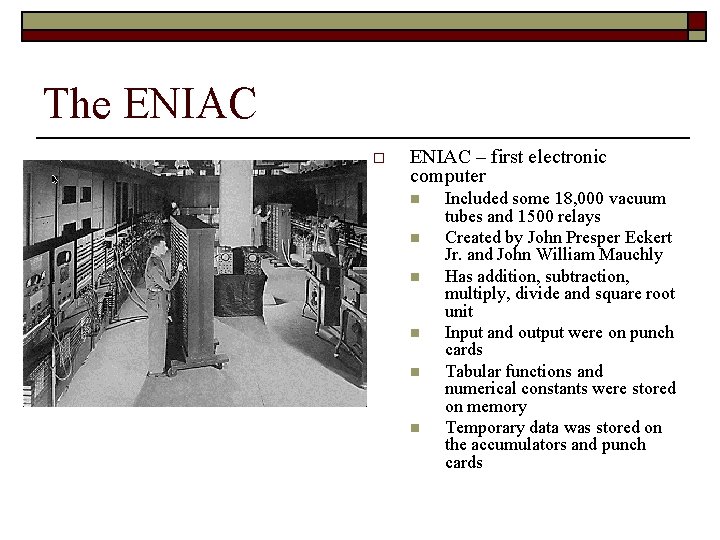

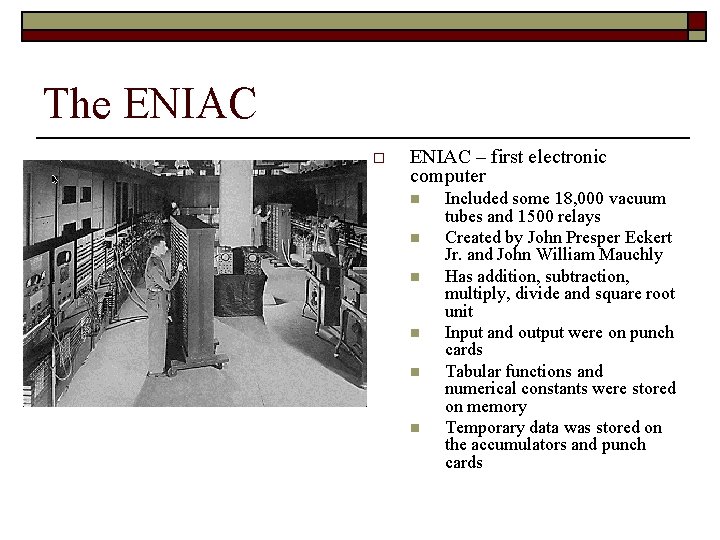

The ENIAC o ENIAC – first electronic computer n n n Included some 18, 000 vacuum tubes and 1500 relays Created by John Presper Eckert Jr. and John William Mauchly Has addition, subtraction, multiply, divide and square root unit Input and output were on punch cards Tabular functions and numerical constants were stored on memory Temporary data was stored on the accumulators and punch cards

Von Neumann Contribution (cont) o o o Combined Babbage machine and ENIAC technology and innovated the concept of stored-program machine instructions and program data are stored on a common memory Advantage of stored-programs can be generated by other programs (compilers, loaders) A. k. a self-modifying code –an unfavorable technique today, i. e. software virus program

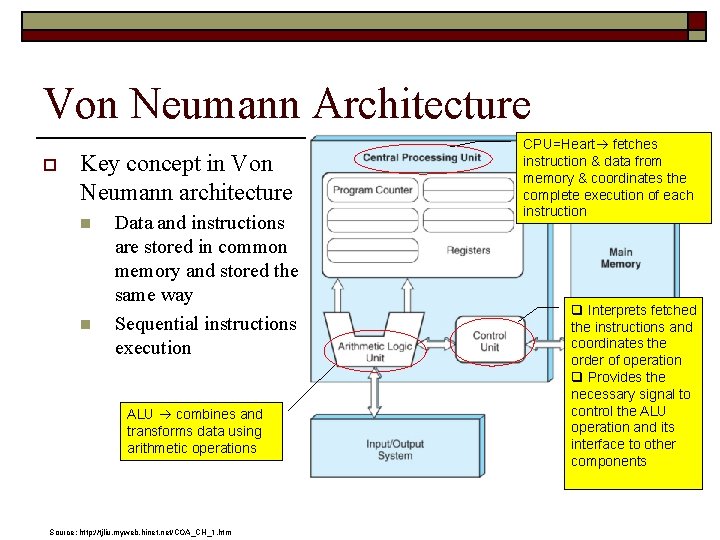

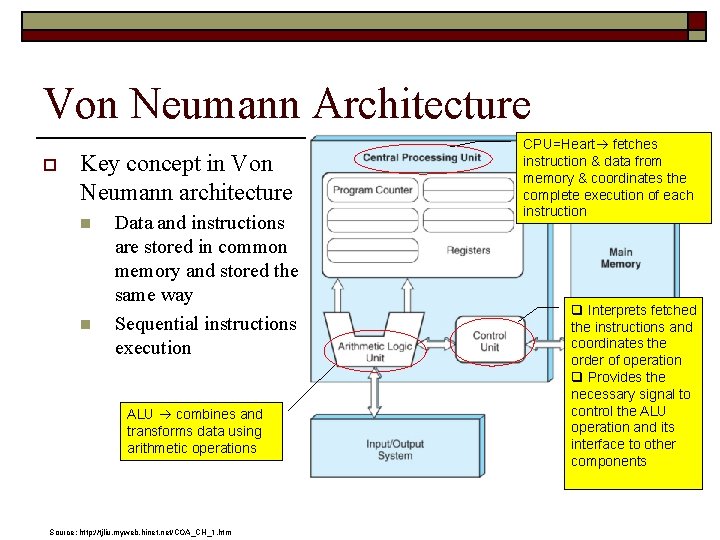

Von Neumann Architecture o Key concept in Von Neumann architecture n n Data and instructions are stored in common memory and stored the same way Sequential instructions execution ALU combines and transforms data using arithmetic operations Source: http: //tjliu. myweb. hinet. net/COA_CH_1. htm CPU=Heart fetches instruction & data from memory & coordinates the complete execution of each instruction q Interprets fetched the instructions and coordinates the order of operation q Provides the necessary signal to control the ALU operation and its interface to other components

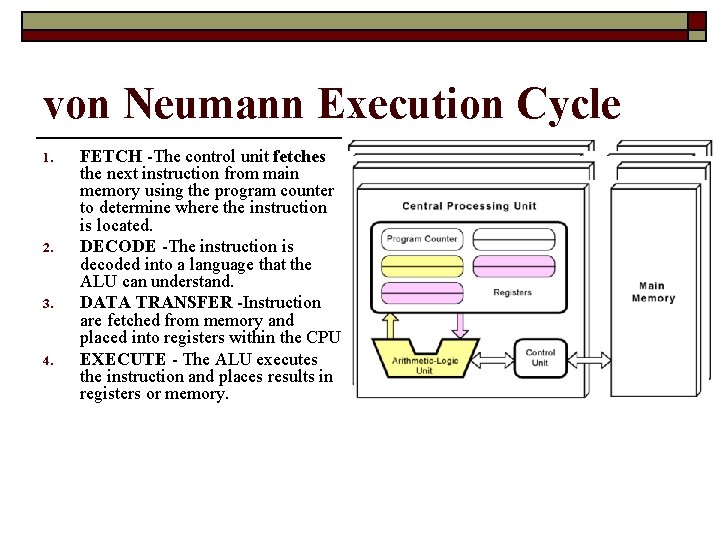

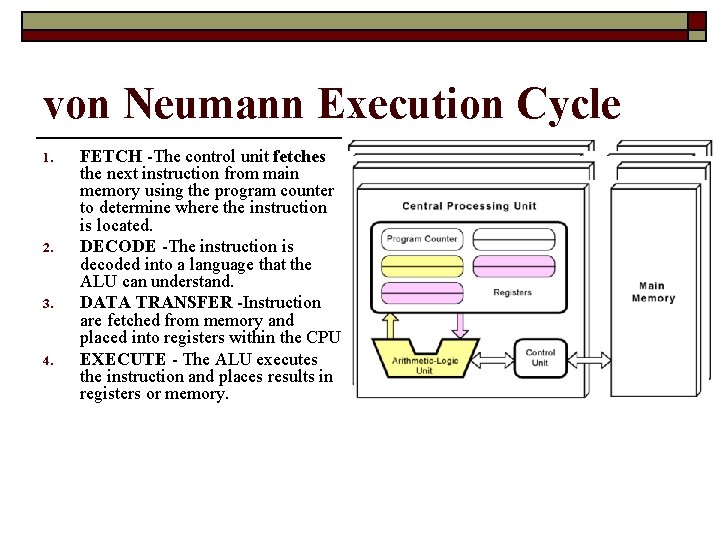

von Neumann Execution Cycle 1. 2. 3. 4. FETCH -The control unit fetches the next instruction from main memory using the program counter to determine where the instruction is located. DECODE -The instruction is decoded into a language that the ALU can understand. DATA TRANSFER -Instruction are fetched from memory and placed into registers within the CPU. EXECUTE - The ALU executes the instruction and places results in registers or memory.

Key Features of Von Neumann Architecture o o o Instructions & data are both stored in the same main memory, thus not distinguishable from each other Each instructions must specify how it interprets the data on which it operates Memory is accessed by name (address) independent of the bit pattern stored at each address, thus values stored in memory can be interpret as addresses as well as data or instructions Self-modifying code: program can manipulate addresses using the same set of instructions that the CPU uses to manipulate data Order of execution is sequential, unless explicitly altered (BRANCH, JUMP instruction)

Instruction Types 1. 2. 3. 4. Data movement – copy data between registers or memory locations or between I/O and CPU Data transformation – take one or more values as input and perform some operation Program control – alter the flow of its sequential instruction execution System control – instruction used to improve performance (prefetch instructions)

Basic Instruction Specification 1. 2. 3. 4. The operation to be performed (op-code) The location of the operands (input) The destination location The next instruction to be executed

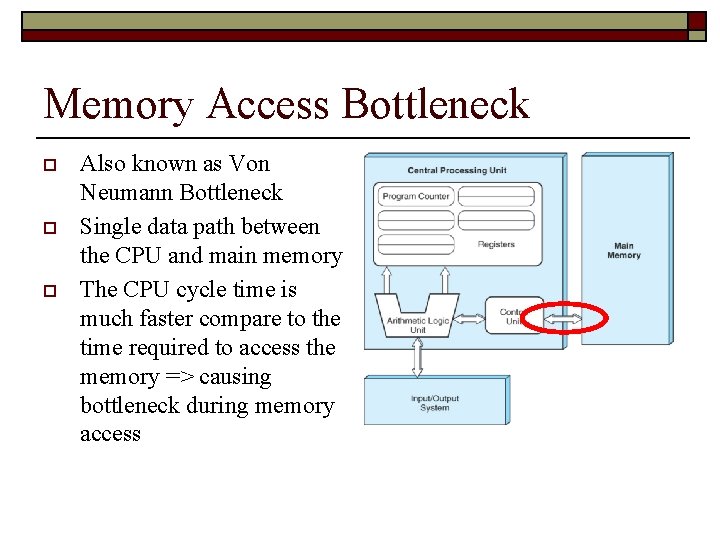

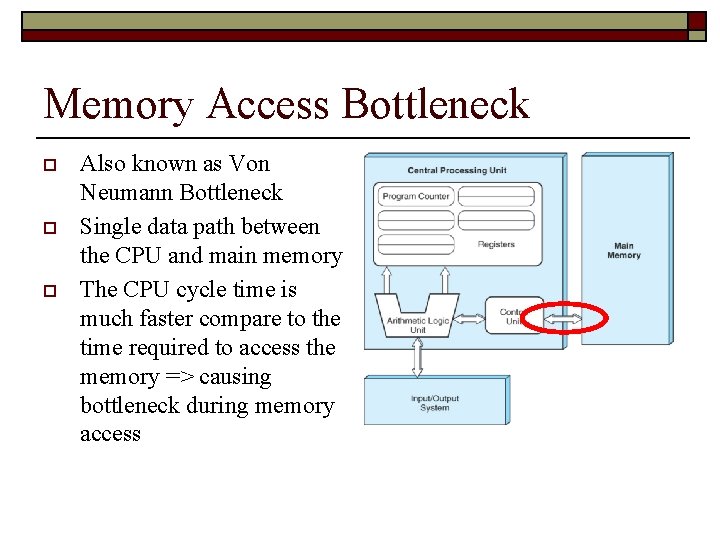

Memory Access Bottleneck o o o Also known as Von Neumann Bottleneck Single data path between the CPU and main memory The CPU cycle time is much faster compare to the time required to access the memory => causing bottleneck during memory access

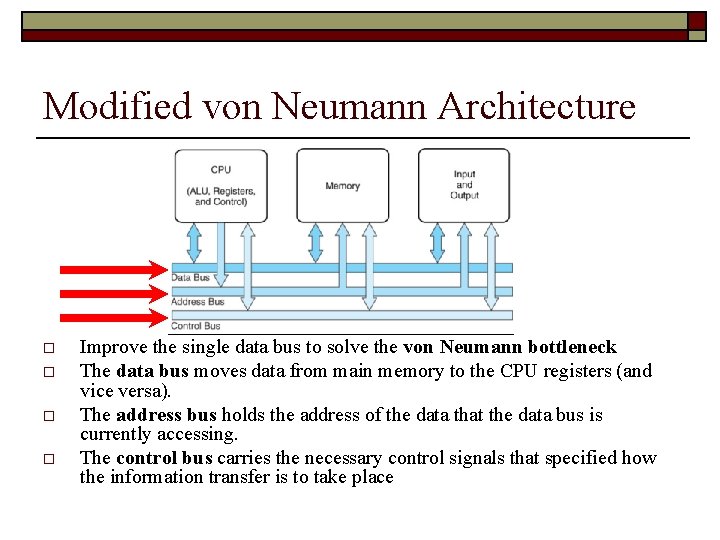

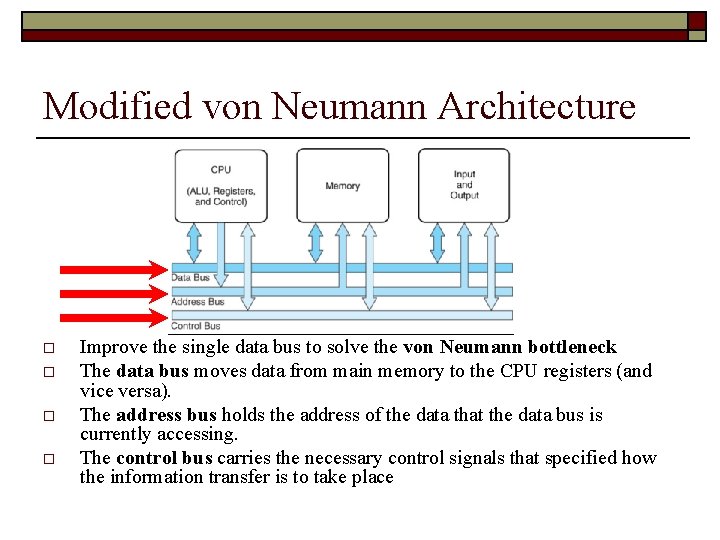

Modified von Neumann Architecture o o Improve the single data bus to solve the von Neumann bottleneck The data bus moves data from main memory to the CPU registers (and vice versa). The address bus holds the address of the data that the data bus is currently accessing. The control bus carries the necessary control signals that specified how the information transfer is to take place

Latency & Bandwidth o o Latency – time elapses from the initiate request by the CPU to the memory until that requested is satisfied Bandwidth – amount of data can be transferred per unit time from memory to the processor Improve the memory bandwidth by increasing the bus size Reduce memory latency by using caches in a memory hierarchy- near the processor

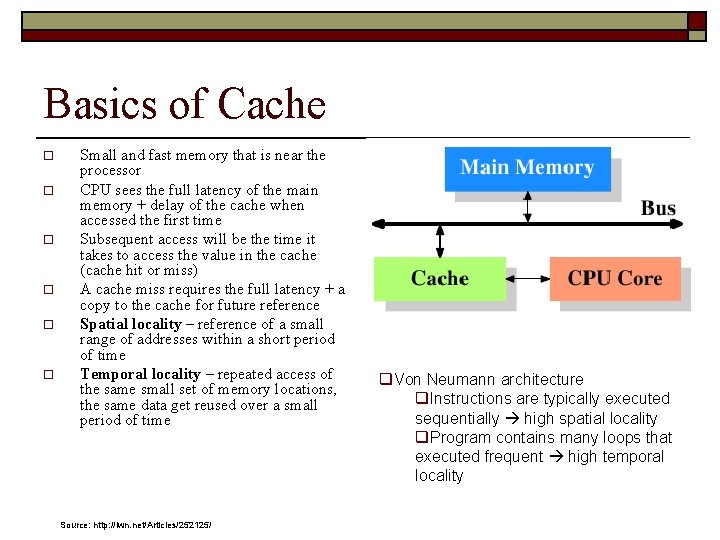

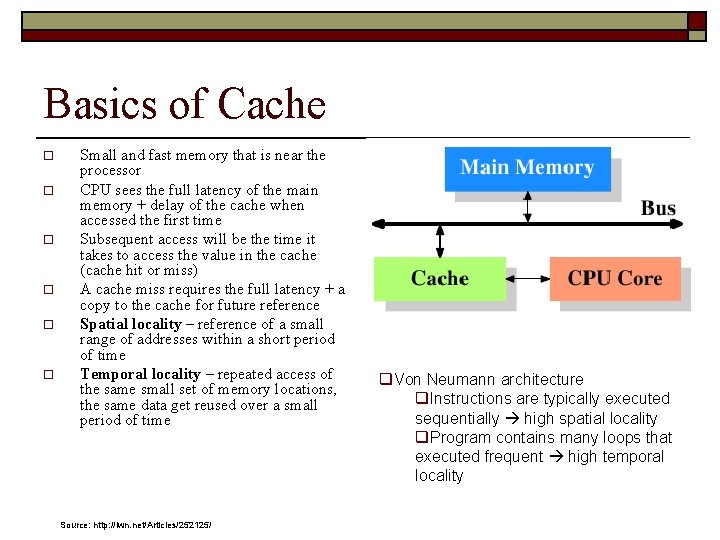

Basics of Cache o o o Small and fast memory that is near the processor CPU sees the full latency of the main memory + delay of the cache when accessed the first time Subsequent access will be the time it takes to access the value in the cache (cache hit or miss) A cache miss requires the full latency + a copy to the cache for future reference Spatial locality – reference of a small range of addresses within a short period of time Temporal locality – repeated access of the same small set of memory locations, the same data get reused over a small period of time Source: http: //lwn. net/Articles/252125/ q. Von Neumann architecture q. Instructions are typically executed sequentially high spatial locality q. Program contains many loops that executed frequent high temporal locality

Modern Computer Cache o o Last several decades have used the von Neumann architecture Advantage in separating the caches used for code and for data Intel has used separate code and data caches since 1993 Another concept emerged Cache the decoded instructions to speed up the execution Instruction Cache Data Cache

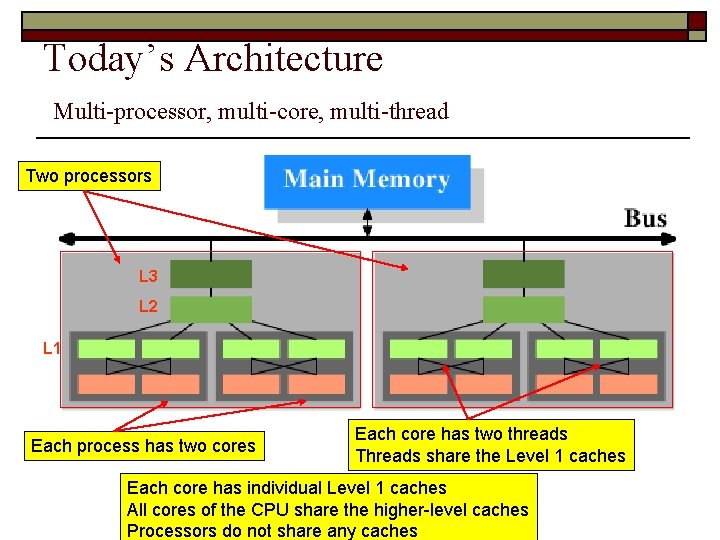

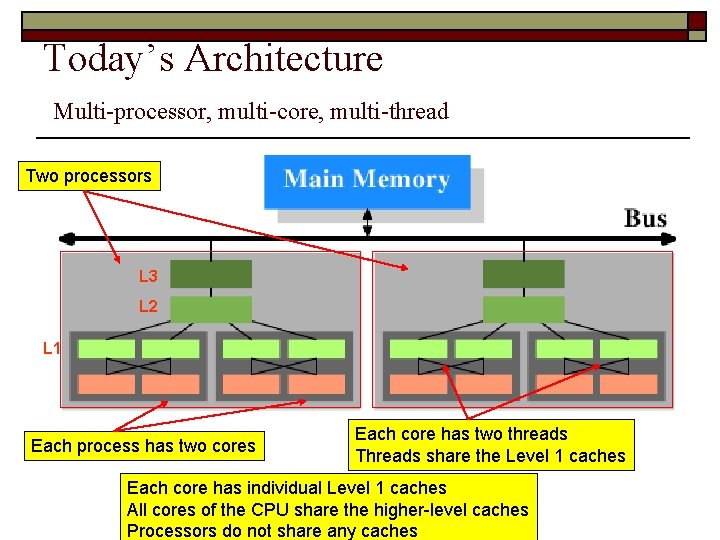

Today’s Architecture Multi-processor, multi-core, multi-thread Two processors L 3 L 2 L 1 Each process has two cores Each core has two threads Threads share the Level 1 caches Each core has individual Level 1 caches All cores of the CPU share the higher-level caches Processors do not share any caches

Alternative to Von Neumann Architecture Limitations n n o Single Bus Memory access bottleneck Performance limitation by the single instruction execution paradigm Alternative to Von Neumann Architecture n n Pipeline parallelism Multiple operations decoder that can executes simultaneously

Von Neumann Computers Today o Von Neumann concepts exist in today’s world n Supercomputers – fastest computer on the market o n n n 1976 - Cray-1 computer, 80 Mhz Workstations Personal computers Laptops