VMEbus A tutorial B Satyanarayana Department of High

VMEbus: A tutorial B. Satyanarayana Department of High Energy Physics TIFR, Mumbai, INDIA bsn@tifr. res. in VMEbus: A tutorial by B. Satyanarayana

Introduction to the VMEbus v Acronym for Versa Module Europa v High performance Eurocard standard TTL based backplane bus v Suitable for Single or multiple microprocessors v A completely memory mapped scheme v Introduced by Motorola, Phillips, Thompson and Mostek in 1981 v Released by VMEbus International Trade Association(VITA) in 1982 v Approved by IEEE and ANSI in 1987 2/25/2021 VMEbus: A tutorial by B. Satyanarayana 2

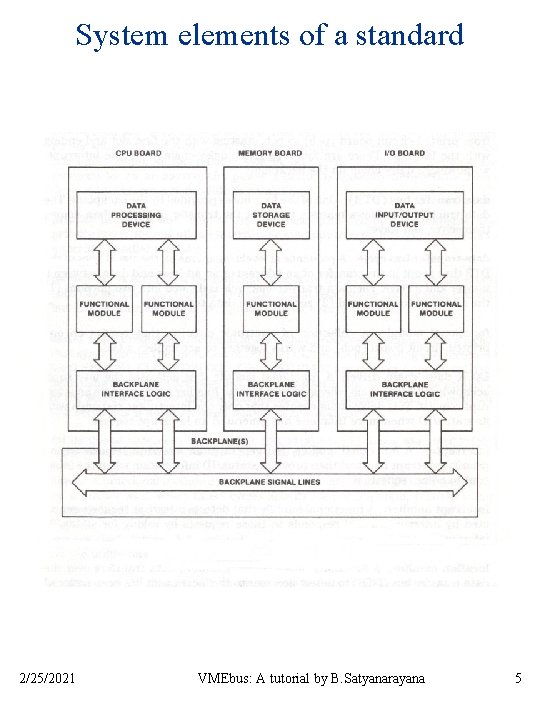

Interface standard An interfacing system used to interconnect data processing, data storage and peripheral control devices in a tightly coupled hardware configuration v Objectives: q To allow communication between devices on the bus without disturbing the internal activities of other devices interfaced to the bus q To specify the electrical and mechanical system characteristics required to design devices q To specify protocols that precisely define interaction between the bus and the devices interfaced to it q To provide terminology and definitions that describe system protocols q To allow a broad range of design latitude so that the designer can optimise cost and performance without affecting the system compatibility q To provide a system where performance is primarily device limited, rather than system interface limited 2/25/2021 VMEbus: A tutorial by B. Satyanarayana 3

Interface system elements v Mechanical specification describes the physical dimensions of subracks, backplanes, front panels, plug-in boards etc. q Backplane q Board q Slot q Subrack v Functional specification describes the manner in which the bus operates, the functional modules that are involved in each transaction and the rules that govern their behaviour q Requester, arbiter and arbitration bus q Backplane interface bus q Bus timer, serial clock driver and system clock driver q Daisy chain and IACK daisy chain driver q Data transfer bus and data transfer cycle q Functional module q Interrupter, interrupt handler and priority interrupt bus q Location monitor, power monitor & system controller q Master, slave and utility bus 2/25/2021 VMEbus: A tutorial by B. Satyanarayana 4

System elements of a standard 2/25/2021 VMEbus: A tutorial by B. Satyanarayana 5

Types of bus cycles v Read cycle v Write cycle v Block read cycle v Block write cycle v Read-modify-write cycle v Address-only cycle v Interrupt acknowledge cycle 2/25/2021 VMEbus: A tutorial by B. Satyanarayana 6

Basic structure v Data transfer bus q Supports 8/16/32 -bit transfers over a non-multiplexed 32 -bit data and address highway q Transfer protocols are synchronous and fully handshaken (Data transfer rate about 20 MBytes/sec) v Priority interrupts bus q Provides real-time interrupt services v Arbitration bus q Allocation of bus mastership q Allows round robin and prioritized arbitration algorithms v Utility bus q Provides with power-up and power-down synchronisation 2/25/2021 VMEbus: A tutorial by B. Satyanarayana 7

Other bus specifications v Specification diagrams q Timing diagrams q Sequence diagrams q Flow diagrams v Terminology q Rule q Recommendation q Suggestion q Permission q Observation v Protocol q Interlocked bus signal q Broadcast bus signal v System examples and explanations 2/25/2021 VMEbus: A tutorial by B. Satyanarayana 8

- Slides: 8