VME test card for VMEACETTC interface for CMX

- Slides: 4

VME test card for VME/ACE/TTC interface for CMX Yuri Ermoline Level-1 Calorimeter Trigger General Meeting, CERN December 15, 2011

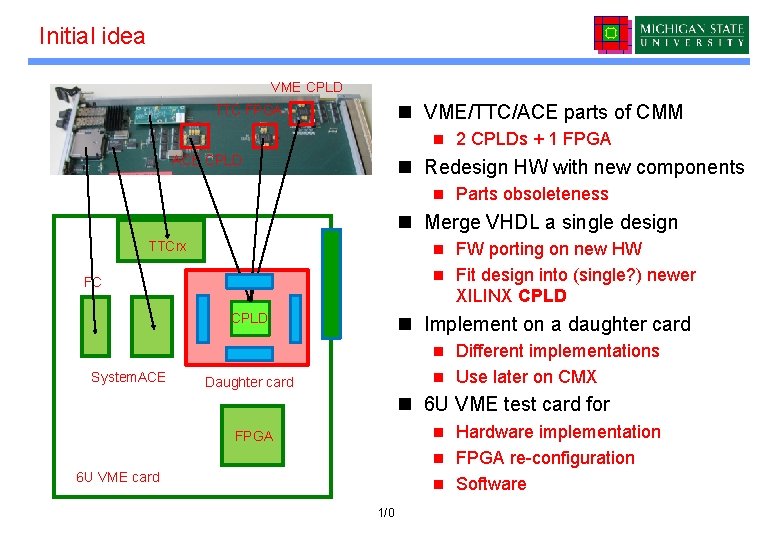

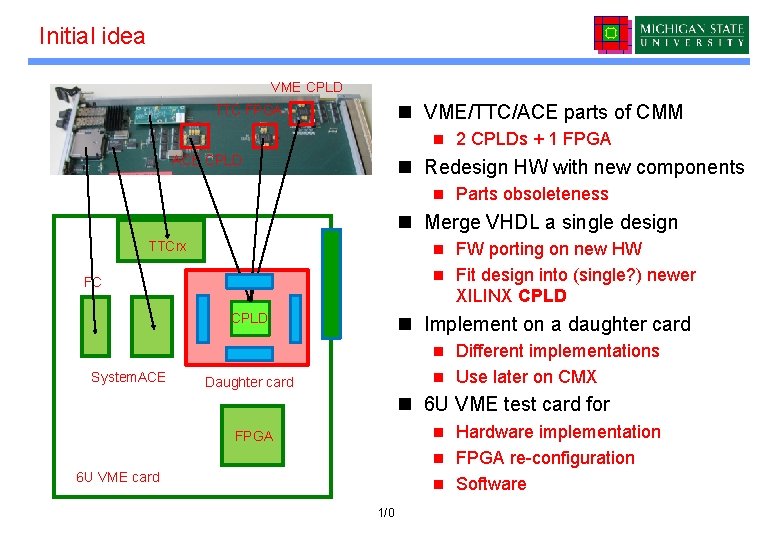

Initial idea VME CPLD n VME/TTC/ACE parts of CMM TTC FPGA n ACE CPLD 2 CPLDs + 1 FPGA n Redesign HW with new components n Parts obsoleteness n Merge VHDL a single design TTCrx FW porting on new HW n Fit design into (single? ) newer XILINX CPLD n FC CPLD n Implement on a daughter card Different implementations n Use later on CMX n System. ACE Daughter card n 6 U VME test card for Hardware implementation n FPGA re-configuration n Software n FPGA 6 U VME card 1/0

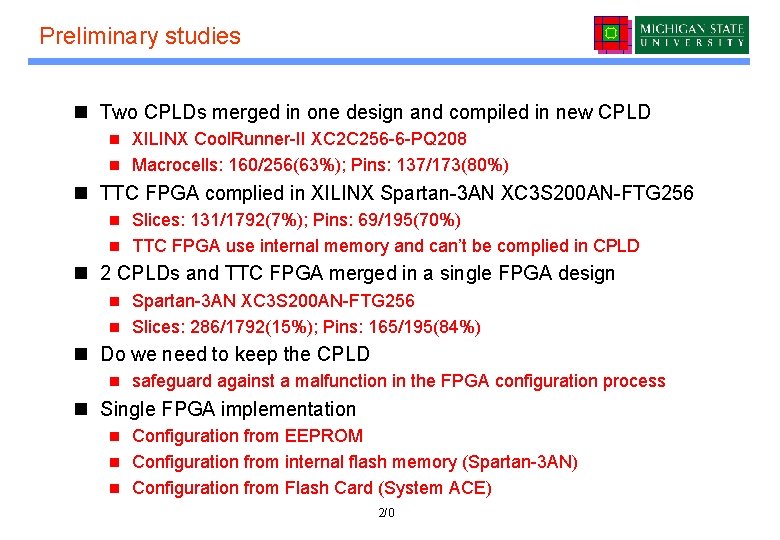

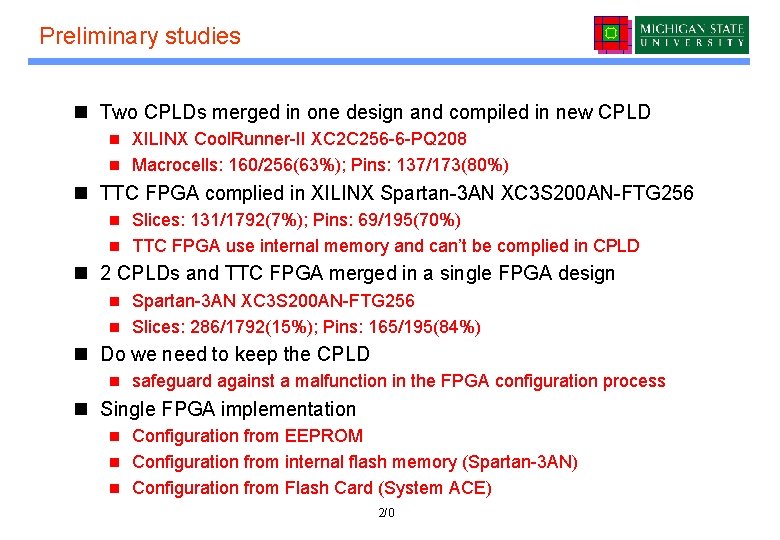

Preliminary studies n Two CPLDs merged in one design and compiled in new CPLD XILINX Cool. Runner-II XC 2 C 256 -6 -PQ 208 n Macrocells: 160/256(63%); Pins: 137/173(80%) n n TTC FPGA complied in XILINX Spartan-3 AN XC 3 S 200 AN-FTG 256 Slices: 131/1792(7%); Pins: 69/195(70%) n TTC FPGA use internal memory and can’t be complied in CPLD n n 2 CPLDs and TTC FPGA merged in a single FPGA design Spartan-3 AN XC 3 S 200 AN-FTG 256 n Slices: 286/1792(15%); Pins: 165/195(84%) n n Do we need to keep the CPLD n safeguard against a malfunction in the FPGA configuration process n Single FPGA implementation Configuration from EEPROM n Configuration from internal flash memory (Spartan-3 AN) n Configuration from Flash Card (System ACE) n 2/0

Next steps n Development process: CADENCE schematics of the 6 U VME card based on CMM schematics n Launch PCB layout/production/assembly n Design daughter card(s) n In parallel work on FW n n Different daughter card implementations CPLD (Cool. Runner-II) + FPGA (Spartan-3 AN) n Single FPGA (Spartan-3 AN) n n Test of FPGA configuration failure n Procedure? n Re-configuration On time-out? n Via DCS? n 3/0