VLSI TESTING PROJECT Dominance Fault Collapsing Anandshankar Mudlapur

- Slides: 20

VLSI TESTING PROJECT Dominance Fault Collapsing Anandshankar Mudlapur Arun Balaji Kannan Muthu Balaji Ramkumar Muthu Balan Varadharajaperumal Dominance Fault Collapsing 1

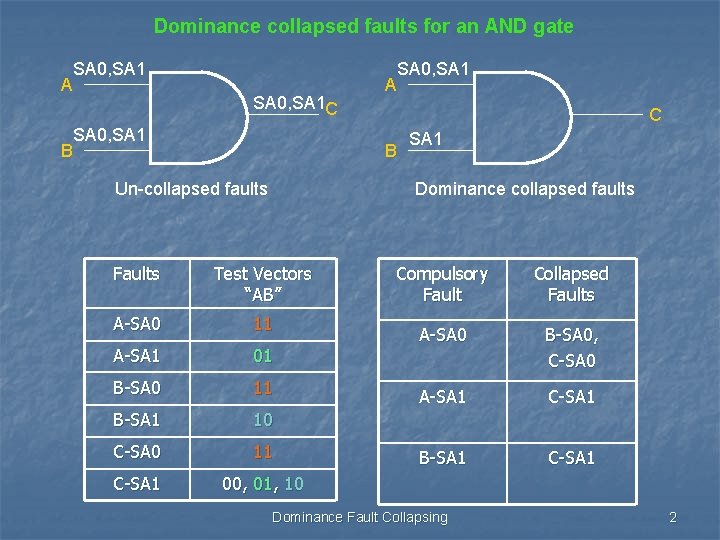

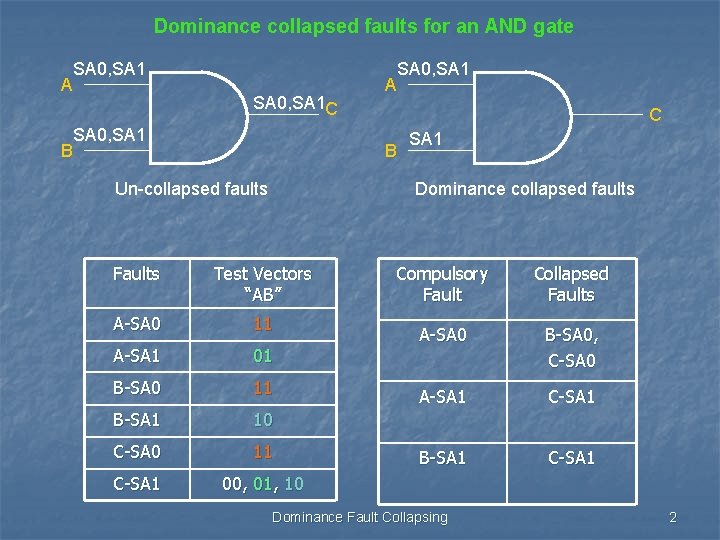

Dominance collapsed faults for an AND gate A B SA 0, SA 1 C SA 0, SA 1 A C B Un-collapsed faults SA 0, SA 1 Dominance collapsed faults Faults Test Vectors “AB” A-SA 0 11 A-SA 1 01 B-SA 0 11 B-SA 1 10 C-SA 0 11 C-SA 1 00, 01, 10 Compulsory Fault Collapsed Faults A-SA 0 B-SA 0, C-SA 0 A-SA 1 C-SA 1 B-SA 1 C-SA 1 Dominance Fault Collapsing 2

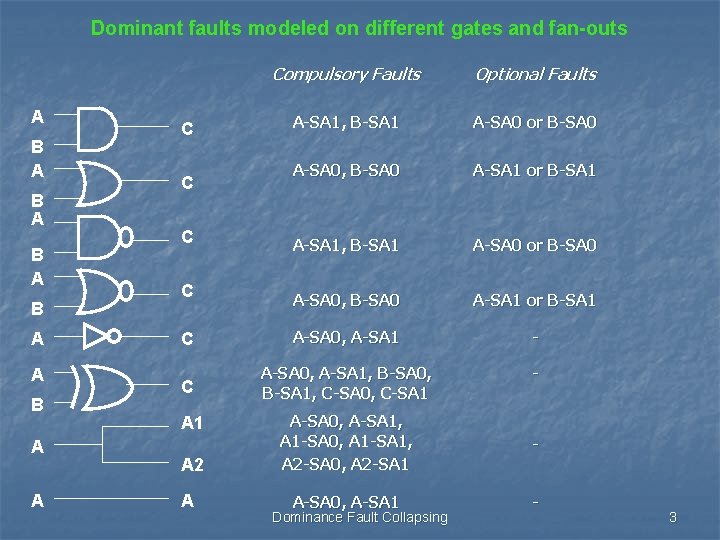

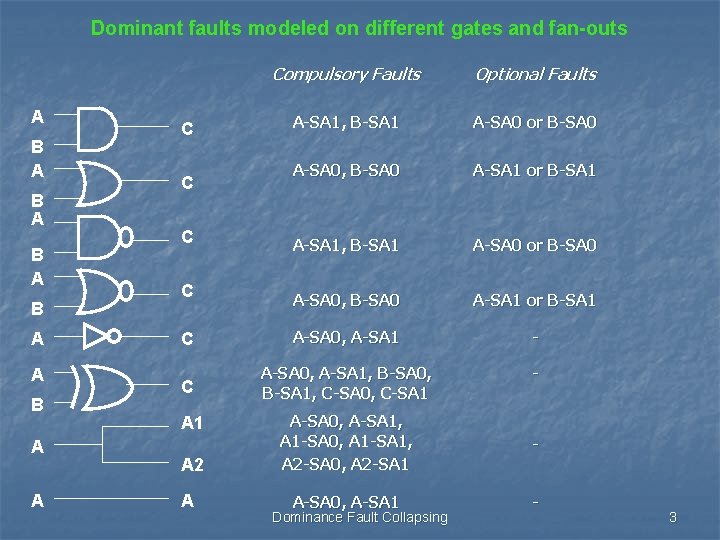

Dominant faults modeled on different gates and fan-outs A B A B A A Compulsory Faults Optional Faults A-SA 1, B-SA 1 A-SA 0 or B-SA 0 A-SA 0, B-SA 0 A-SA 1 or B-SA 1 C A-SA 0, A-SA 1 - C A-SA 0, A-SA 1, B-SA 0, B-SA 1, C-SA 0, C-SA 1 - C C A 1 A 2 A A-SA 0, A-SA 1, A 1 -SA 0, A 1 -SA 1, A 2 -SA 0, A 2 -SA 1 - A-SA 0, A-SA 1 - Dominance Fault Collapsing 3

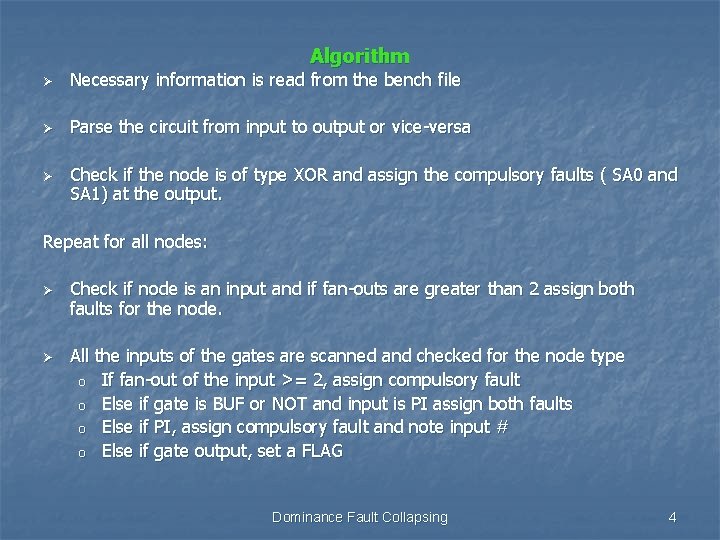

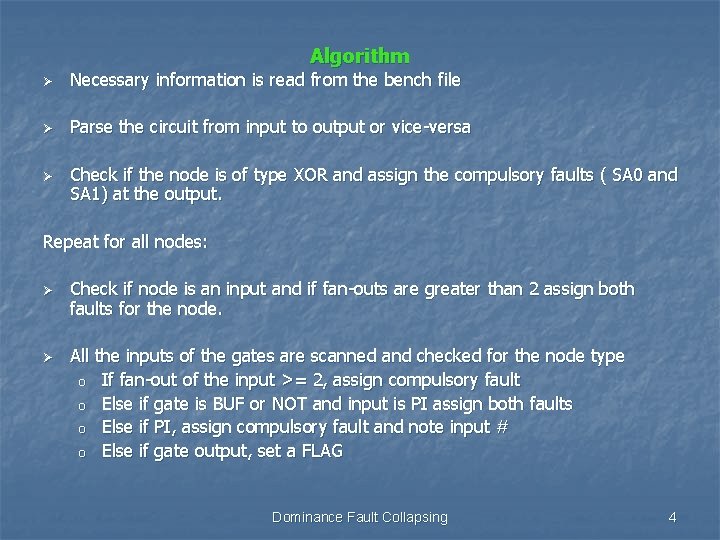

Algorithm Ø Necessary information is read from the bench file Ø Parse the circuit from input to output or vice-versa Ø Check if the node is of type XOR and assign the compulsory faults ( SA 0 and SA 1) at the output. Repeat for all nodes: Ø Ø Check if node is an input and if fan-outs are greater than 2 assign both faults for the node. All the inputs of the gates are scanned and checked for the node type o If fan-out of the input >= 2, assign compulsory fault o Else if gate is BUF or NOT and input is PI assign both faults o Else if PI, assign compulsory fault and note input # o Else if gate output, set a FLAG Dominance Fault Collapsing 4

Algorithm Continued… Ø Ø Check if FLAG is unchanged and if no primary inputs are encountered; assign the optional fault to the last input Else if FLAG is unchanged; assign the optional fault to the PI End Loop Ø If PO has fan-outs; both faults are assigned Ø The result obtained is saved! Dominance Fault Collapsing 5

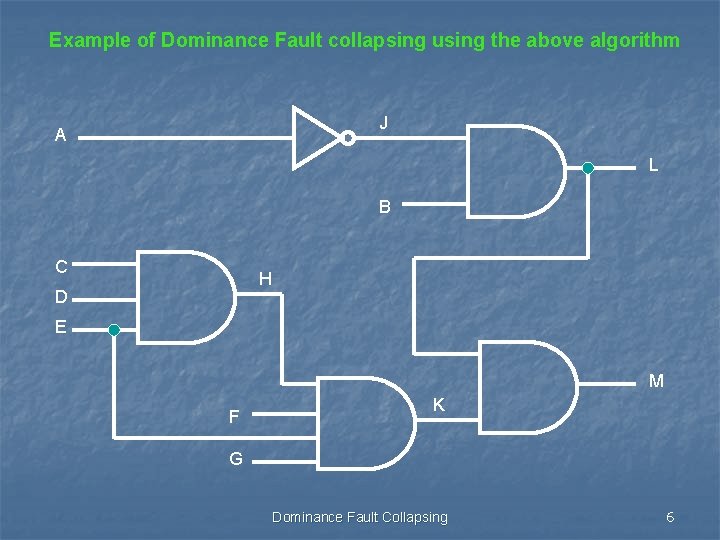

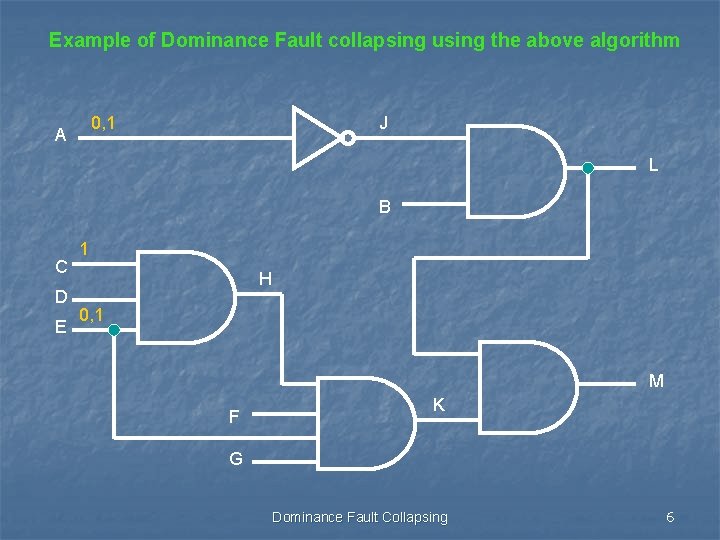

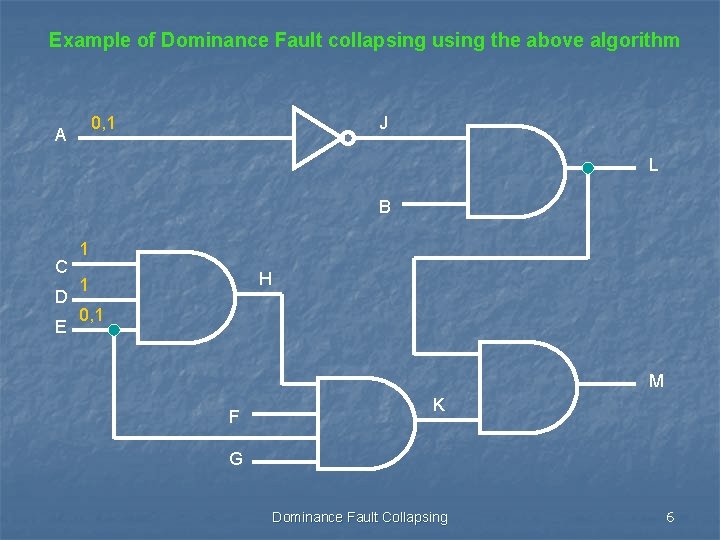

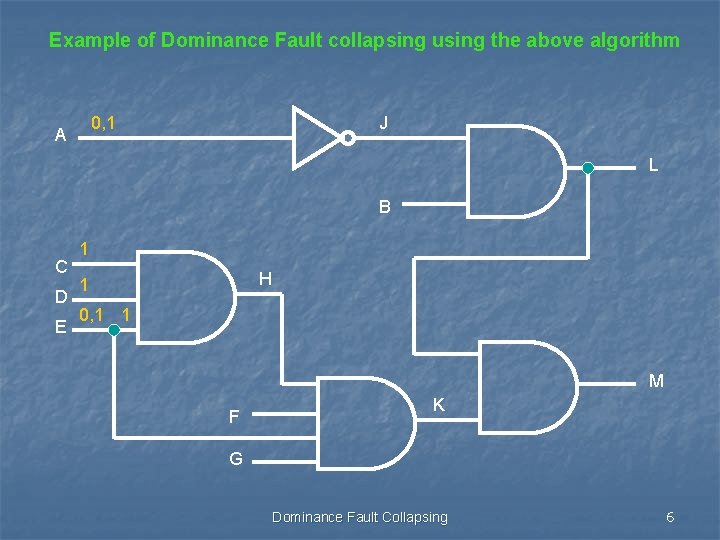

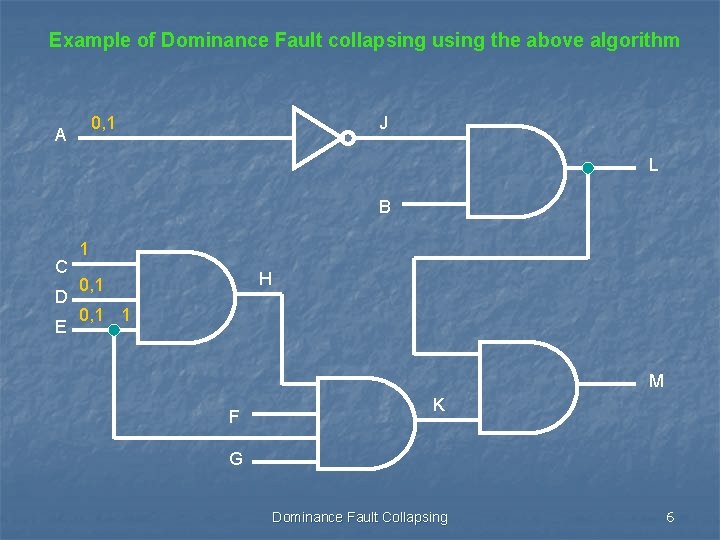

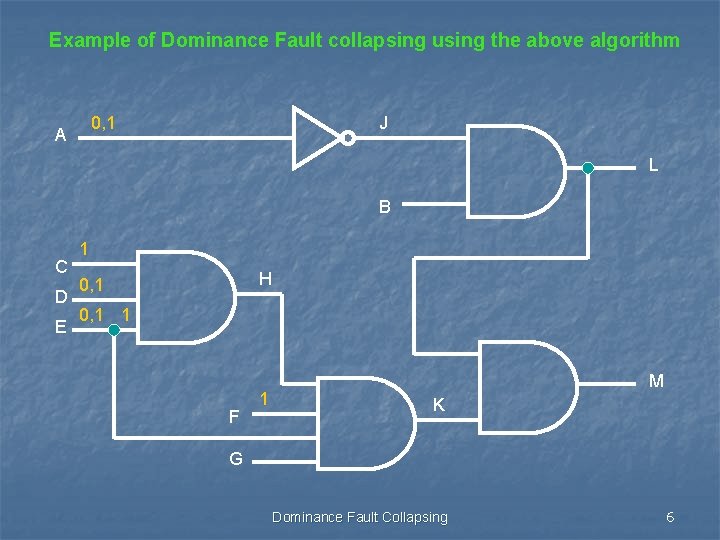

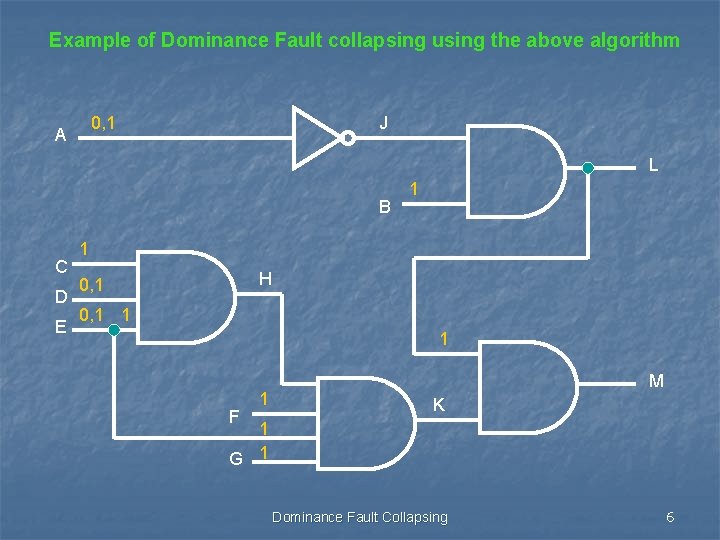

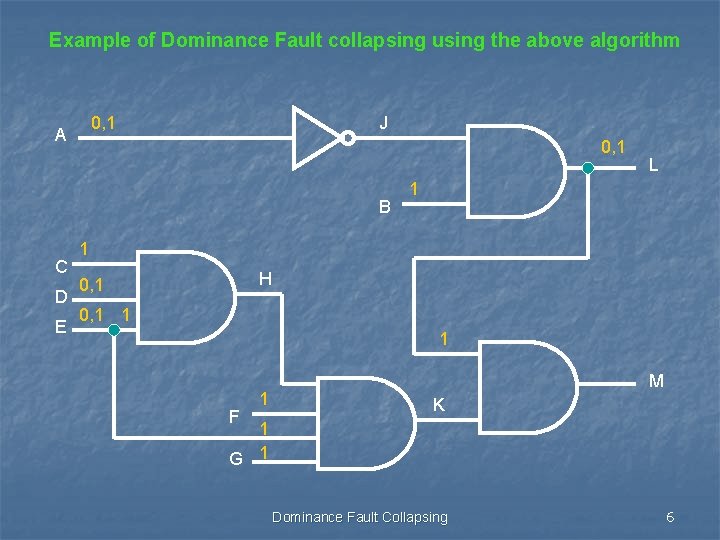

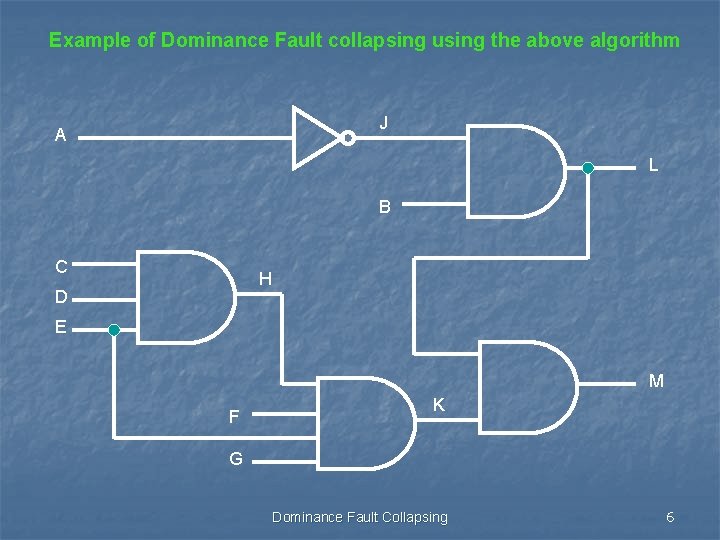

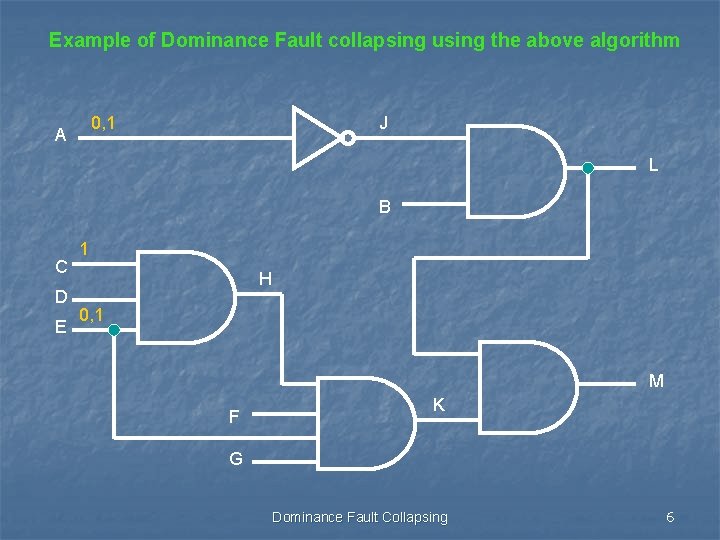

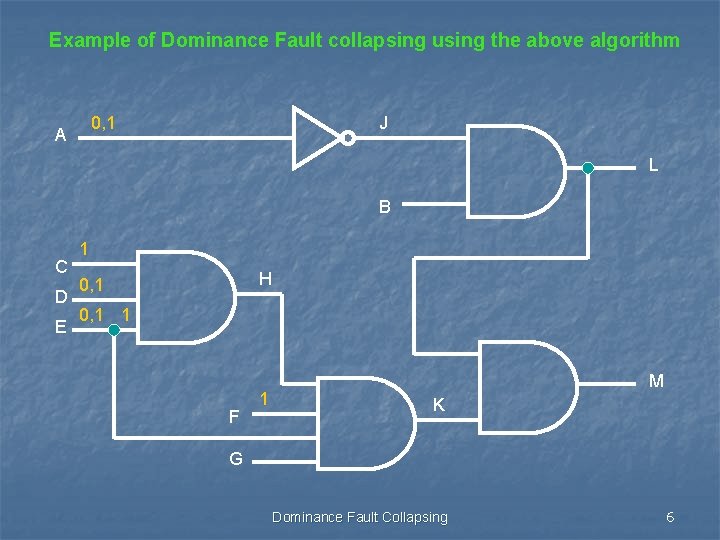

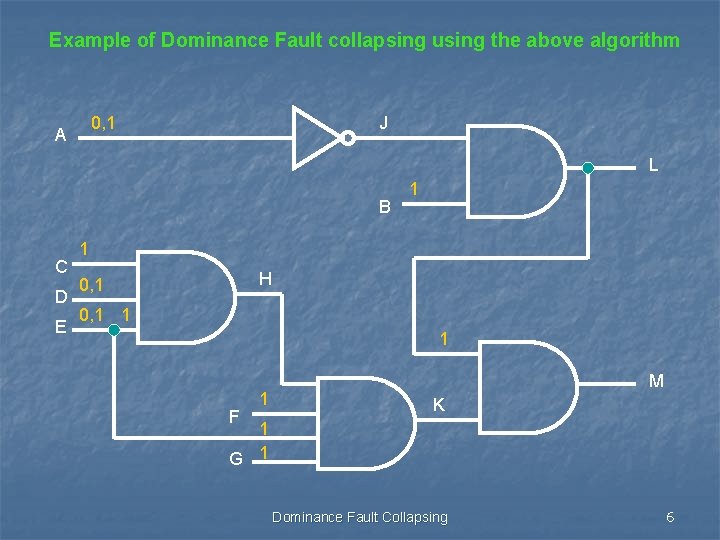

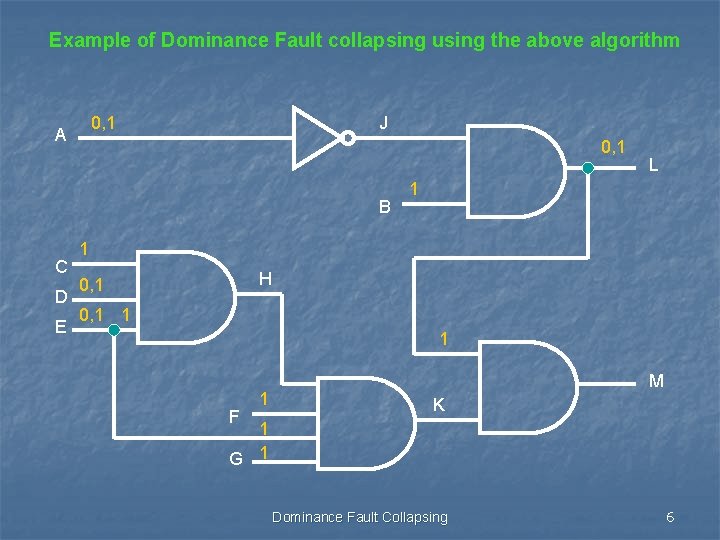

Example of Dominance Fault collapsing using the above algorithm J A L B C H D E M F K G Dominance Fault Collapsing 6

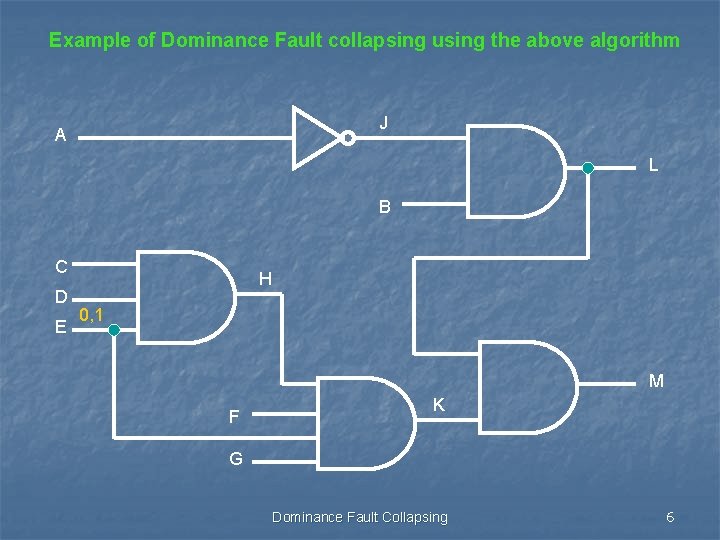

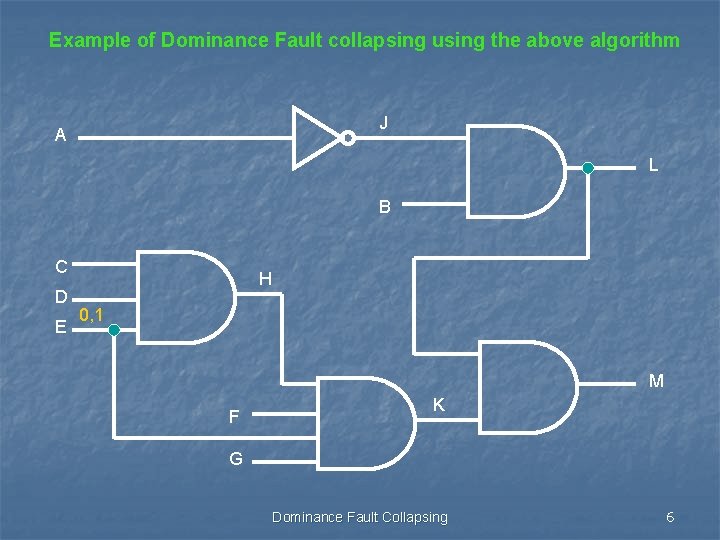

Example of Dominance Fault collapsing using the above algorithm J A L B C D E H 0, 1 M F K G Dominance Fault Collapsing 6

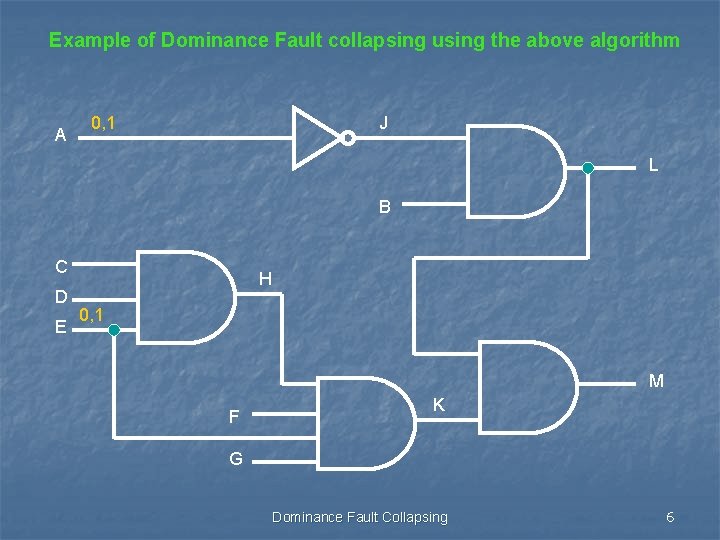

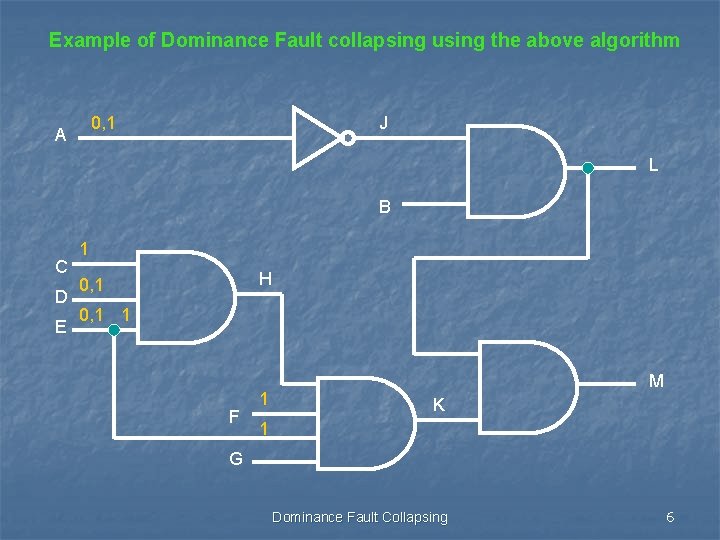

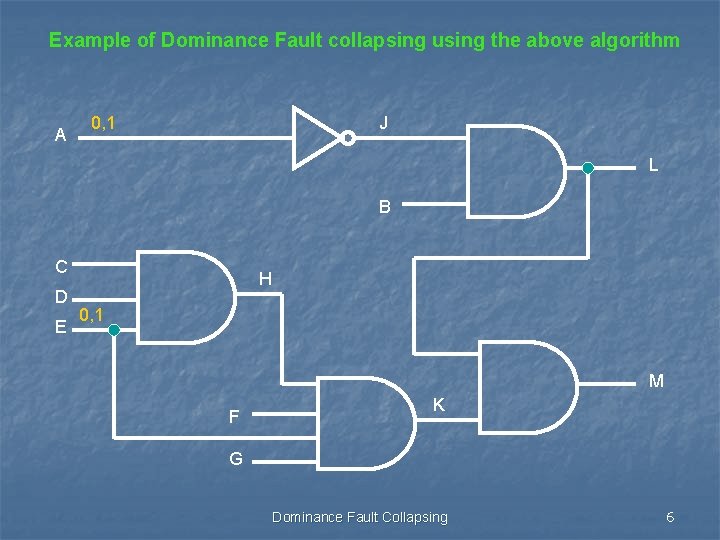

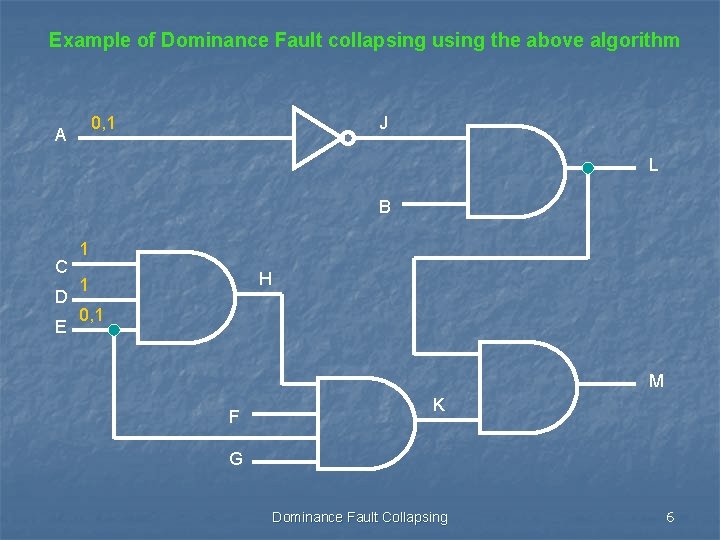

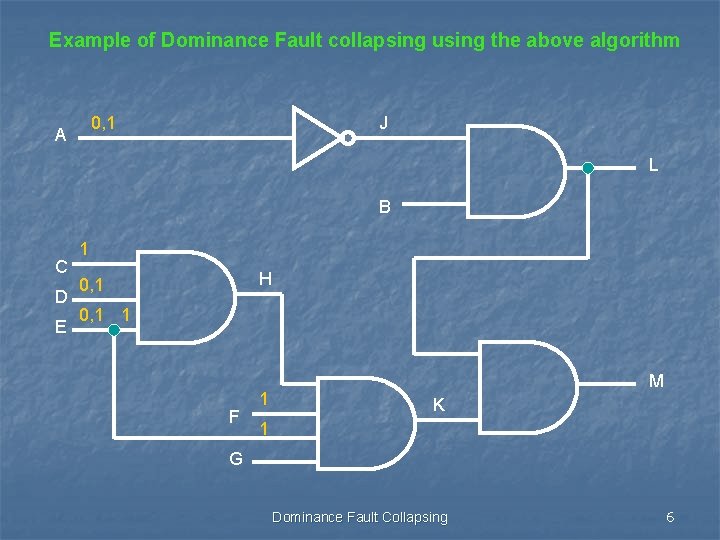

Example of Dominance Fault collapsing using the above algorithm A 0, 1 J L B C D E H 0, 1 M F K G Dominance Fault Collapsing 6

Example of Dominance Fault collapsing using the above algorithm 0, 1 A J L B C D E 1 H 0, 1 M F K G Dominance Fault Collapsing 6

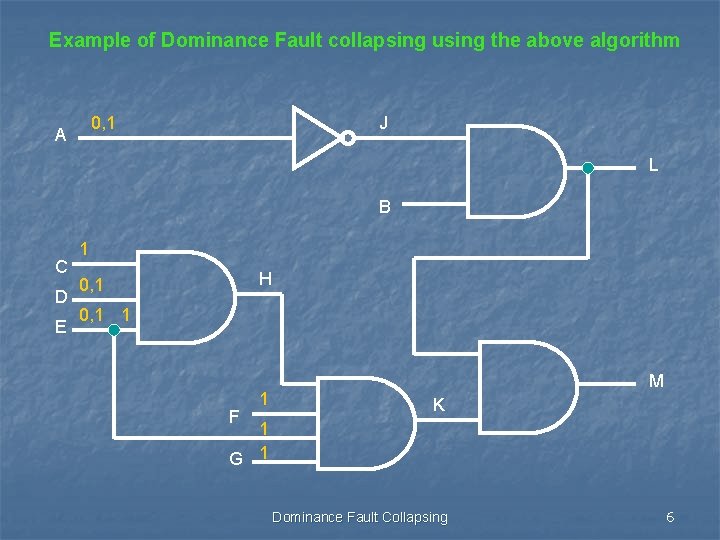

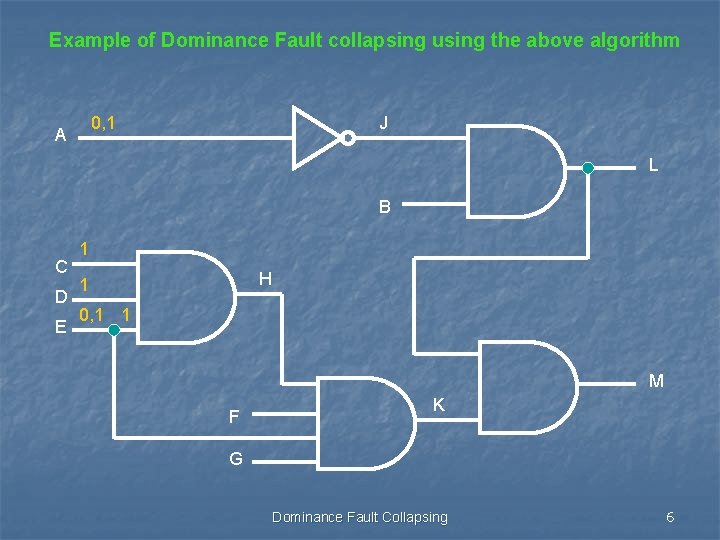

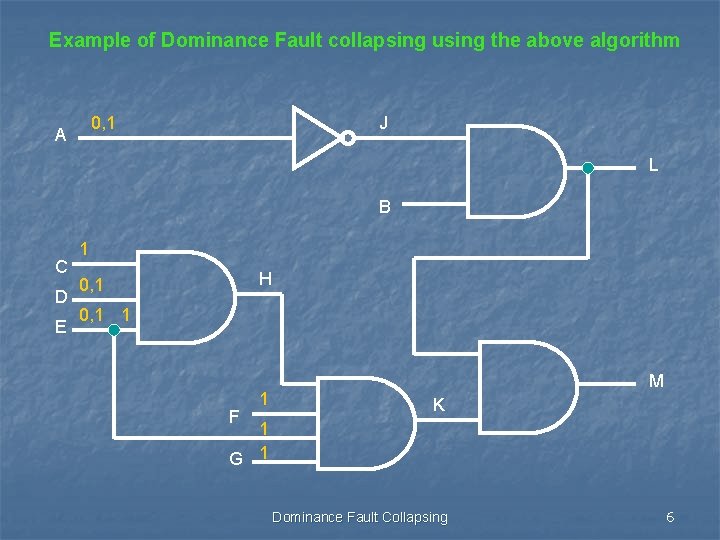

Example of Dominance Fault collapsing using the above algorithm 0, 1 A J L B C D E 1 H 1 0, 1 M F K G Dominance Fault Collapsing 6

Example of Dominance Fault collapsing using the above algorithm 0, 1 A J L B C D E 1 H 1 0, 1 1 M F K G Dominance Fault Collapsing 6

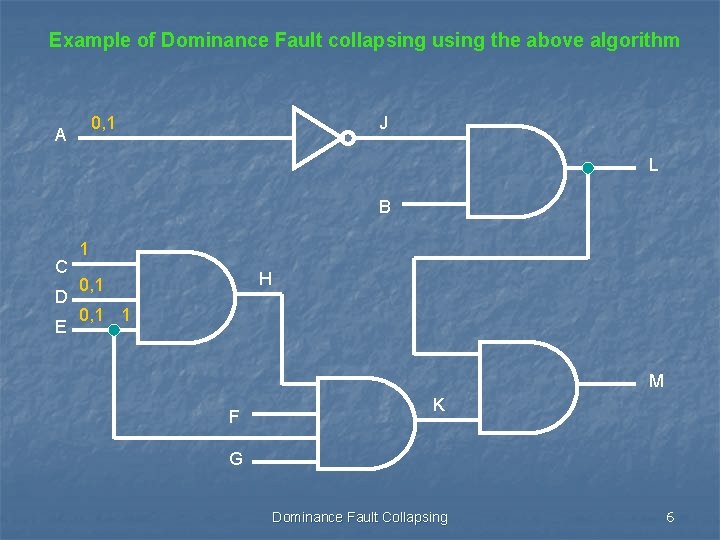

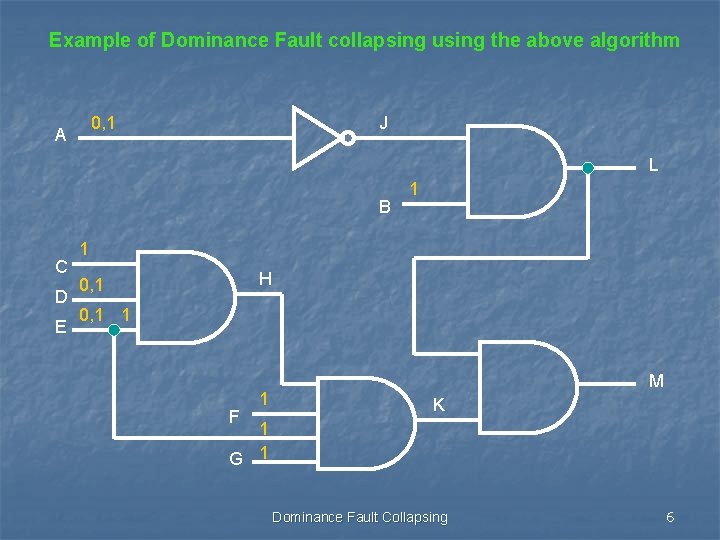

Example of Dominance Fault collapsing using the above algorithm 0, 1 A J L B C D E 1 H 0, 1 1 M F K G Dominance Fault Collapsing 6

Example of Dominance Fault collapsing using the above algorithm 0, 1 A J L B C D E 1 H 0, 1 1 F 1 M K G Dominance Fault Collapsing 6

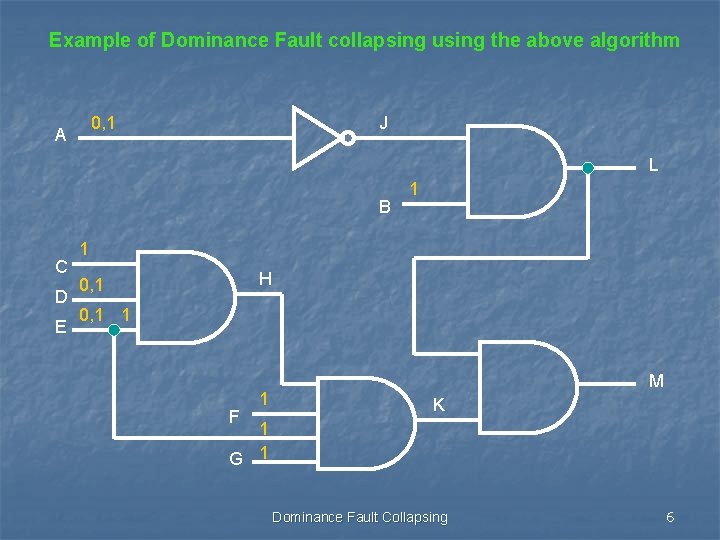

Example of Dominance Fault collapsing using the above algorithm 0, 1 A J L B C D E 1 H 0, 1 1 F 1 M K 1 G Dominance Fault Collapsing 6

Example of Dominance Fault collapsing using the above algorithm 0, 1 A J L B C D E 1 H 0, 1 1 F 1 M K 1 G 1 Dominance Fault Collapsing 6

Example of Dominance Fault collapsing using the above algorithm 0, 1 A J L B C D E 1 1 H 0, 1 1 F 1 M K 1 G 1 Dominance Fault Collapsing 6

Example of Dominance Fault collapsing using the above algorithm 0, 1 A J L B C D E 1 1 H 0, 1 1 1 F 1 M K 1 G 1 Dominance Fault Collapsing 6

Example of Dominance Fault collapsing using the above algorithm 0, 1 A J 0, 1 B C D E L 1 1 H 0, 1 1 1 F 1 M K 1 G 1 Dominance Fault Collapsing 6

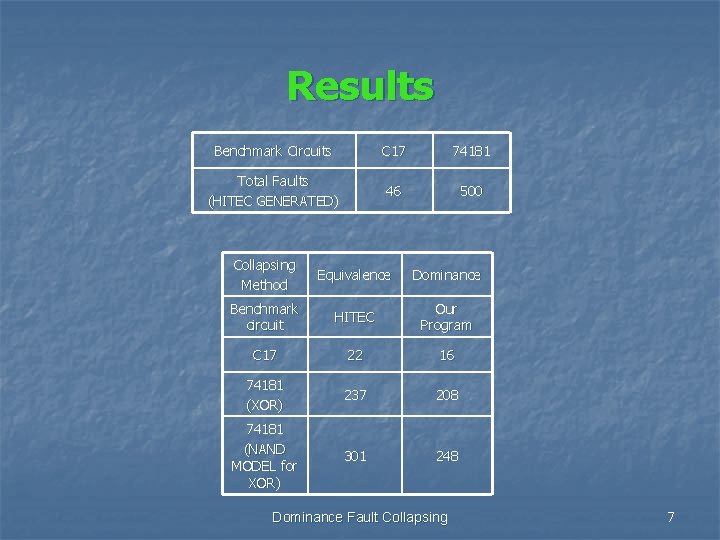

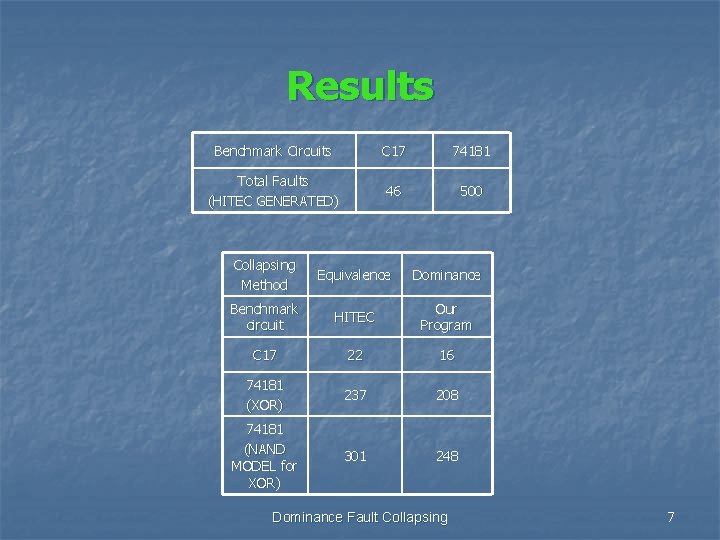

Results Benchmark Circuits C 17 74181 Total Faults (HITEC GENERATED) 46 500 Collapsing Method Equivalence Dominance Benchmark circuit HITEC Our Program C 17 22 16 74181 (XOR) 237 208 74181 (NAND MODEL for XOR) 301 248 Dominance Fault Collapsing 7

Conclusion As a conclusion, q Results may coincidentally match! q A Double check on the results : always advisable q Plan what you do, do what you plan and record what you have accomplished! Dominance Fault Collapsing 8