VLSI Testing Lecture 8 Sequential ATPG Dr Vishwani

- Slides: 21

VLSI Testing Lecture 8: Sequential ATPG Dr. Vishwani D. Agrawal James J. Danaher Professor of Electrical and Computer Engineering Auburn University, Alabama 36849, USA vagrawal@eng. auburn. edu http: //www. eng. auburn. edu/~vagrawal IIT Delhi, Aug 21, 2013, 3: 30 -4: 30 PM Copyright 2001, Agrawal & Bushnell Lecture 8: Sequential ATPG 1

Contents n n Problem of sequential circuit ATPG Time-frame expansion n n n Nine-valued logic ATPG implementation and drivability Complexity of ATPG Cycle-free and cyclic circuits Asynchronous circuits Summary Copyright 2001, Agrawal & Bushnell Lecture 8: Sequential ATPG 2

Sequential Circuits n n A sequential circuit has memory in addition to combinational logic. Test for a fault in a sequential circuit is a sequence of vectors, which n n Initializes the circuit to a known state Activates the fault, and Propagates the fault effect to a primary output Methods of sequential circuit ATPG n n Time-frame expansion methods Simulation-based methods Copyright 2001, Agrawal & Bushnell Lecture 8: Sequential ATPG 3

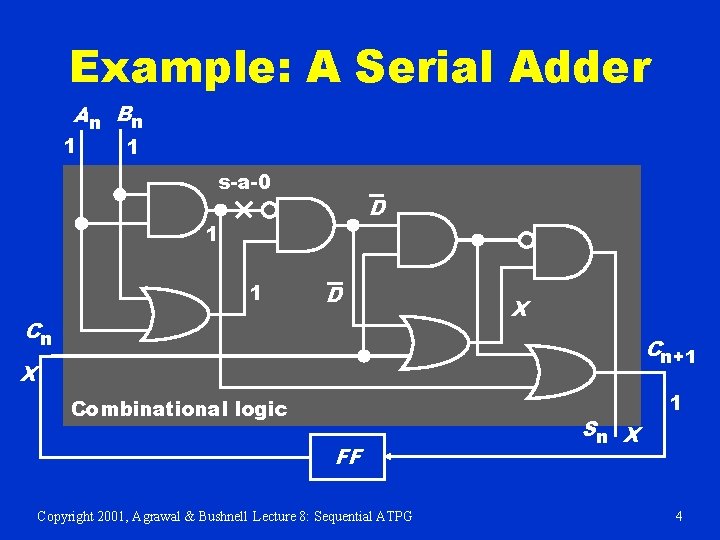

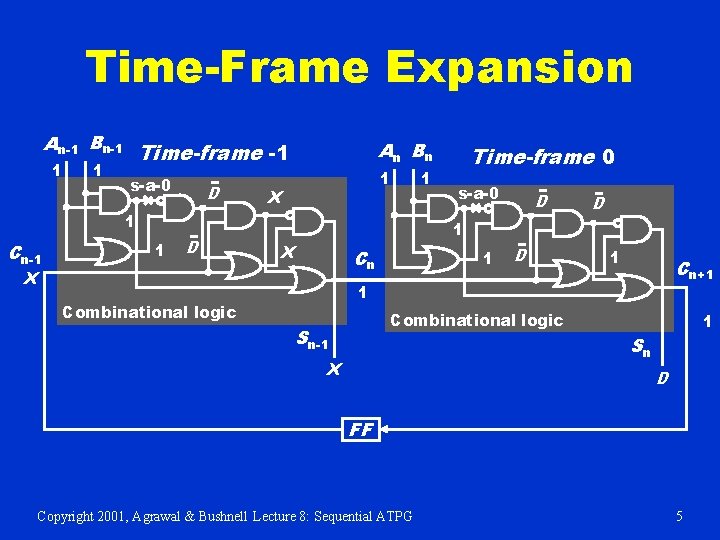

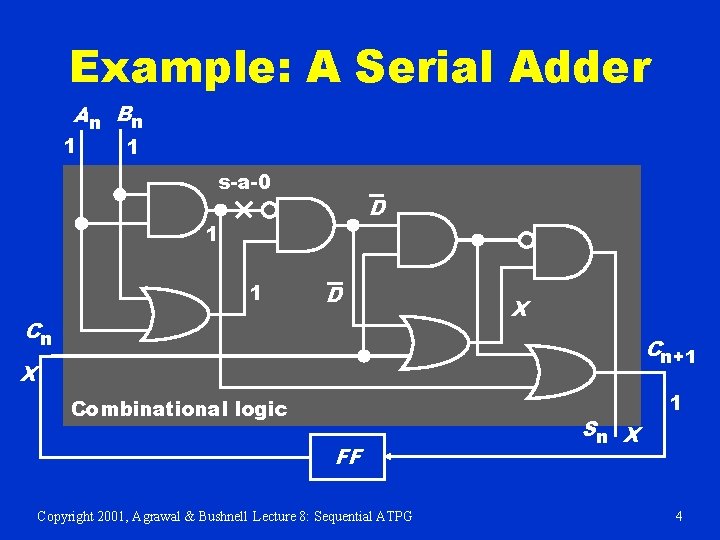

Example: A Serial Adder An Bn 1 1 s-a-0 D 1 1 D Cn X Cn+1 X Combinational logic FF Copyright 2001, Agrawal & Bushnell Lecture 8: Sequential ATPG Sn X 1 4

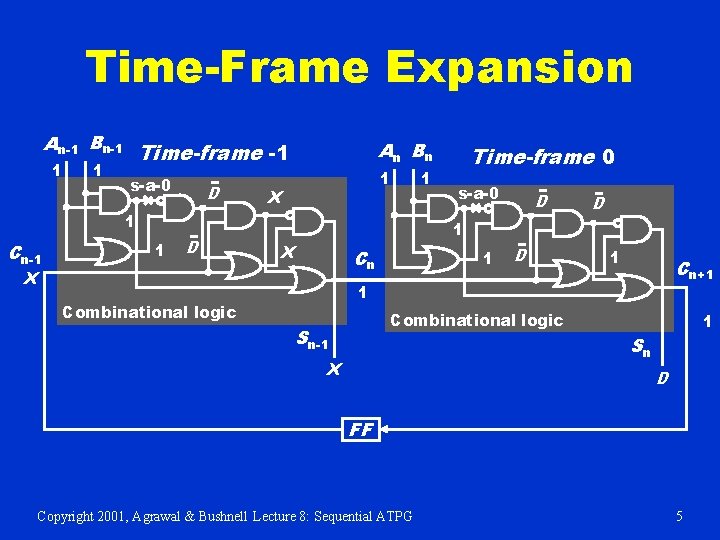

Time-Frame Expansion An-1 Bn-1 1 1 An Bn Time-frame -1 s-a-0 D 1 X 1 1 Cn-1 1 D Time-frame 0 s-a-0 D D 1 X Cn X 1 D 1 Cn+1 1 Combinational logic Sn-1 1 Sn X D FF Copyright 2001, Agrawal & Bushnell Lecture 8: Sequential ATPG 5

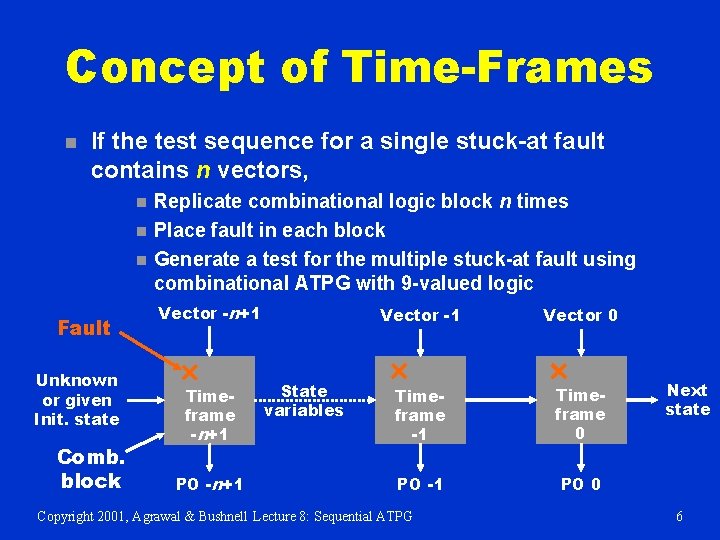

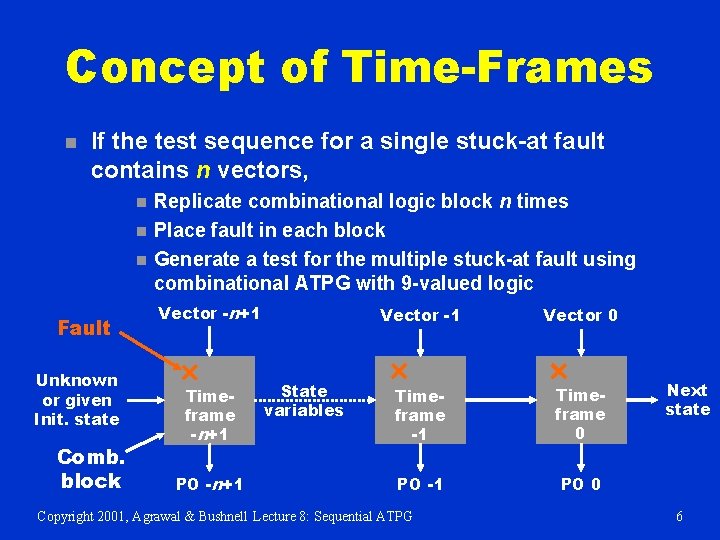

Concept of Time-Frames n If the test sequence for a single stuck-at fault contains n vectors, n n n Fault Unknown or given Init. state Comb. block Replicate combinational logic block n times Place fault in each block Generate a test for the multiple stuck-at fault using combinational ATPG with 9 -valued logic Vector -n+1 Timeframe -n+1 PO -n+1 State variables Vector -1 Vector 0 Timeframe -1 Timeframe 0 PO -1 PO 0 Copyright 2001, Agrawal & Bushnell Lecture 8: Sequential ATPG Next state 6

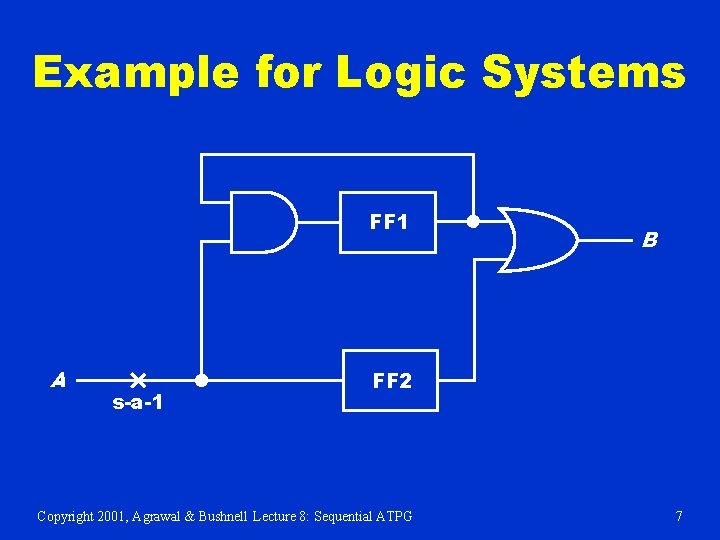

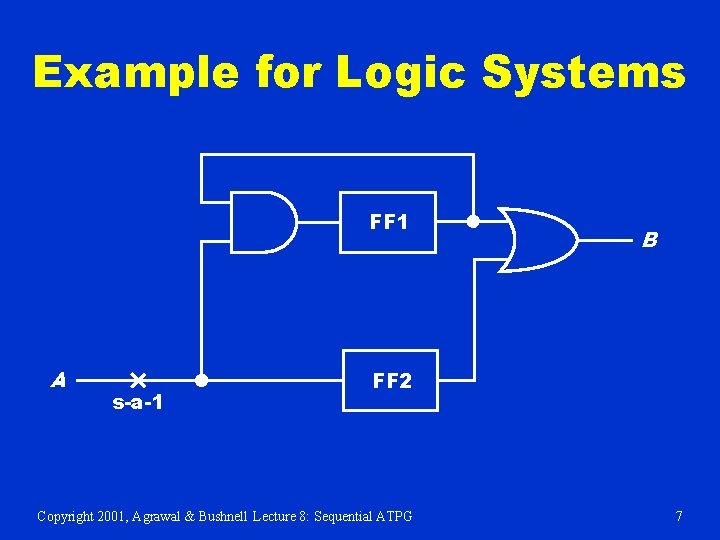

Example for Logic Systems FF 1 A s-a-1 B FF 2 Copyright 2001, Agrawal & Bushnell Lecture 8: Sequential ATPG 7

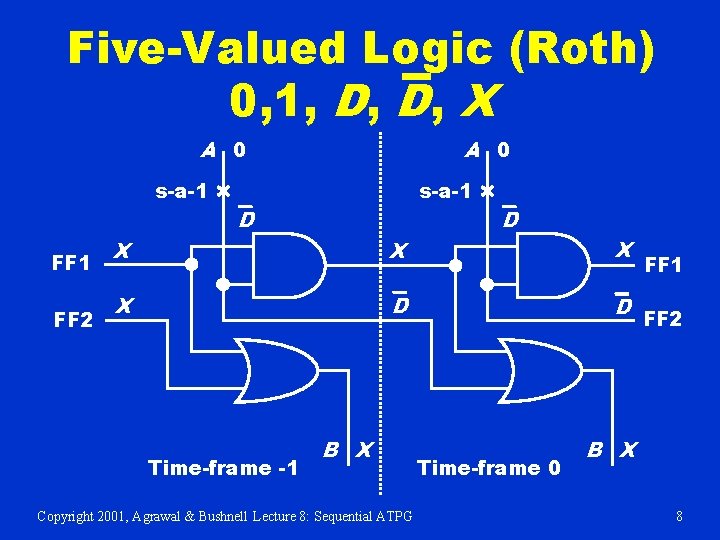

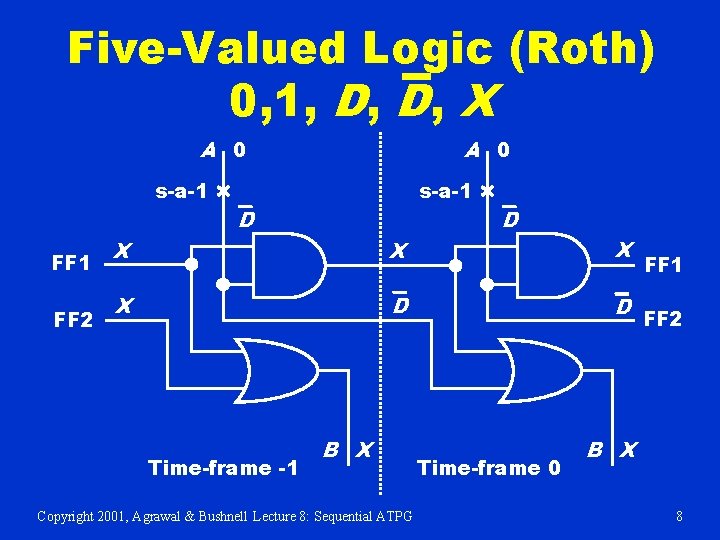

Five-Valued Logic (Roth) 0, 1, D, D, X A 0 s-a-1 FF 2 A 0 s-a-1 D D X X D D Time-frame -1 B X Copyright 2001, Agrawal & Bushnell Lecture 8: Sequential ATPG Time-frame 0 FF 1 FF 2 B X 8

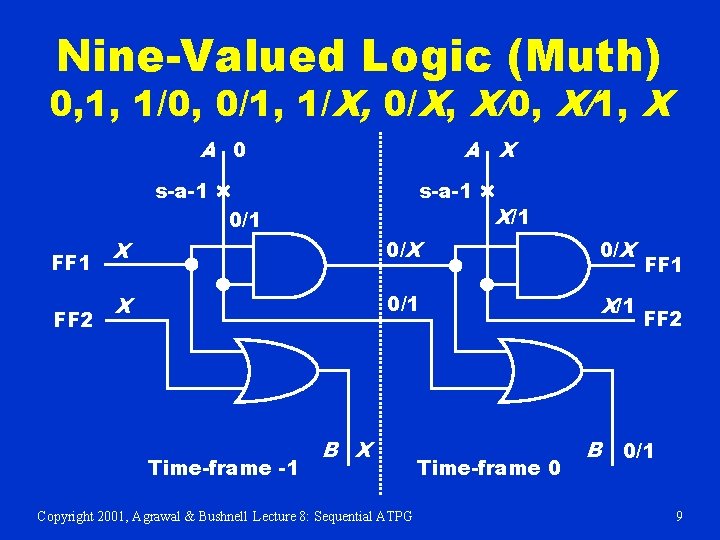

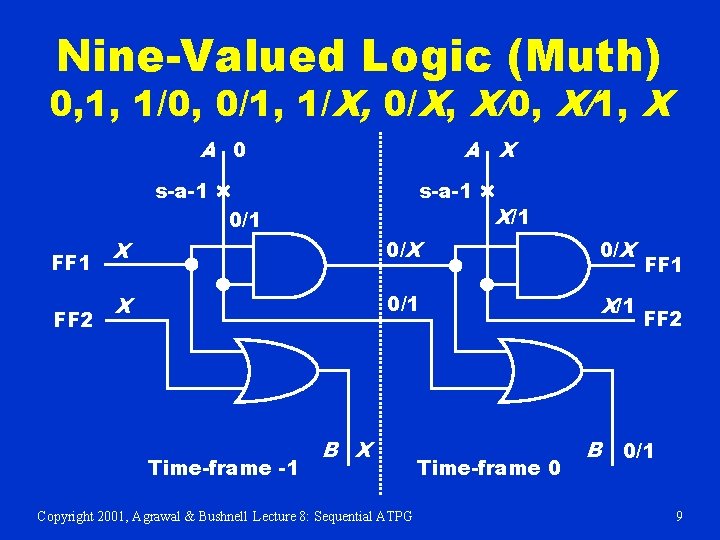

Nine-Valued Logic (Muth) 0, 1, 1/0, 0/1, 1/X, 0/X, X/0, X/1, X A 0 A X s-a-1 0/1 FF 2 X/1 X 0/X X 0/1 X/1 Time-frame -1 B X Copyright 2001, Agrawal & Bushnell Lecture 8: Sequential ATPG Time-frame 0 B FF 1 FF 2 0/1 9

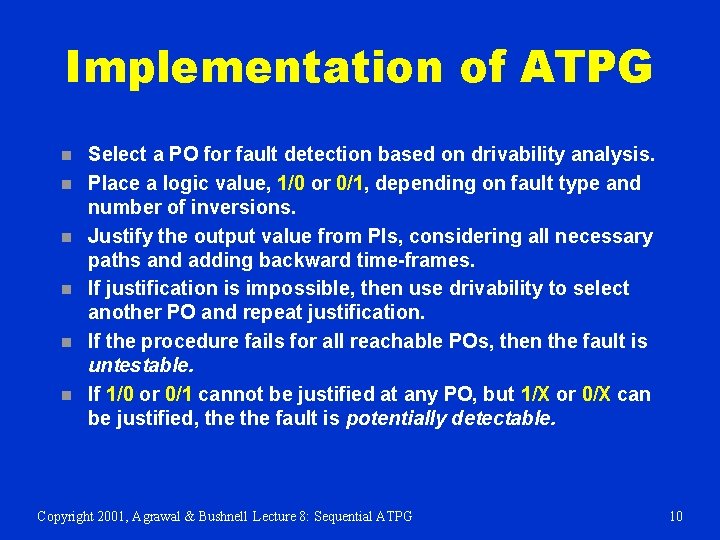

Implementation of ATPG n n n Select a PO for fault detection based on drivability analysis. Place a logic value, 1/0 or 0/1, depending on fault type and number of inversions. Justify the output value from PIs, considering all necessary paths and adding backward time-frames. If justification is impossible, then use drivability to select another PO and repeat justification. If the procedure fails for all reachable POs, then the fault is untestable. If 1/0 or 0/1 cannot be justified at any PO, but 1/X or 0/X can be justified, the fault is potentially detectable. Copyright 2001, Agrawal & Bushnell Lecture 8: Sequential ATPG 10

Drivability Example (10, 15) s-a-1 8 d(0/1) = d(1/0) = 20 8 d(0/1) = 4 d(1/0) = (10, 16) d(0/1) = 9 d(1/0) = FF (6, 10) d(0/1) = 109 d(1/0) = d(0/1) = d(1/0) = 32 (17, 11) d(0/1) = 120 d(1/0) = 27 8 (CC 0, CC 1) = (6, 4) (5, 9) 8 (4, 4) (22, 17) 8 (11, 16) CC 0 and CC 1 are SCOAP combinational controllabilities d(0/1) and d(1/0) of a line are effort measures for driving a specific fault effect to that line Copyright 2001, Agrawal & Bushnell Lecture 8: Sequential ATPG 11

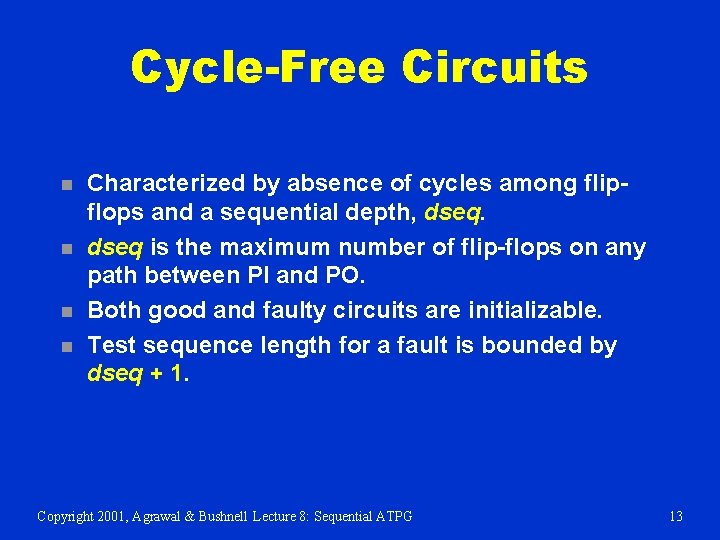

Complexity of ATPG § Synchronous circuit -- All flip-flops controlled by clocks; PI and PO synchronized with clock: § Cycle-free circuit – No feedback among flip-flops: Test generation for a fault needs no more than dseq + 1 timeframes, where dseq is the sequential depth. § Cyclic circuit – Contains feedback among flip-flops: May need 9 Nff time-frames, where Nff is the number of flipflops. Asynchronous circuit – Higher complexity! § Smax Time. Frame max-1 Time. Frame max-2 S 3 Time- S 2 Time- S 1 Time. Frame -2 -1 0 S 0 max = Number of distinct vectors with 9 -valued elements = 9 Nff Copyright 2001, Agrawal & Bushnell Lecture 8: Sequential ATPG 12

Cycle-Free Circuits n n Characterized by absence of cycles among flipflops and a sequential depth, dseq is the maximum number of flip-flops on any path between PI and PO. Both good and faulty circuits are initializable. Test sequence length for a fault is bounded by dseq + 1. Copyright 2001, Agrawal & Bushnell Lecture 8: Sequential ATPG 13

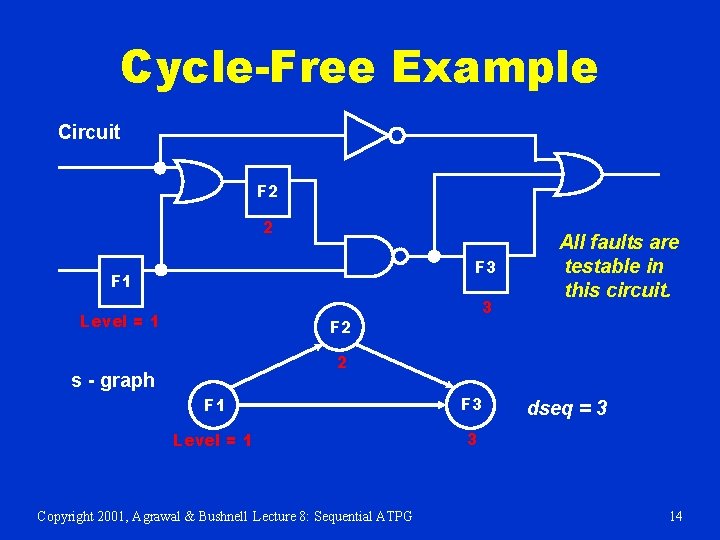

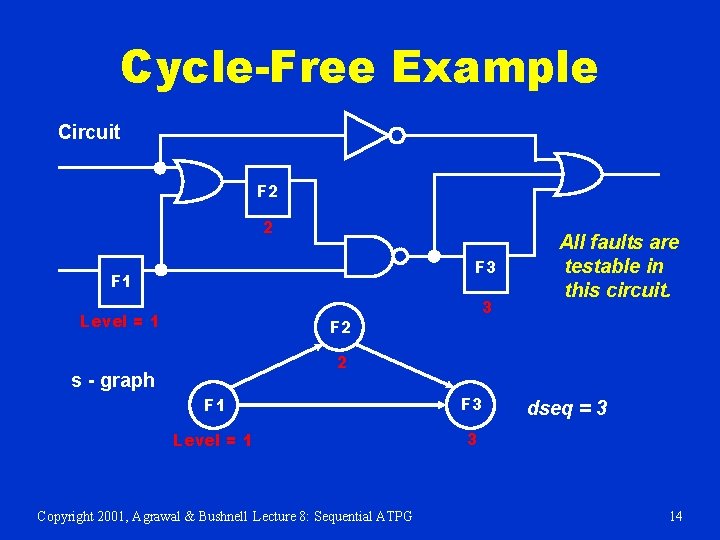

Cycle-Free Example Circuit F 2 2 F 3 F 1 Level = 1 3 F 2 All faults are testable in this circuit. 2 s - graph F 1 F 3 Level = 1 3 Copyright 2001, Agrawal & Bushnell Lecture 8: Sequential ATPG dseq = 3 14

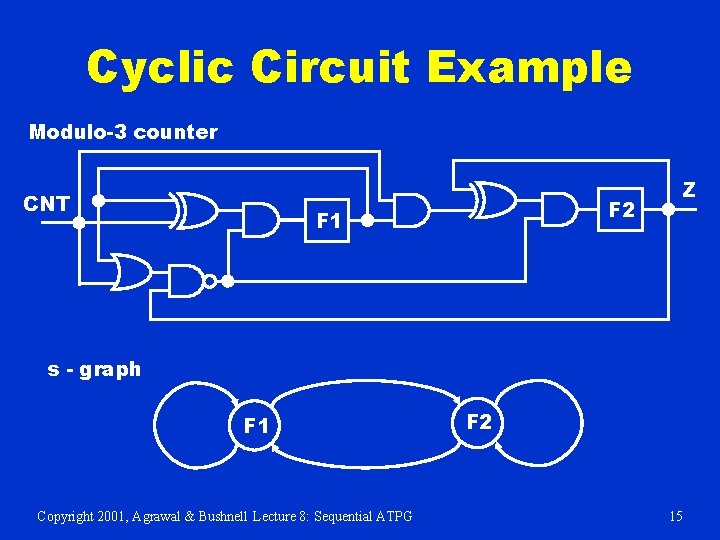

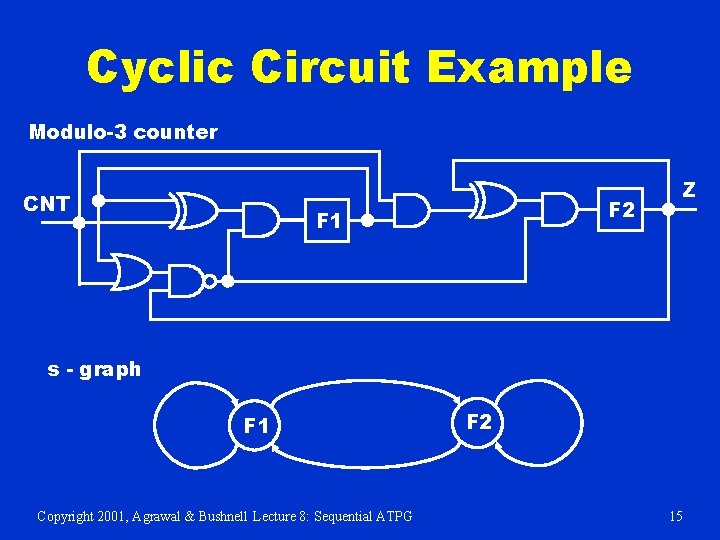

Cyclic Circuit Example Modulo-3 counter CNT F 2 F 1 Z s - graph F 1 Copyright 2001, Agrawal & Bushnell Lecture 8: Sequential ATPG F 2 15

Modulo-3 Counter n n n Cyclic structure – Sequential depth is undefined. Circuit is not initializable. No tests can be generated for any stuck-at fault. After expanding the circuit to 9 Nff = 81, or fewer, time-frames ATPG program calls any given target fault untestable. Circuit can only be functionally tested by multiple observations. Functional tests, when simulated, give no fault coverage. Copyright 2001, Agrawal & Bushnell Lecture 8: Sequential ATPG 16

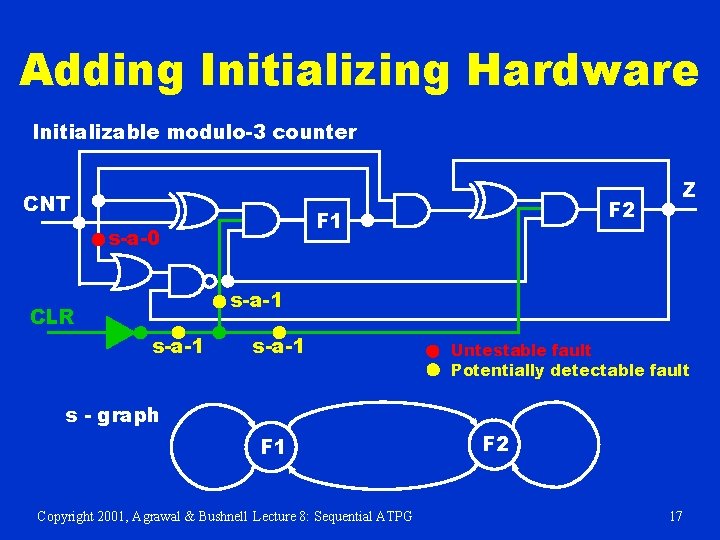

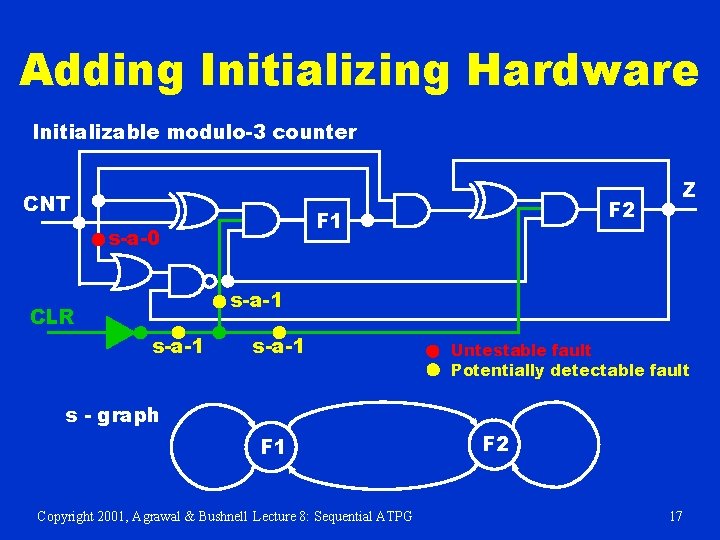

Adding Initializing Hardware Initializable modulo-3 counter CNT F 2 F 1 s-a-0 Z s-a-1 CLR s-a-1 Untestable fault Potentially detectable fault s - graph F 1 Copyright 2001, Agrawal & Bushnell Lecture 8: Sequential ATPG F 2 17

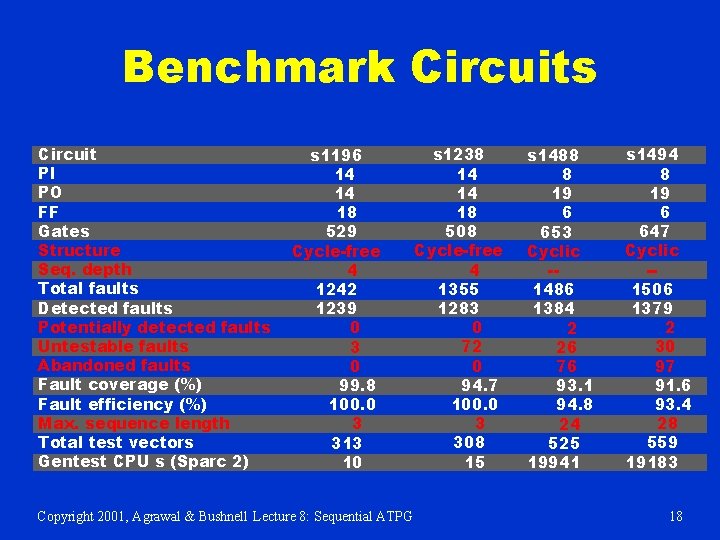

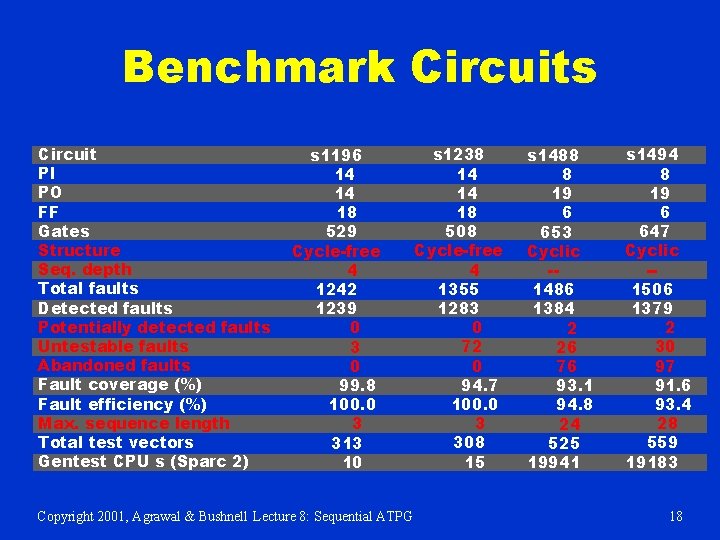

Benchmark Circuits Circuit PI PO FF Gates Structure Seq. depth Total faults Detected faults Potentially detected faults Untestable faults Abandoned faults Fault coverage (%) Fault efficiency (%) Max. sequence length Total test vectors Gentest CPU s (Sparc 2) s 1196 14 14 18 529 Cycle-free 4 1242 1239 0 3 0 99. 8 100. 0 3 313 10 Copyright 2001, Agrawal & Bushnell Lecture 8: Sequential ATPG s 1238 14 14 18 508 Cycle-free 4 1355 1283 0 72 0 94. 7 100. 0 3 308 15 s 1488 8 19 6 653 Cyclic -1486 1384 2 26 76 93. 1 94. 8 24 525 19941 s 1494 8 19 6 647 Cyclic -1506 1379 2 30 97 91. 6 93. 4 28 559 19183 18

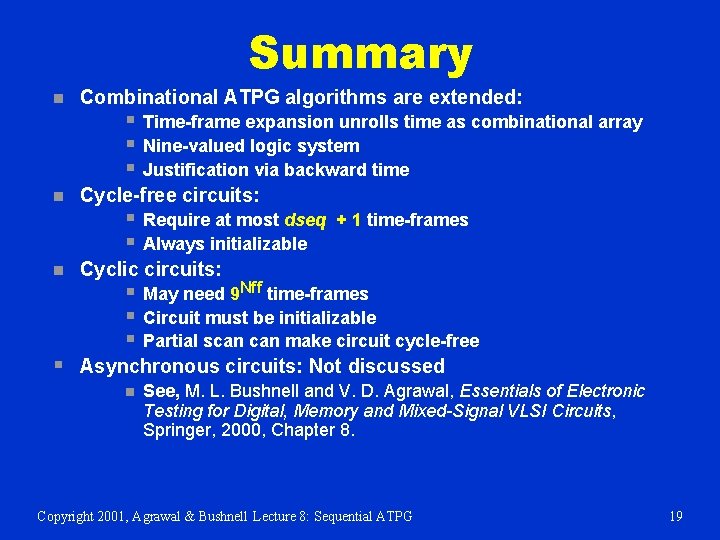

Summary n Combinational ATPG algorithms are extended: § § § n Cycle-free circuits: § § n § Time-frame expansion unrolls time as combinational array Nine-valued logic system Justification via backward time Require at most dseq + 1 time-frames Always initializable Cyclic circuits: § § § May need 9 Nff time-frames Circuit must be initializable Partial scan make circuit cycle-free Asynchronous circuits: Not discussed n See, M. L. Bushnell and V. D. Agrawal, Essentials of Electronic Testing for Digital, Memory and Mixed-Signal VLSI Circuits, Springer, 2000, Chapter 8. Copyright 2001, Agrawal & Bushnell Lecture 8: Sequential ATPG 19

Problems to Solve 1. Which type of circuit is easier to test? Circle one in each: n n n 2. Combinational or sequential Cyclic or cycle-free Synchronous or asynchronous What is the maximum number of input vectors that may be needed to initialize a cycle-free circuit with k flip-flops? Copyright 2001, Agrawal & Bushnell Lecture 8: Sequential ATPG 20

Solution 1. Which type of circuit is easier to test? Circle one in each: q Combinational or sequential q Cyclic or cycle-free q Synchronous or asynchronous 2. What is the maximum number of input vectors that may be needed to initialize a cycle-free circuit with k flip-flops? k vectors. Because that is the maximum sequential depth possible. An example is a k bit shift register. Copyright 2001, Agrawal & Bushnell Lecture 8: Sequential ATPG 21