VLSI System Design Lecture 1 3 Hardware Description

- Slides: 23

VLSI System Design Lecture 1. 3 Hardware Description Languages (HDLs) Engr. Anees ul Husnain ( anees. buzdar@gmail. com ) Department of Computer Systems Engineering, College of Engineering & Technology, IUB

In this Lecture o o o Design steps Designing through HDLs Introduction HDLs What and why HDL Verilog HDL Modelling a simple circuit. n n Delays Stimulus

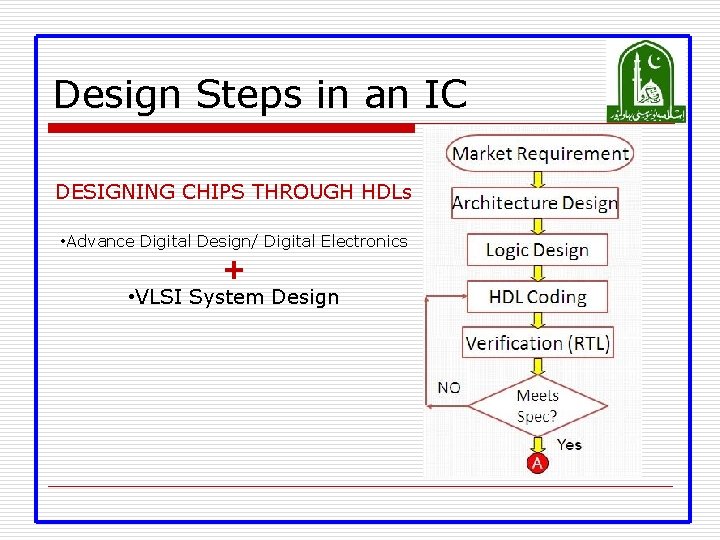

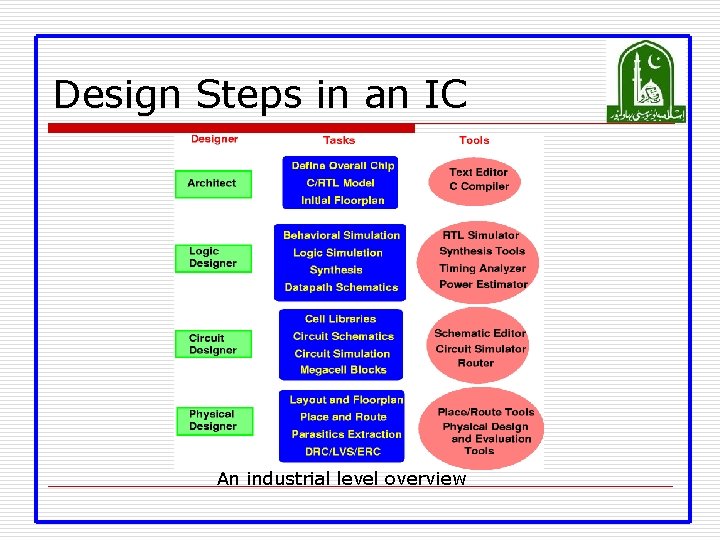

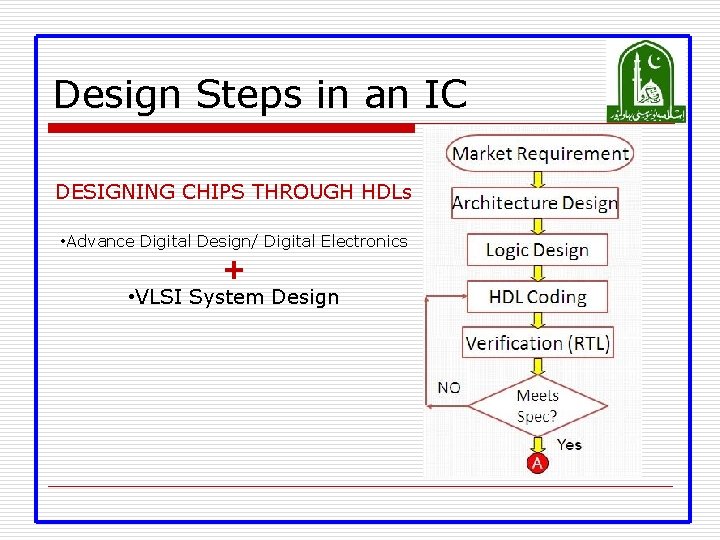

Design Steps in an IC DESIGNING CHIPS THROUGH HDLs • Advance Digital Design/ Digital Electronics + • VLSI System Design

Design Steps in an IC o o Design Description Optimization Simulation Synthesis + o Physical design o Critical sub-systems o Enhancing speeds through design o Floor planning n so on…

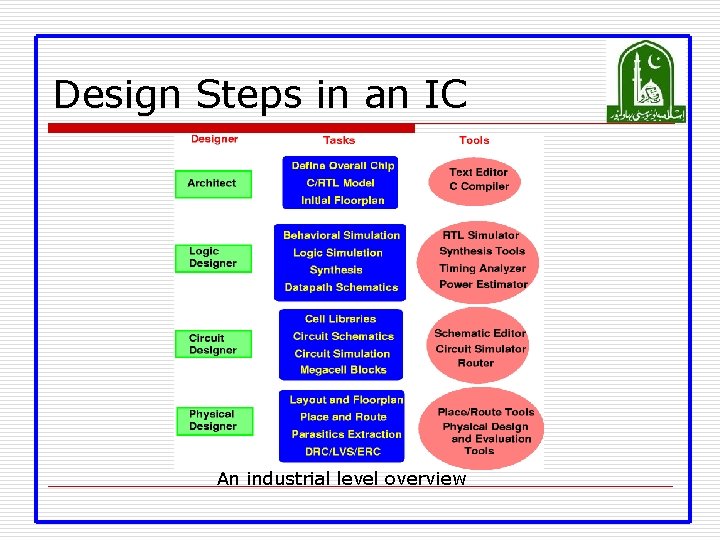

Design Steps in an IC An industrial level overview

Hardware Description Language (HDL) o Basic idea is a programming language to describe hardware o Initial purpose was to allow abstract design and simulation n Design could be verified then implemented in hardware o Now Synthesis tools allow direct implementation from HDL code. n Large improvement in designer productivity

HDL o HDL allows write-run-debug cycle for hardware development. n Similar to programming software n Much, much faster than design-implement-debug o Combined with modern Field Programmable Gate Array chips large complex circuits (100000 s of gates) can be implemented.

HDLs o There are many different HDLs n Verilog HDL n ABEL – Advance Boolean Expressions Language n VHDL o VHDL is the most common n Large standard developed by US Do. D n VHDL = VHSIC HDL n VHSIC = Very High Speed Integrated Circuit

Verilog HDL o Verilog HDL is second most common n Easier to use in many ways = better for teaching n C - like syntax o History n Developed as proprietry language in 1985 n Opened as public domain spec in 1990 o Due to losing market share to VHDL n Became IEEE standard in 1995

Verilog HDL o Verilog constructs are use defined keywords n Examples: and, or, wire, input output o One important construct is the module n Modules have inputs and outputs n Modules can be built up of Verilog primatives or of user defined submodules.

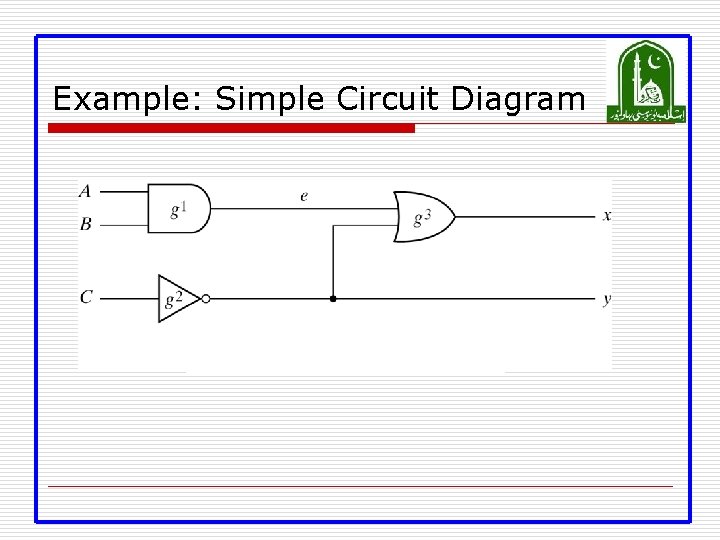

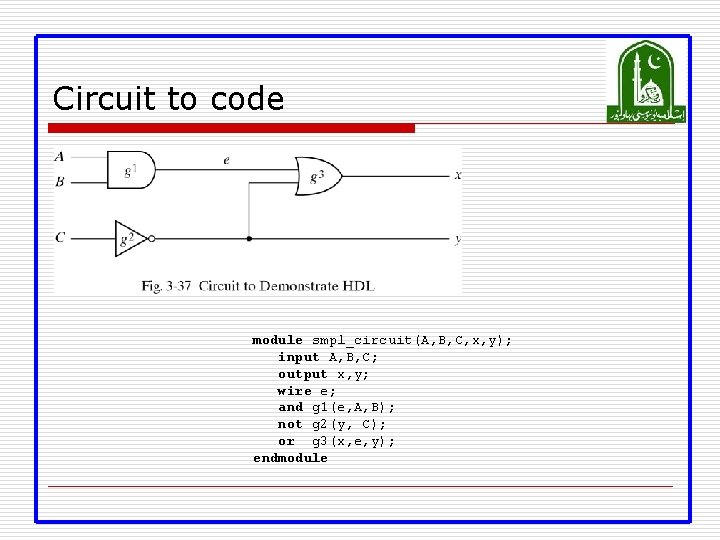

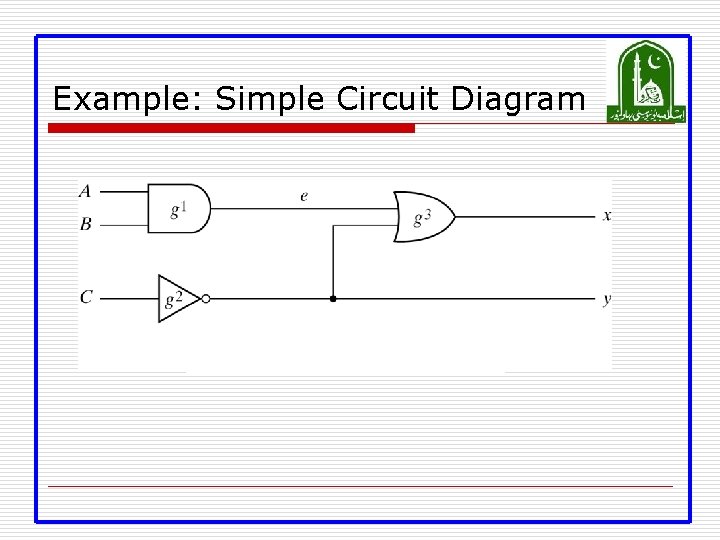

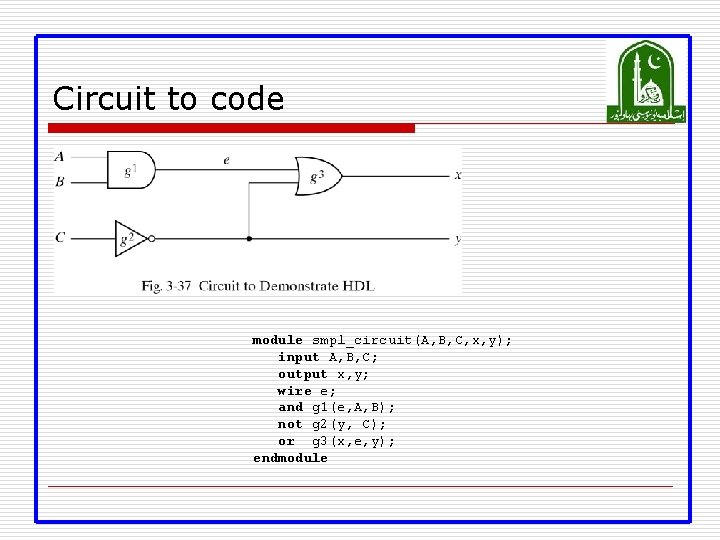

Example: Simple Circuit Diagram

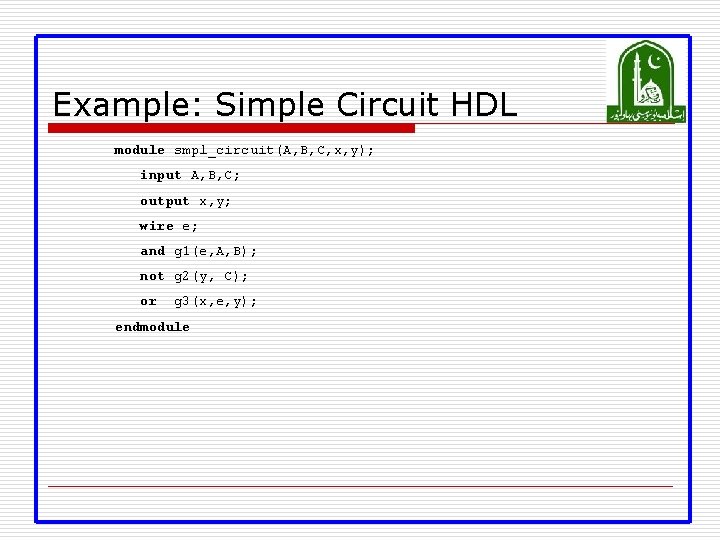

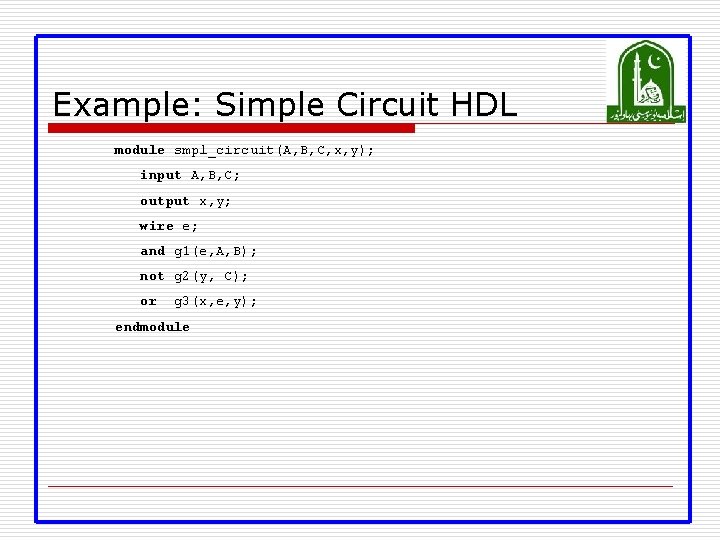

Example: Simple Circuit HDL module smpl_circuit(A, B, C, x, y); input A, B, C; output x, y; wire e; and g 1(e, A, B); not g 2(y, C); or g 3(x, e, y); endmodule

Simple Circuit Notes o The module starts with module keyword and finishes with endmodule. o Internal signals are named with wire. o Comments follow // o input and output are ports. These are placed at the start of the module definition. o Each statement ends with a semicolon, except endmodule.

Circuit to code module smpl_circuit(A, B, C, x, y); input A, B, C; output x, y; wire e; and g 1(e, A, B); not g 2(y, C); or g 3(x, e, y); endmodule

Adding Delays o To simulate a circuits real world behaviour it is important that propagation delays are included. o The units of time for the simulation can be specified with timescale. n Default is 1 ns with precision of 100 ps o Component delays are specified as #(delay)

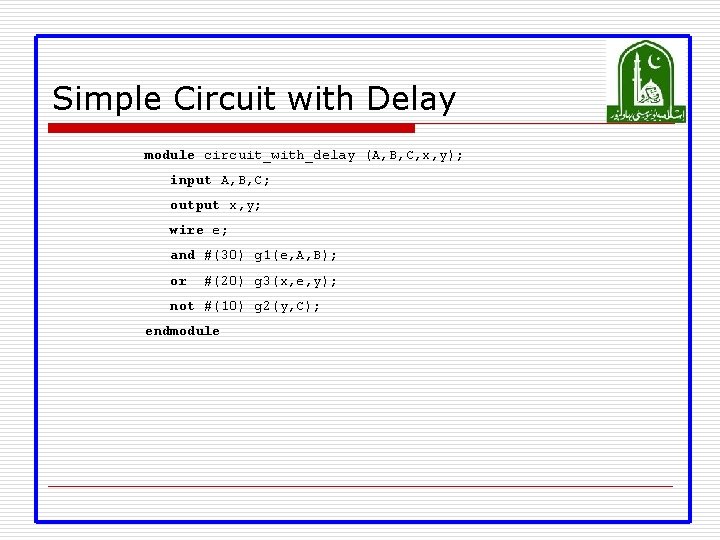

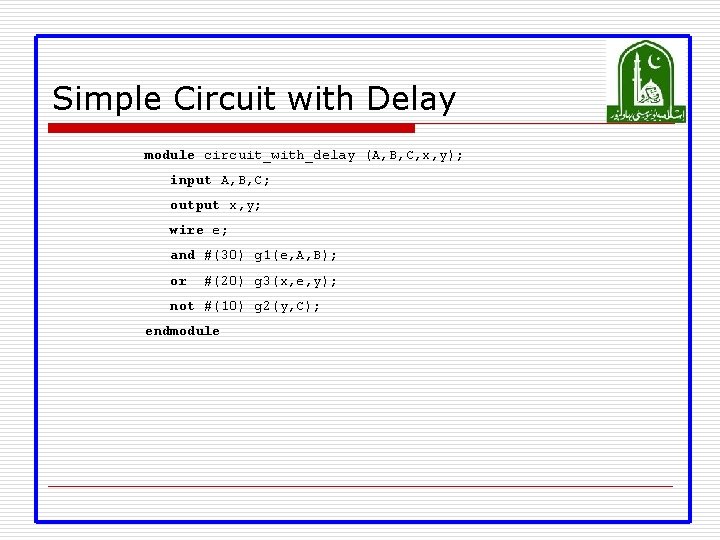

Simple Circuit with Delay module circuit_with_delay (A, B, C, x, y); input A, B, C; output x, y; wire e; and #(30) g 1(e, A, B); or #(20) g 3(x, e, y); not #(10) g 2(y, C); endmodule

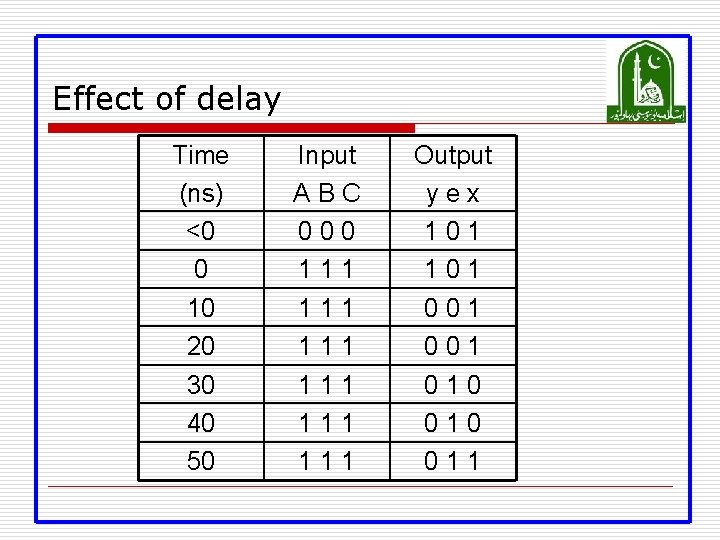

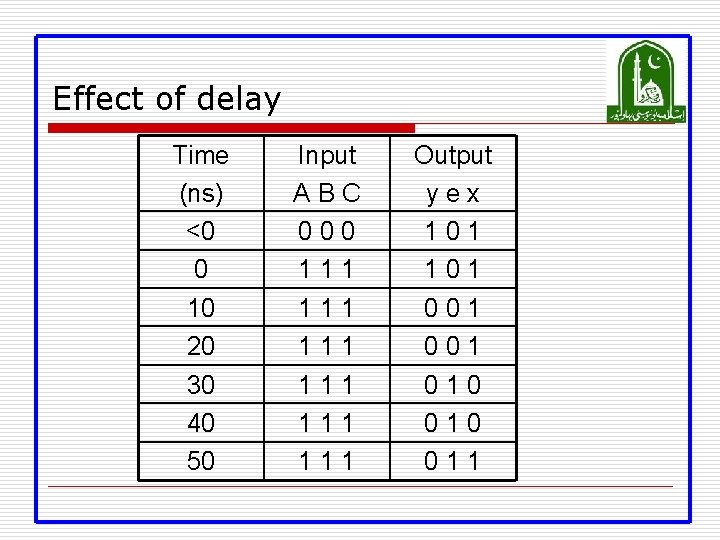

Effect of delay Time (ns) <0 0 10 20 30 40 50 Input ABC 000 111 111 111 Output yex 101 001 010 011

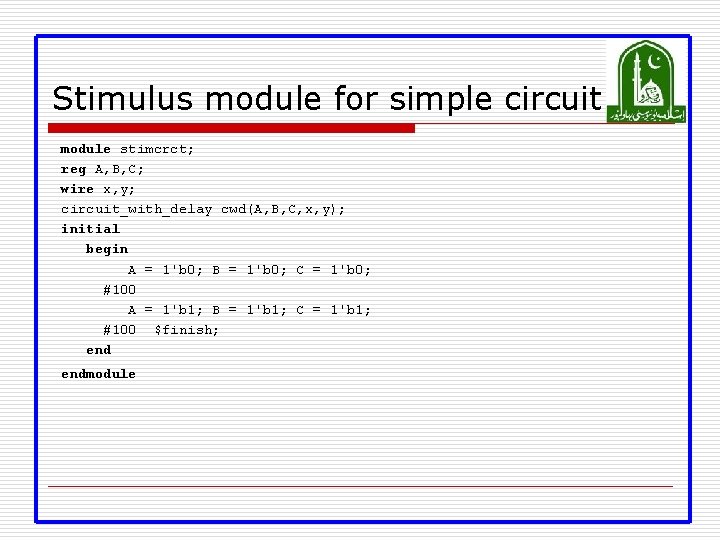

Input signals o In order to simulate a circuit the input signals need to be known so as to generate an output signal. o The input signals are often called the circuit stimulus. o An HDL module is written to provide the circuit stimulus. This is known as a testbench.

Testbench o The testbench module includes the module to be tested. o There are no input or output ports for the testbench. o The inputs to the test circuit are defined with reg and the outputs with wire. o The input values are specified with the keyword initial o A sequence of values can be specified between begin and end.

Signal Notation o In Verilog signals are generalised to support multi-bit values (e. g. for buses) n The notation A = 1’b 0; n means signal A is one bit with value zero. o The end of the simulation is specified with $finish.

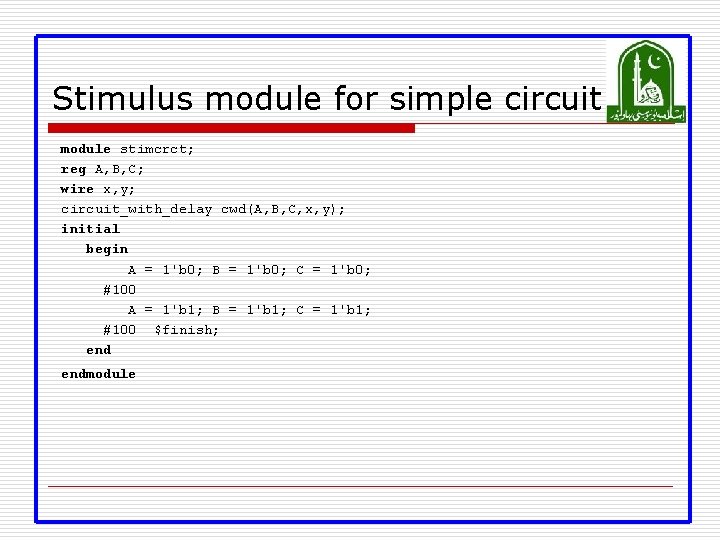

Stimulus module for simple circuit module stimcrct; reg A, B, C; wire x, y; circuit_with_delay cwd(A, B, C, x, y); initial begin A = 1'b 0; B = 1'b 0; C = 1'b 0; #100 A = 1'b 1; B = 1'b 1; C = 1'b 1; #100 $finish; endmodule

Tools you’re equipped with… o Xilinx ISE o ISE Simulator

Language what you need o Verilog… o Syntax & Structure (at Lab hours)